B638128/607

1/2

Complete data available on

DATA-on-DISC CD-ROM

or at

www.st.com

LOW VOLTAGE: 3.3V

±

0.3V

128K x 8 VERY FAST SRAM with OUTPUT

ENABLE

EQUAL CYCLE and ACCESS TIMES:

12, 15, 20ns

LOW V

CC

DATA RETENTION: 2V

TRI-STATE COMMON I/O

JEDEC PLASTIC SOJ, 400 mil PACKAGE

DESCRIPTION

The M638128 is a 1 Megabit (1,048,576 bit) Fast

CMOS SRAM, organized as 131,072 words by 8

bits. It is fabricated using SGS-THOMSON’s Ad-

vanced, low power, high performance, CMOS tech-

nology. The device features fully static operation

requiring no external clocks or timing strobes, with

equal address access and cycle times. It requires

a single 3.3V

±

0.3V supply, and all inputs and

outputs are TTL compatible.

M638128

LOW VOLTAGE 1 Megabit (128K x 8) VERY FAST SRAM

WITH OUTPUT ENABLE

DATA BRIEFING

AI01878

17

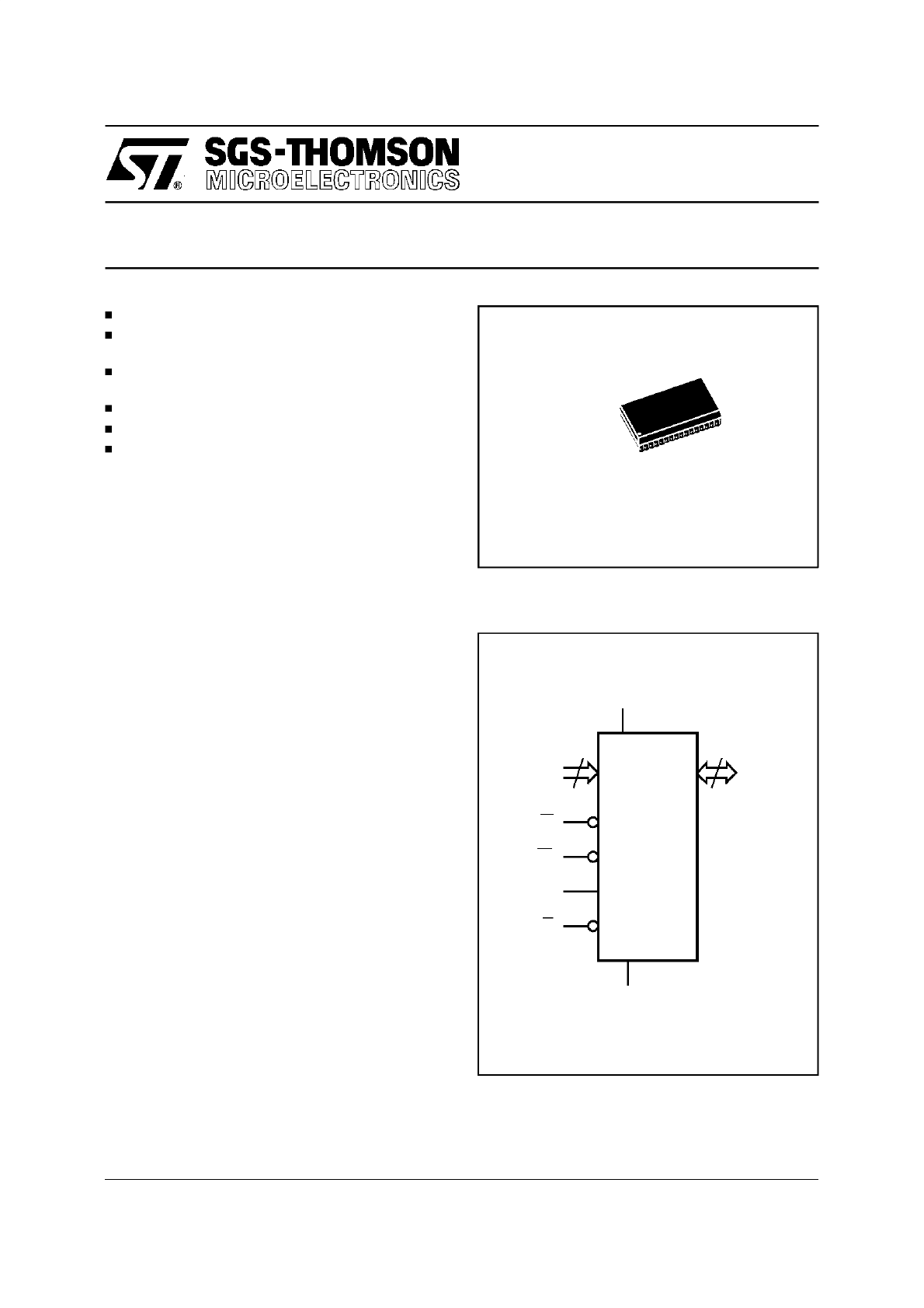

A0-A16

W

DQ0-DQ7

VCC

M638128

G

E2

VSS

8

E1

Logic Diagram

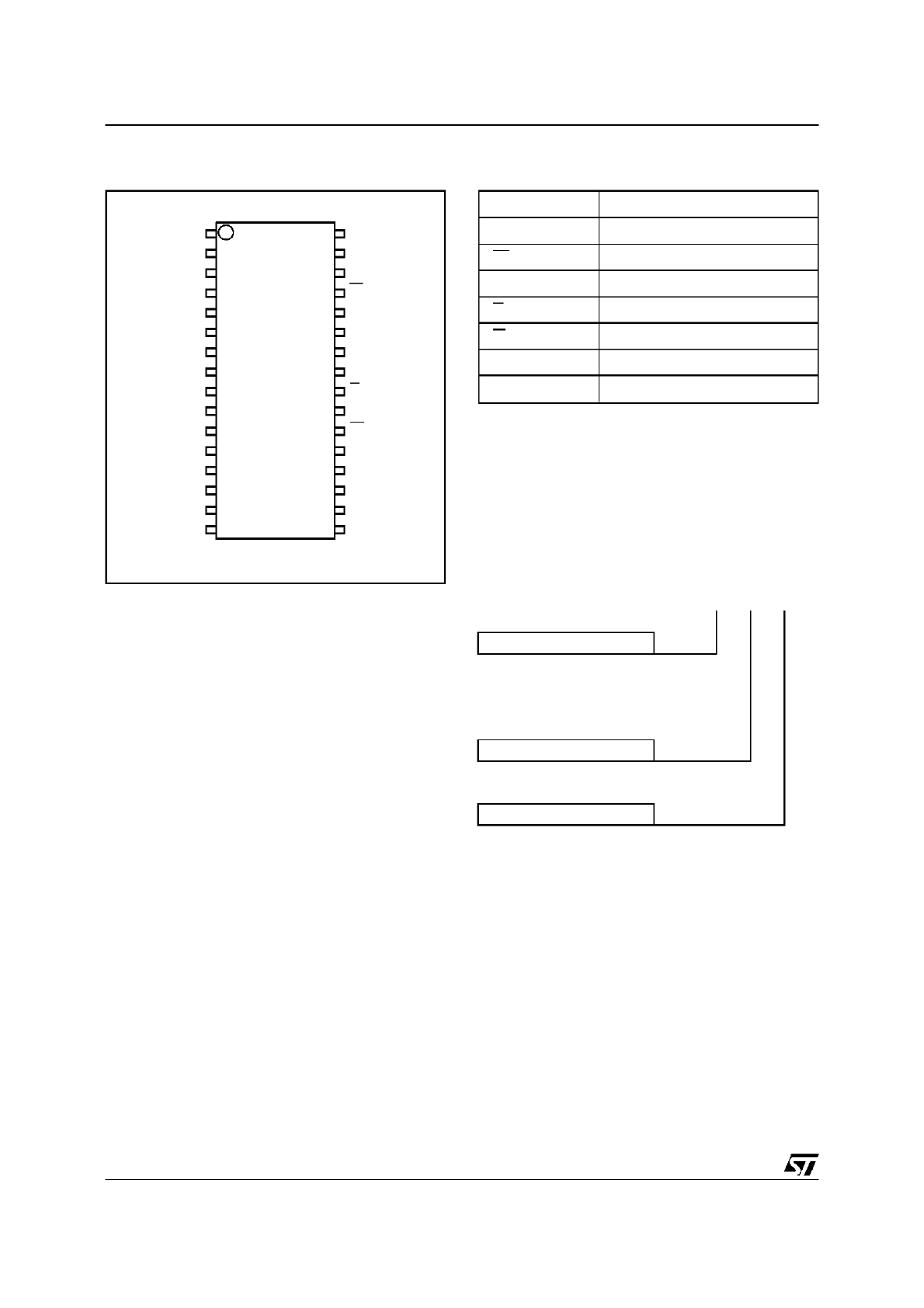

32

1

SOJ32 (E)

300 mils

M638128

A0 - A16

Address Inputs

DQ0 - DQ7

Data Inputs / Outputs

E1

Chip Enable 1

E2

Chip Enable 2

G

Output Enable

W

Write Enable

V

CC

Supply Voltage

V

SS

Ground

Signal Names

AI01879

8

2

3

4

5

6

7

9

10

11

12

13

14

22

21

20

19

18

17

16

15

28

27

26

25

24

23

1

A1

A0

DQ0

A14

A4

A3

A2

A6

A5

E2

A10

A8

A9

DQ7

A15

A11

G

E1

DQ5

DQ1

DQ2

DQ3

VSS

DQ4

DQ6

A16

NC

VCC

M638128

A13

W

A7

A12

32

31

30

29

SOJ Pin Connections

Warning: NC = Not Connected.

Example:

M638128

-15

E

1

Speed

-12

12ns

-15

15ns

-20

20ns

Package

E

SOJ32 300 mils

Temp. Range

1

0 to 70

°

C

Ordering Information Scheme

For a list of available options refer to the current

Memory Shortform catalogue.

For further information on any aspect of this device,

please contact the SGS-THOMSON Sales Office

nearest to you.

2/2