C167 FAMILY

PRELIMINARY

USER MANUAL

C167 FAMILY PRELIMINARY USER MANUAL

2/180

USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED

SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE

SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON

Microelectronics.

As used herein:

1. Life support devices or systems are those which

(a) are intended for surgical implant into the body,

or (b) support or sustain life, and whose failure to

perform, when properly used in accordance with

instructions for use provided with the product, can

be reasonably expected to result in significant

injury to the user.

2. A critical component is any component of a life

support device or system whose failure to perform

can reasonably be expected to cause the failure of

the life support device or system, or to affect its

safety or effectiveness.

C167 FAMILY PRELIMINARY USER MANUAL

3/180

TABLE OF CONTENTS

TABLE OF CONTENTS ................................ ......................... ....... ..............................

3

ST10167......................... ....... ............................. ..........................................................

5

1. Instruction Set................................................................................................ ........

7

1.1 Atomic Instruction............................ .................................................................7

1.2 Extend Segment/Extend Page Instructions .................................................... 8

1.3 Extend Register Instructions...........................................................................8

2. On-Chip Memory ......................... ....... ............................. ...................................

23

2.1 On-Chip ROM ...............................................................................................23

2.2 On-Chip RAM............................ ....................................................................24

2.3 PEC Pointer Address Space............................. ............................................26

2.4 Extended Special Function Register Space (ESFR)......................... ....... .....26

2.5 Internal Address Space.................................................................................29

3. Bus Control Unit......................... ....... ............................. ....................................

31

3.1 Extended Address Space ........................ ........ ............................ .................

31

3.2 System and Bus Configuration Control............................... ..........................33

3.2.1

SYSCON Register...............................................................................33

3.2.2

BUSCON0 Register................................ .......................... ...................

36

3.2.3

BUSCON1..4 and ADDRSEL1..4 Registers........................................ 38

3.3 Chip Selects ................................................................ ........................ ........ ..

43

3.3.1

Address Chip Selects ............................. .............................................44

3.3.2

Read/Write Chip Selects......................................................................45

3.4 Byte High Enable or Write High , Write Low Operation......................... ....... .47

3.5 System Startup Configuration................................................................ .......51

3.6 On-Chip Bootstrap Loader............................................................................ 58

4. PWM Module................................................................................................ .......

61

4.1 PWM-Channel.............................. .................................................................62

4.1.1

Operating Modes................................ ........................ ........ .................

63

4.1.2

PWM Module Registers.......................... .................................... .........

71

4.1.3

Interrupt Request Generation.............................................................. 76

4.1.4

PWM Output Signals ................................................................ ...........

78

5. Second Capture/Compare Unit, CAPCOM2 .....................................................79

6. Asynchronous/Synchronous Serial Interface................................................. 87

6.1 Even / Odd Parity Selection.............................. ............................................87

6.2 Double Buffered Transmit ............................. ................................................88

7. Synchronous Serial Channel, SSC........................ ........ ............................ .......

91

7.1 SSC Block Diagram ................................................................ ......................

91

7.2 General Operation of the SSC ......................................................................93

7.3 SSC Control, Status and Data Registers...................................................... 94

C167 FAMILY PRELIMINARY USER MANUAL

4/180

7.3.1

SSC Control Register SSCCON.......................... ................................94

7.3.2

Buffer Registers SSCTB and SSCRB ................................ ...............100

7.3.3

Baud Rate Register SSCBR................................ ..............................100

7.3.4

Interrupt Control Registers ................................................................101

7.3.5

Port Control Registers .......................................................................103

7.4 Detailled Operation of the SSC ...................................................................105

7.4.1

Single Master, Full-Duplex Operation................................................ 106

7.4.2

Multi-Master, Full-Duplex Operation.................................................. 109

7.4.3

Half-Duplex Operation....................................................................... 110

7.4.4

Continuous Transfers ........................... .................................... .........

112

7.5 Error Detection................................................................ ............................ 113

7.5.1

Receive Error (Master and Slave Mode)........................................... 114

7.5.2

Phase Error (Master and Slave Mode)................................ ..............114

7.5.3

Baud Rate Error (Slave Mode).......................................................... 115

7.5.4

Transmit Error (Slave Mode)............................................................. 115

8. A/D Converter (ADC) ........................................................................................117

8.1 Additional A/D Input Channels ........................ ........ ............................ ........117

8.2 Wait for ADDAT Read Mode........................... .................................... ........

118

8.3 Channel Injection Mode ............................... ...............................................122

9. GPT1 and GPT2 Enhancements ............................... ......................................127

10. Interrupt System...............................................................................................133

10.1 External Interrupts................................................................ ..................... 133

10.2 Additional Peripheral Interrupts................................ ........................... ......134

11. Ports ................................................................................................ ..................

137

11.0 PORT0: Ports P0L and P0H ....................................................................141

11.1 PORT1: Ports P1L and P1H ....................................................................144

11.2 PORT2 ................................ ........................ ........ ........................... ...........

146

11.3 PORT3 ................................ ........................ ........ ............................ ..........

148

11.4 PORT4 ................................ ........................ ........ ............................ ..........

151

11.5 PORT5 ................................ ........................ ........ ............................ ..........

153

11.6 PORT6 ................................ ........................ ........ ............................ ..........

154

11.7 PORT7 ................................ ........................ ........ ............................ ..........

159

11.8 PORT8 ................................ ........................ ........ ............................ ..........

163

12. Dedicated Pins................... ............................................. ........................... .......

167

13. Pinout ................................................................................................................169

14. Index (figures) ............................ ......................................................................179

C167 FAMILY PRELIMINARY USER MANUAL

5/180

ST10167

This Preliminary User Manual describes the enhancements bring to the new ST10

Family, the C167 Family and specially the ST10167 which is the first derivative

component of the C167 Family. Compared to the ST10x166, besides adding more

functionality in the peripheral and bus controller section, some enhancements and

changes are made in the CPU core of the C167. The following list gives a short

overview on the additional features and functions of the ST10167:

-

8 KByte On-Chip Mask-Programmable ROM

-

2 KByte On-Chip RAM

Extended System Stack, Variable, and Register Bank Space

PEC Pointers Mapped to Non-Bitaddressable Space

-

Additional Instructions to Support HLL and Operating Systems

-

Extended Address Range up to 16 MByte

-

Five Bus Configuration Registers

-

Five Selectable Chip Select Signals

-

Extended SFR Space

-

Enhanced A/D Converter Operation:

16 Analog Input Channels

Wait for Read Mode: Start New Conversion after ADDAT Read

Channel Injection: Convert Specific Channel during Auto Scan or

Continuous Mode

-

Second Capture/Compare Unit with 16 Channels

-

Serial Interfaces:

One Synchronous/Asynchronous Serial Interface (ASC0) with Even/Odd

Parity Selection

One Synchronous Serial Interface (SSC) with Master/Slave Option

-

Pulse Width Modulation (PWM) Unit with 4 Independent Channels:

Up to 78 KHz Frequency with 8-Bit Resolution

Four Modes of Operation: Standard, Symetrical, Burst Mode, Single Shot

-

Extended Interrupt System:

8 Fast External Interrupt Inputs, 50 ns Sample Rate

24 Additional Interrupt Sources and Vectors

-

On-Chip Bootstrap Loader

-

144-Pin MQFP Package (EIAJ)

C167 FAMILY PRELIMINARY USER MANUAL

6/180

In this document, only these add-on features and differences of the C167 compared

to the ST10x166 are described. For more detailled information about features and

functions of the ST10 family please refer to the ST10 User Manual.

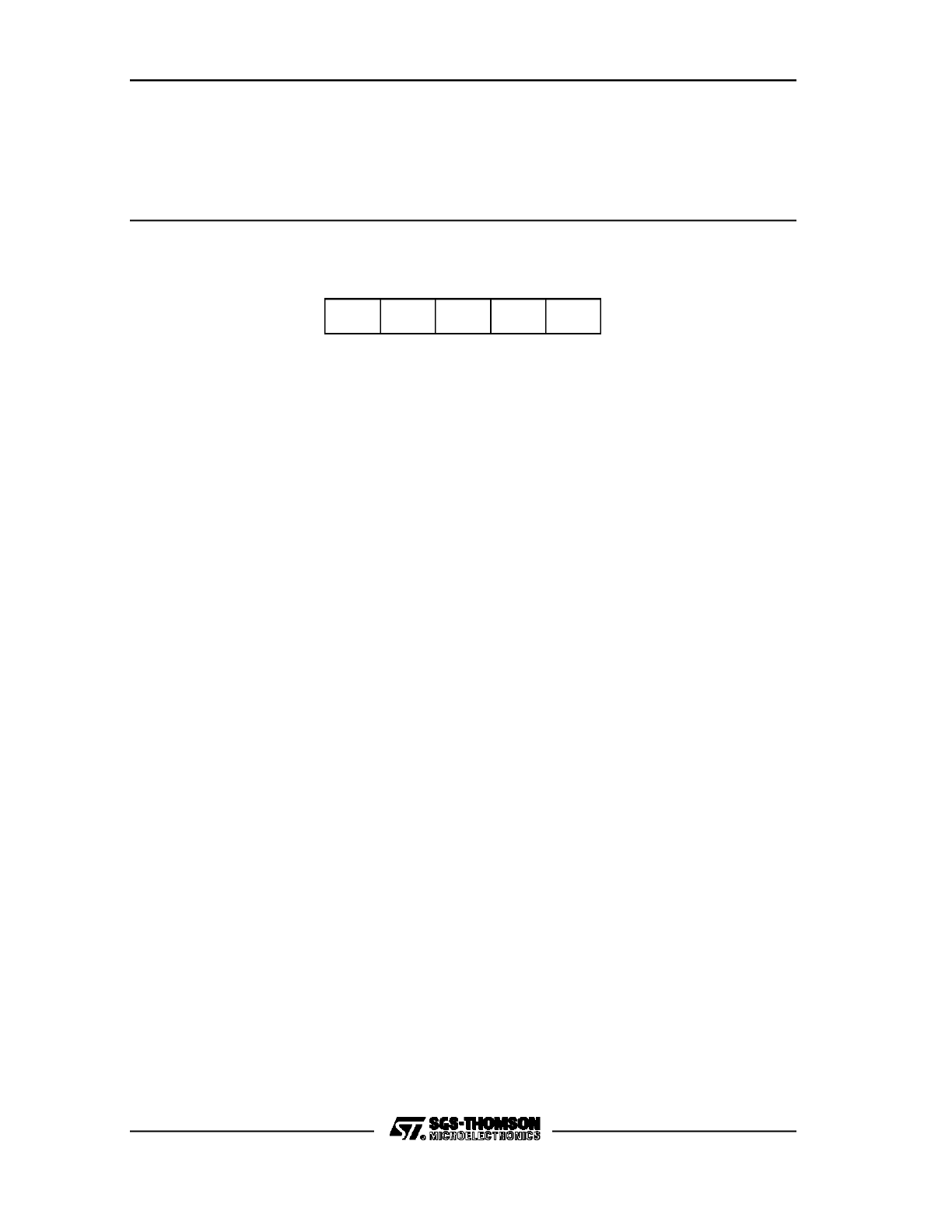

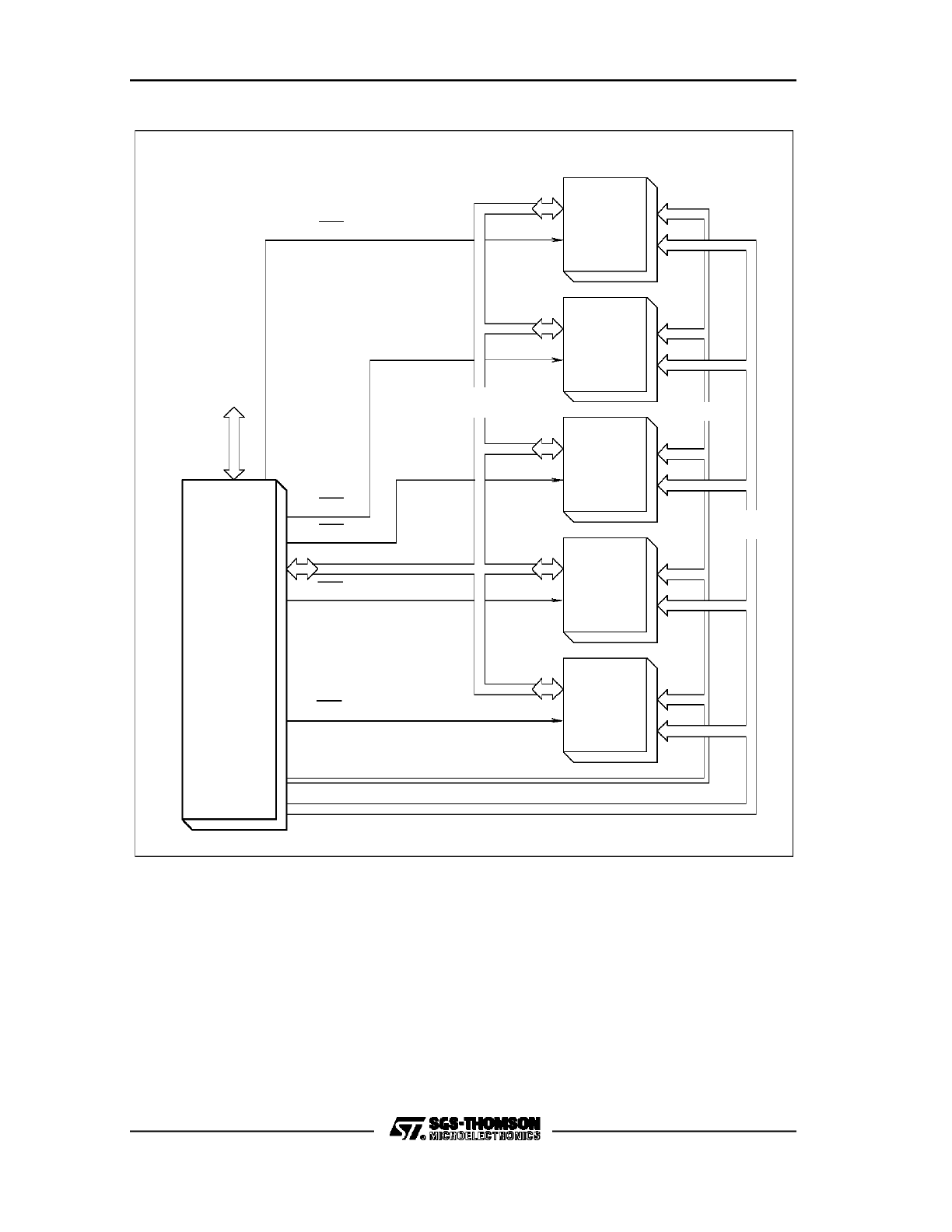

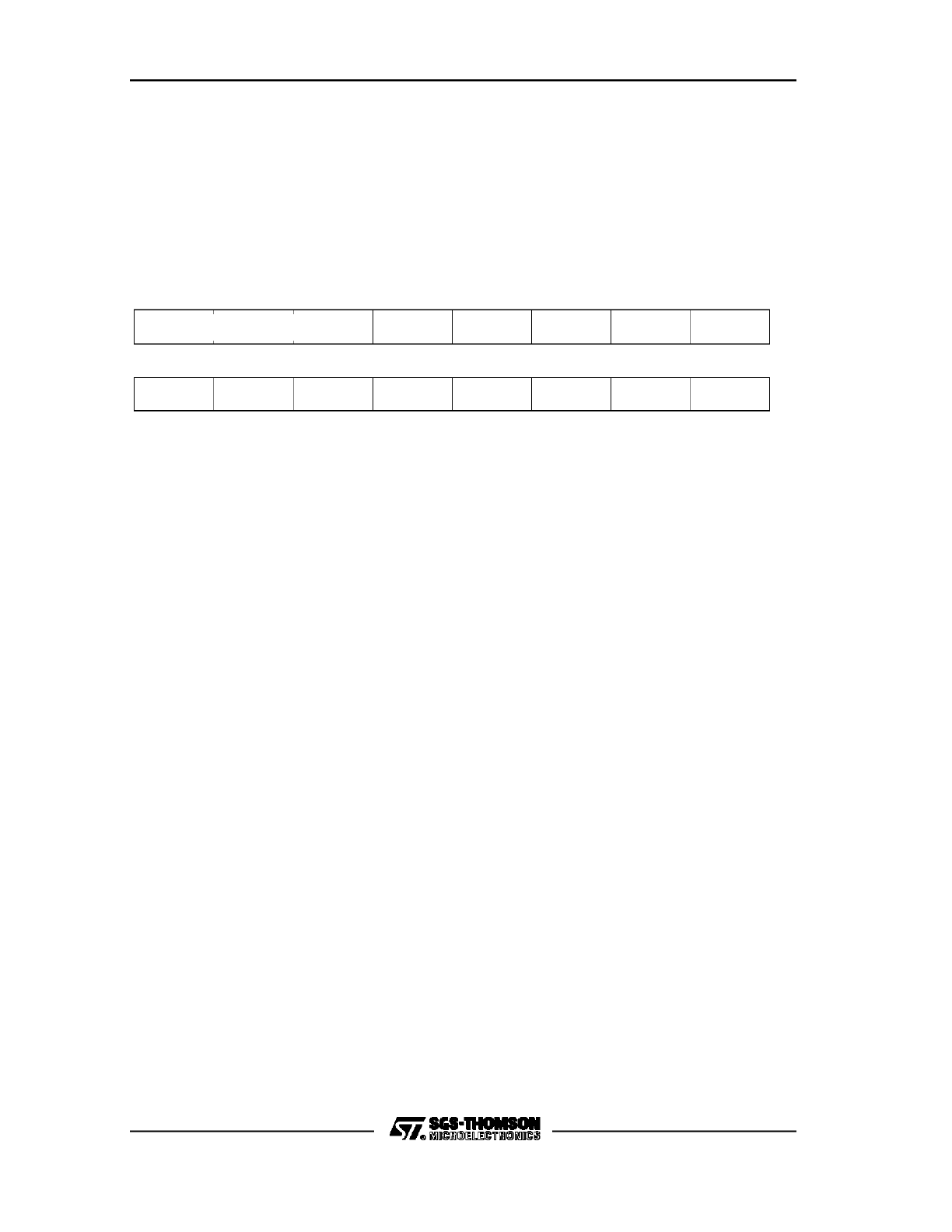

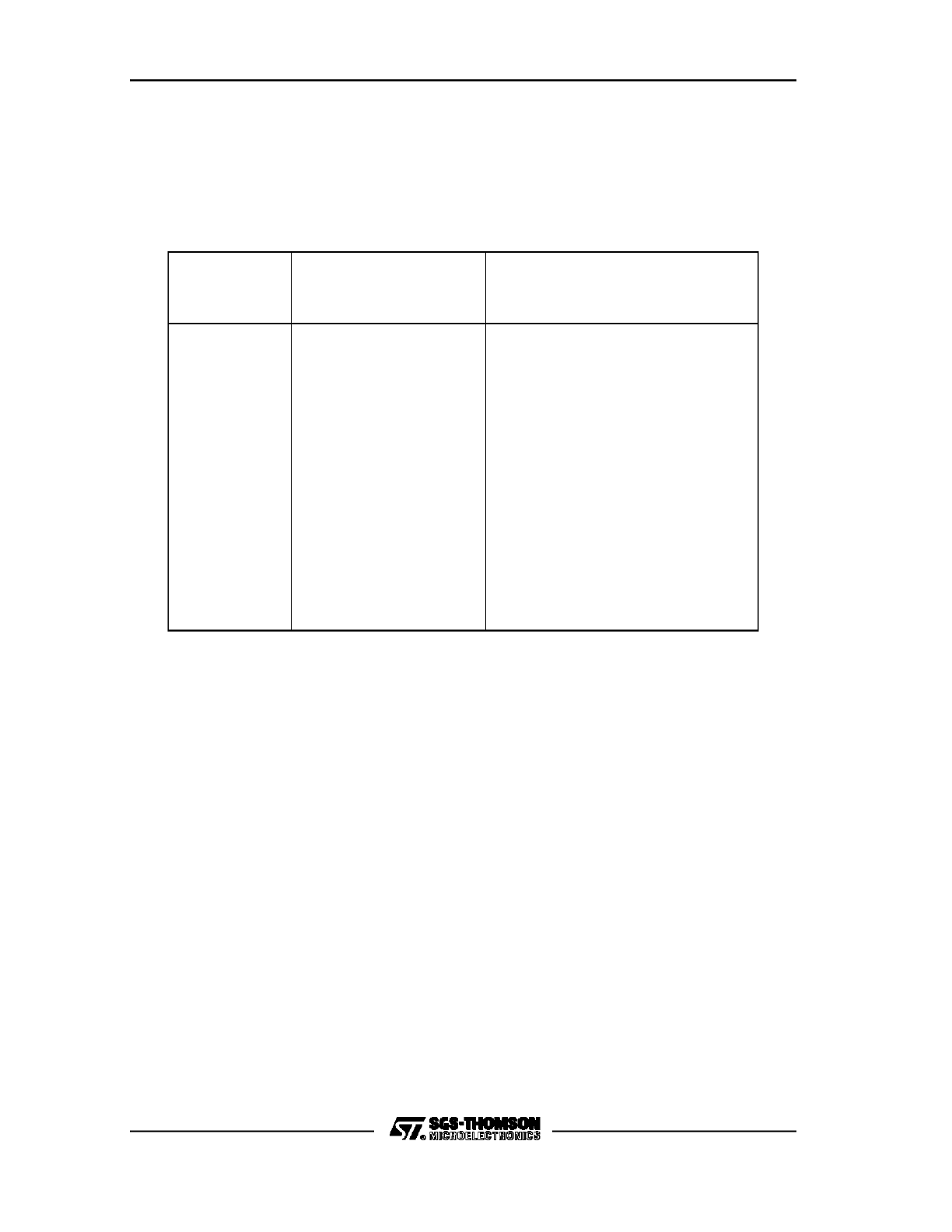

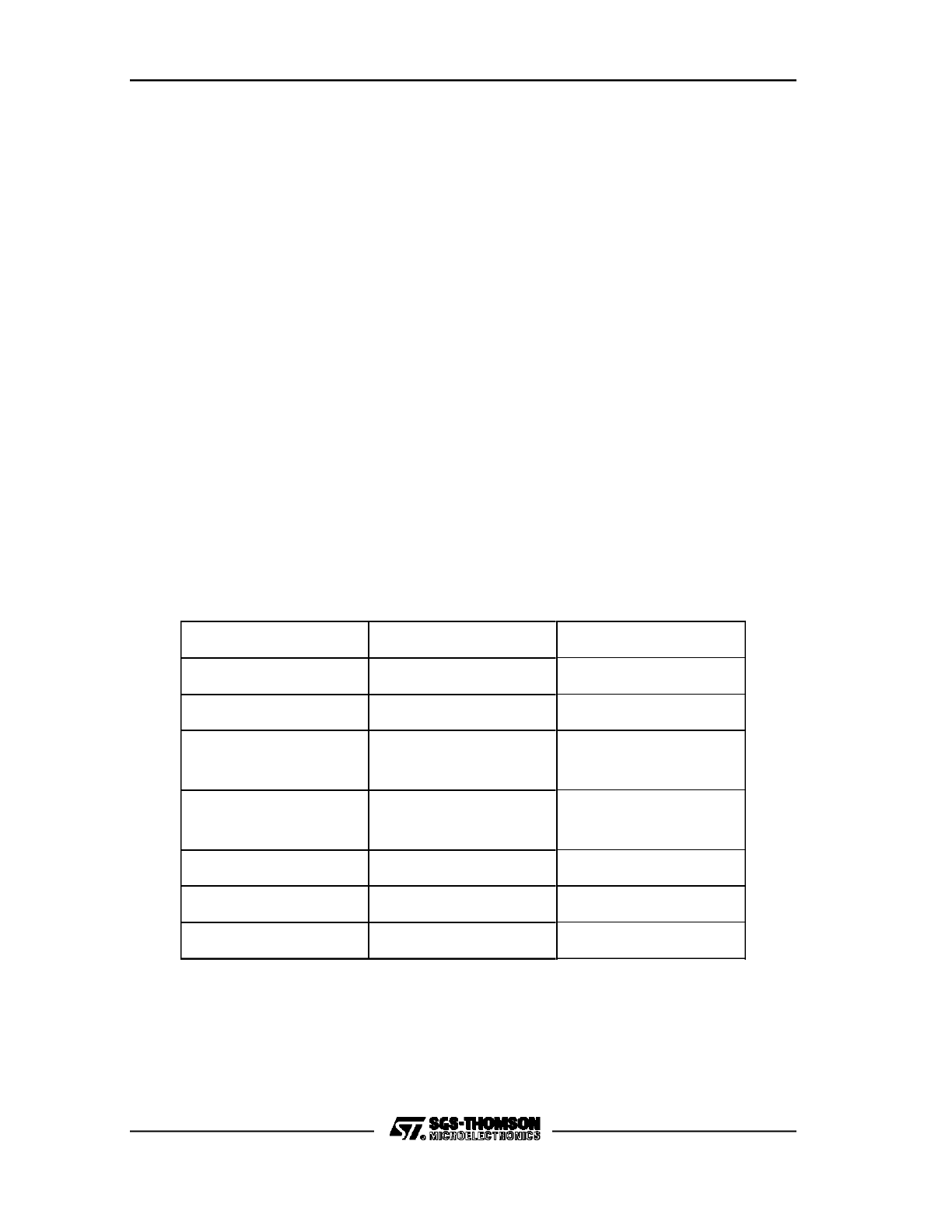

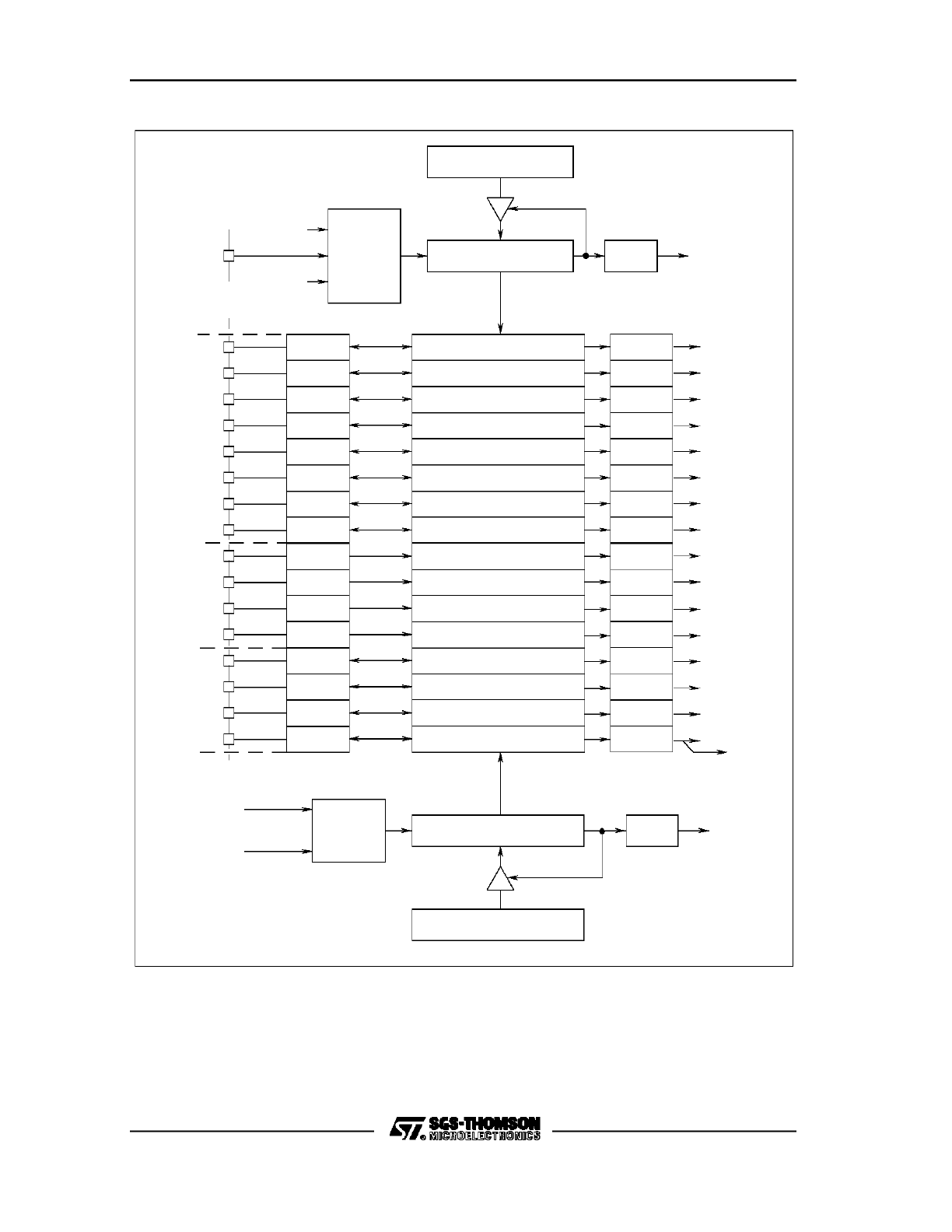

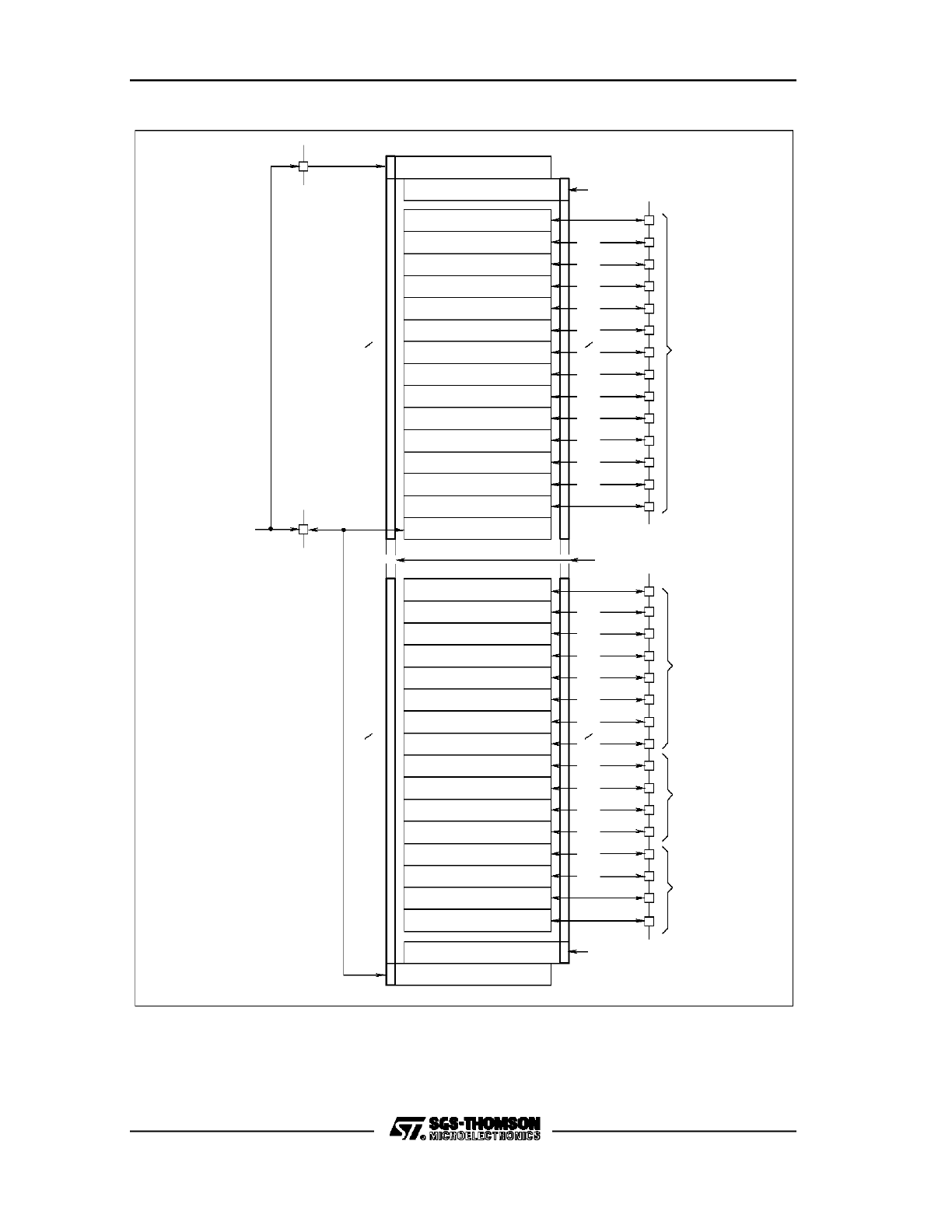

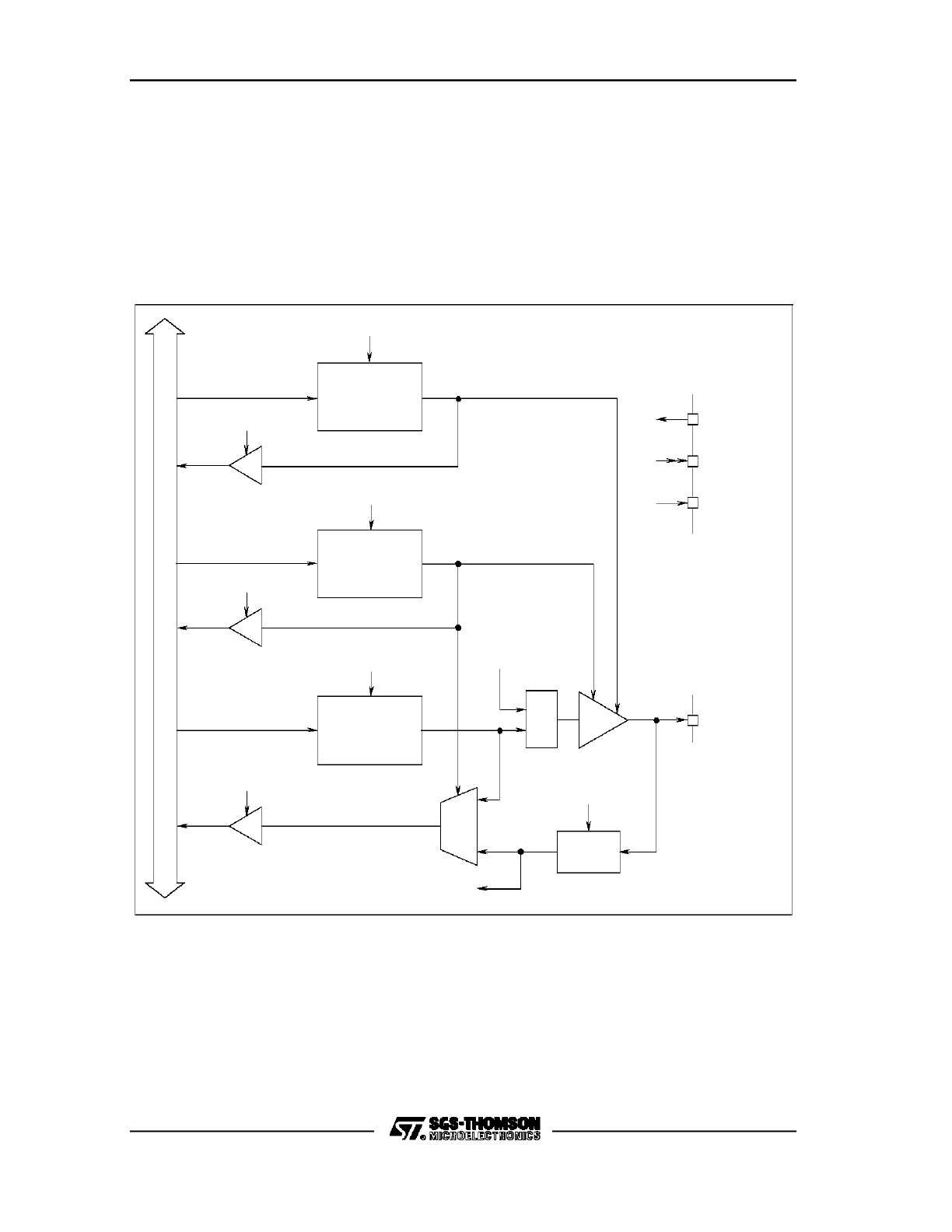

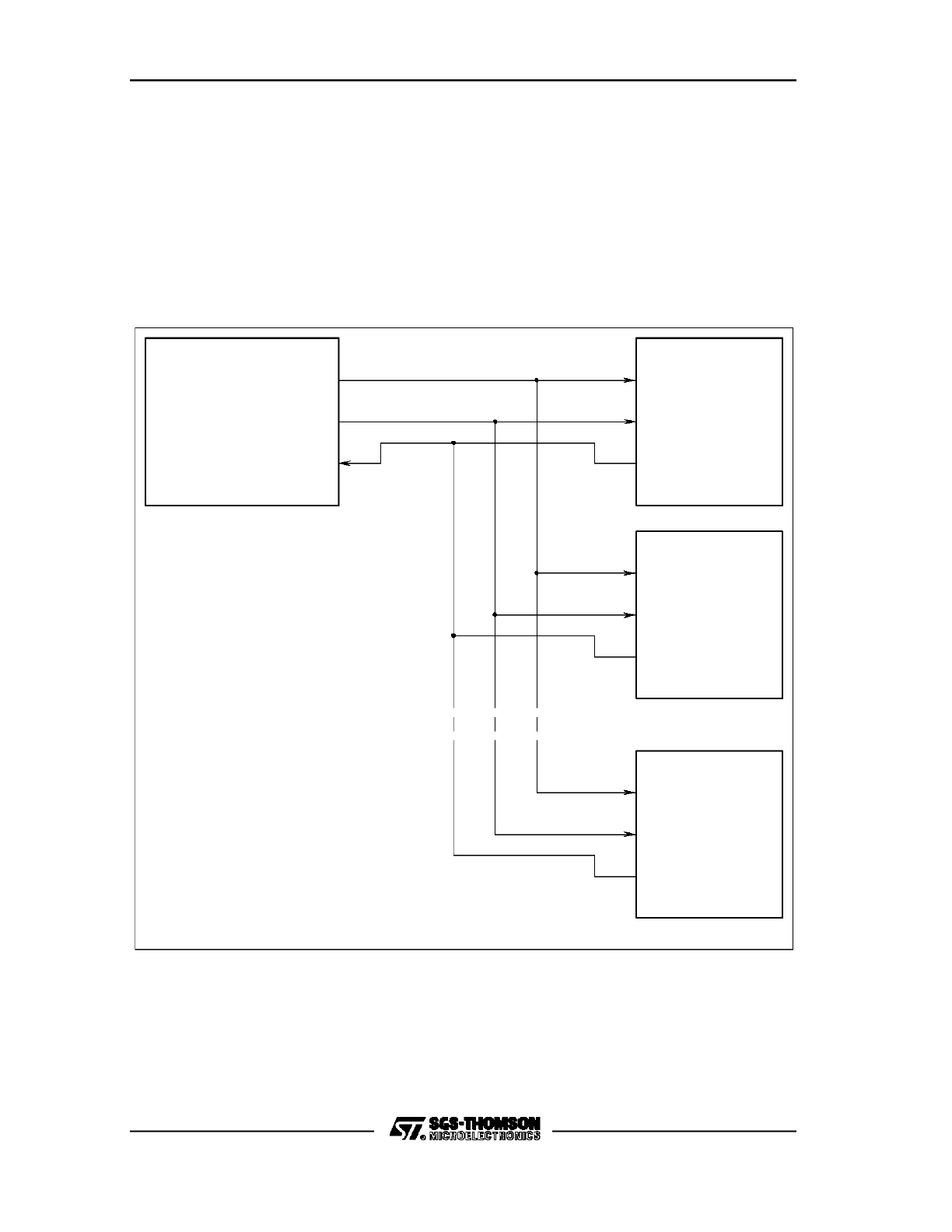

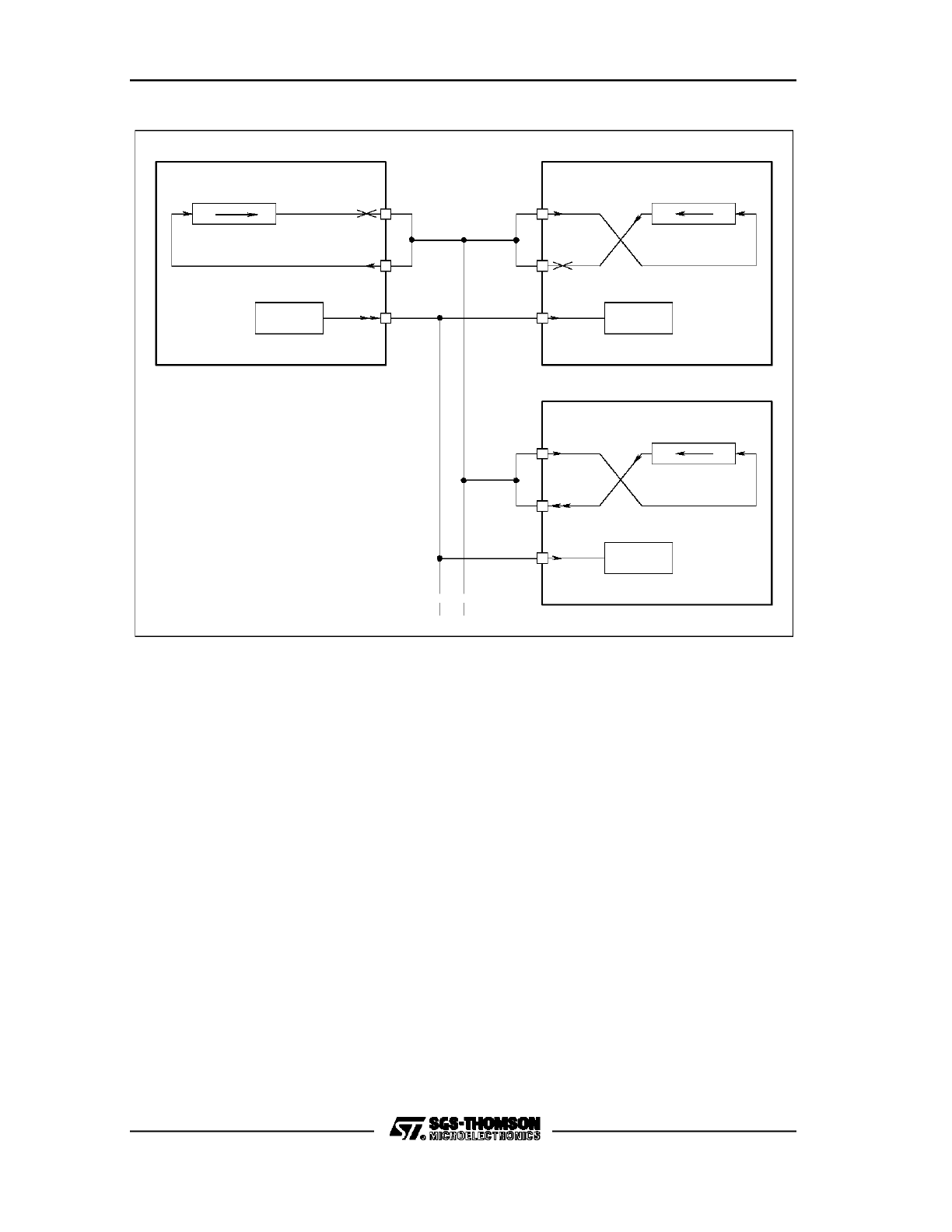

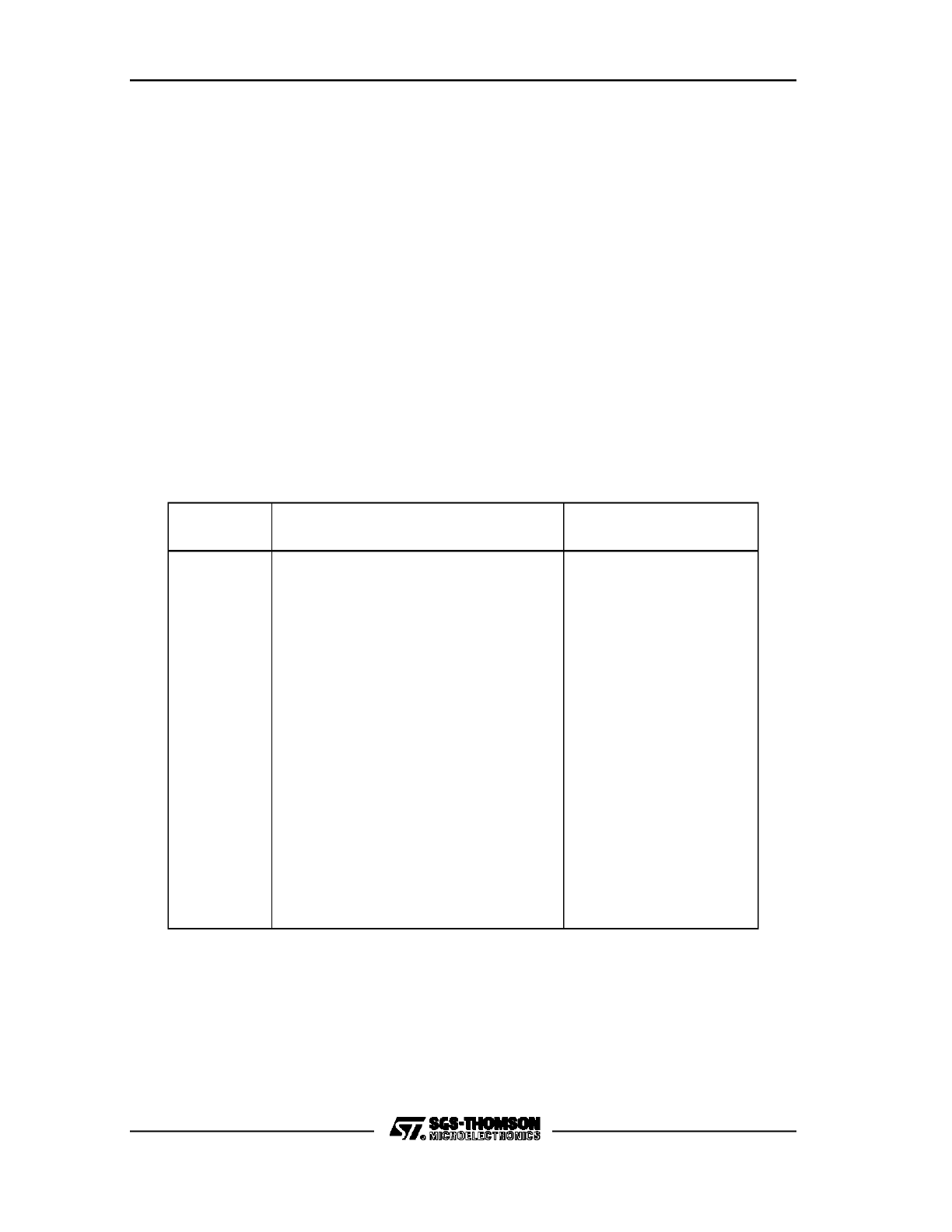

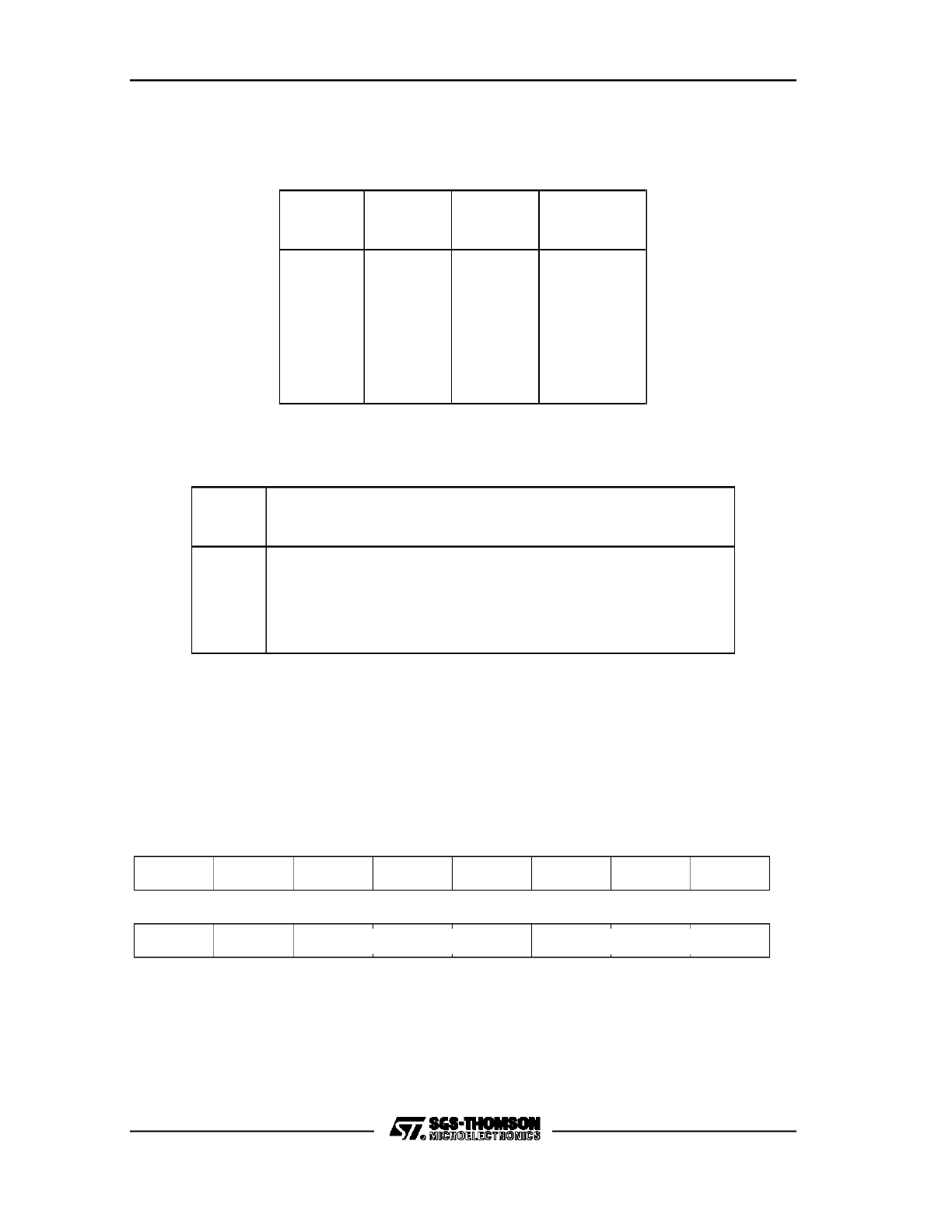

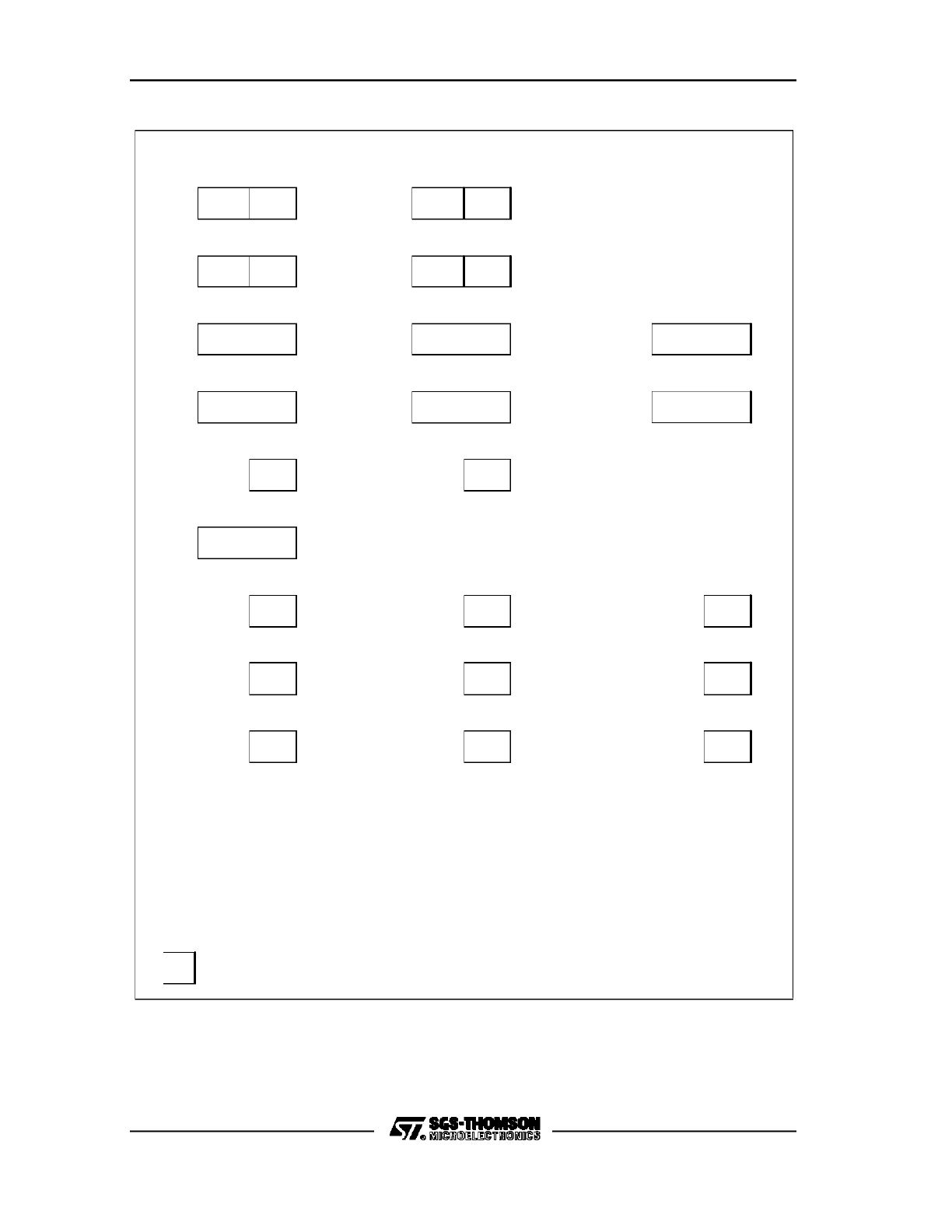

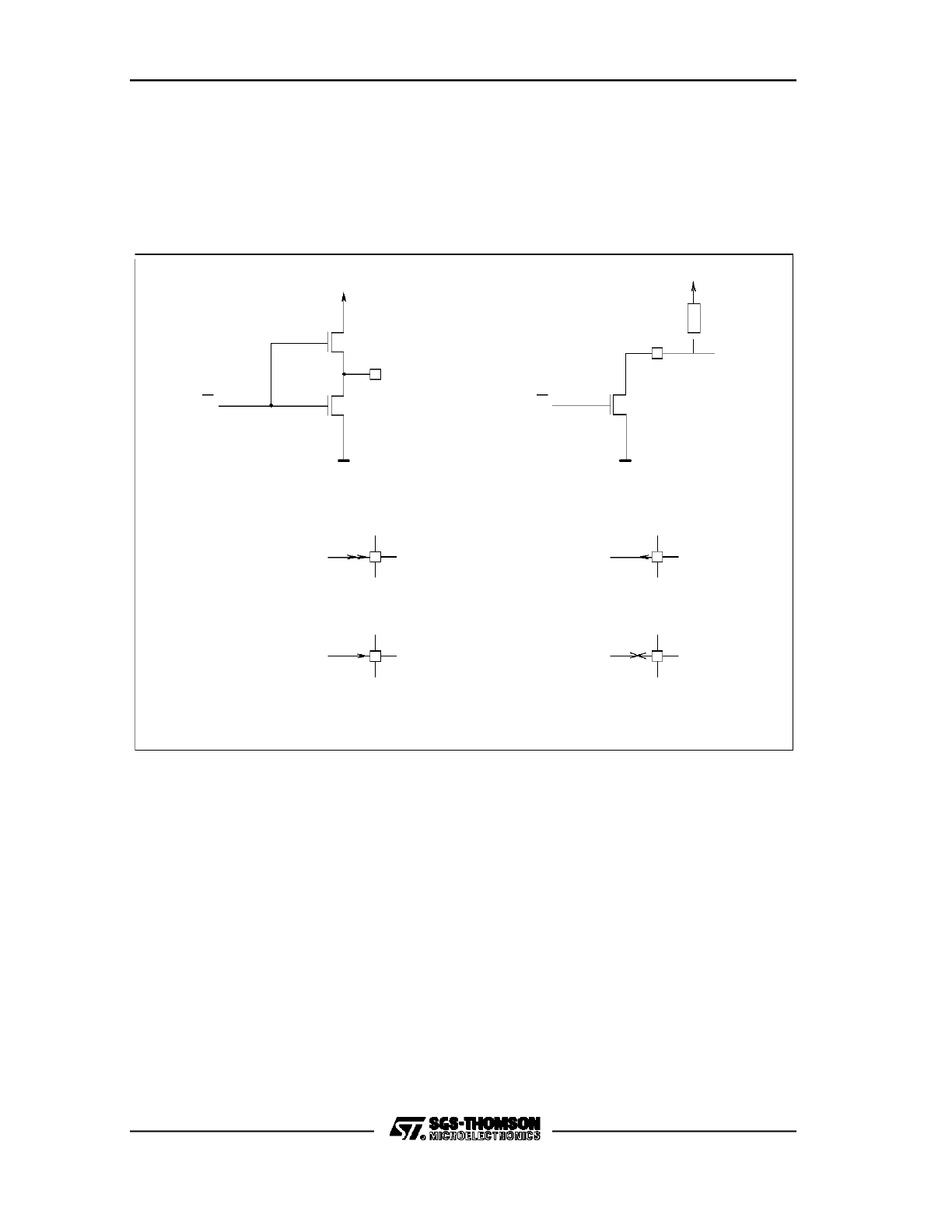

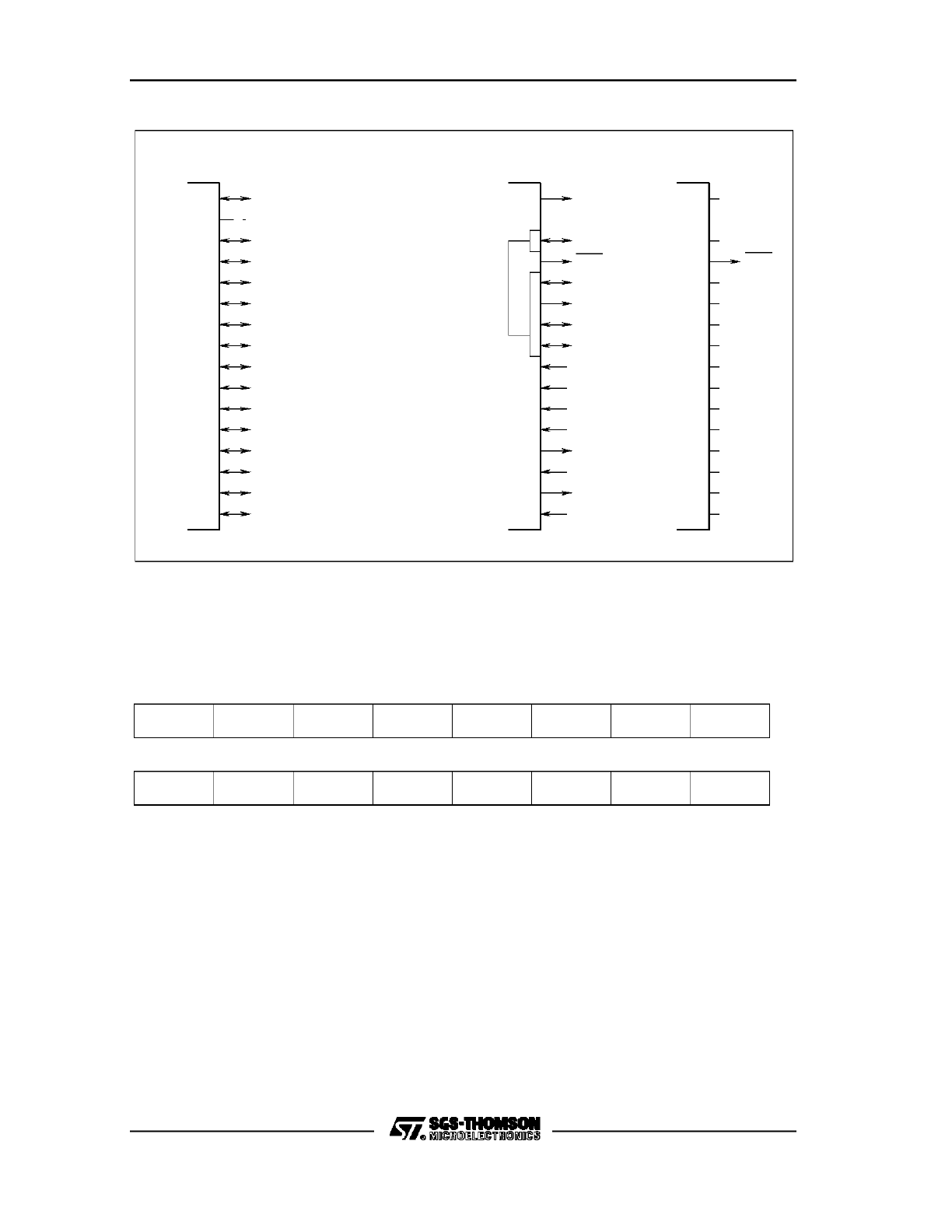

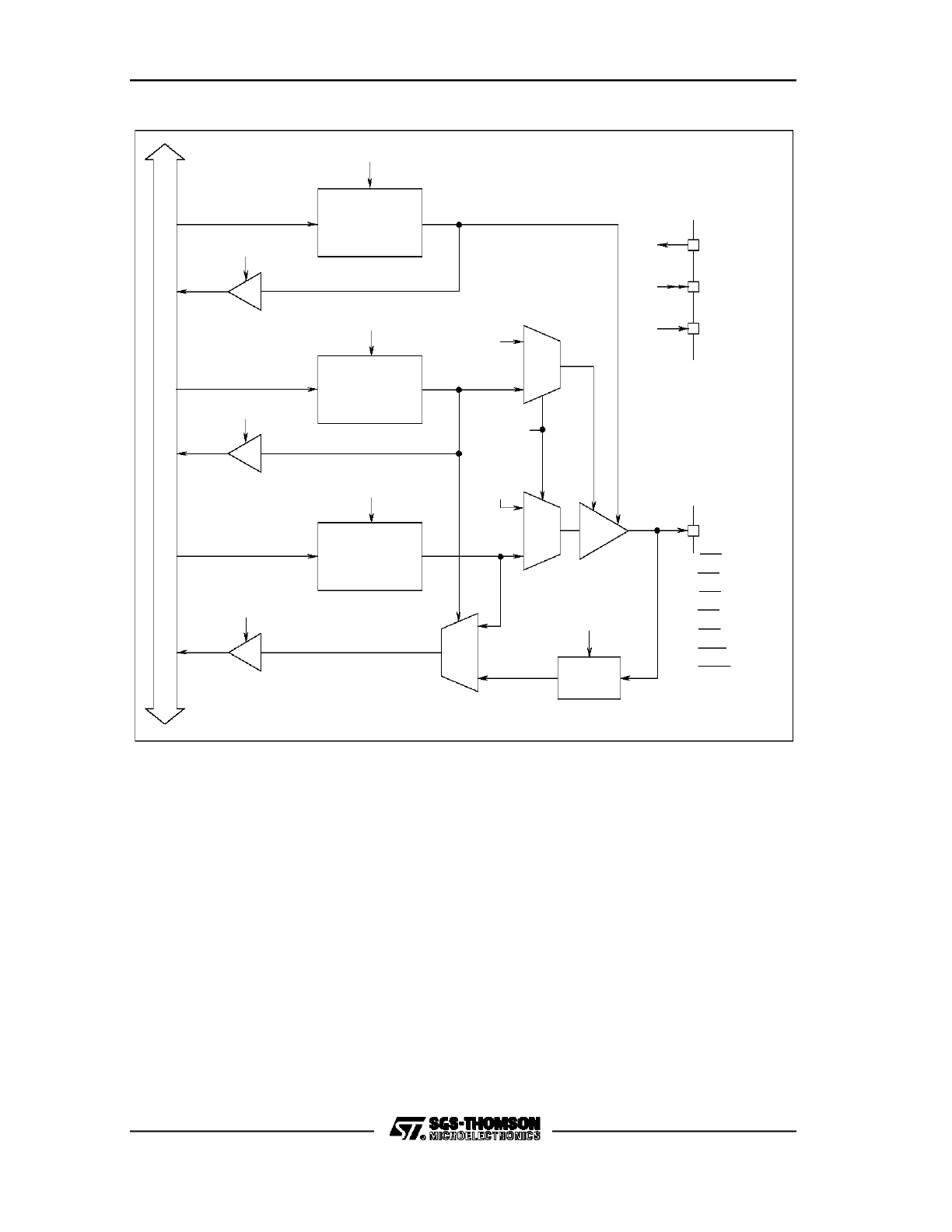

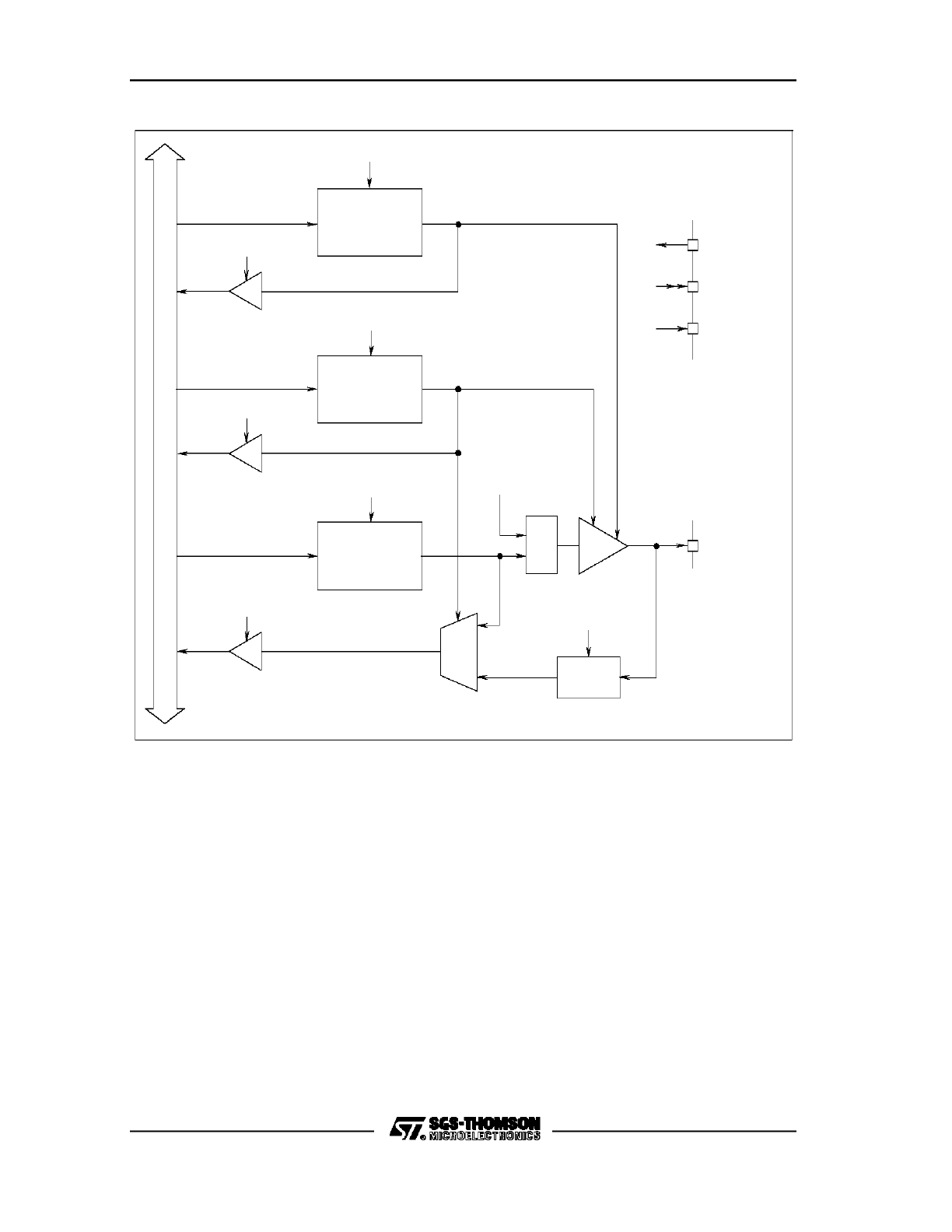

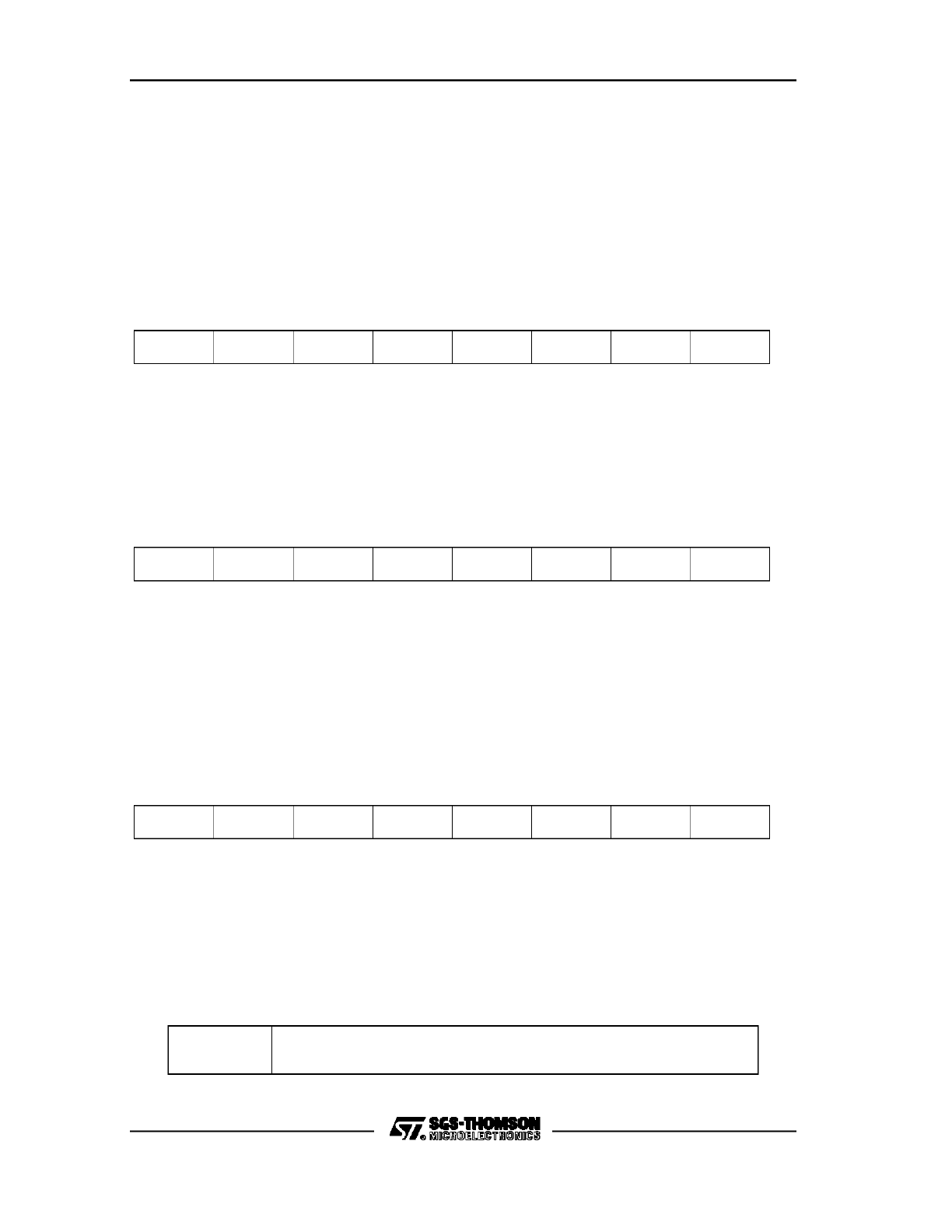

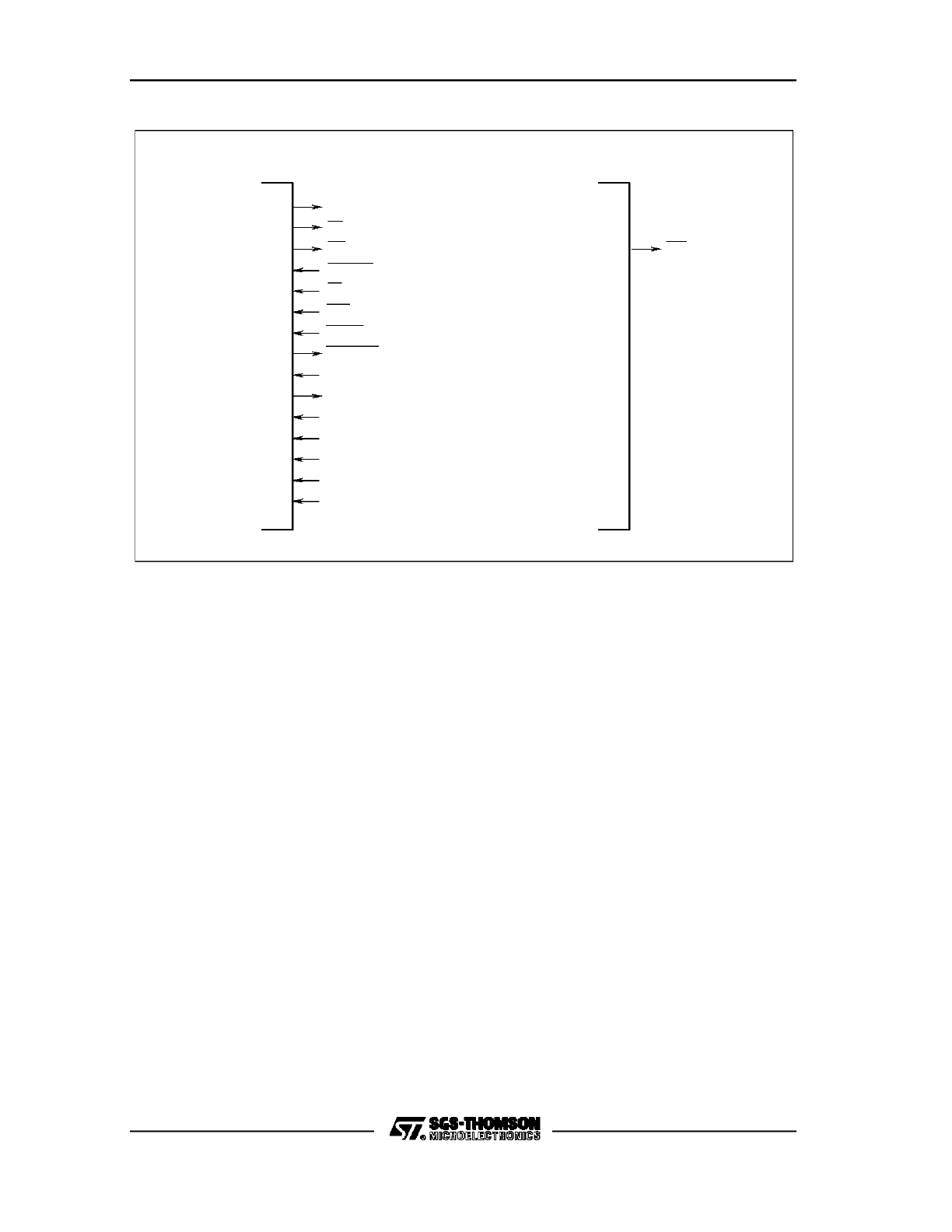

Figure 1. Block diagram of the major units of the ST10167

VR001925

CPU

CORE

RAM

ROM

OSC

Interrupt Controller

WDT

P0

P1

P8

P7

GPT2

GPT1

ADC

ASC

SSC

PWM

PEC

BUS

CTL

CAPCOM2

CAPCOM1

P4

P6

P2

P3

P5

C167 FAMILY PRELIMINARY USER MANUAL

7/180

1. INSTRUCTION SET

The instruction set of the C167 is enhanced by a number of instructions, which can

greatly reduce the code size generated by C-Compilers, and which enable the user

to write uninterruptable instruction sequences in a very effective way. A further

instruction is used to support the Extended SFR space in the C167 (see Chapter

2.4). The new instructions are described below, the syntax and formats of these

instructions are detailled on the next pages.

1.1 Atomic Instruction

This instruction is intended to allow the user to write an uninterruptable sequence of

code. The execution of this instruction causes the interrupt system (standard

interrupts and PEC requests) and Class A Traps to be disabled for a specific

number of instructions, between 1 to 4 instructions. All instructions requiring multiple

cycles or hold states are regarded as one instruction in this sense (e.g. MUL is one

instruction). The atomic instruction is immediately active such that no NOPs are

required. Any instruction type can be used with this instruction.

Note that, while Class A Traps (NMI#, Stack Overflow/Underflow) are disabled during

the scope of the atomic instruction, the occurence of a Class B Trap (Illegal Opcode,

Illegal Bus Access, etc.) will interrupt the atomic sequence, since it indicates a

severe hardware problem.

The operation of the atomic instruction is the basis also for the Extend instructions.

Example:

ATOMIC #3

; scope is 3 instructions

; the following 3 instructions are uninterruptable

MOV

R0,#1234h

; instr. 1

MOV

R1,#5678h

; instr. 2

MUL

R0,R1

; instr. 3: MUL regarded as one instruction

MOV

R2,MDL

; this instruction is out of the scope of the atomic sequence

C167 FAMILY PRELIMINARY USER MANUAL

8/180

1.2

Extend Segment/Extend Page Instructions

These instructions allow the user to bypass the code segment and data page

scheme for a specific number of instructions (between 1 to 4). These instructions will

mainly be used by HLL-Compilers to access large data areas without the overhead of

data page pointer swapping. As with the atomic instruction, interrupts and Class A

Traps are disabled for up to 4 instructions after the extend instructions. Additional

instruction formats are implemented for a combination of the Extend Segment/Extend

Page instructions with the Extend Register instruction.

1.3

Extend Register Instructions

In the C167, due to the amount of Special Function Registers (SFRs) required to

control the on-chip peripherals, the SFR space is extended. This new Extended SFR

range, ESFR, can be accessed like any other memory location with a 16-bit address

(mem or [Rw]). However, when using short 8-bit addresses (REG or BITOFF), a

distinction has to be made between the normal and the extended SFR space (see

also Chapter 2.4). For this purpose, Extend Register instructions are implemented,

which allow access to the ESFR space with short 8-bit addresses for a specific

number of instructions (between 1 and 4). Again, interrupts and Class A Traps are

disabled during execution of this code sequence. Additional instruction formats are

implemented for a combination of the Extend Register instruction with the Extend

Segment/Extend Page instructions. Examples for these instructions can be found in

section 2.4.

C167 FAMILY PRELIMINARY USER MANUAL

9/180

Note:

Signal active low will be marked in the text with # and with

__

in the

figures.

C167 FAMILY PRELIMINARY USER MANUAL

10/180

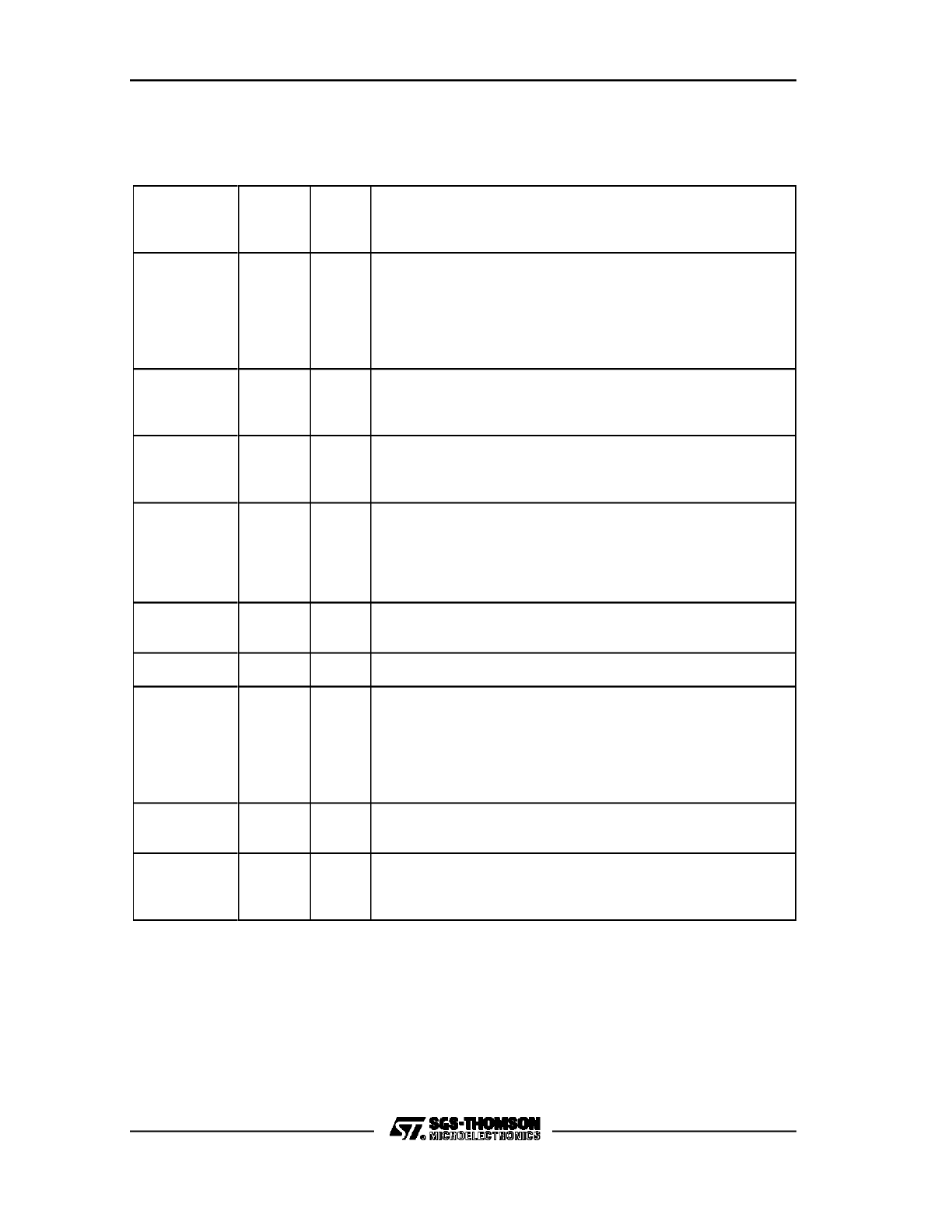

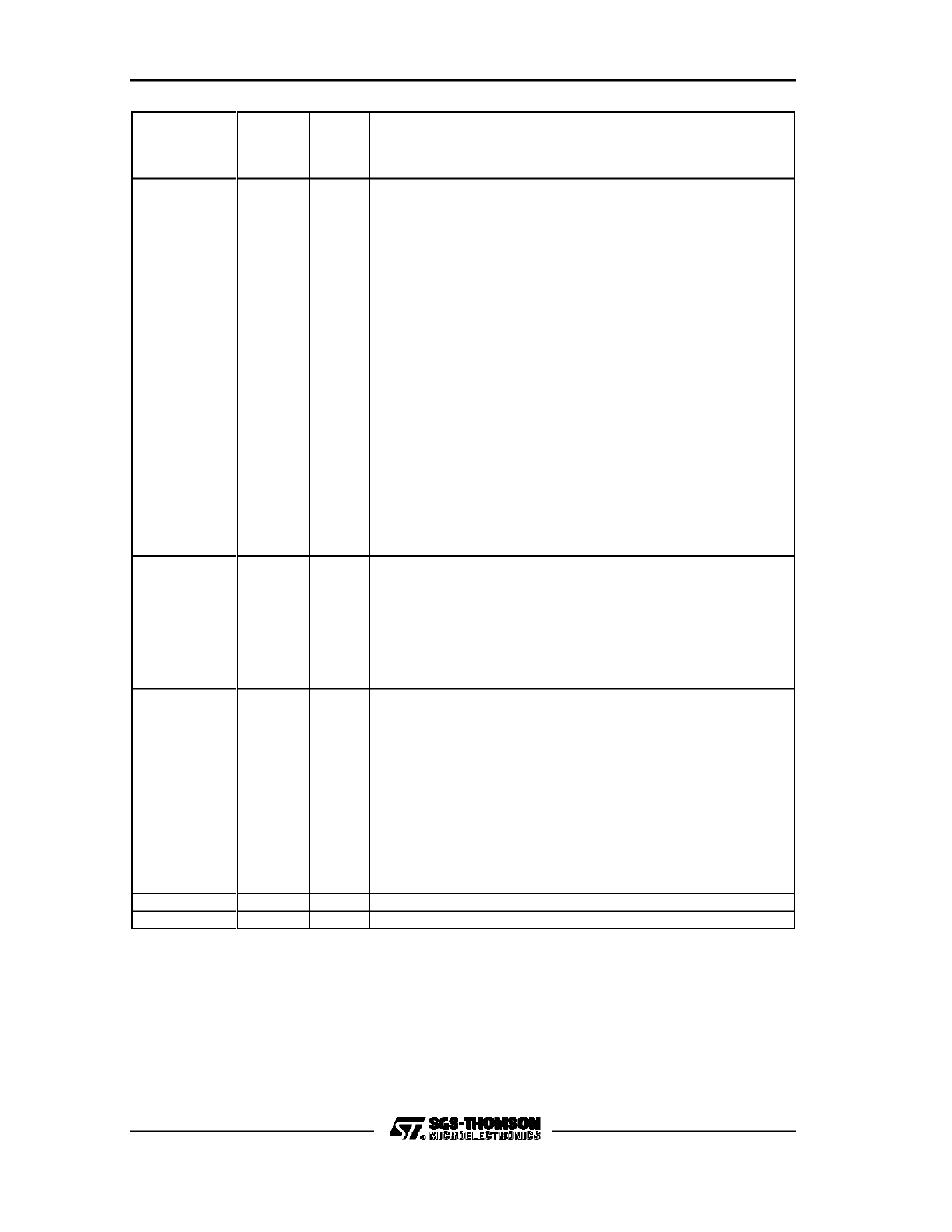

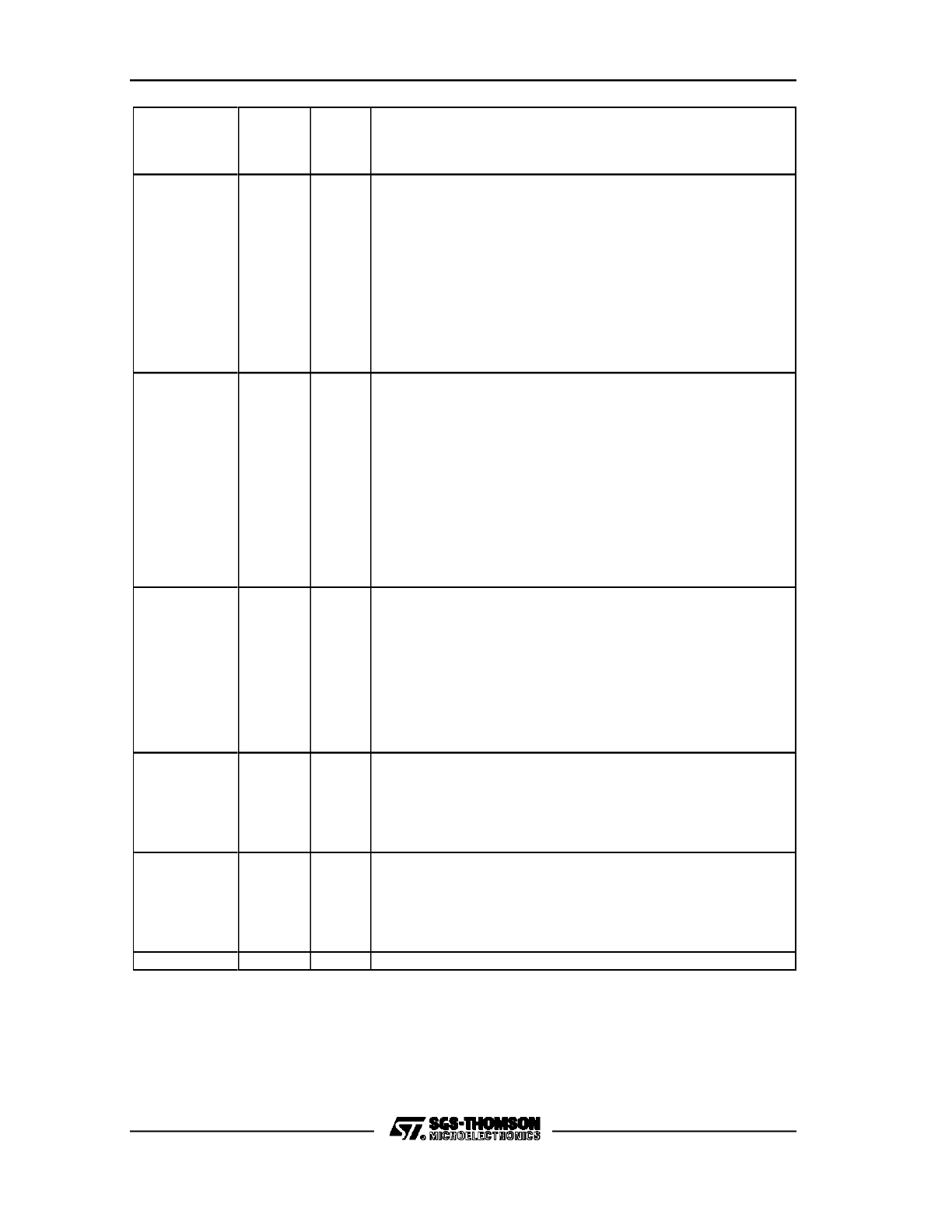

ATOMIC

begin ATOMIC sequence

ATOMIC

op1

OPERATION

(count) <= op1(1 <=

op1 <= 4)

Disable Interrupts and Class A Traps

DO WHILE (count != 0 AND Class B Trap Condition != TRUE)

next instruction

(count) <= (count) - 1

END WHILE

(count) = 0

Enable Interrupts and Traps

Causes standard and PEC interrupts and class A hardware

traps to be disabled for a specified number of instructions. The

ATOMIC instruction becomes immediately active such that no

additional NOPs are required.

Depending on the value of op1, the period of validity of the

ATOMIC sequence extends over the sequence of the next 1 to

4 instructions being executed after the ATOMIC instruction. All

instructions requiring multiple cycles or hold states to be

executed are regarded as one instruction in this sense. Any

instruction type can be used with the ATOMIC instruction.

NOTE: A lot of care must be taken over the use of the ATOMIC

instruction with other system control or branch instructions. One

must also be very careful when a class B trap condition

becomes present before the ATOMIC instruction sequence is

completed. In such a case, the ATOMIC instruction ceases its

validity, the interrupt locking is removed, and the class B trap is

executed. An ATOMIC instruction sequence can normally not

be continued properly if it was interrupted!

C167 FAMILY PRELIMINARY USER MANUAL

11/180

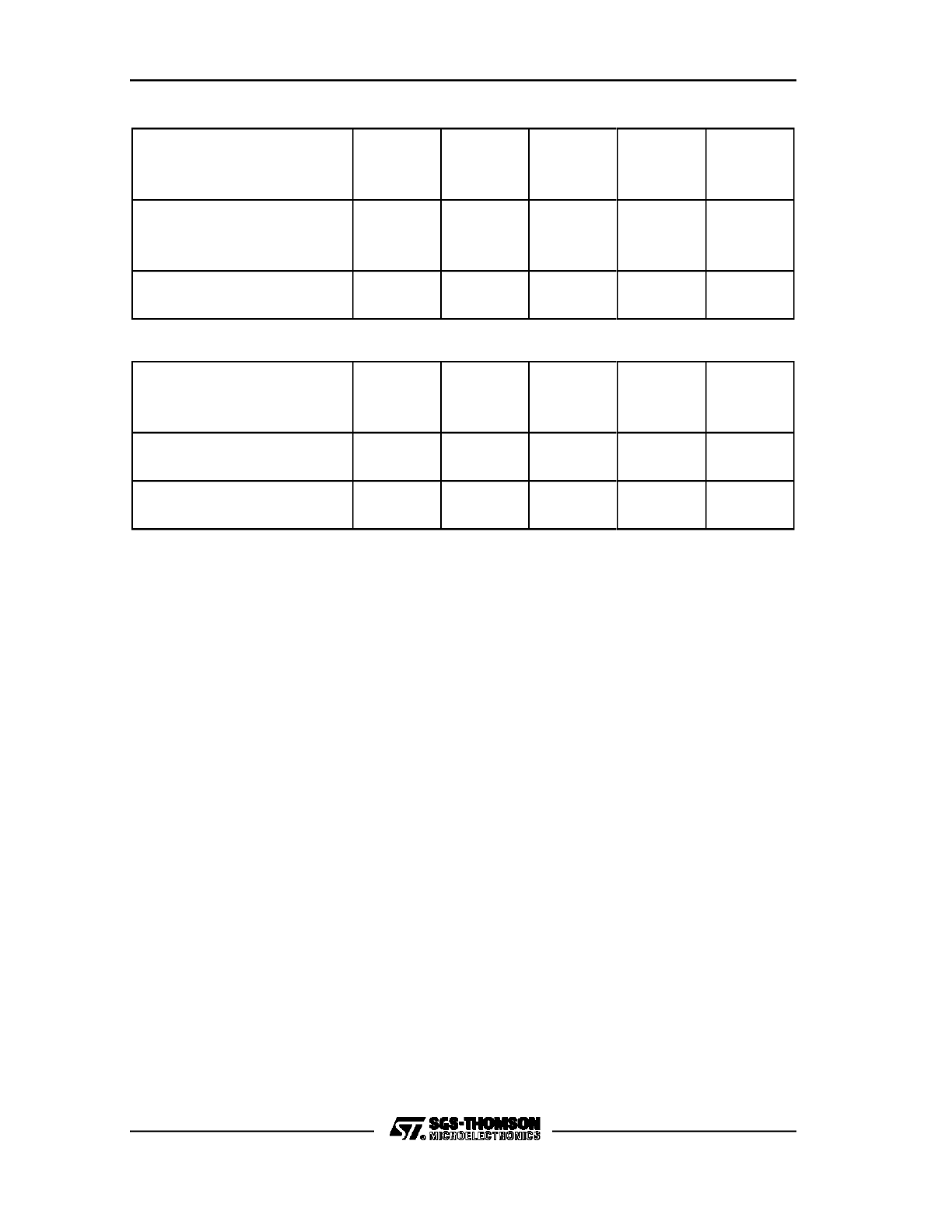

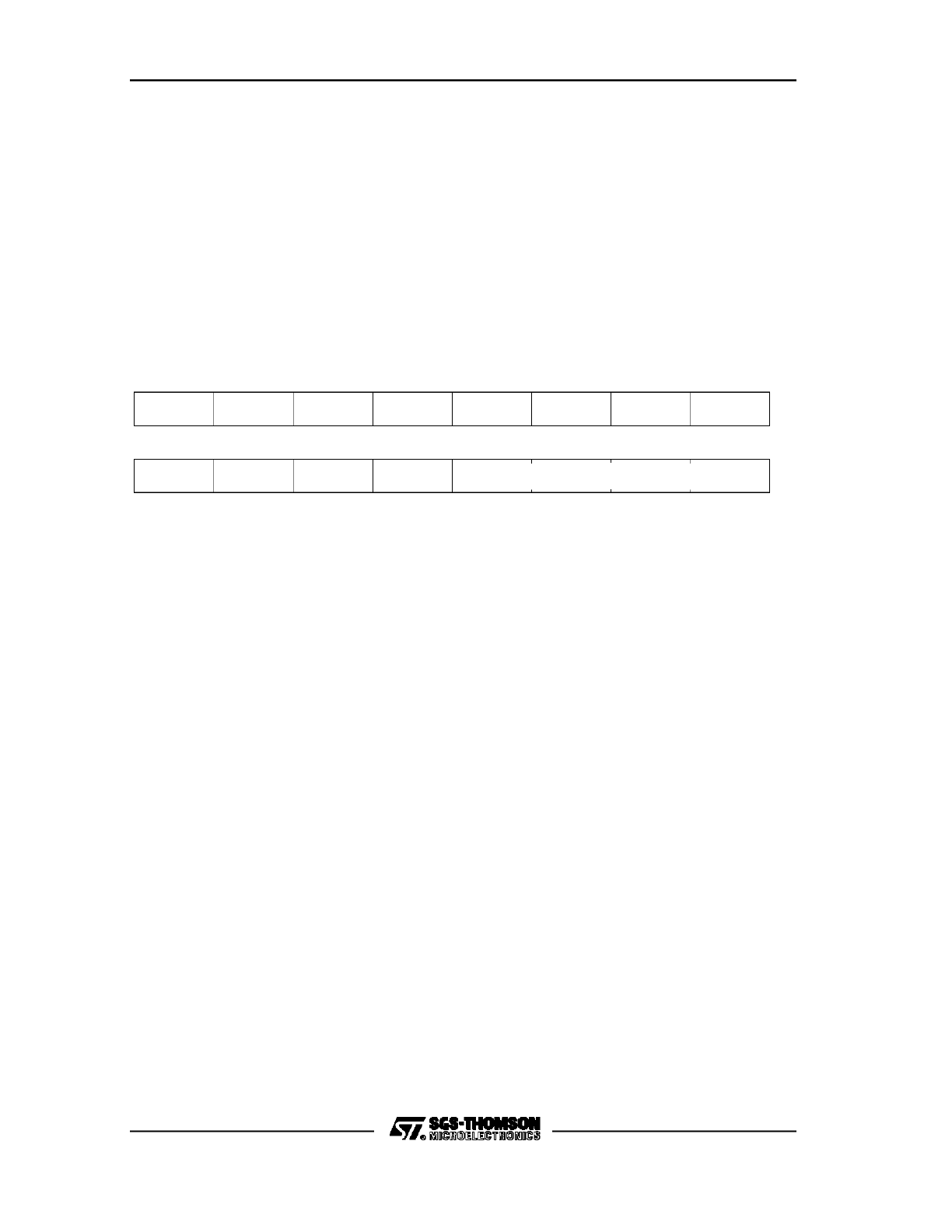

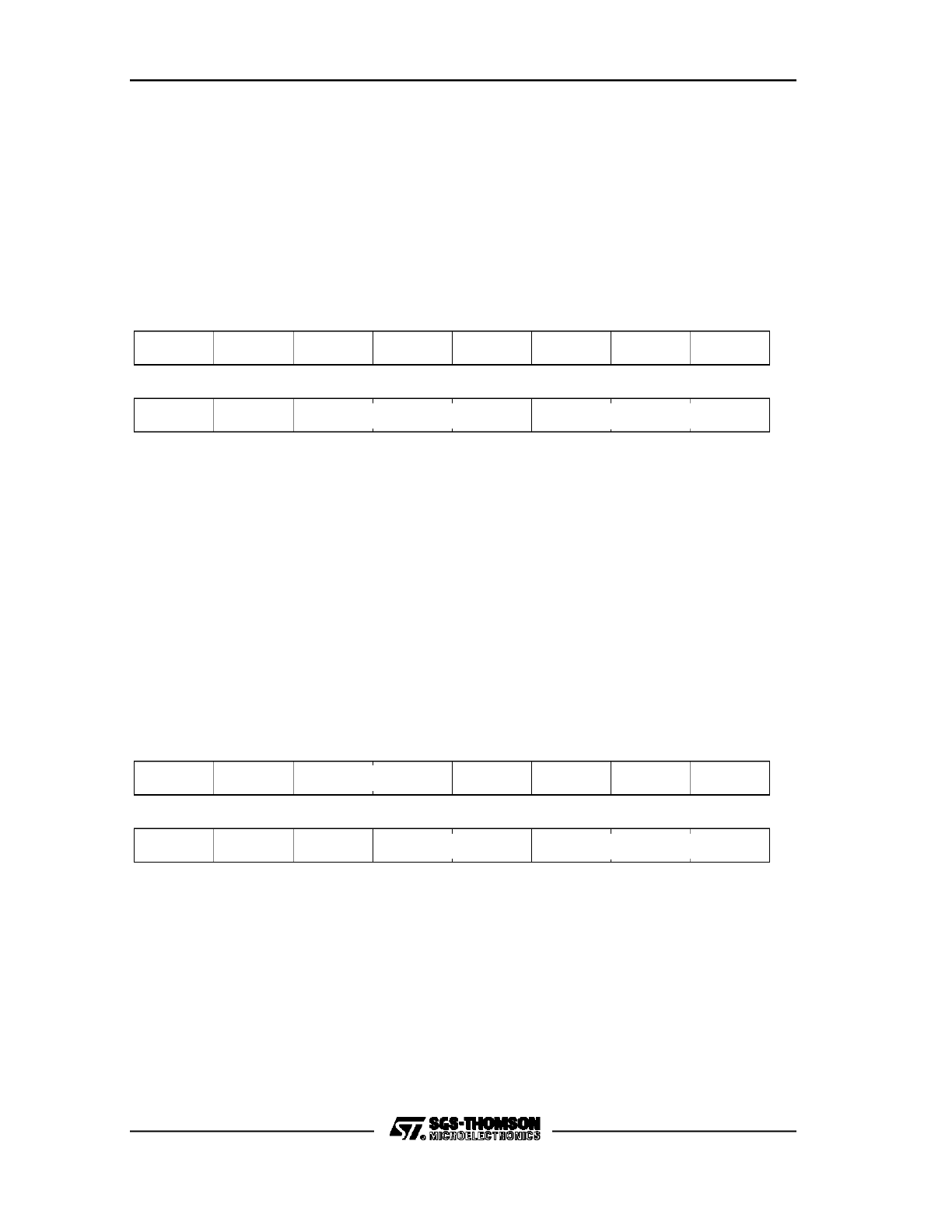

ATOMIC

begin ATOMIC sequence

FLAGS

E

Z

V

C

N

-

-

-

-

-

E

Not affected

Z

Not affected

V

Not affected

C

Not affected

N

Not affected

INSTRUCTION FORMAT

Mnemonic

Operands

Format

Bytes

ATOMIC

#data2

D1 :00##-0

2

C167 FAMILY PRELIMINARY USER MANUAL

12/180

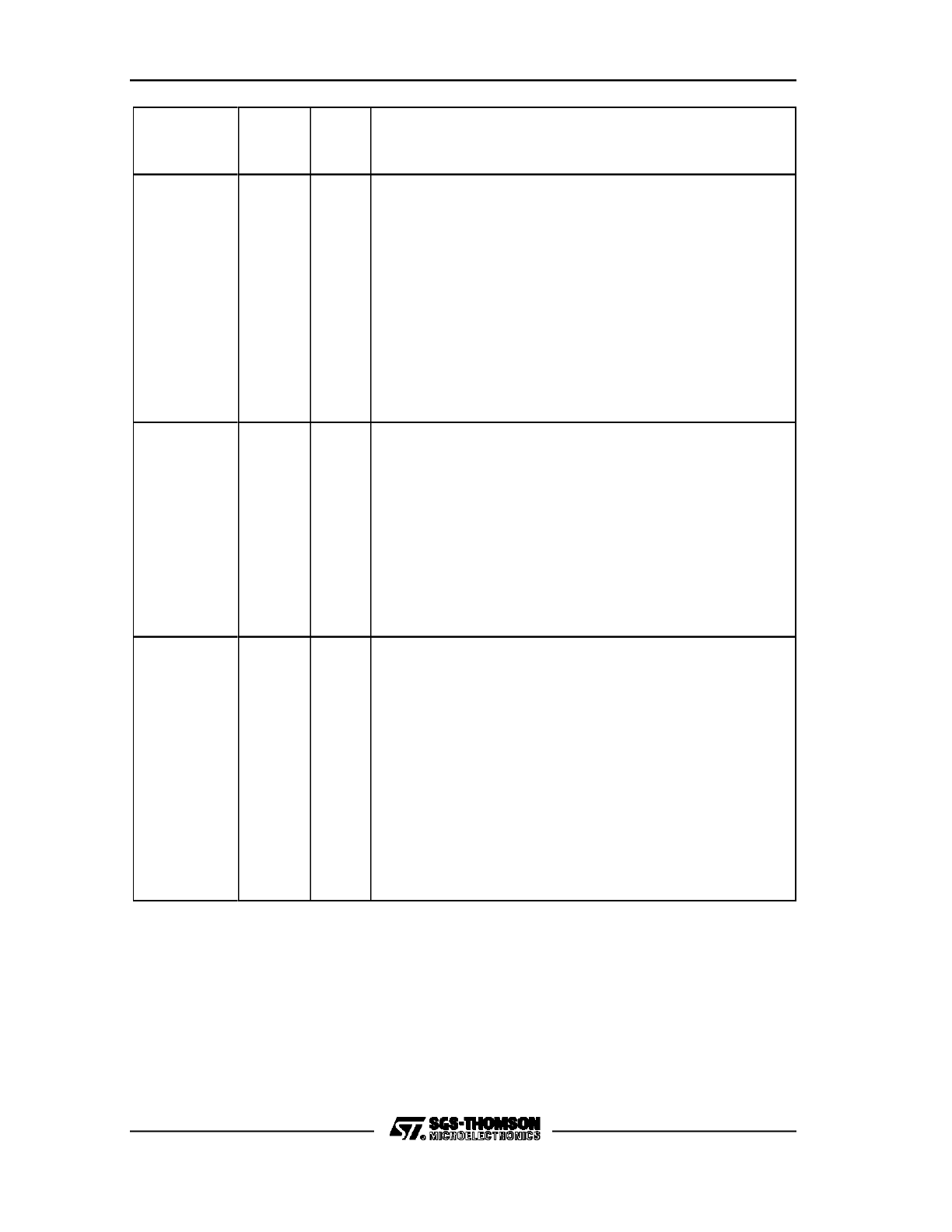

EXTR

begin EXTended Register sequence

EXTR

op1

OPERATION

(count) <= op1(1 <= op1 <= 4)

Disable Interrupts and Class A Traps

SFR range = Extended

DO WHILE (count != 0 AND Class B Trap Condition != TRUE)

next instruction

(count) <= (count) - 1

END WHILE

(count) = 0

SFR range = Standard

Enable Interrupts and Traps

Causes all SFR or SFR bit accesses via the ’reg’, ’bitoff’ or

’bitaddr’ addressing modes being made to the Extended SFR

space for a specified number of instructions. During their

execution, both standard and PEC interrupts and class A

hardware traps are locked. The EXTR instruction becomes

immediately active such that no additional NOPs are required.

Depending on the value of op1, the period of validity of the

EXTR instruction extends over the sequence of the next 1 to 4

instructions being executed after the EXTR instruction. All

instructions requiring multiple cycles or hold states to be

executed are regarded as one instruction in this sense. Any

instruction type can be used with the EXTR instruction.

NOTE: A lot of care must be taken over the use of the EXTR

instruction with other system control or branch instructions. One

must also be very careful when a class B trap condition

becomes present before the EXTR instruction sequence is

completed. In such a case, the EXTR instruction ceases its

validity, the interrupt locking is removed, and the class B trap is

executed. An EXTR instruction sequence can normally not be

continued properly if it was interrupted!

C167 FAMILY PRELIMINARY USER MANUAL

13/180

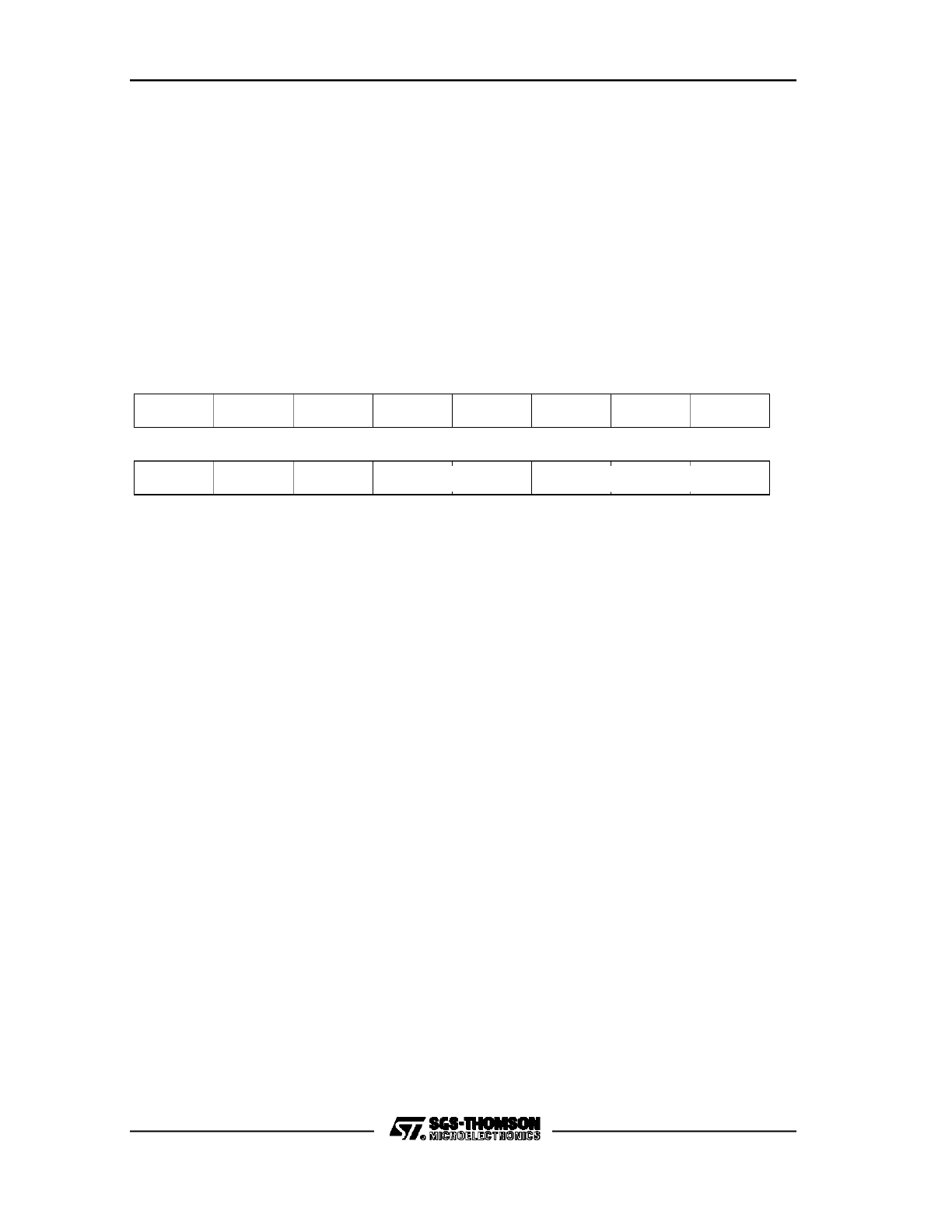

EXTR

begin EXTended Register sequence

FLAGS

E

Z

V

C

N

-

-

-

-

-

E

Not affected

Z

Not affected

V

Not affected

C

Not affected

N

Not affected

INSTRUCTION FORMAT

Mnemonic

Operands

Format

Bytes

EXTR

#data2

D1 :10##-0

2

C167 FAMILY PRELIMINARY USER MANUAL

14/180

EXTP

begin EXTended Page sequence

EXTP

op1, op2

OPERATION

(count) <= op2(1 <= op2 <= 4)

Disable Interrupts and Class A Traps

Data Page = (op1)

DO WHILE (count != 0 AND Class B Trap Condition != TRUE)

next instruction

(count) <= (count) - 1

END WHILE

(count) = 0

Data Page = (DPPx)

Enable Interrupts and Traps

Overrides the standard DPP addressing scheme of the long

and indirect addressing modes for a specified number of

instructions. During their execution, both standard and PEC

interrupts and class A hardware traps are locked. The EXTP

instruction becomes immediately active such that no additional

NOPs are required.

For any long (’mem’) or indirect ([...]) address in the EXTP

instruction sequence, the 10-bit page number (address bits

A

23

-A

14

) is not determined by the contents of a DPP register

but by the value of op1 itself. The 14-bit page offset (address

bits A

13

-A

0

) is derived from the long or indirect address as

usual.

Depending on the value of op2, the period of validity of the

EXTP instruction extends over the sequence of the next 1 to 4

instructions being executed after the EXTP instruction. All

instructions requiring multiple cycles or hold states to be

executed are regarded as one instruction in this sense. Any

instruction type can be used with the EXTP instruction.

C167 FAMILY PRELIMINARY USER MANUAL

15/180

EXTP

begin EXTended Page sequence

NOTE: A lot of care must be taken over the use of the EXTP

instruction with other system control or branch instructions. One

must also be very careful when a class B trap condition

becomes present before the EXTP instruction sequence is

completed. In such a case, the EXTP instruction ceases its

validity, the interrupt locking is removed, and the class B trap is

executed. An EXTP instruction sequence can normally not be

continued properly if it was interrupted!

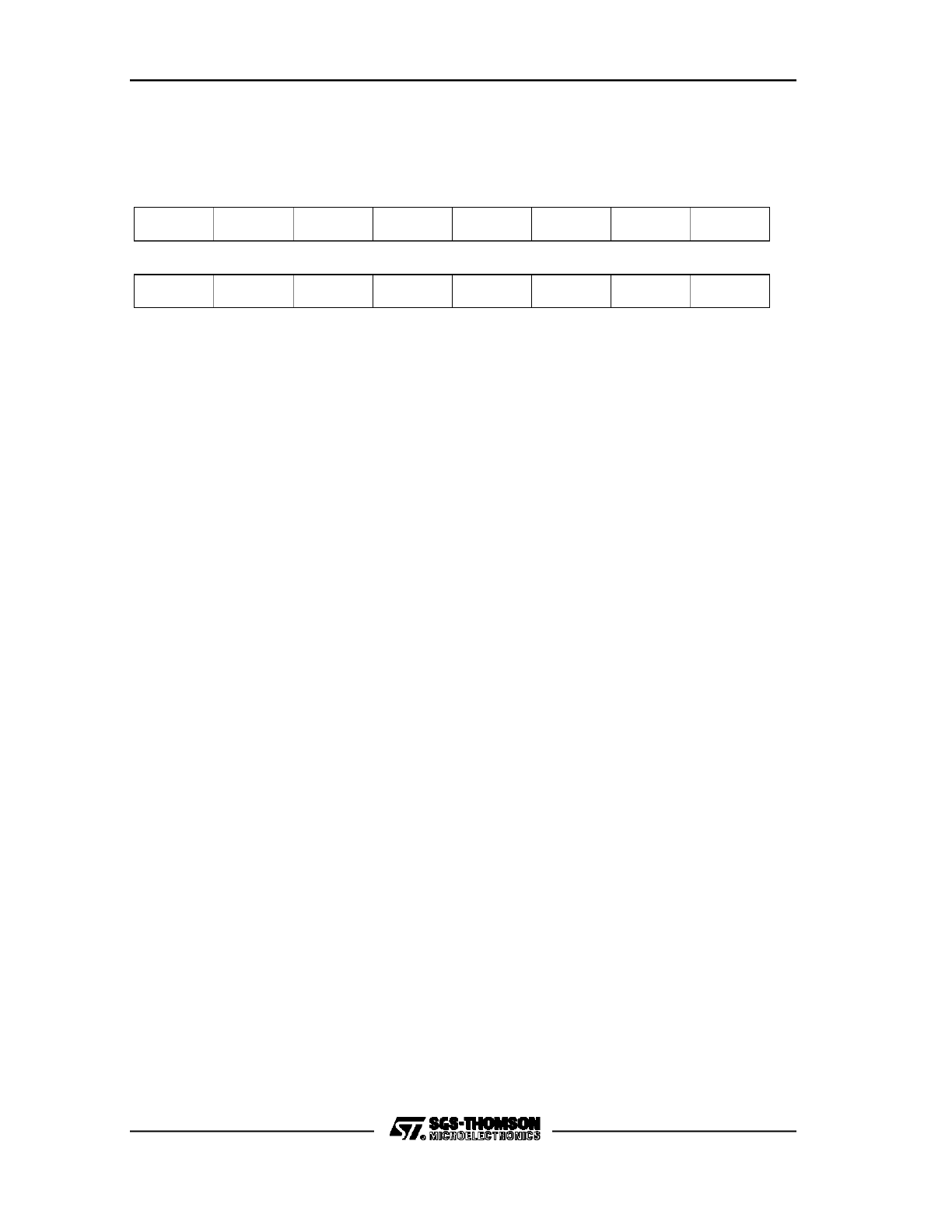

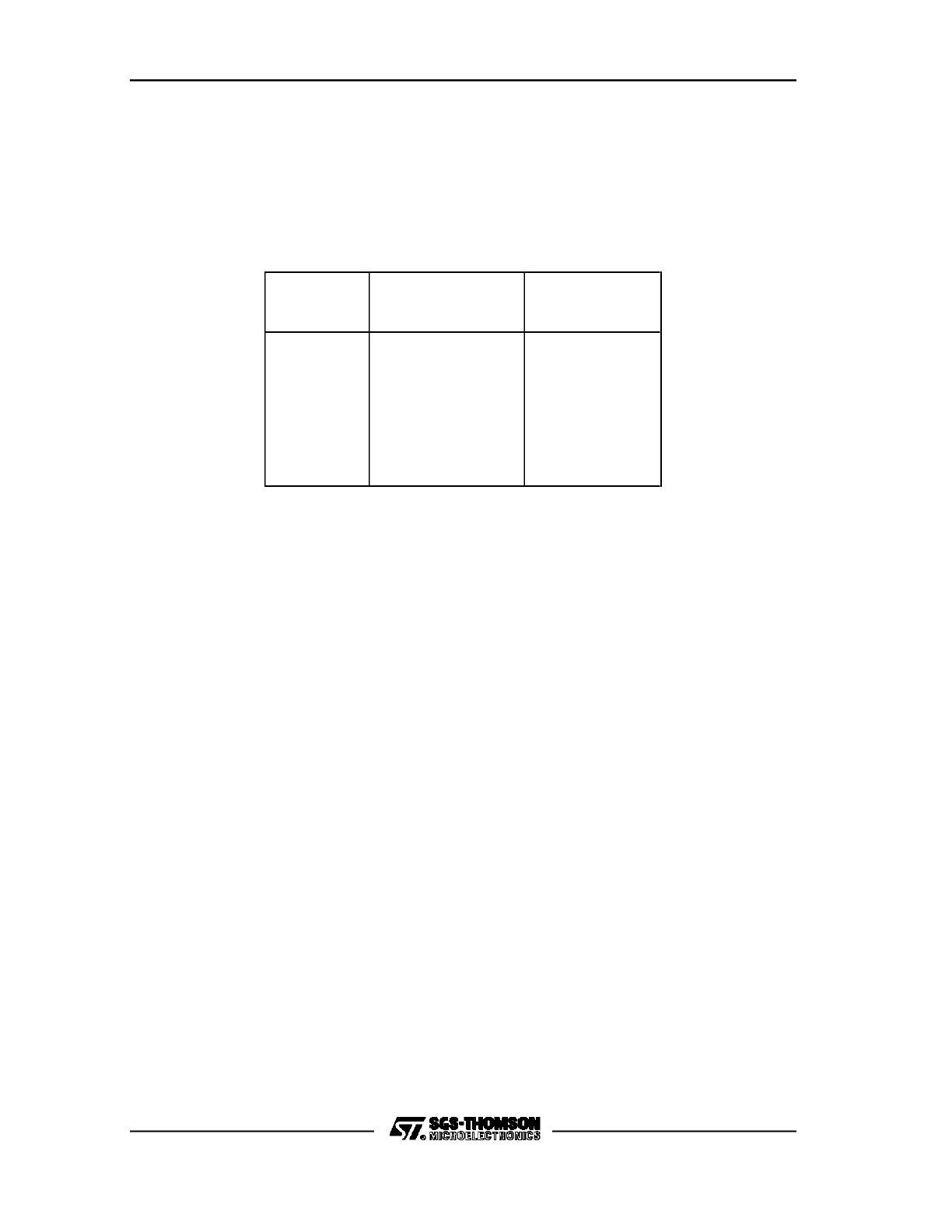

FLAGS

E

Z

V

C

N

-

-

-

-

-

E

Not affected

Z

Not affected

V

Not affected

C

Not affected

N

Not affected

INSTRUCTION FORMAT

Mnemonic

Operands

Format

Bytes

EXTP

Rwm, #data2

DC :01##-m

2

EXTP

#pag,#data2

D7 :01##-0 pp 0:00pp

4

C167 FAMILY PRELIMINARY USER MANUAL

16/180

EXTPR

begin EXTended Page and Register sequence

EXTPR

op1, op2

OPERATION

(count) <= op2(1 <= op2 <= 4)

Disable Interrupts and Class A Traps

Data Page = (op1) AND SFR range = Extended

DO WHILE (count != 0 AND Class B Trap Condition != TRUE)

next instruction

(count) <= (count) - 1

END WHILE

(count) = 0

Data Page = (DPPx) AND SFR range = Standard

Enable Interrupts and Traps

Overrides the standard DPP addressing scheme of the long

and indirect addressing modes and causes all SFR or SFR bit

accesses via the ’reg’, ’bitoff’ or ’bitaddr’ addressing modes

being made to the Extended SFR space for a specified number

of instructions. During their execution, both standard and PEC

interrupts and class A hardware traps are locked. The EXTPR

instruction becomes immediately active such that no additional

NOPs are required.

For any long (’mem’) or indirect ([...]) address in the EXTPR

instruction sequence, the 10-bit page number (address bits

A

23

-A

14

) is not determined by the contents of a DPP register

but by the value of op1 itself. The 14-bit page offset (address

bits A

13

-A

0

) is derived from the long or indirect address as

usual.

Depending on the value of op2, the period of validity of the

EXTPR instruction extends over the sequence of the next 1 to 4

instructions being executed after the EXTPR instruction. All

instructions requiring multiple cycles or hold states to be

executed are regarded as one instruction in this sense. Any

instruction type can be used with the EXTPR instruction.

C167 FAMILY PRELIMINARY USER MANUAL

17/180

EXTPR

begin EXTended Page and Register sequence

NOTE: A lot of care must be taken over the use of the EXTPR

instruction with other system control or branch instructions. One

must also be very careful when a class B trap condition

becomes present before the EXTPR instruction sequence is

completed. In such a case, the EXTPR instruction ceases its

validity, the interrupt locking is removed, and the class B trap is

executed. An EXTPR instruction sequence can normally not be

continued properly if it was interrupted!

FLAGS

E

Z

V

C

N

-

-

-

-

-

E

Not affected

Z

Not affected

V

Not affected

C

Not affected

N

Not affected

INSTRUCTION FORMAT

Mnemonic

Operands

Format

Bytes

EXTPR

Rwm, #data2

DC :11##-m

2

EXTPR

#pag,#data2

D7 :11##-0 pp 0:00pp

4

C167 FAMILY PRELIMINARY USER MANUAL

18/180

EXTS

begin EXTended Segment sequence

EXTS

op1, op2

OPERATION

(count) <= op2(1 <= op2 <= 4)

Disable Interrupts and Class A Traps

Data Segment = (op1)

DO WHILE (count != 0 AND Class B Trap Condition != TRUE)

next instruction

(count) <= (count) - 1

END WHILE

(count) = 0

Data Page= (DPPx)

Enable Interrupts and Traps

Overrides the standard DPP addressing scheme of the long

and indirect addressing modes for a specified number of

instructions. During their execution, both standard and PEC

interrupts and class A hardware traps are locked. The EXTS

instruction becomes immediately active such that no additional

NOPs are required.

For any long (’mem’) or indirect ([...]) address in an EXTS

instruction sequence, the value of op1 determines the 8-bit

segment (address bits A

23

-A

16

) valid for the corresponding

data access. The long or indirect address itself represents the

16-bit segment offset (address bits A

15

-A

0

).

Depending on the value of op2, the period of validity of the

EXTS instruction extends over the sequence of the next 1 to 4

instructions being executed after the EXTS instruction. All

instructions requiring multiple cycles or hold states to be

executed are regarded as one instruction in this sense. Any

instruction type can be used with the EXTS instruction.

C167 FAMILY PRELIMINARY USER MANUAL

19/180

EXTS

begin EXTended Segment sequence

NOTE: A lot of care must be taken over the use of the EXTS

instruction with other system control or branch instructions. One

must also be very careful when a class B trap condition

becomes present before the EXTS instruction sequence is

completed. In such a case, the EXTS instruction ceases its

validity, the interrupt locking is removed, and the class B trap is

executed. An EXTS instruction sequence can normally not be

continued properly if it was interrupted!

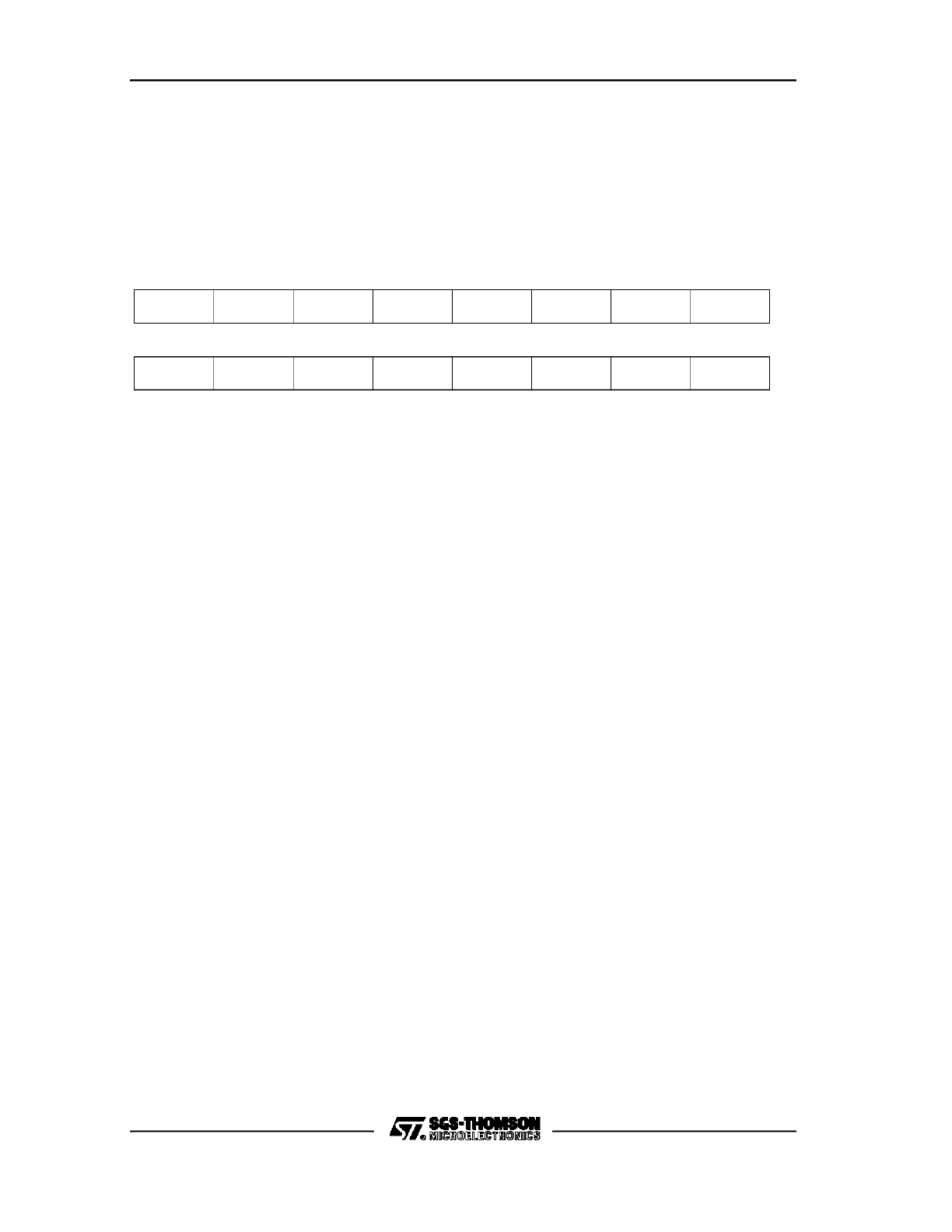

FLAGS

E

Z

V

C

N

-

-

-

-

-

E

Not affected

Z

Not affected

V

Not affected

C

Not affected

N

Not affected

INSTRUCTION FORMAT

Mnemonic

Operands

Format

Bytes

EXTS

Rwm, #data2

DC :00##-m

2

EXTS

#seg,#data2

D7 :00##-0 ss 00

4

C167 FAMILY PRELIMINARY USER MANUAL

20/180

EXTSR

begin EXTended Segment and Register sequence

EXTSR

op1, op2

OPERATION

(count) <= op1(1 <= op2 <= 4)

Disable Interrupts and Class A Traps

Data Segment = (op1) AND SFR range = Extended

DO WHILE (count

!=

0 AND Class B Trap Condition != TRUE)

next instruction

(count) <= (count) - 1

END WHILE

(count) = 0

Data Page= (DPPx) AND SFR range = Standard

Enable Interrupts and Traps

Overrides the standard DPP addressing scheme of the long

and indirect addressing modes and causes all SFR or SFR bit

accesses via the ’reg’, ’bitoff’ or ’bitaddr’ addressing modes

being made to the Extended SFR space for a specified number

of instructions. During their execution, both standard and PEC

interrupts and class A hardware traps are locked. The EXTSR

instruction becomes immediately active such that no additional

NOPs are required.

For any long (’mem’) or indirect ([...]) address in the EXTSR

instruction sequence, the value of op1 determines the 8-bit

segment (address bits A

23

-A

16

) valid for the corresponding

data access. The long or indirect address itself represents the

16-bit segment offset (address bits A

15

-A

0

).

Depending on the value of op2, the period of validity of the

EXTSR instruction extends over the sequence of the next 1 to 4

instructions being executed after the EXTSR instruction. All

instructions requiring multiple cycles or hold states to be

executed are regarded as one instruction in this sense. Any

instruction type can be used with the EXTSR instruction.

C167 FAMILY PRELIMINARY USER MANUAL

21/180

EXTSR

begin EXTended Segment and Register sequence

NOTE: A lot of care must be taken over the use of the EXTSR

instruction with other system control or branch instructions. One

must also be very careful when a class B trap condition

becomes present before the EXTSR instruction sequence is

completed. In such a case, the EXTSR instruction ceases its

validity, the interrupt locking is removed, and the class B trap is

executed. An EXTSR instruction sequence can normally not be

continued properly if it was interrupted!

FLAGS

E

Z

V

C

N

-

-

-

-

-

E

Not affected

Z

Not affected

V

Not affected

C

Not affected

N

Not affected

INSTRUCTION FORMAT

Mnemonic

Operands

Format

Bytes

EXTSR

Rwm, #data2

DC :10##-m

2

EXTSR

#seg,#data2

D7 :10##-0 ss 00

4

C167 FAMILY PRELIMINARY USER MANUAL

22/180

C167 FAMILY PRELIMINARY USER MANUAL

23/180

2.

ON-CHIP MEMORY

2.1

On-Chip ROM

In this version of the ST10167, 8 KByte of internal ROM are implemented (depending

on market needs, future versions with different ROM sizes may follow). The ROM

can either be mapped to segment 0, addresses 000000 - 001FFFh, or to segment 1,

addresses 010000 - 011FFFh.

Although the ROM is 8 Kbyte in size, a full 32 KByte address range will be reserved

for it. When mapping the ROM to segment 0, the address range 000000h through

007FFFh will be mapped internally, that is, no external addresses will be generated

within this range. When mapping the ROM to segment 1, the address range 010000h

through 017FFFh will be reserved, and no external addresses are generated within

this range. In either case, the internal ROM is multiple mapped to this 32 KByte

range. Crossing the ROM boundary at n * 8K (n = 1..3) results to an access in the

respective address range 000000h - 007FFFh (010000h - 017FFFh in segment 1,

respectively). See also Chapter 2.5, Internal Address Space.

C167 FAMILY PRELIMINARY USER MANUAL

24/180

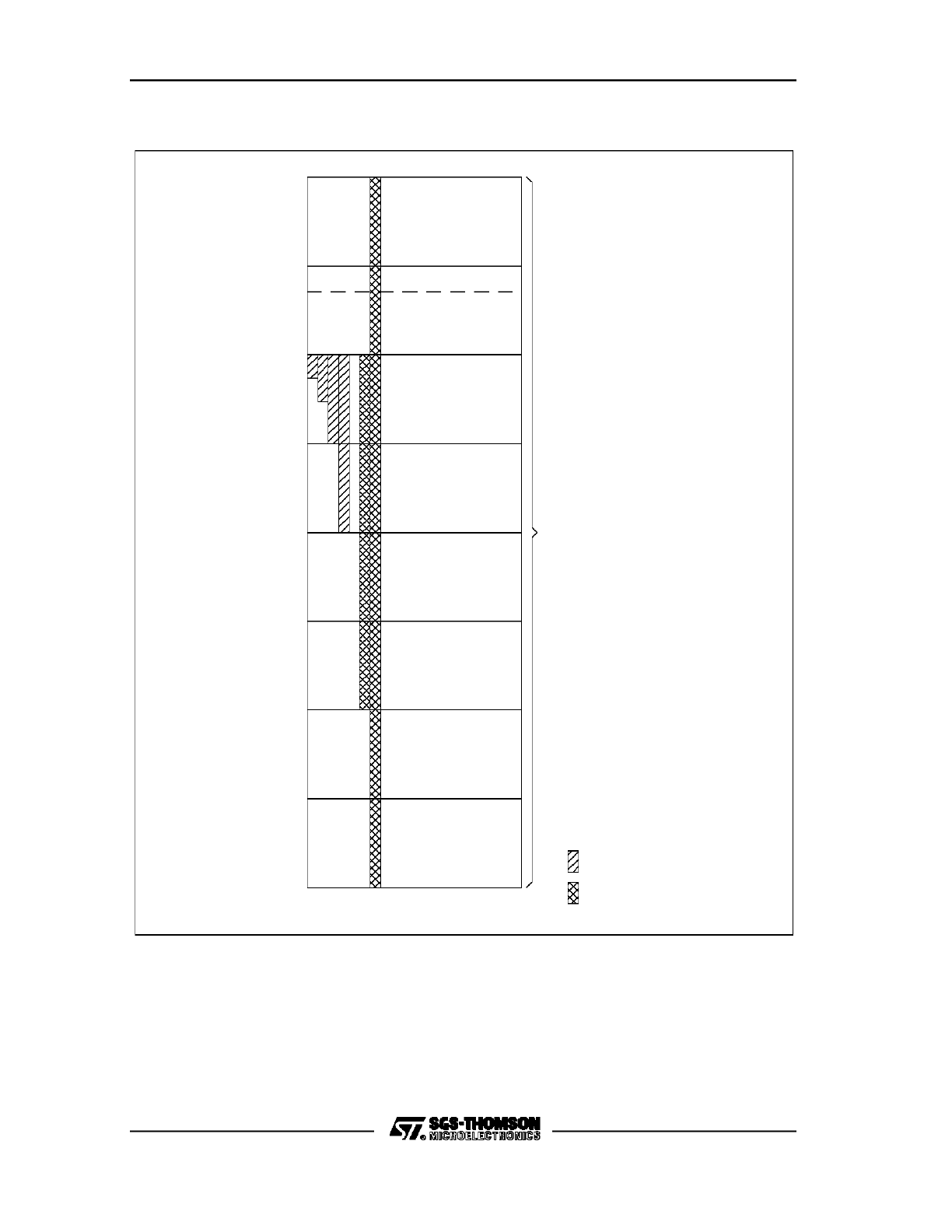

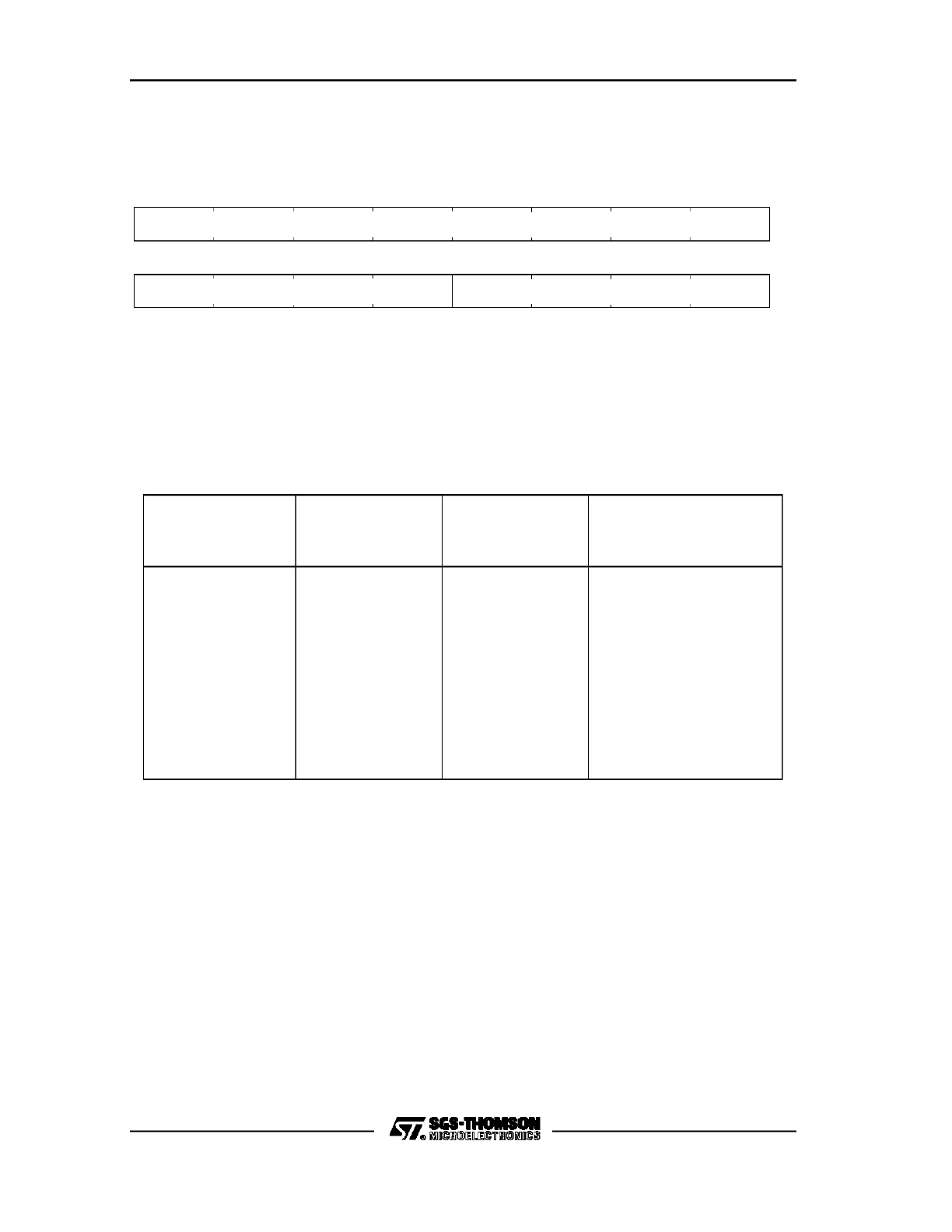

Figure 2. On-chip ROM Address Range, Mapping Option, and Expandability

Segment 0

03 0000

02 0000

01 7FFF

01 0000

00 7FFF

00 0000

Space

Address

Segment 2

Segment 1

Segment 0

Mapping

via ROM

VR001890

<32 KByte

or

Segment 1

<32 KByte

ROM

Expansion

>32 KByte

2.2

On-Chip RAM

The C167 incorporates a total of 2 KByte on-chip RAM, located in the address range

from 00F600h through 00FDFFh, shown in Figure 3. The stack size options are

extended accordingly, described in detail in section 3.3. The entire 2 KByte of internal

RAM can be used for variables, stack, and general purpose register banks.

C167 FAMILY PRELIMINARY USER MANUAL

25/180

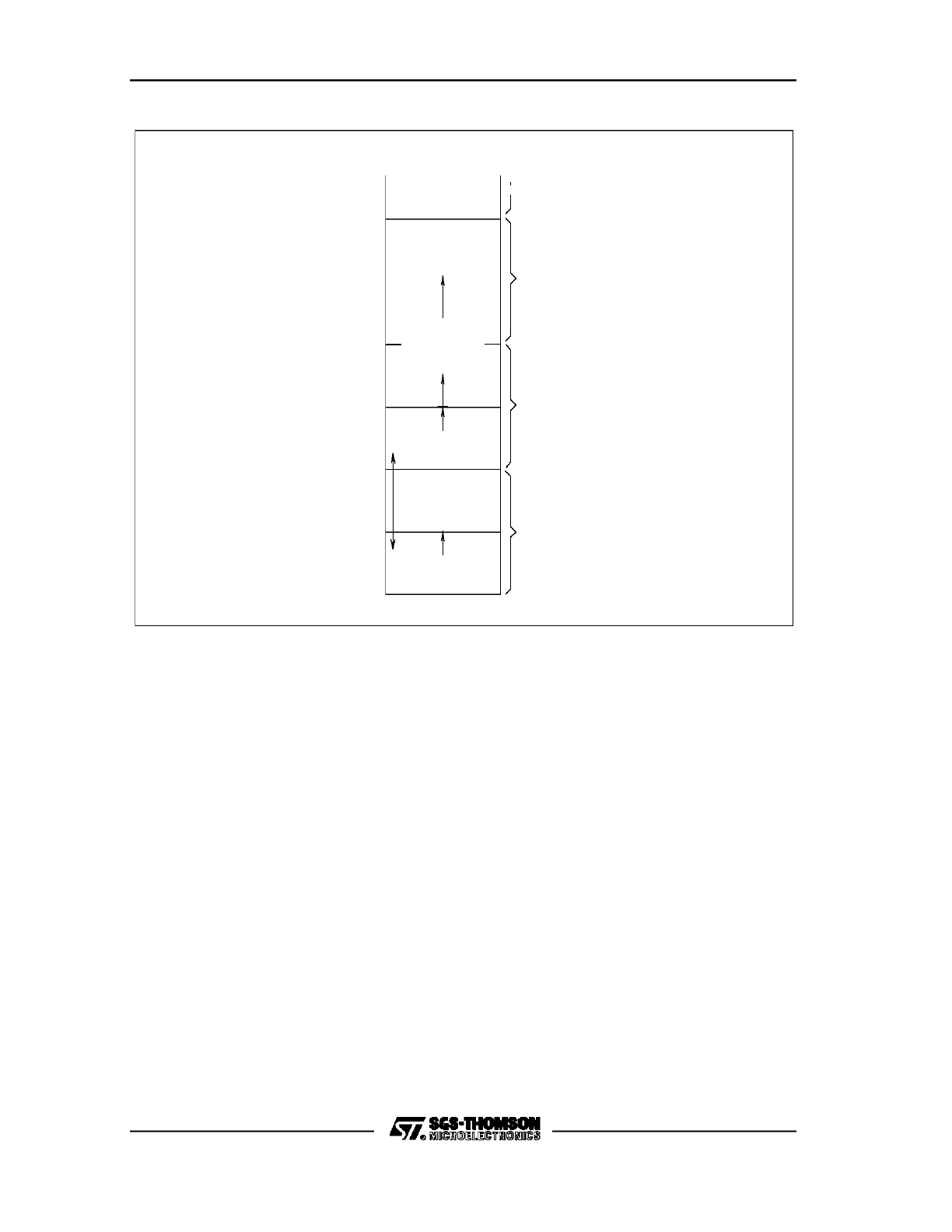

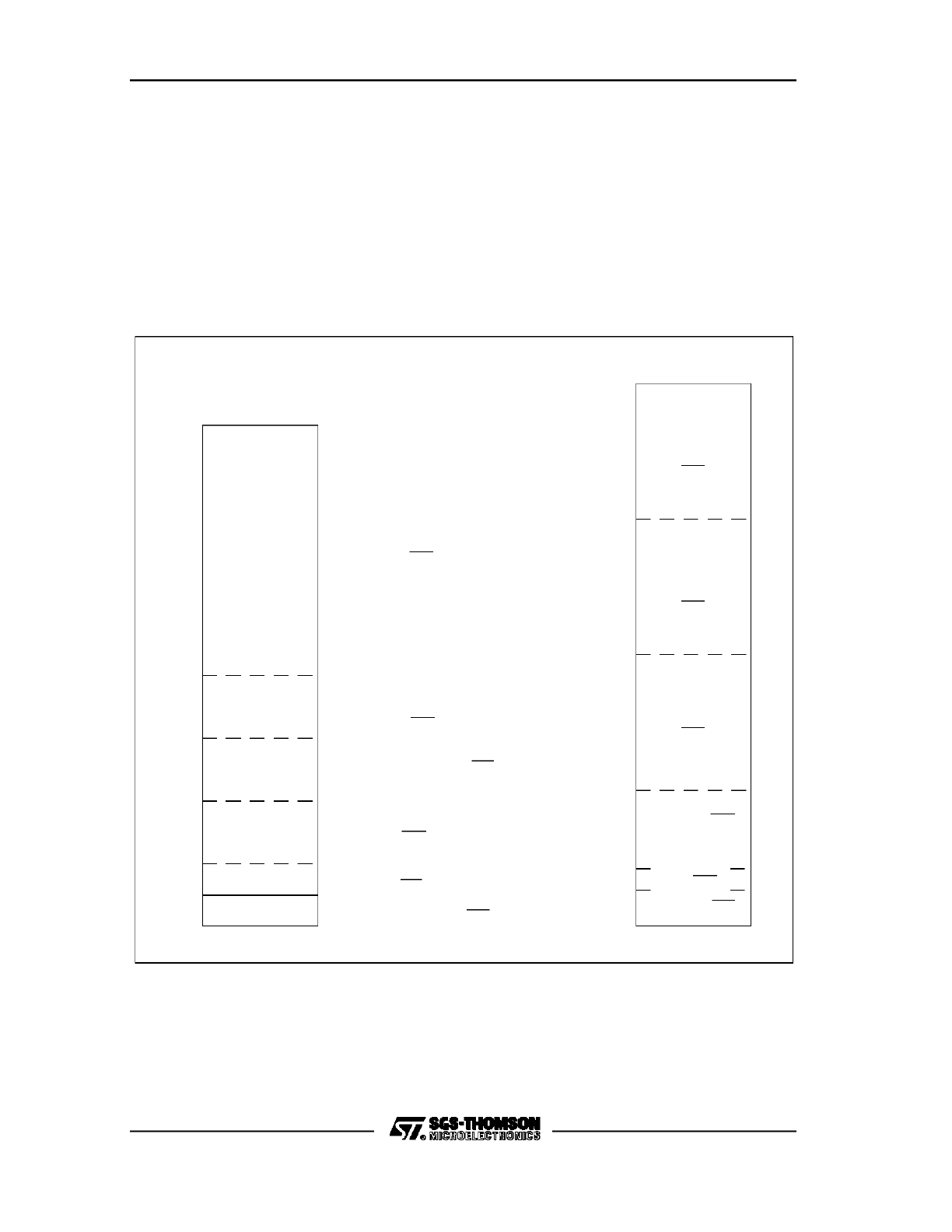

Figure 3. On-Chip RAM Address Map

00 F600h

00 F700h

VR001891

00 FDFFh

Bit-

Addressable

Space

PEC Pointers

00 FD00h

00 FC00h

00 FB00h

00 FA00h

00 F900h

00 F800h

2 KByte

Dual Port RAM

used for

Registerbanks

Data

Stack Code

Stack Size Options:

ST10x66 Options

Additional

C167 FAMILY PRELIMINARY USER MANUAL

26/180

2.3

PEC Pointer Address Space

The source and destination pointers for the PEC channels, which in the ST10x166

occupy the bitaddressable address range 0FDE0h through 0FDFFh, are remapped in

the C167 to the address range 0FCE0h through FCFFh, as illustrated in Figure 3.

This change enables the user to utilize all 2048 bits in the RAM without having to

sacrifice this valuable space when using the PEC channels.

Note:

This change is an incompatibility with the ST10x166 !

2.4

Extended Special Function Register Space (ESFR)

In the C167, due to the amount of registers required to control the additional on-chip

peripherals, the address range for the special function registers (SFRs) is extended.

This new Extended SFR range, ESFR, is located in the address range 00F000h

through 00F1FFh. It has the same size as the normal SFR range, and it is also split

into a bitaddressable and a non-bitaddressable section.

Due to the special addressing modes available for SFRs, some exceptions have to

be taken into account when accessing registers in the ESFR space. SFRs can be

addressed via a 16-bit direct (MEM) or indirect address ([Rw]), via a bit address

(BITOFF), or via a short 8-bit address (REG). Accessing SFRs via a 16-bit address

(MEM or [Rw]) is no problem since they are easily distinguished by that address. The

short addressing modes (REG or BITOFF), however, implicitly use the fixed base

address of the normal SFR range, and the addressing capability with 8 bits is totally

occupied by this range.

Thus, a method is implemented to allow the short address access (REG or BITOFF)

also for the new ESFR range. Instead of a windowing option, where either one or the

other of the SFR ranges would be available, this method allows both ranges to be

accessible at the same time.

For this purpose, an Extend Register EXTR (EXTPR, EXTSR) instruction is

implemented. This instruction is required before an access to a register in the ESFR

range is made with a short addressing mode (see also Chapter 1, Instruction Set).

The tools will provide options to insert this instruction automatically depending on the

addressing mode used. The following examples show accesses to the normal and

the extended SFR ranges:

C167 FAMILY PRELIMINARY USER MANUAL

27/180

Example 1:

Direct MEM access to an ESFR: No EXTR instruction required

MOV

R0, #const16

; GPRs are directly accessible in both ranges

MOV

ODP2, R0

; mem, reg addressing mode for the ESFR ODP2

Example 2:

Direct REG access to an ESFR: EXTR instruction required

EXTR

#4

; Extend Register for the following four instructions

MOV

ODP2, #data16

; reg, #data16 addressing mode

BFLDL

DP6, #mask, #data8

; bitoff addressing mode

BSET

DP1H.7

; bitaddr (= bitoff+bitnr) addressing mode

MOV

XP0IC, R1

; mem, reg addressing mode (XP0IC via mem, R1 via reg)

; GPRs are always accessible in both ranges

; ==> EXTR scope not required for this instruction

Example 3:

Access to both SFR spaces: No EXTR instruction required

MOV

S0TBUF, SSCRB

; reg, mem: S0TBUF via reg, SSCRB via mem

MOV

SSCTB, S0RBUF

; mem, reg: SSCTB via mem, S0RBUF via reg

In order to optimize accesses to the ESFR space, the distribution of the special

function registers between the two SFR ranges was chosen such that the ESFR

space holds registers which are rarely used during normal program execution. These

registers are mainly only written to during the initialization of the peripherals, and are

in most cases accessed via direct MEM addressing. However, except for the

direction control registers of PORT0 and PORT1, only registers new in the C167 are

moved to the extended SFR space. This is done to provide compatibility with existing

designs.

With one new module, however, a retranslation or even rewriting of pieces of code is

necessary. The CAPCOM2 Unit is on one hand new in the C167, on the other hand it

is somehow an ’old’ peripheral, since it is equal to the CAPCOM1 Unit known from

the ST10x166. Due to the amount of registers required for this unit, it is not possible

to place all registers into the normal SFR space in order to use code written for the

CAPCOM1 Unit to be used for the CAPCOM2 Unit without any changes (except for

address modifications). To minimize the modification effort, mostly used CAPCOM2

registers, such as the capture/compare or the mode control registers, are located in

the normal SFR space, and rarely used registers are placed into the ESFR space.

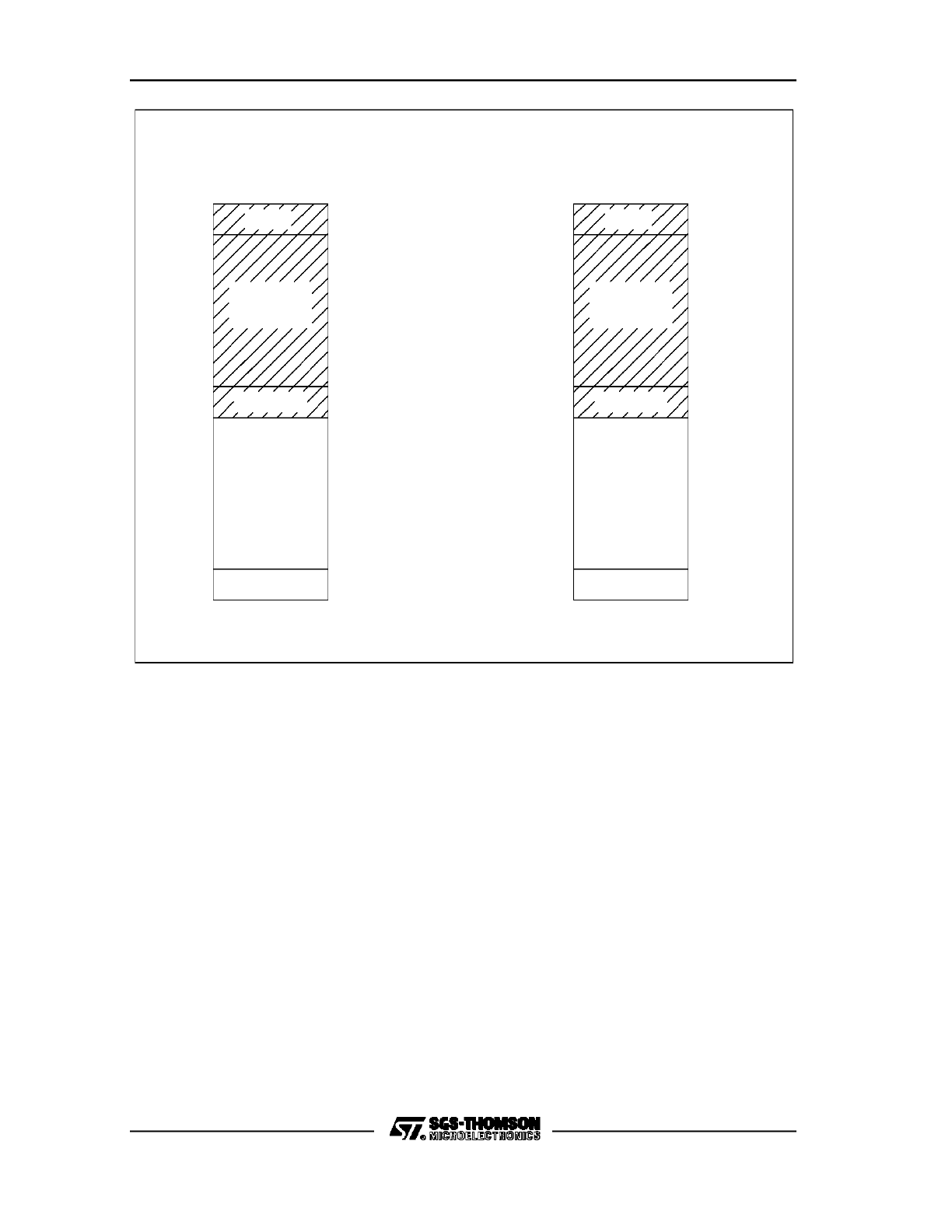

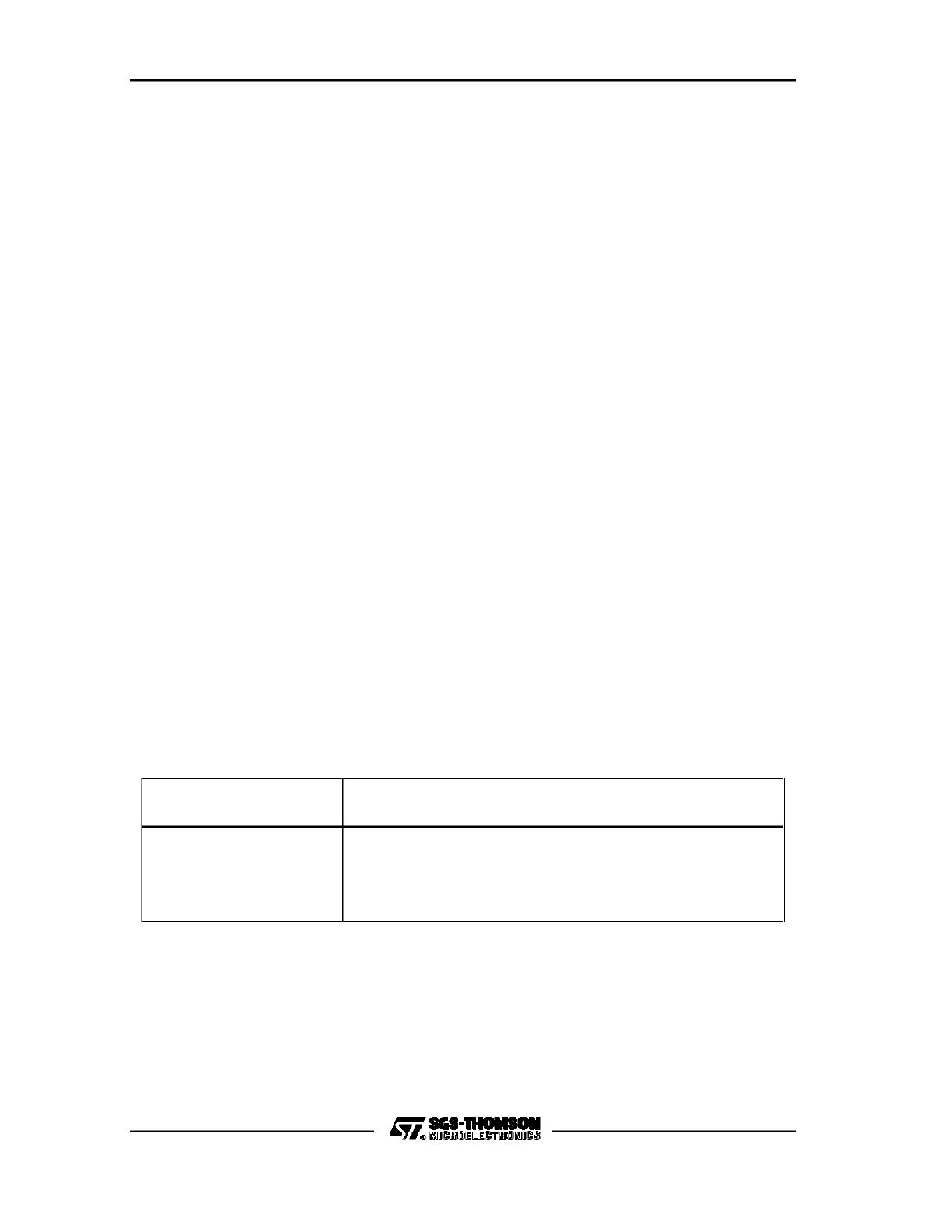

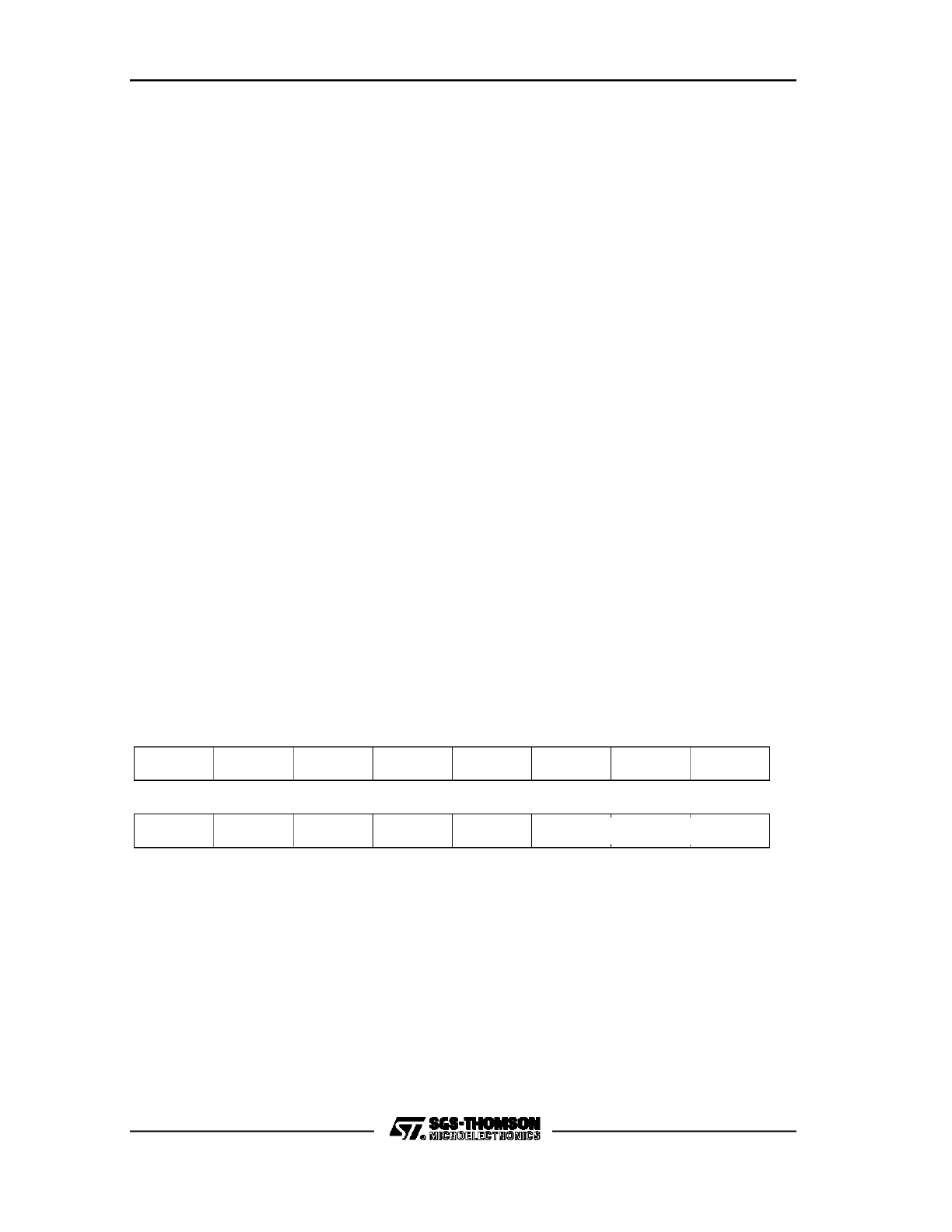

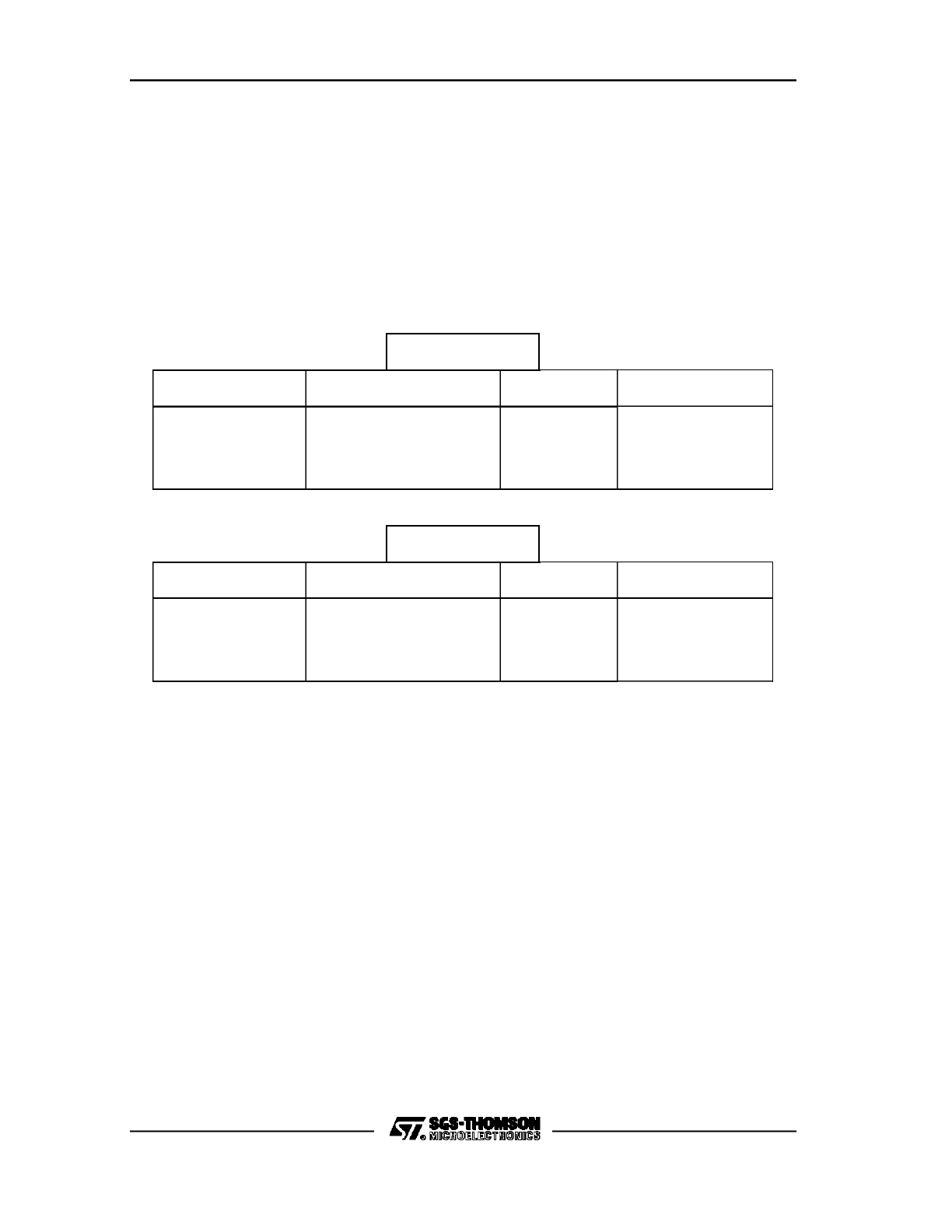

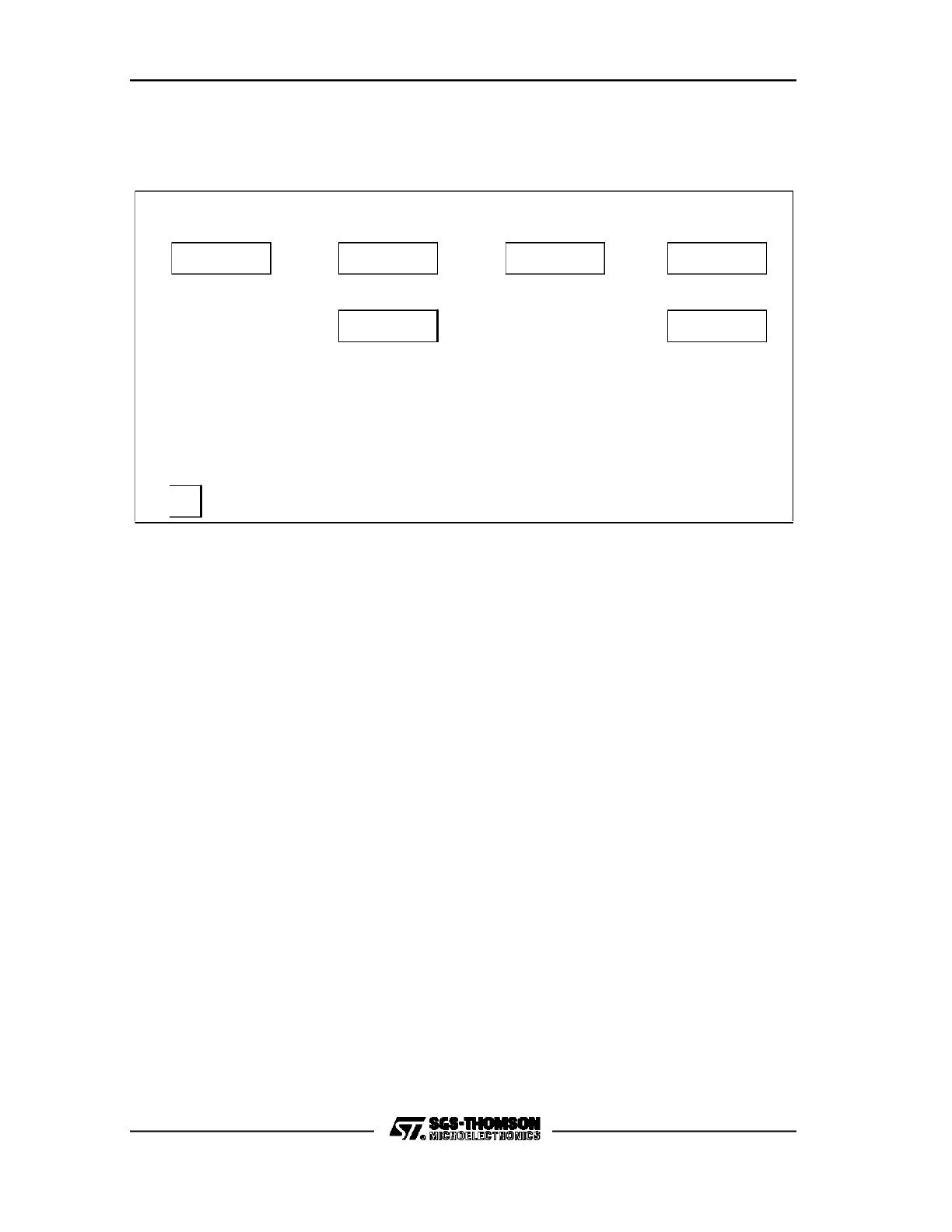

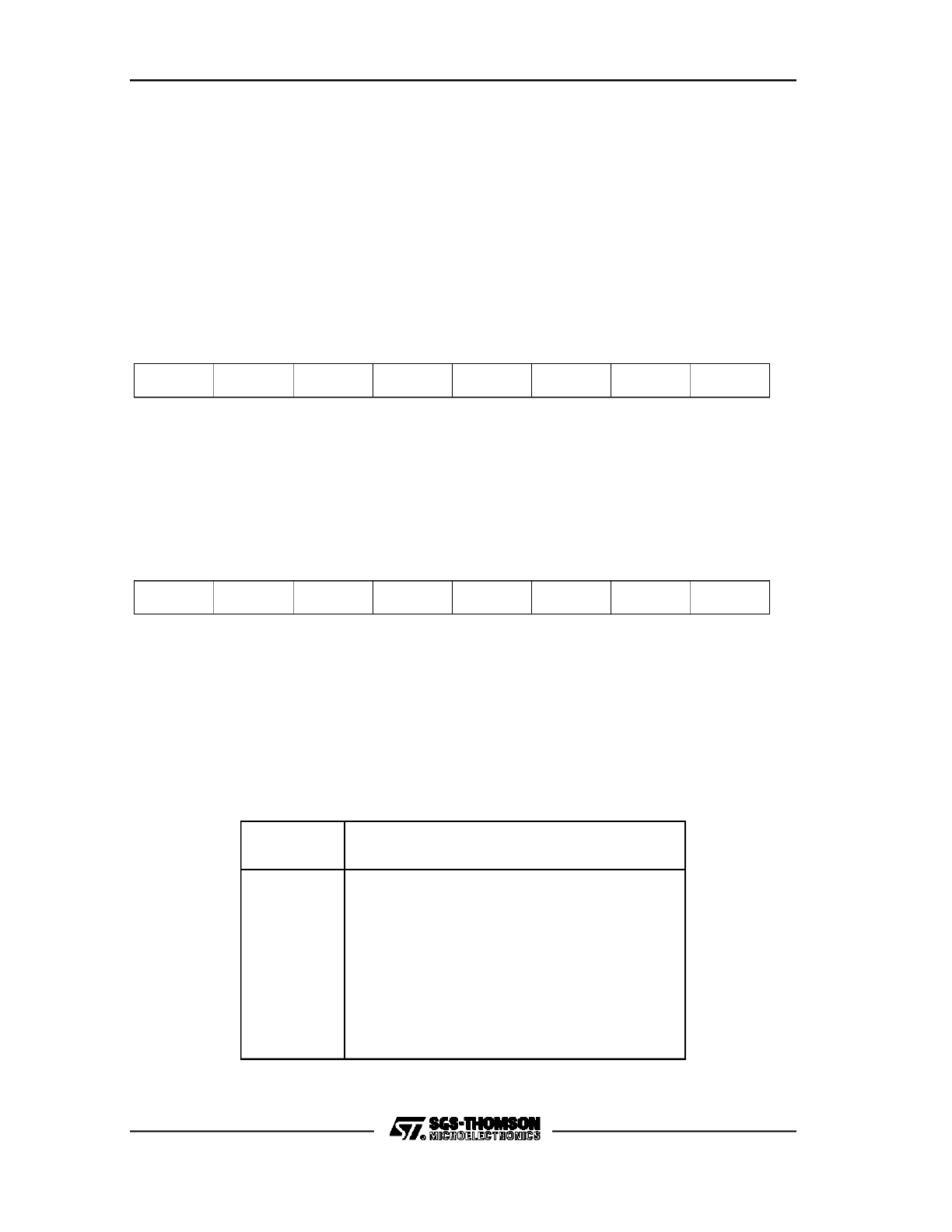

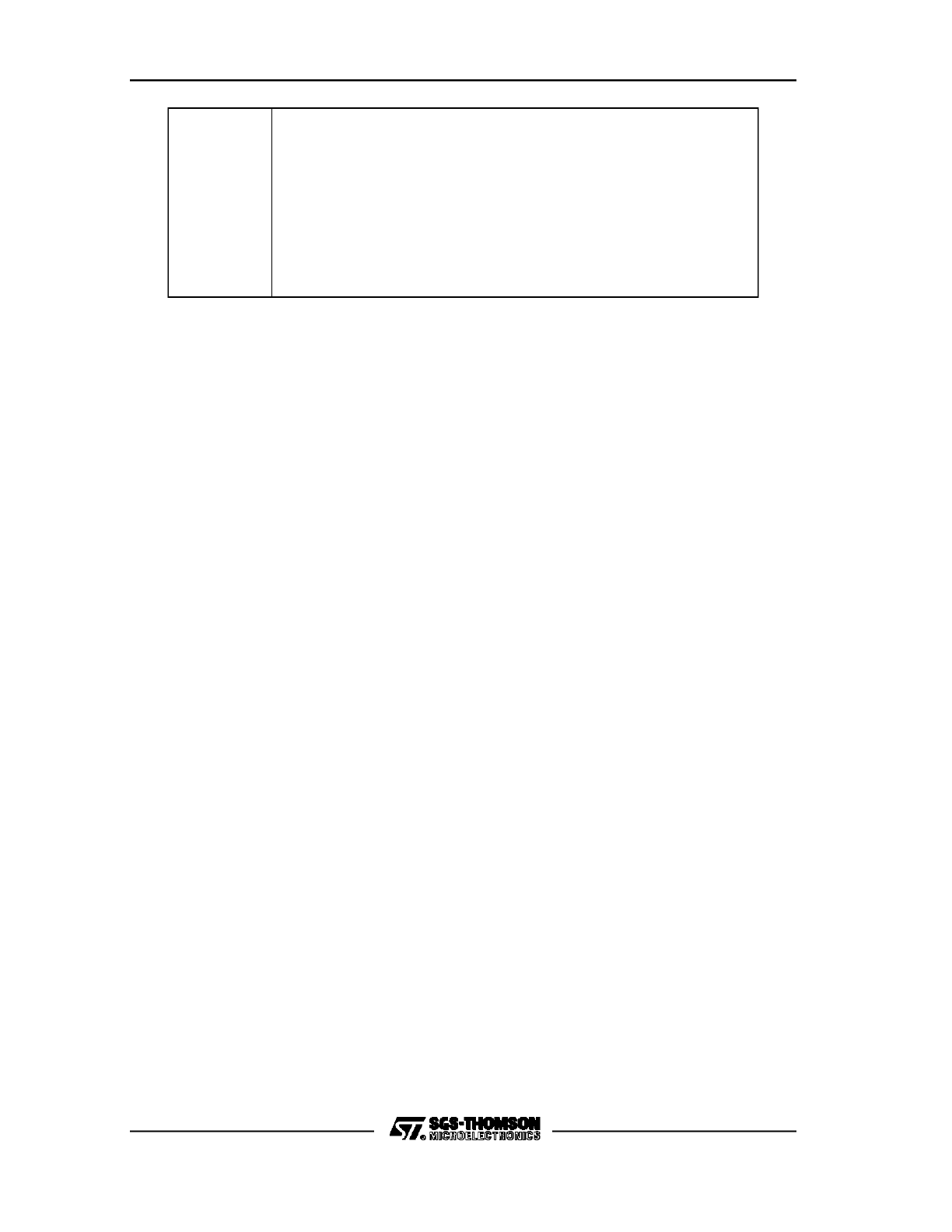

Figure 4. Standard and Extended SFR Spaces

C167 FAMILY PRELIMINARY USER MANUAL

28/180

GPRs

Reserved

Reserved

FEh

F0h

90h

80h

10h

00h

8-Bit

Address

Address

16-Bit

F1DFh

100h

F120h

F000h

F020h

*

*

Except for Port 0 and 1 Direction Registers

Bit-

Addressable

Addressable

Non Bit-

Non Bit-

Addressable

Addressable

Bit-

FE20h

FE00h

FF20h

FF00h

FFDFh

16-Bit

Address

Address

8-Bit

00h

10h

80h

90h

F0h

FEh

CPU Reg.

GPRs

VR001892

Standard SFR space

Extended ESFR Space

CPU Reg.

Figure 4 shows an overview of both, the normal SFR space and the ESFR space.

One can see, that the two spaces are very similar. The General Purpose Register

area in the upper portion of the normal SFR space is also reflected in the ESFR

range. Thus, the GPRs are also available within an EXTR instruction sequence. Note

that the GPR area in both SFR spaces (the upper 16 word locations) must not be

accessed via a 16-bit address. Except for the PORT0 and PORT1 direction control

registers, the address range occupied by the CPU registers (FE00 - FE1E, and FF00

- FF1E) are reserved in the ESFR space.

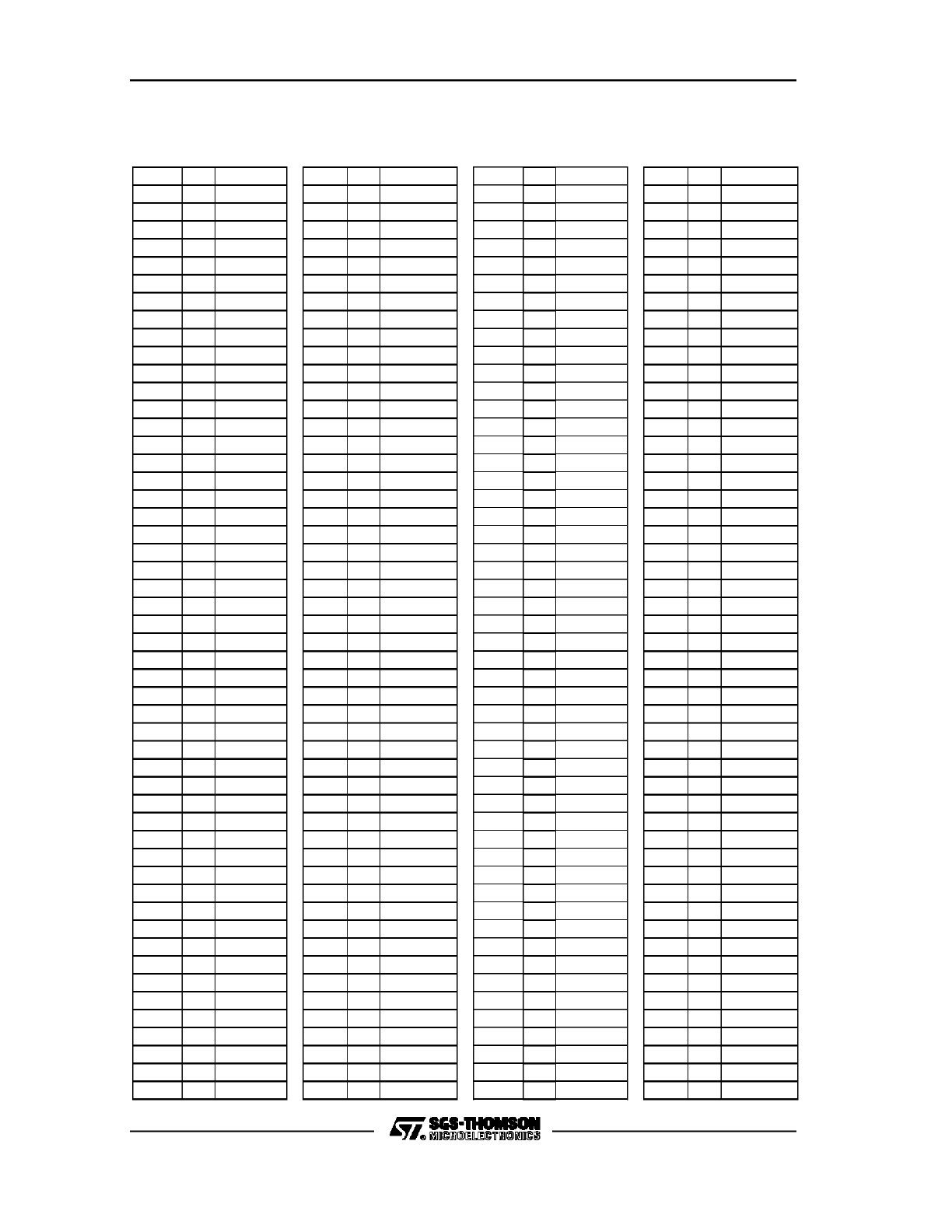

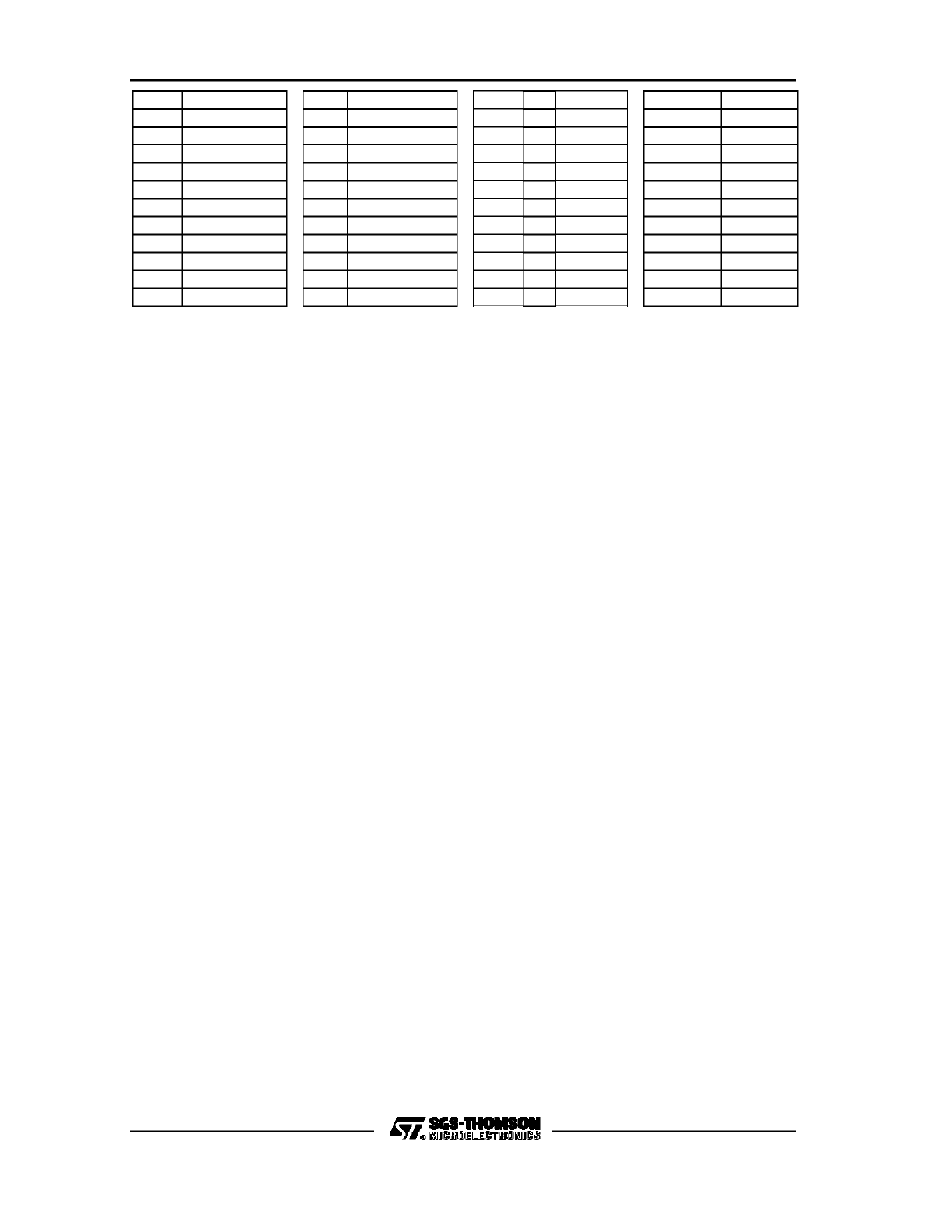

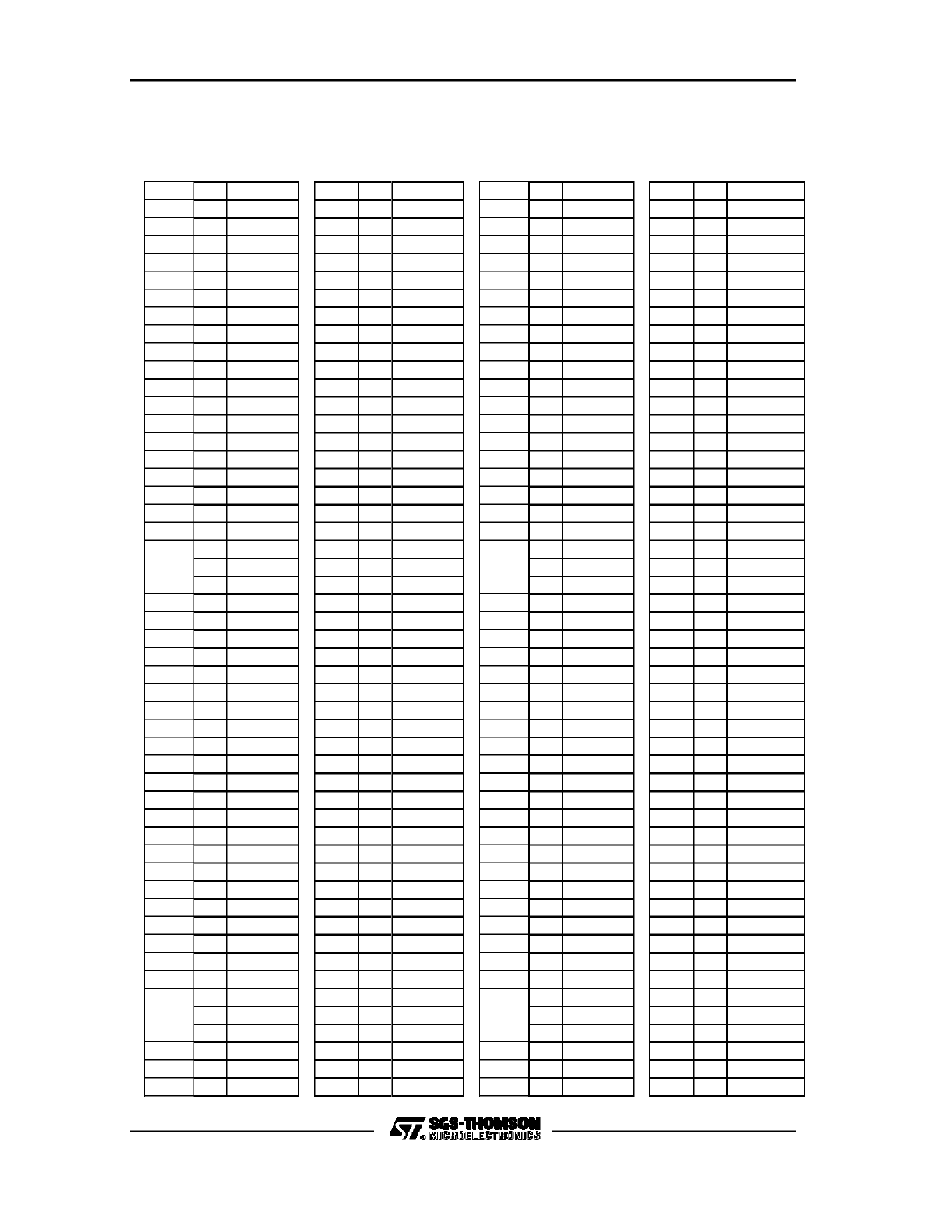

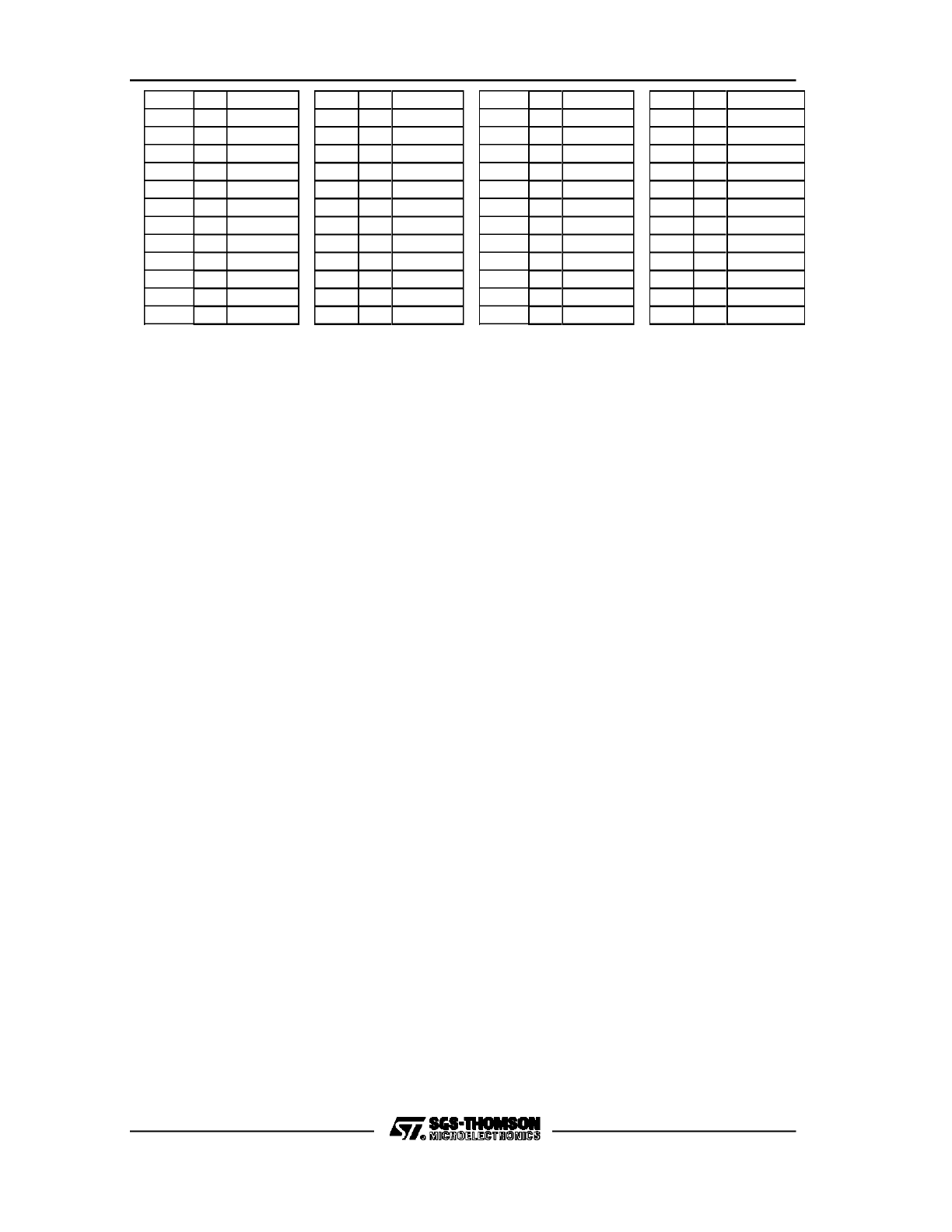

Tables 2.4-1 and 2.4-2 at the end of the Manual list all the Special Function Registers

in the C167.

Note: With respect to some Special Function Registers, this is an incompatibility with

the ST10x166 !

C167 FAMILY PRELIMINARY USER MANUAL

29/180

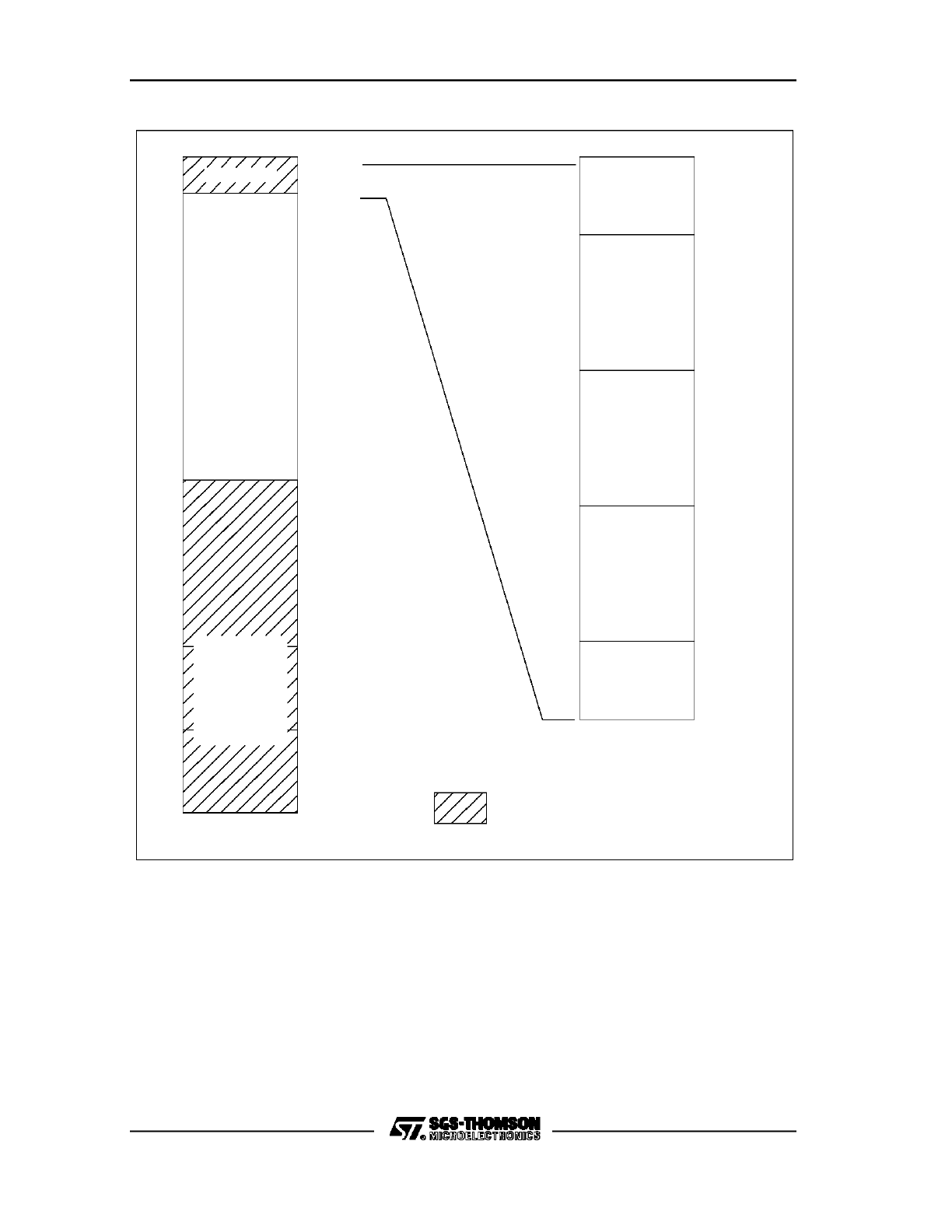

2.5

Internal Address Space

In the C167, the entire address range 00F000h through 00FFFFh in segment 0 is

mapped to internal addresses, that means, no external addresses will be generated

within this range. The right hand side of Figure 5 illustrates the different portions of

this area. Although the address space F200h through F5FFh is currently not used in

the C167, it is reserved for future expansion, and should not be used in an

application. An access to this area will result in a dummy access, and no external

addresses will be generated. The data of a write access will be lost, and a read

returns no valid data.

As already described in Chapter 2.1, the lower 32 KByte of either segment 0 or 1

(depending on ROM mapping) will also be mapped to internal addresses if the ROM

is enabled. The left hand side of Figure 5 shows the internal address spaces within

segment 0.

Note: This is an incompatibility with the ST10x166 !

C167 FAMILY PRELIMINARY USER MANUAL

30/180

Figure 5. Internal Address Space (Segment 0)

FE00h

FA00h

F200h

F000h

0000h

2000h

4000h

VR001893

F000h

FFFFh

Internal

8000h

ROM

(if enabled

and mapped

to Segment

0)

External

Memory

RAM, SFR

Extended

ESFR

Space

F600h

Reserved

Normal

SFR

Space

RAM

Dual Port

2 KByte

Internal Address Space

No External Addresses Generated

C167 FAMILY PRELIMINARY USER MANUAL

31/180

3.

BUS CONTROL UNIT

3.1

Extended Address Space

The C167 provides the full addressing capability of the ST10 family. The total

address space is extended to the maximum range of 16 MByte. This requires 24-bit

addressing, address lines A23..A0. The lower 16 bits of the address are provided via

Port 0 (in multiplexed bus mode) or via Port 1 (in non-multiplexed bus mode). The

upper 8 bits of the address are optionally provided via Port 4, which in the C167 is

extended to 8 bits (see Chapter 11).

The C167 has the capability of addressing up to 16 MByte, however, there are

several options for the user to configure the part for the number of physical external

address lines actually required in the system. First, one can switch between

segmented or non-segmented mode. In the non-segmented mode, the total address

range is 64 KByte, segment 0. Second, in the segmented mode, the user can specify

the number of segment address lines required in the system. Either 0, 2, 4, or all 8

segment address lines can be configured. By this, the user can select the external

address space addressable through physical external address lines to be either

64 KByte, 256 KByte, 1 MByte, or the full 16 MByte range. And third, up to five chip

select signals can be generated automatically to select several, different address

ranges. For example, the segment address lines may be limited to four lines, giving

direct addressing capability of up to 1 MByte, but the chip select signals can be used

to enable several blocks (or memory devices) of 1 MByte, giving a total address

range of, for instance, 5 MByte. Figure 6 shows such a configuration example.

C167 FAMILY PRELIMINARY USER MANUAL

32/180

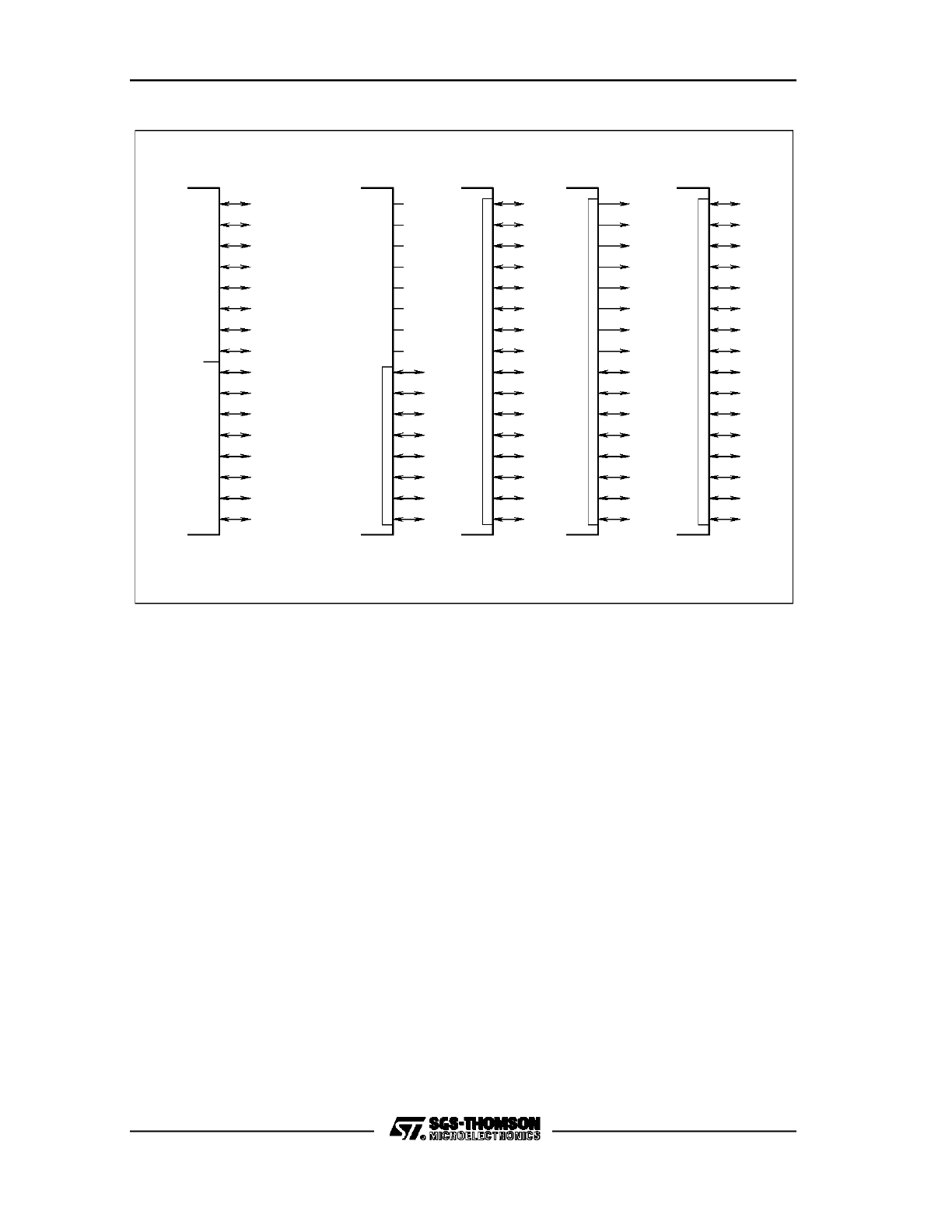

Figure 6. Address Range Configuration Example

ST10167

I/O

1 MByte

Device 5

Device 4

1 MByte

1 MByte

Device 3

Device 2

1 MByte

Device 1

1 MByte

CS4

CS3

CS2

CS1

CS0

P4.7-P4.4

PORT 0

PORT 1

P4.3-P4.0

Example: Using 20 Address Lines and

5 Chip Selects to Access a

VR0D1646

Range of 5 MByte

D15-D0

Data Bus

A19-A16

A15-A0

Address Bus

The total address space is divided into code segments and data pages. Each code

segment has an address range of 64 KByte, thus there exist 256 code segments.

The currently active code segment is specified by the Code Segment Pointer, CSP,

which is modified only through any JMPS (Jump Segment) or CALLS (Call Segment)

instruction. The CSP is also extended to 8 bits, which represent address bits

A23..A16.

C167 FAMILY PRELIMINARY USER MANUAL

33/180

Since each data page has an address range of 16 KByte, there exist 1024 data

pages. To select the data pages, four Data Page Pointers, DPP0 through DPP3, are

available, giving access to four data pages at one time. The data page pointers are

selected through the two most significant bits of any 16-bit data address. Each of the

four data page pointers in the C167 is extended to 10 bits, which represent address

bits A23..A14. See also Chapter 1 for a scheme to bypass the segments and pages.

For more information on the data page pointers please refer to the ST10 User

Manual.

3.2

System and Bus Configuration Control

In the ST10x166, the SYSCON register is used to control the overall system

configuration and the external bus. In addition, the BUSCON1 register and the

associated ADDRSEL1 register allow the user to partition the address space for

external devices with different bus access parameters such as bus width, wait states,

etc. Now in the C167, five bus configuration registers, BUSCON0 through

BUSCON4,

and

four

address

range

select

registers,

ADDRSEL1

through

ADDRSEL4, are implemented, offering the option to have at least five address

ranges with different bus parameters, adapted to the needs of the memories or

peripherals located to these address ranges.

The SYSCON register known from the ST10x166 is separated into two registers in

the C167: Into one new BUSCON0 register, which is used for programming the bus

related parameters as with the other BUSCON registers, and into one SYSCON

register, which holds the bits to program the overall configuration of the system. With

this separation, it is now possible, for instance, to have the ALE lengthening feature

directly after reset, and to have a clear and transparent way of programming the

ROM mapping, bus enable, etc. In the following sections, the new registers are

described.

Note: This is an incompatibility with the ST10x166 !

3.2.1 SYSCON Register

The new SYSCON register is dedicated to global system functions, and is primarily

only written once during the initialization routine. The entire SYSCON register is

locked out from being written after the first occurrence of the EINIT instruction. This

improves system security such that if software were to unintentionally execute a write

access to this SFR, after the execution of the EINIT instruction, that it would be

ignored.

C167 FAMILY PRELIMINARY USER MANUAL

34/180

The new SYSCON register hereafter will occupy the bit addressable address

0FF12h. In the following, some important controls of the SYSCON register are

described.

SYSCON (FF12h/89h)

System Configuration Register

Reset Value: xxxxh

STKSZ

ROMS1

SGTDIS

ROMEN

BYTDIS

CLKEN

15

14

13

12

11

10

9

8

0

1

2

3

4

5

6

7

WRCFG

R

R

R

R

R

R

R

b15, b14, b13 = STKSZ: System Stack Size Selection.

b12 = ROMS1: ROM Segment Mapping control bit.

ROMS1 = 0: internal ROM mapped to segment 0.

ROMS1 = 1: internal ROM mapped to segment 1.

b11 = SGTIS: Segmentation Disable bit.

SGTDIS = 0: Segmentation enabled.

SGTDIS = 1: Segmentation disabled.

This bit does not control the number of Part 4 pins used.

b10 = ROMEN: ROM Enable bit.

ROMEN = 0: Internal ROM disabled, all instruction and data accesses to the ROM

space will be accessed externally.

ROMEN = 1: Internal ROM enabled, all instruction and data accesses to the ROM

space will access the ROM/FLASH.

b9 = BYTDIS: Byte High Enable (BHE#) pin control bit.

BYTDIS = 0: BHE# enabled.

BYTDIS = 1: BHE# disabled ; pin can be used for normal I/O.

b8 = CLKEN: System Clock Output (CLKOUT) Enable bit.

CLKEN = 0: CLKOUT disabled ; pin can be used for normal I/O.

CLKEN = 1: CLKOUT enabled ; pin used for system clock output.

b7 = WRCFG: Write Configuration Control Bit.

WRCFG = 0: Normal configuration of WR# and BHE#.

WRCFG = 1: WR# pin acts as WRL#, BHE# pin acts as WRH#.

b6 to b0 = R: Reserved.

Stack Size Parameters

The stack size selection is extended in the new SYSCON register from two to three

bits, due to the extended RAM space. The following table shows the possible options

for the stack:

C167 FAMILY PRELIMINARY USER MANUAL

35/180

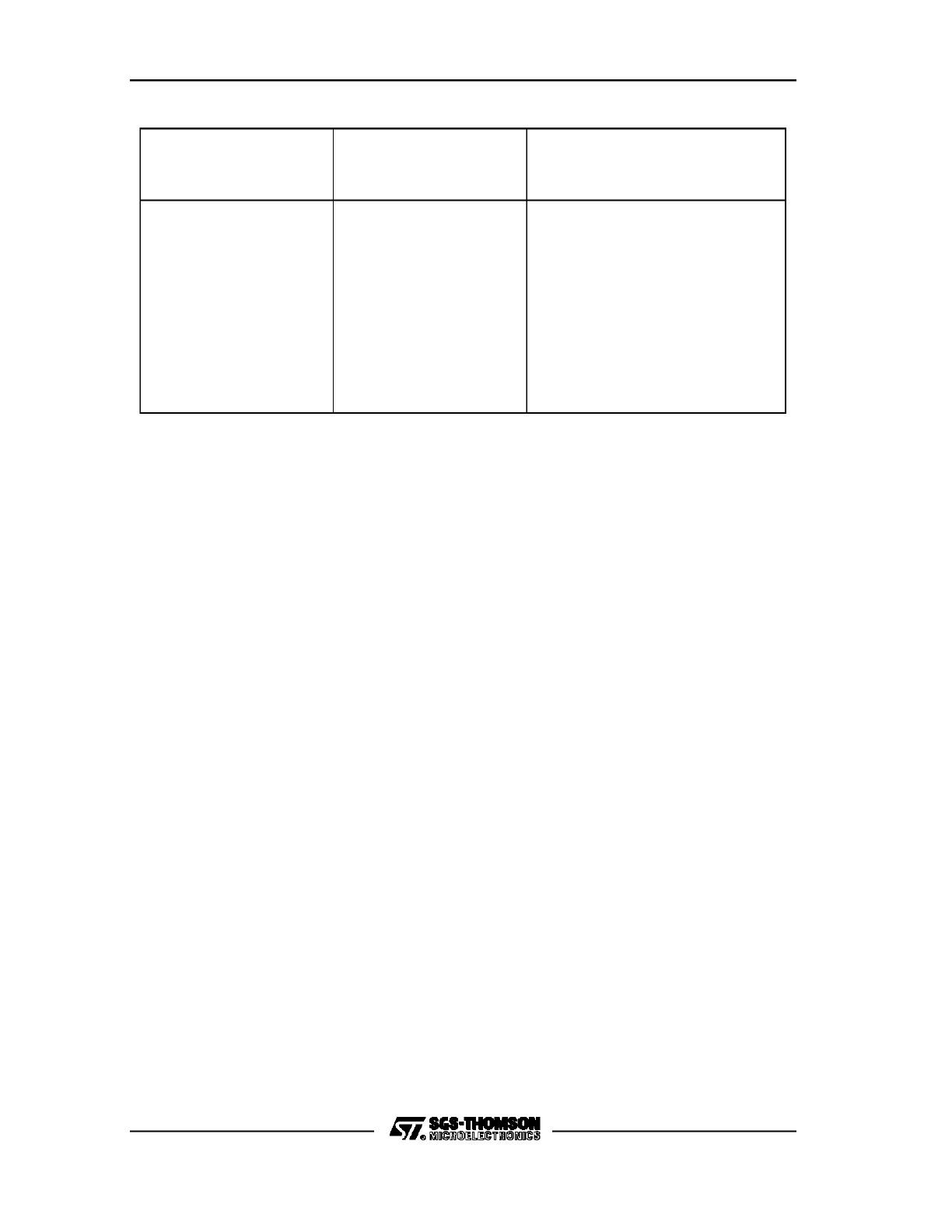

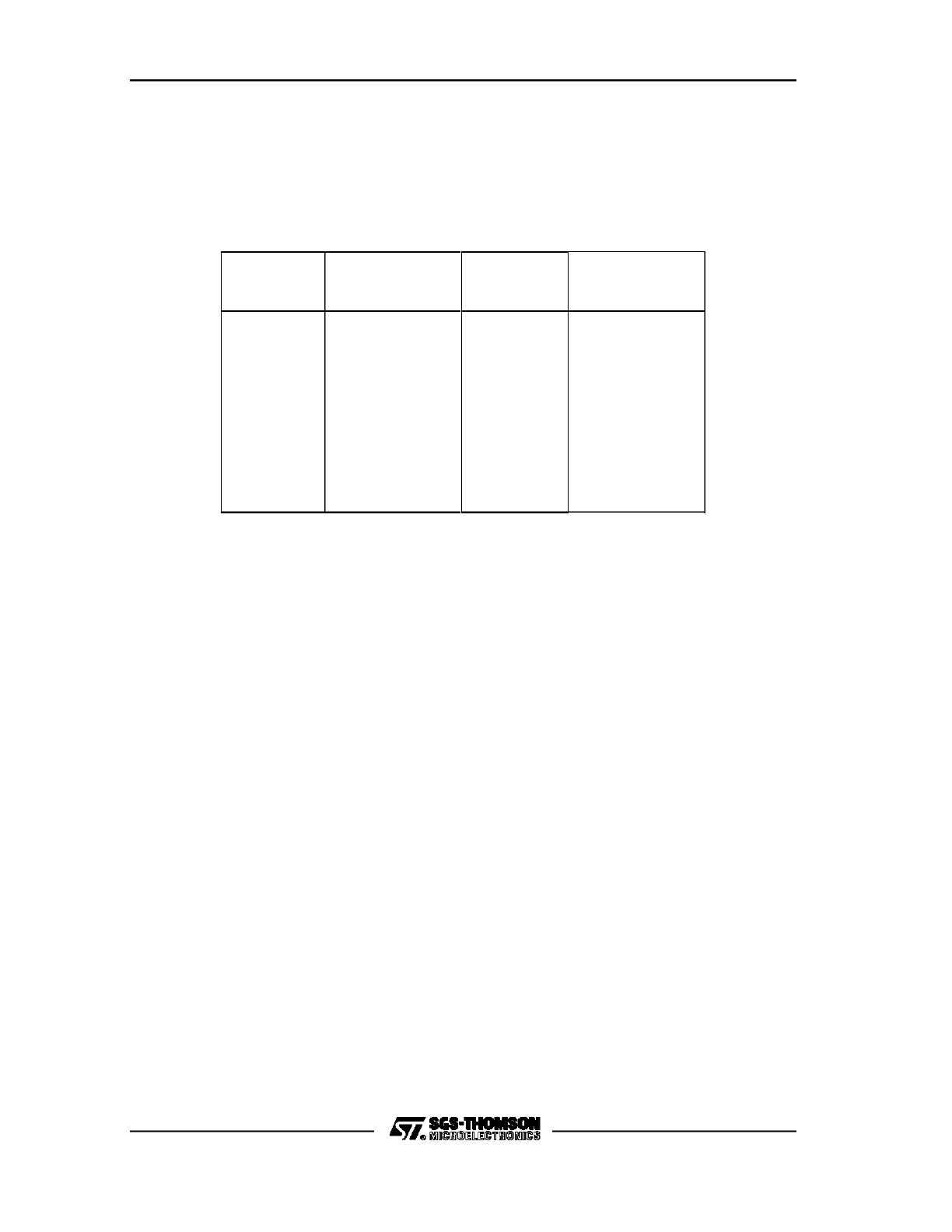

SYSCON[15..13]

STKSZ

Maximum System

Stack Size

Address Range

0 0 0

256 Words

FA00h - FBFFh

0 0 1

128 Words

FB00h - FBFFh

0 1 0

64 Words

FB80h - FBFFh

0 1 1

32 Words

FBC0h - FBFFh

1 0 0

512 Words

F800h - FBFFh

1 0 1

reserved

reserved

1 1 0

reserved

reserved

1 1 1

No Wrapping

F600h - FDFFh

Entire internal RAM (see Note)

As one can see from this table, the internal system stack may be mapped to the

single port RAM area. Stack size options 0..4 mean that the stack will always reside

in the specified address range, there is a wrap-around mechanism implemented for

the stack (although the contents of the stack pointer itself will not perform this

wrapping; see ST10 User Manual). When the No Wrapping option is selected, the

stack may occupy the entire internal RAM space, from 00F600h to 00FDFFh. In this

case, the Stack Underflow and Overflow SFRs should be used to ensure that

unintentional accesses do not occur. In all cases, the internal system stack can

never be mapped to external memory.

Note: Special care must be taken when the no wrapping option is selected. In this

case, the Stack Pointer, SP, can be loaded with any word address between F000h

and FFFEh. No hardware protection exists against address values which are

occupied by either the reserved address space, or the standard or extended SFR

ranges, thus, the SP must never be loaded with addresses in the range F000h

through F1FEh (ESFR space), F200h through F5FFh (reserved space), and FE00h

through FFFEh (SFR space), otherwise unexpected results will occur!

Segmentation Control

As in the ST10x166, the bit SGTDIS controls whether segmentation is enabled or

not. After reset, this bit is ’0’, thus segmentation is enabled. However, different to the

ST10x166, this bit does not automatically configure port P4 to output the segment

address lines (this is performed through the system startup configuration, described

in section 3.5). The SGTDIS bit in the C167 is only used to enable segment

addresses to port P4, and to determine the correct stack operations for traps and

interrupts (optionally push/pop the Code Segment Pointer, CSP).

C167 FAMILY PRELIMINARY USER MANUAL

36/180

ROM Enabling and Mapping

The ROM Enable bit, ROMEN, determines whether the on-chip ROM is enabled or

not. This bit is set automatically during reset according to the state of the External

Access input pin, EA#. If this pin is high during reset, ROMEN will be set to ’1’, and

the C167 will start execution out of the internal ROM. A low level at this pin during

reset will force the C167 to start execution out of external memory, with external bus

parameters determined through the System Startup Configuration Selection (see

section 3.5). Bit ROMEN will be cleared in this case.

For the mapping of the internal ROM to either segment 0 or segment 1, other than in

the ST10x166, an individual bit, ROMS1, is implemented. The default after reset is

ROMS1 = 0, mapping the ROM to segment 0. If the ROM is enabled, one has to take

care of that no external addresses will be generated in the lower 32 KByte address

space of either segment 0 (ROMS1 = 0) or segment 1 (ROMS1 = 1).

Note that, until the execution of the EINIT instruction, the default values in the

SYSCON register can be changed through software. One has to take care, however,

that bits ROMEN and ROMS1 should never be changed when executing out of the

on-chip ROM, otherwise unexpected results may occur.

Note: The Write Configuration (WRCFG) control is explained in detail in section 3.4.

3.2.2 BUSCON0 Register

As mentioned above, the bus related control bits of the ST10x166 SYSCON register

are moved to a new BUSCON0 register in the C167. This register is shown hereafter.

This change allows to organize the BUSCON0 register in the same way as any other

BUSCON register, giving the same functionality and a consistent way of

programming.

BUSCON0 (FF0Ch/86h)

Bus Configuration Register 0

Reset Values: 0000h/ 0600h/ 0640h/ 0680h/ 06C0h

RDYEN0

R

BUSACT0

ALECTL0

R

15

14

13

12

11

10

9

8

0

1

2

3

4

5

6

7

MTTC0

RWDC0

0

0

R

BTYP

MCTC

C167 FAMILY PRELIMINARY USER MANUAL

37/180

b15, b14 = 0.

b13 = R: Reserved.

b12 = RDYEN0: READY# Input Enable control bit.

RDYEN0 = 0: READY# function disabled for BUSCON0 accesses.

RDYEN0 = 1: READY# function enabled for BUSCON0 accesses.

b11 = R: Reserved.

b10 = BUSACT0: Bus Active control bit.

b9 = ALECTL0: ALE Lengthening control bit.

b8 = R: Reserved.

b6, b7 = BTYP: External Bus Configuration Control.

b5 = MTTC0: Memory Tri-state Time Control.

b4 = RWDC0: Read/Write Delay Control.

b3 to b0 = MCTC: Memory CYcle Time Control.

If during reset, the EA# pin is at a high level, the BUSCON0 register is cleared to

’0000’, and execution begins out of the on-chip ROM. An external bus can then be

selected via programming the BUSCON0, BUSCON1..4, and ADDRSEL1..4 registers

appropriately.

If the EA# pin is low, forcing execution to start with external memory, register

BUSCON0 is set according to the selected bus type, with default values for the bus

parameters:

MCTC

= 0000

15 Memory Cycle Time Waitstates

RWDC0

= 0

Read/Write Delay Enabled

MTTC0

= 0

One Memory Tri-State Waitstate

BTYP

= XX

set according to the level at pins P0xx and P0xx during reset

ALECTL0 = 1

ALE Lengthening Enabled

BUSACT0

= 1

External Bus Enabled

RDYEN0 = 0

READY# Input Disabled

The coding of the BTYP bits in the BUSCON0 (and also in registers BUSCON1..4) is

changed compared to the ST10x166. The new BTYP coding is shown in the

following:

BTYP

Selected Bus Operation

0 0

0 1

1 0

1 1

8-Bit Non-Multiplexed Bus

8-Bit Multiplexed Bus

16-Bit Non-Multiplexed Bus

16-Bit Multiplexed Bus

C167 FAMILY PRELIMINARY USER MANUAL

38/180

With this coding, a clear reference of a BTYP bit to the selected operation is given.

BTYP.1 controls the width of the bus (8-bit or 16-bit), while BTYP.0 controls whether

the bus is multiplexed or non-multiplexed. In addition, this coding directly reflects the

default bus configuration selection during reset at the P0 pins (see System Startup

Configuration).

One can see that, other than in the ST10x166, external execution will start with the

ALE lengthening enabled, offering the slowest possible bus. The user can reprogram

the bus parameters during the initialization (or during normal run time) to values

required by the external hardware.

Other than for the bus configuration registers BUSCON1..4, the BUSCON0 register

has no associated address select register ADDRSEL. Instead, the BUSCON0

register controls the bus for any external accesses to addresses which are not

covered by one of the address select register, i.e. it fills the gaps between these

address ranges.

To indicate an external access controlled through the BUSCON0 register, and to

allow a simple selection of the memory or peripheral, an individual chip select line,

CS0#, is assigned to the BUSCON0 register. If CS0# is enabled (through System

Startup Configuration, see section 3.5), it goes to a low level for each external

access controlled through BUSCON0, i.e. for each external access outside the range

of the ADDRSEL registers. It will go to a high level for each other access. See

section 3.3 for details on the chip select lines.

3.2.3 BUSCON1..4 and ADDRSEL1..4 Registers

Hereafter is shown the configuration of a BUSCON1..4 register. Although these

registers look similar to the BUSCON0 register, some differences exist. Each of the

BUSCON1..4 registers has an associated ADDRSEL1..4 register, which specifies the

active address range for this BUSCON register. That means, for an external access

to an address range specified through an ADDRSELx register, the parameters of the

bus are controlled by the respective BUSCONx register.

The second difference is the initialization after reset. The BUSCON1..4 registers are

always initialized to all ’0000’, while the BUSCON0 register is loaded according to the

selected startup configuration during reset.

A further difference between the BUSCON1..4 and the BUSCON0 registers is in the

options for the chip selects, detailled in Chapter 3.3.

C167 FAMILY PRELIMINARY USER MANUAL

39/180

Note: Special care must be taken when programming the BUSCON registers. An

external bus will be enabled as long as at least in one of the BUSCON register the

BUSACTx bit is set. Port 1 will be used for address output if at least through one of

the BUSCON registers a non-multiplexed bus is selected. Port 1 will also continue to

output the addresses for an access via a multiplexed bus, controlled through another

BUSCON register.

BUSCON1 (FF14h/8Ah)

Bus Configuration Register 1

Reset Value: 0000h

RDYEN1

R

BUSACT1

ALECTL1

R

15

14

13

12

11

10

9

8

0

1

2

3

4

5

6

7

MTTC1

RWDC1

CSREN1

R

BTYP

MCTC

CSWEN1

b15 = CSWEN1: Write Chip Select Enable control bit.

b14 = CSREN1: Read Chip Select Enable control bit.

B13 = R: Reserved.

b12 = RDYEN1: READY# Input Enable control bit.

RDYEN1 = 0: READY# function disabled for BUSCON1 accesses.

RDYEN1 = 1: READY# function enabled for BUSCON1 accesses.

b11 = R: Reserved.

b10 = BUSACT1: Bus Active control bit.

b9 = ALECTL1: ALE Lengthening control bit.

b8 = R: Reserved.

b7, b6 = BTYP: External Bus Configuration Control.

b5 = MTTC1: Memory Tri-state Time Control.

b4 = RWDC1: Read/Write Delay Control.

b3 to b0 = MCTC: Memory Cycle Time Control.

For each BUSCON1..4 register, an individual chip select line CS1#..CS4# is

associated to save external glue logic for chip select generation. If a CSx# is enabled

(through System Startup Configuration, see section 3.5), the signal will go low for any

external access in the range defined through the respective address select register

ADDRSELx. It will go to a high level for any internal access or accesses outside the

specified address range.

In order to support the extended address range of 16 MByte, the possible address

range selections in the Address Select Registers ADDRSEL1..4 are also extended.

The Range Size field now allows the selections shown in the following table. This

table also shows the reference between the range size and the range start address.

C167 FAMILY PRELIMINARY USER MANUAL

40/180

All sixteen bits of the ADDRSEL registers are now used for the specification of the

address range for a BUSCON register. Note that the relevant bits (R) define the

associated upper address bits of the selected address range, they are associated

with address lines A23..A12. One can see that the upper 8 bits of the ADDRSEL1..4

registers directly relate to the respective code segment (A23..A16). The bits marked

with ’x’ are don’t care bits.

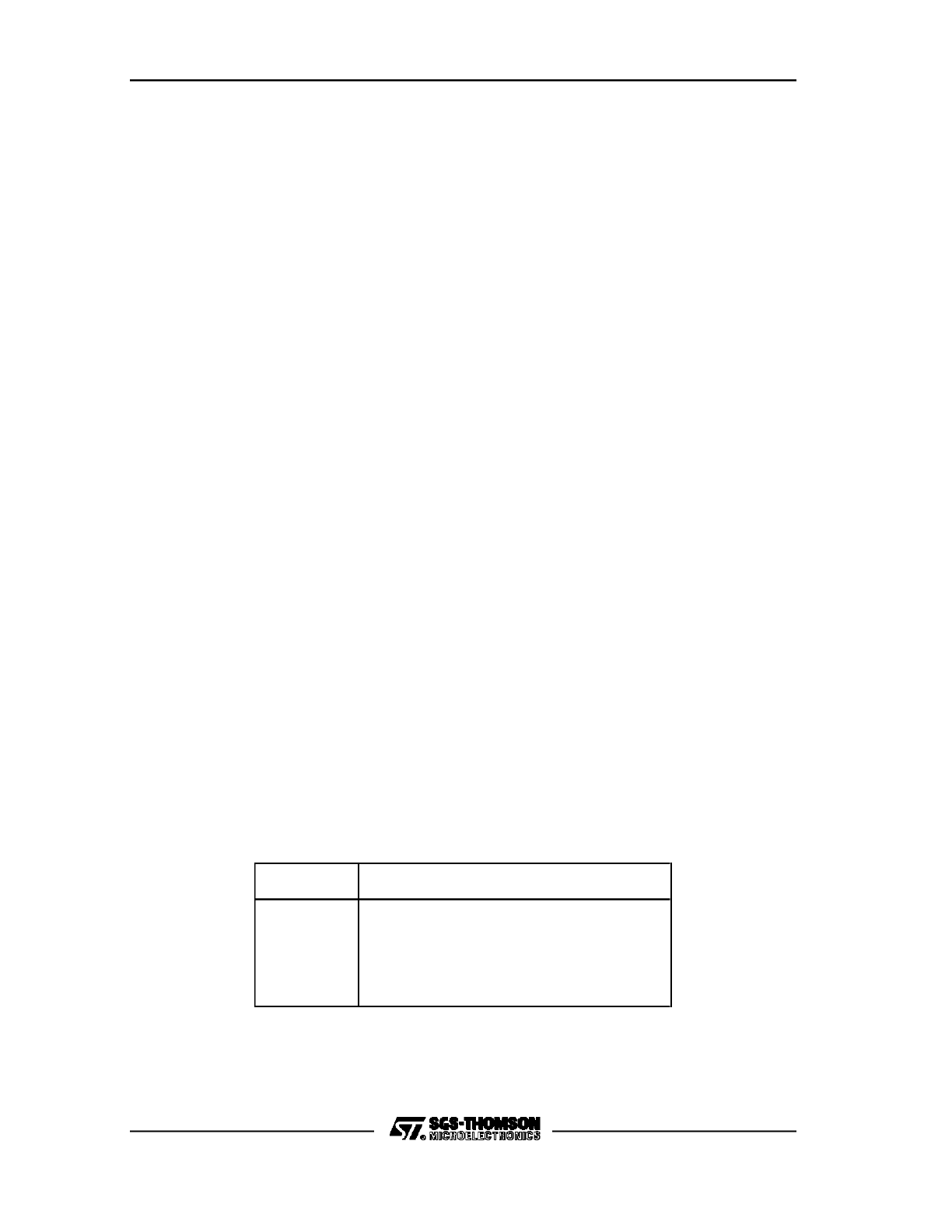

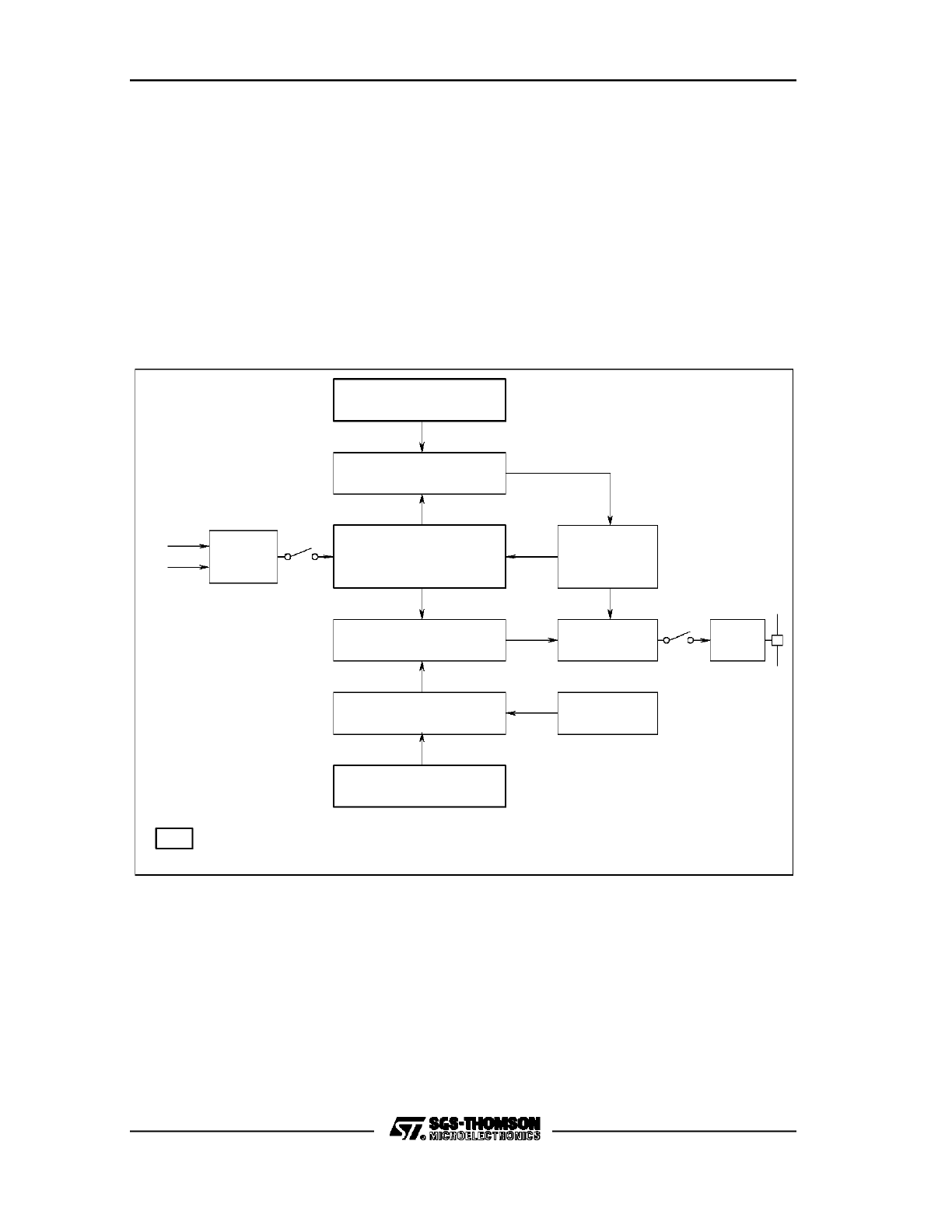

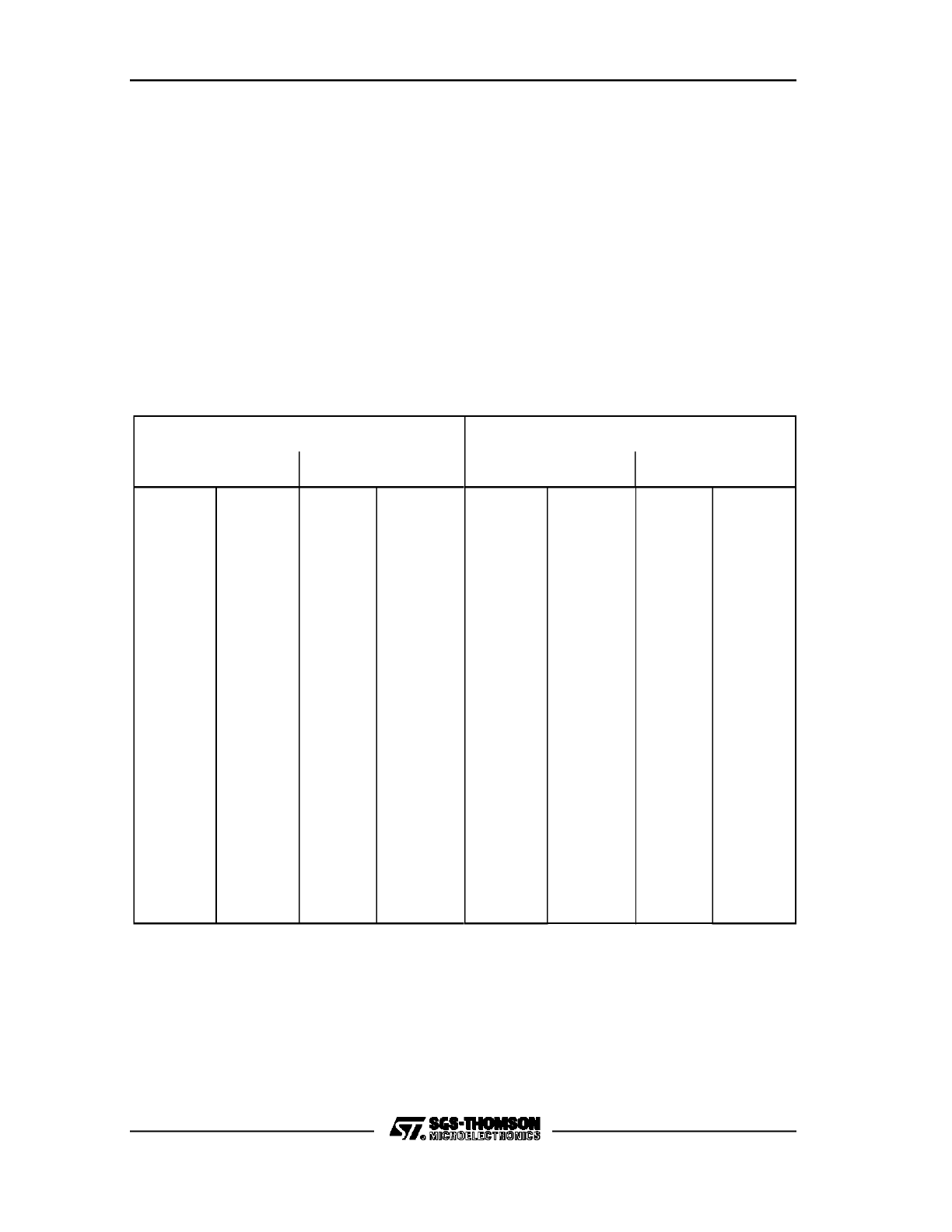

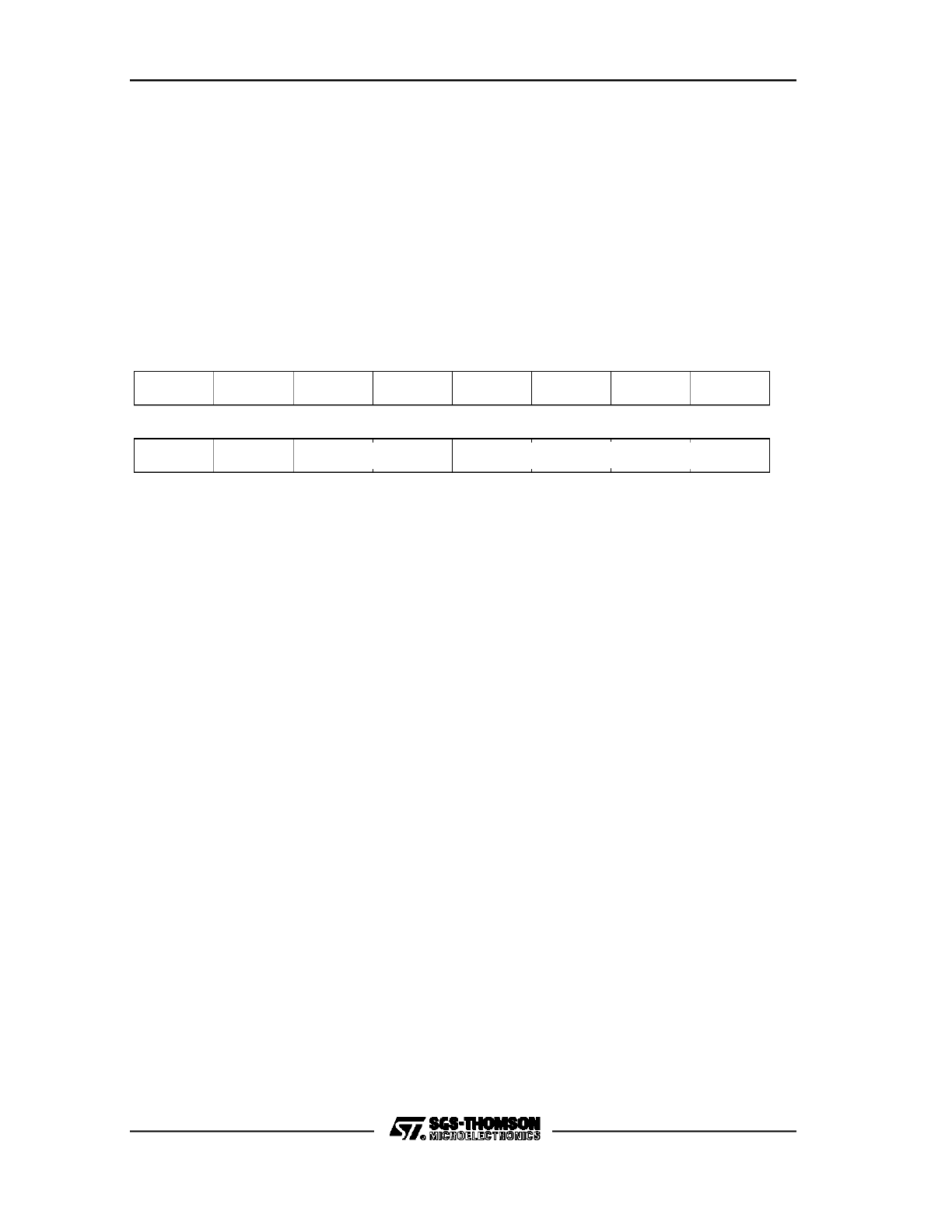

Range Size

RGSZ

Selected Address

Range

Relevant (R) bits of

Range Start Address RGSAD

0 0 0 0

4 KByte

RRRRRRRRRRRR

0 0 0 1

8 KByte

RRRRRRRRRRR x

0 0 1 0

16 KByte

RRRRRRRRRR xx

0 0 1 1

32 KByte

RRRRRRRRR xxx

0 1 0 0

64 KByte

RRRRRRRR xxxx

0 1 0 1

128 KByte

RRRRRRR xxxxx

0 1 1 0

256 KByte

RRRRRR xxxxxx

0 1 1 1

512 KByte

RRRRR xxxxxxx

1 0 0 0

1 MByte

RRRR xxxxxxxx

1 0 0 1

2 MByte

RRR xxxxxxxx x

1 0 1 0

4 MByte

RR xxxxxxxxx x

1 0 1 1

8 MByte

R xxxxxxxxxxx

1 1 x x

reserved

Note: In order to allow sections of 4 and 8 KByte, and to implement a more general

scheme, the ADDRSEL register organization has been rearranged, compared to the

ST10x166. The smallest section will be 4 KByte (instead of 2 KByte in the

ST10x166), the Range Size field is now 4 bits, and the Start Address field is now 12

bits. Although this leads to incompatibility with existing programs, the advantages

justify this change.

Note: This is an incompatibility with the ST10x166 !

Hereabove is the bus configuration register BUSCON1, while the associated address

range select register ADDRSEL1 is shown herafter:

C167 FAMILY PRELIMINARY USER MANUAL

41/180

ADDRSEL1 (FE18h/0Ch)

Address Select Register 1

Reset Value: 0000h

15

14

13

12

11

10

9

8

0

1

2

3

4

5

6

7

RGSZ

RGSAD [11..4]

RGSAD

b15 to b4 = RGSAD: BUSCON1 Address Range Start Address Selection.

b3 to b0 = RGSZ: BUSCON1 Address Range Selection.

Registers BUSCON2..4 and ADDRSEL2..4 are organized in the same manner. For

more details on the BUSCON and ADDRSEL registers please refer to the ST10 User

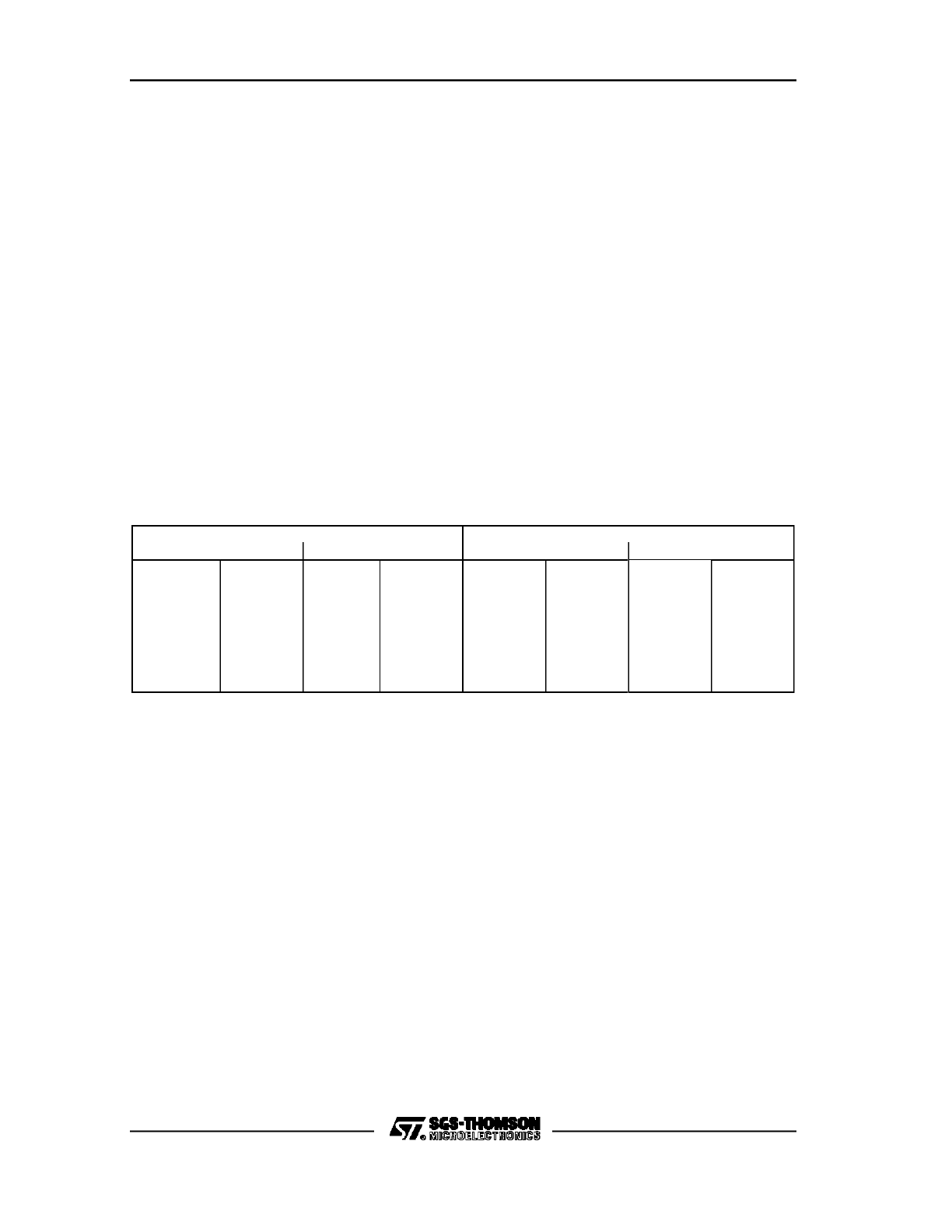

Manual. The address locations of these registers in the SFR space are as follows:

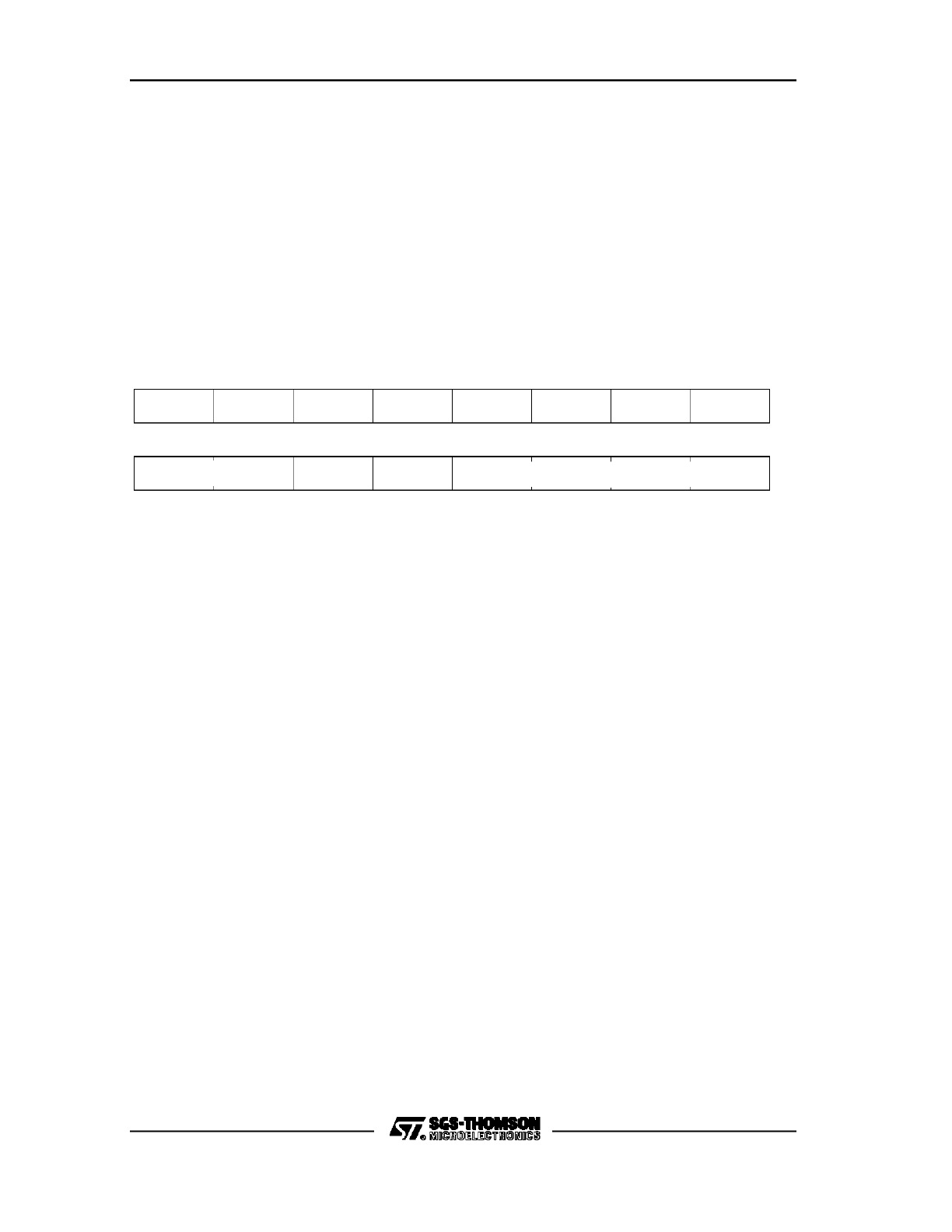

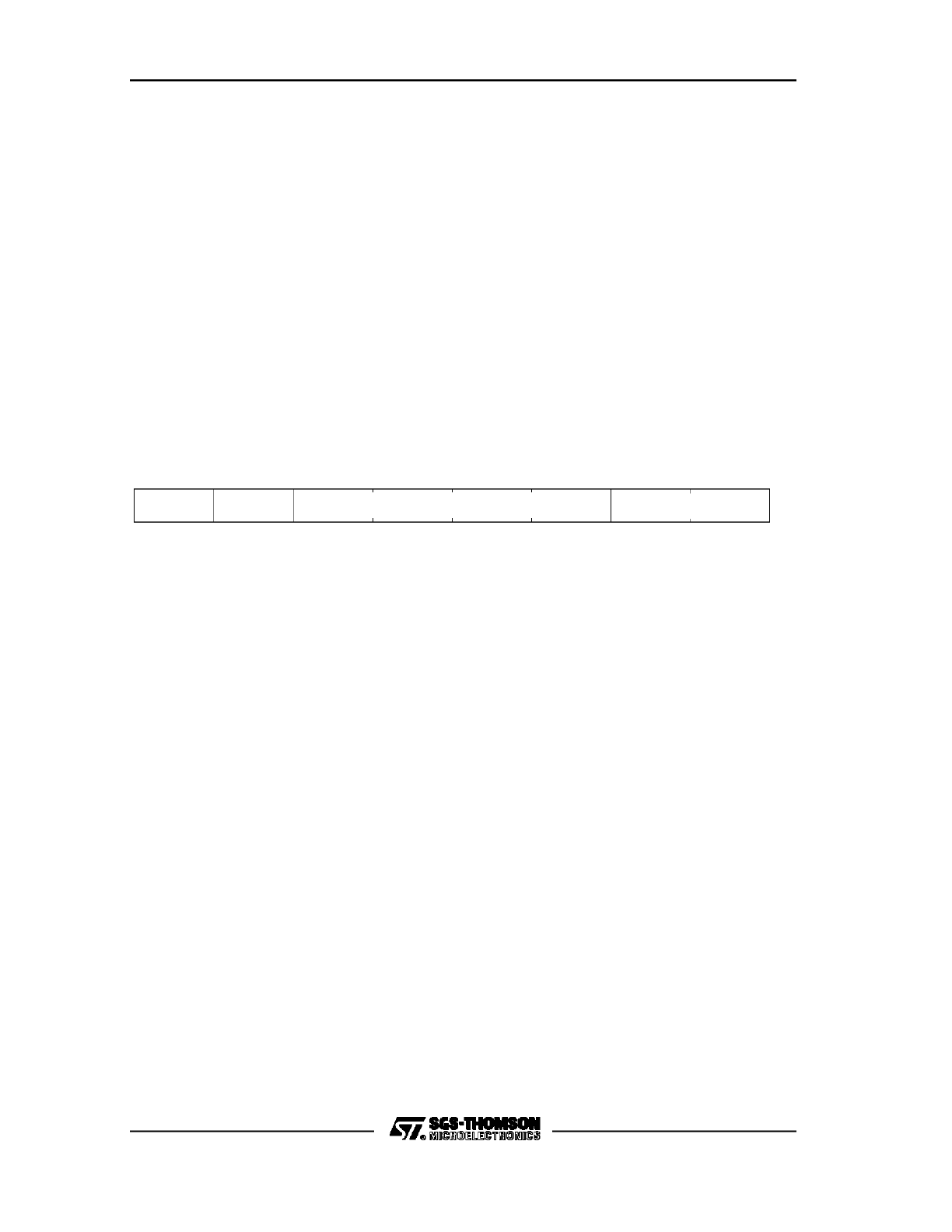

Register

Physical

Address

8-Bit

Address

Note

BUSCON0

0FF0Ch

86h

bitaddressable

BUSCON1

0FF14h

8Ah

bitaddressable

BUSCON2

0FF16h

8Bh

bitaddressable

BUSCON3

0FF18h

8Ch

bitaddressable

BUSCON4

0FF1Ah

8Dh

bitaddressable

ADDRSEL1

0FE18h

0Ch

not bitaddressable

ADDRSEL2

0FE1Ah

0Dh

not bitaddressable

ADDRSEL3

0FE1Ch

0Eh

not bitaddressable

ADDRSEL4

0FE1Eh

0Fh

not bitaddressable

Note that, due to the fact that the bus parameter bits are more often affected by

software than the other system control bits, the BUSCON0 register in the C167 is

placed on the same SFR address as the SYSCON register in the ST10x166. This

requires the least amount of changes in existing software when transferred to the

C167. The new SYSCON register in the C167 is located to a new SFR address,

FF12h / 89h.

Note: One must never program two or more ADDRSEL registers such, that the

selected address ranges overlap either entirely or partially, otherwise unexpected

results may occur. An exception to this restriction, of course, is the address range for

the BUSCON0 register. This register controls the bus for any accesses outside the

ranges defined through the ADDRSEL register. If no other BUSCONx register selects

a bus in a specific address range, the external bus in the entire address range of up

C167 FAMILY PRELIMINARY USER MANUAL

42/180

to 16 MByte is controlled by the BUSCON0 register. Thus, programming another

BUSCON to a certain address range always overlaps the BUSCON0 address range,

however, this is an intended, implemented operation, and no problems will occur in

this case. It can be regarded in this way, that the BUSCON1..4 and ADDRSEL1..4

registers have the same level of priority among them (thus it is not possible to

determine the preference in an address overlap case), while BUSCON0 has a lower

priority. It is possible, however, to overlap an ADDRSEL address range with an

internal (ROM, RAM, SFR, ESFR, etc.) address range. In this case, accesses to

addresses in the overlapping regions are always made to the internal space.

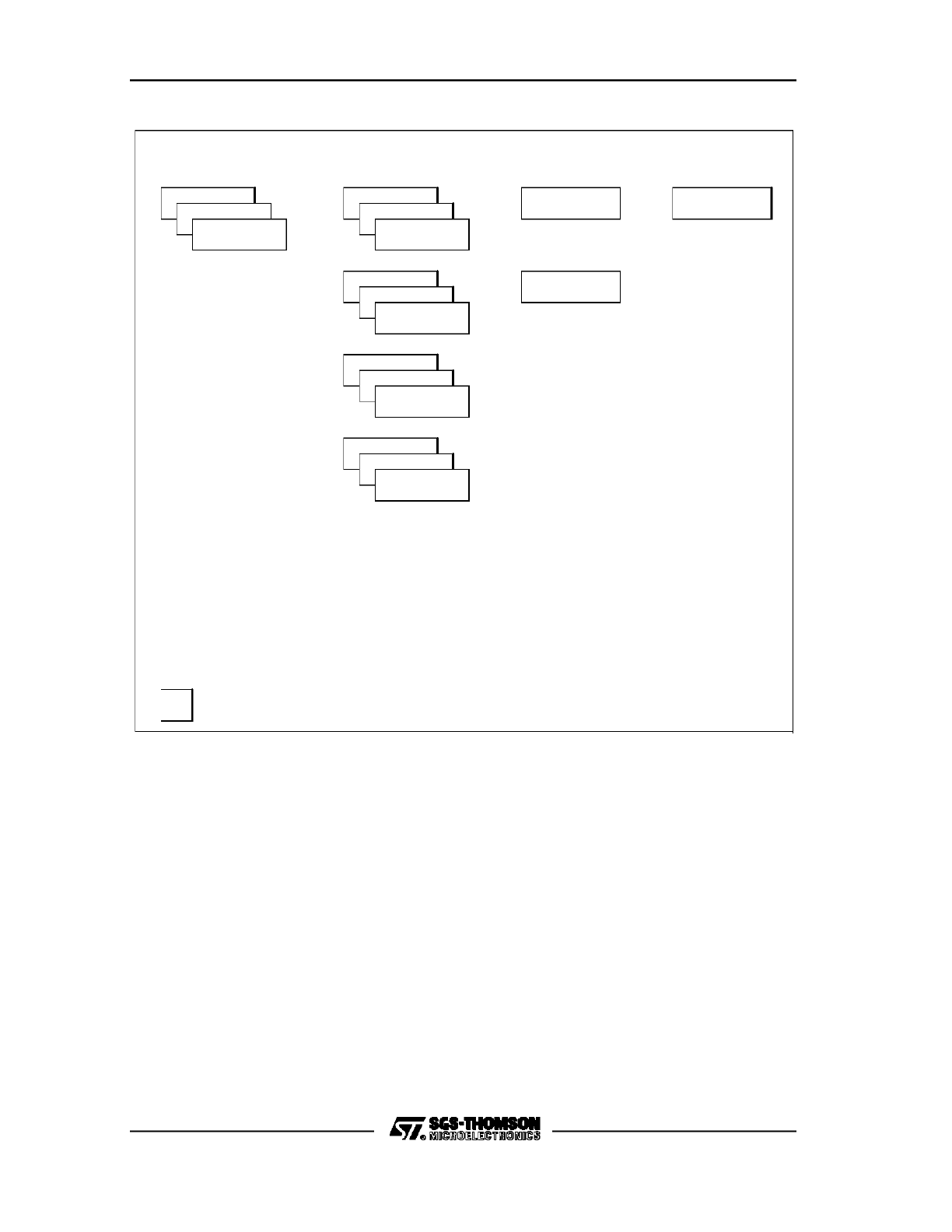

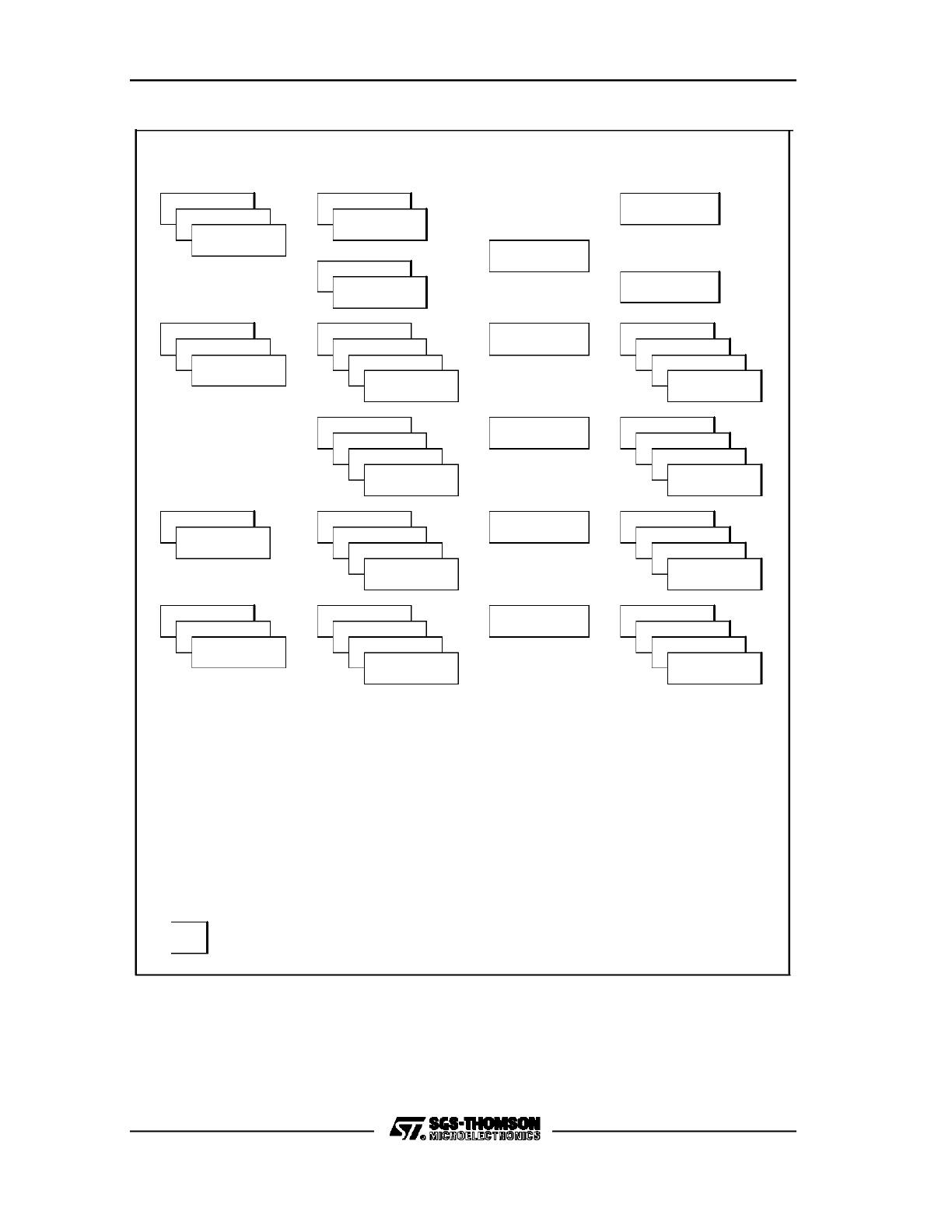

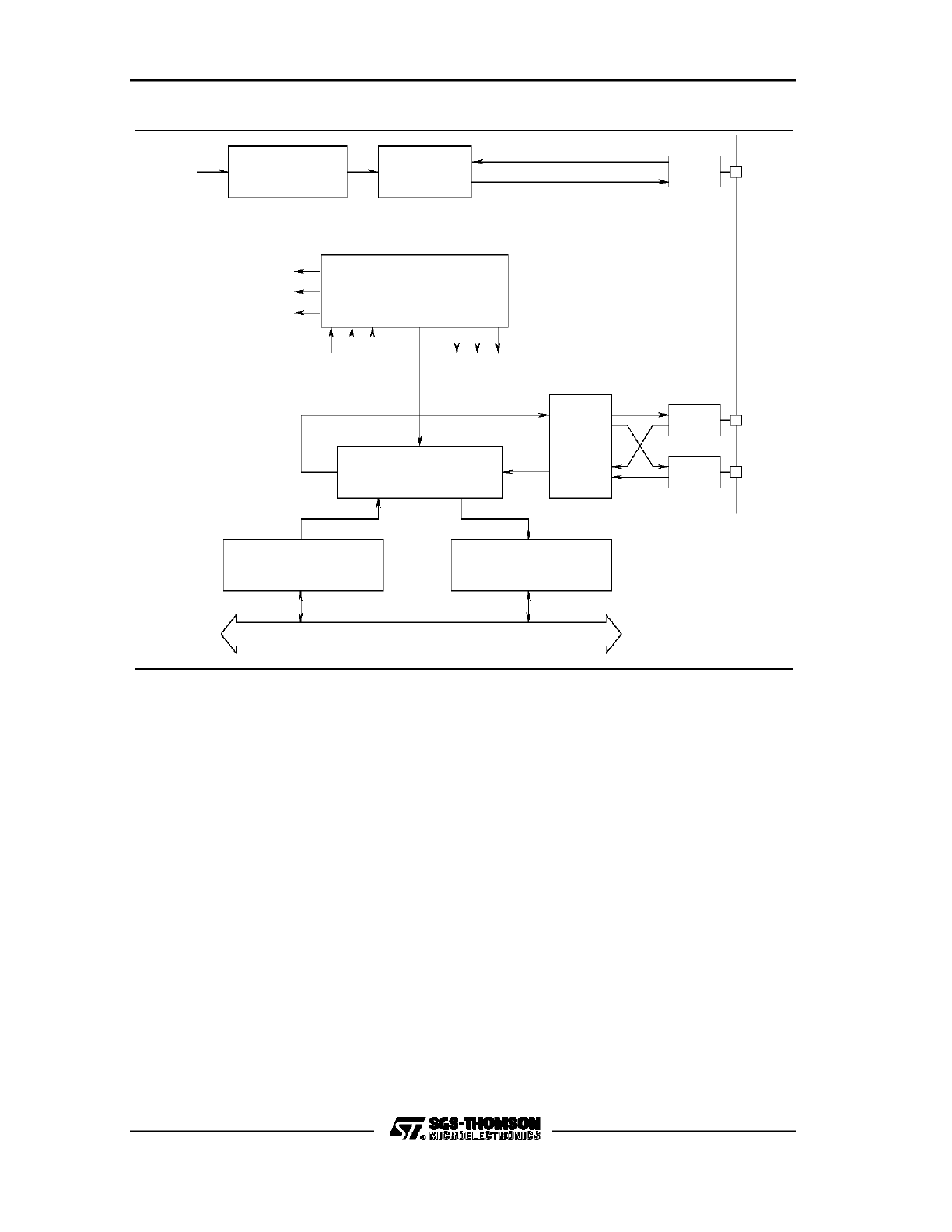

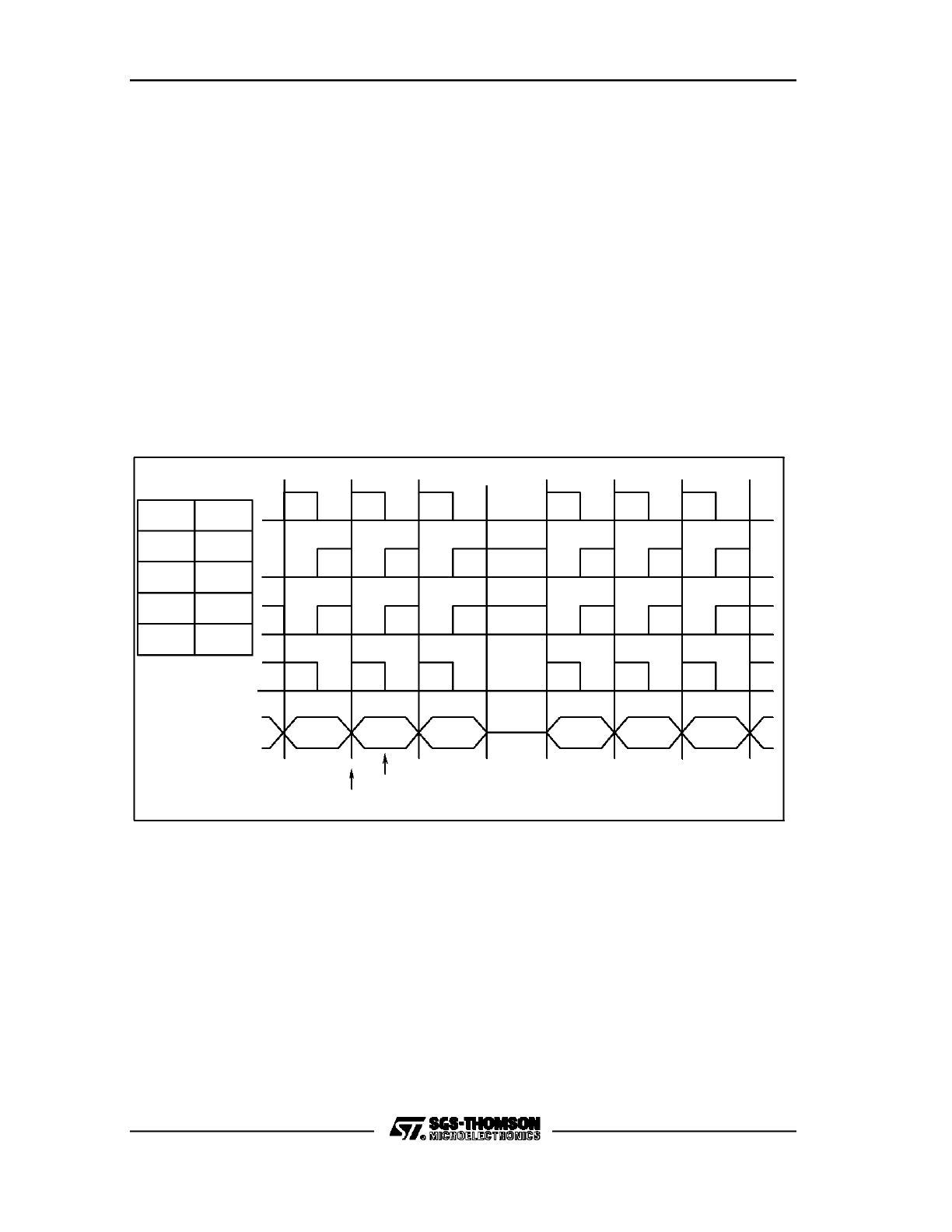

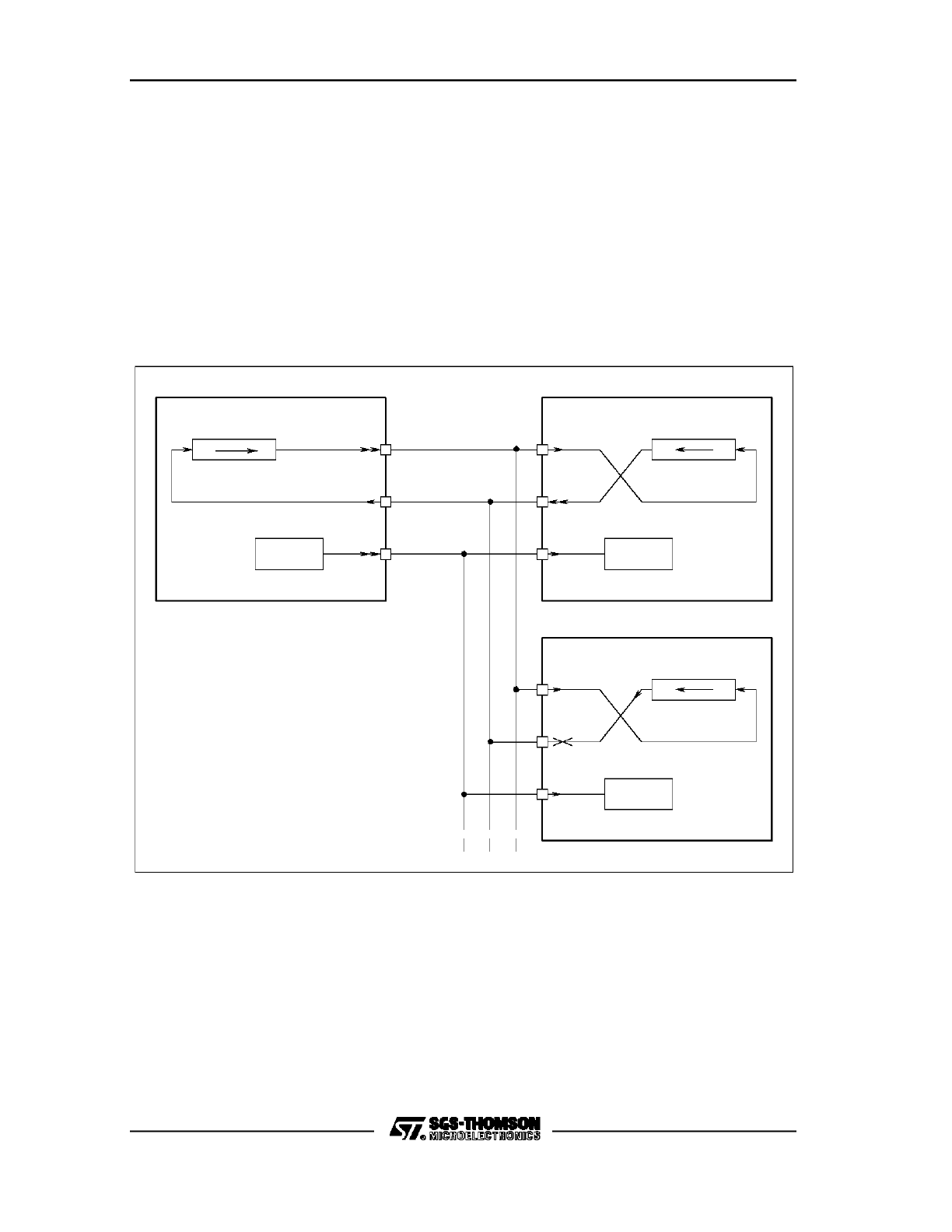

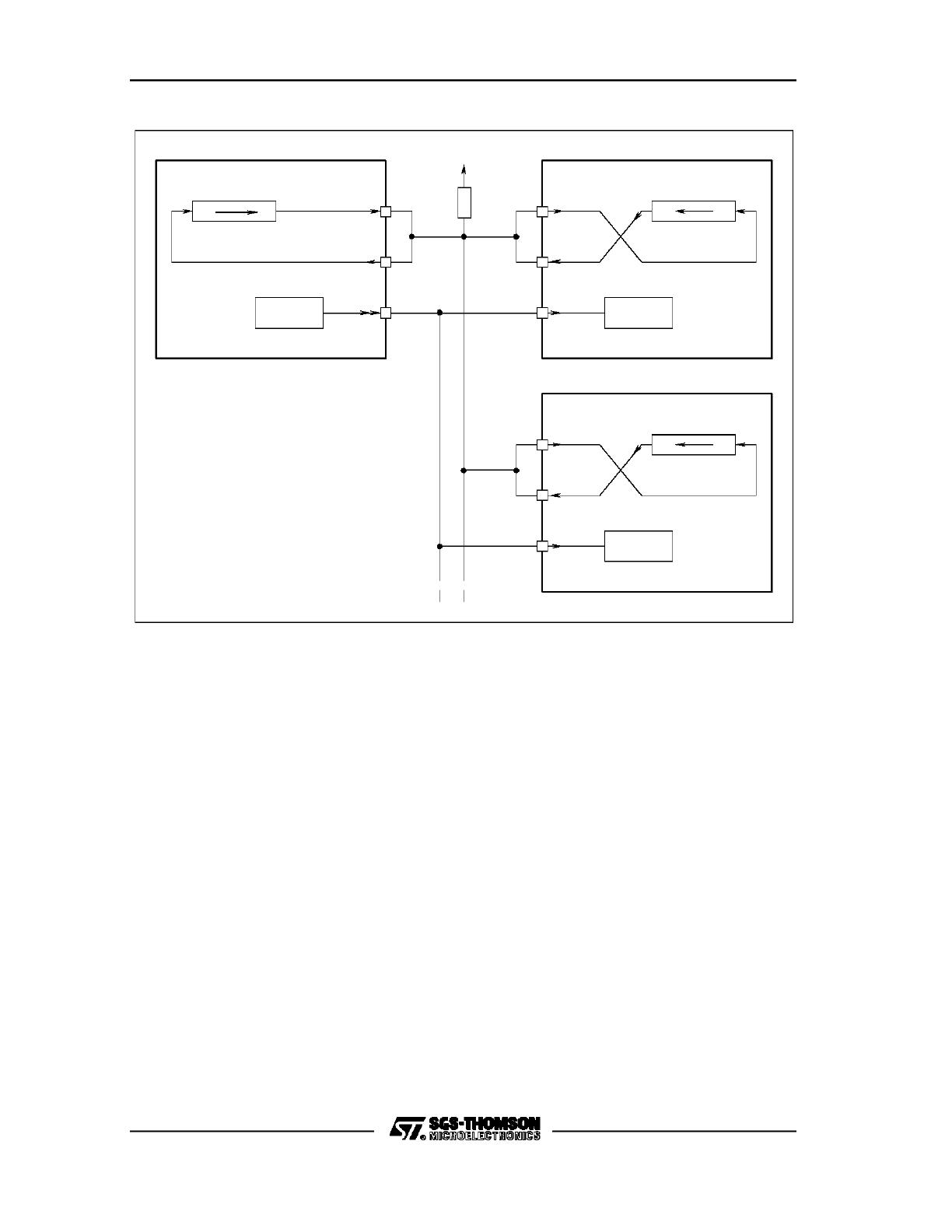

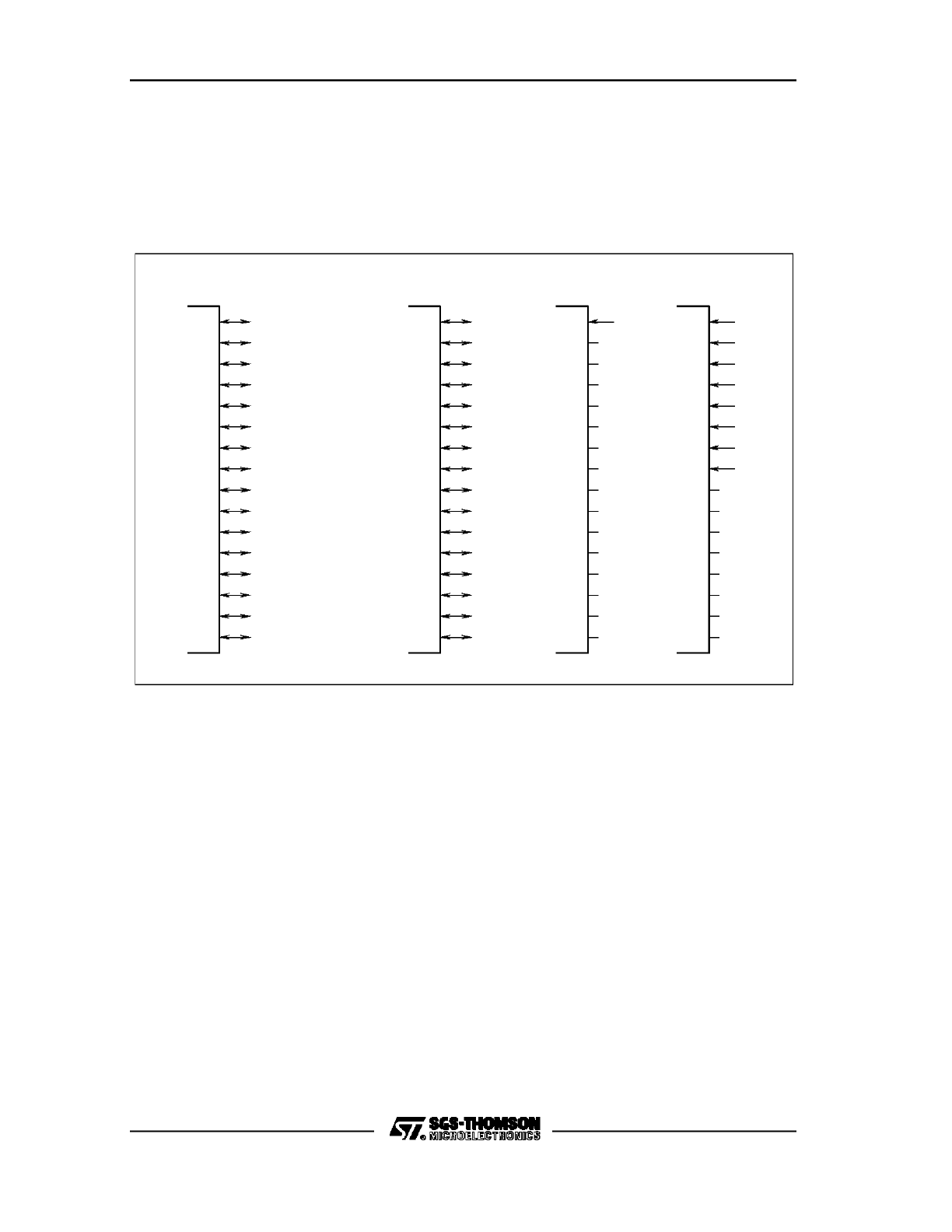

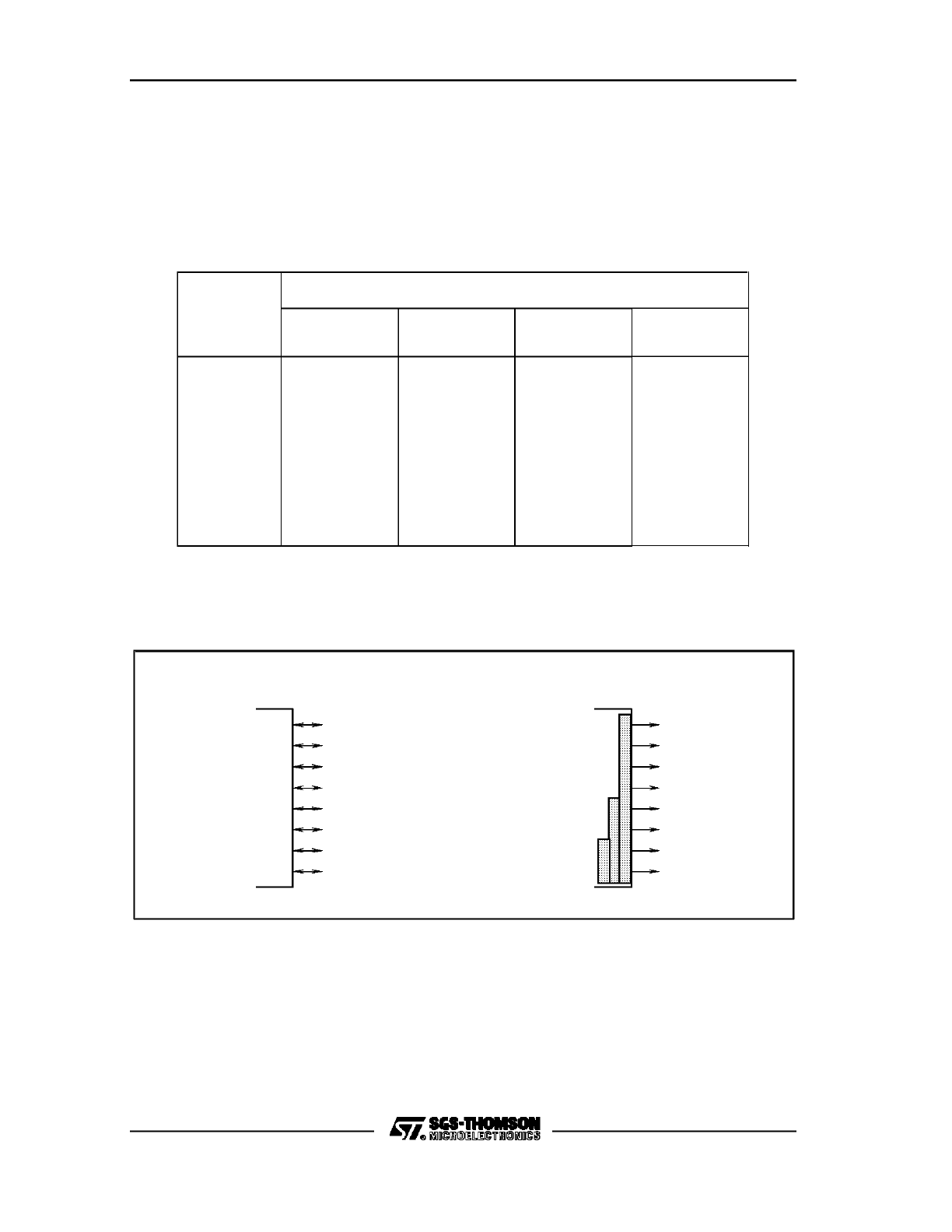

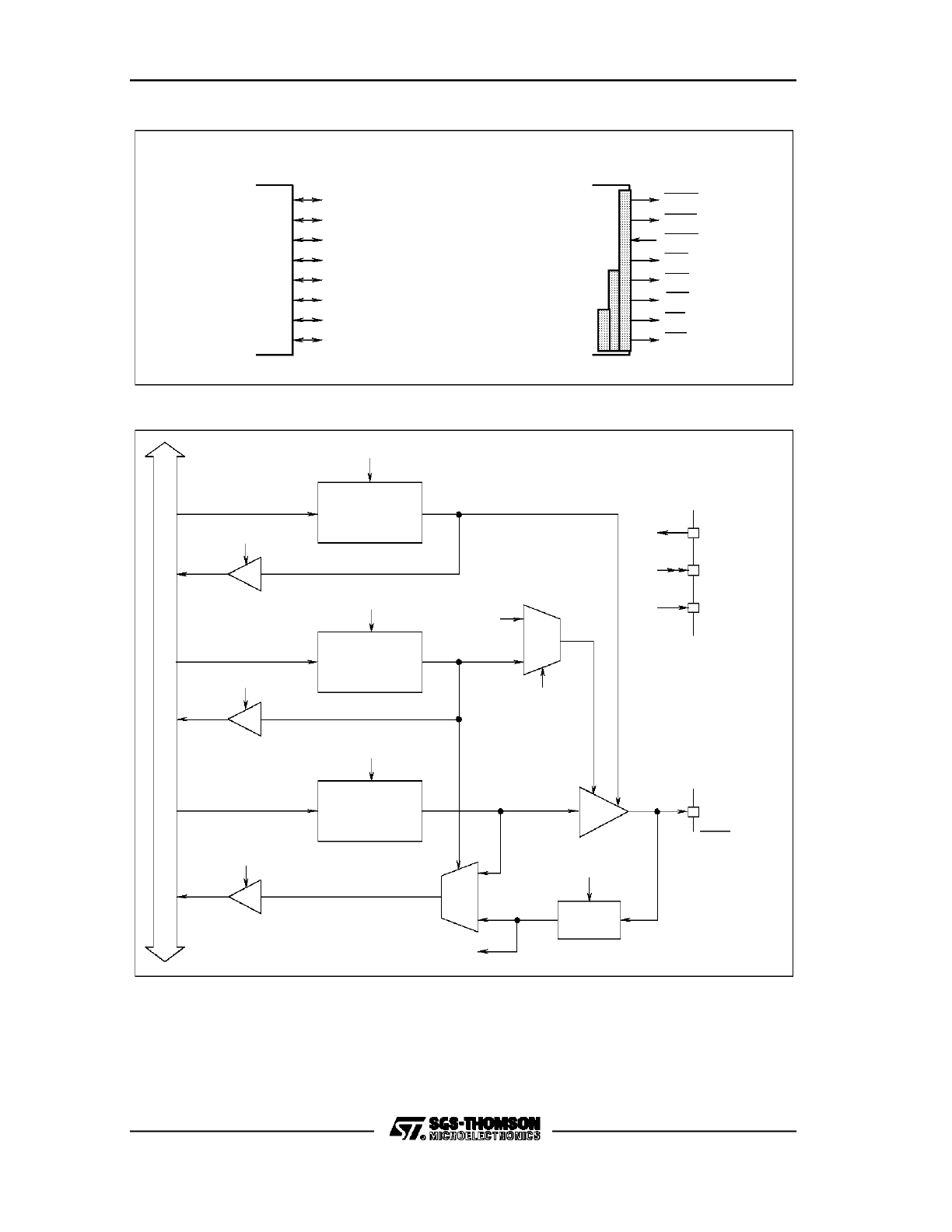

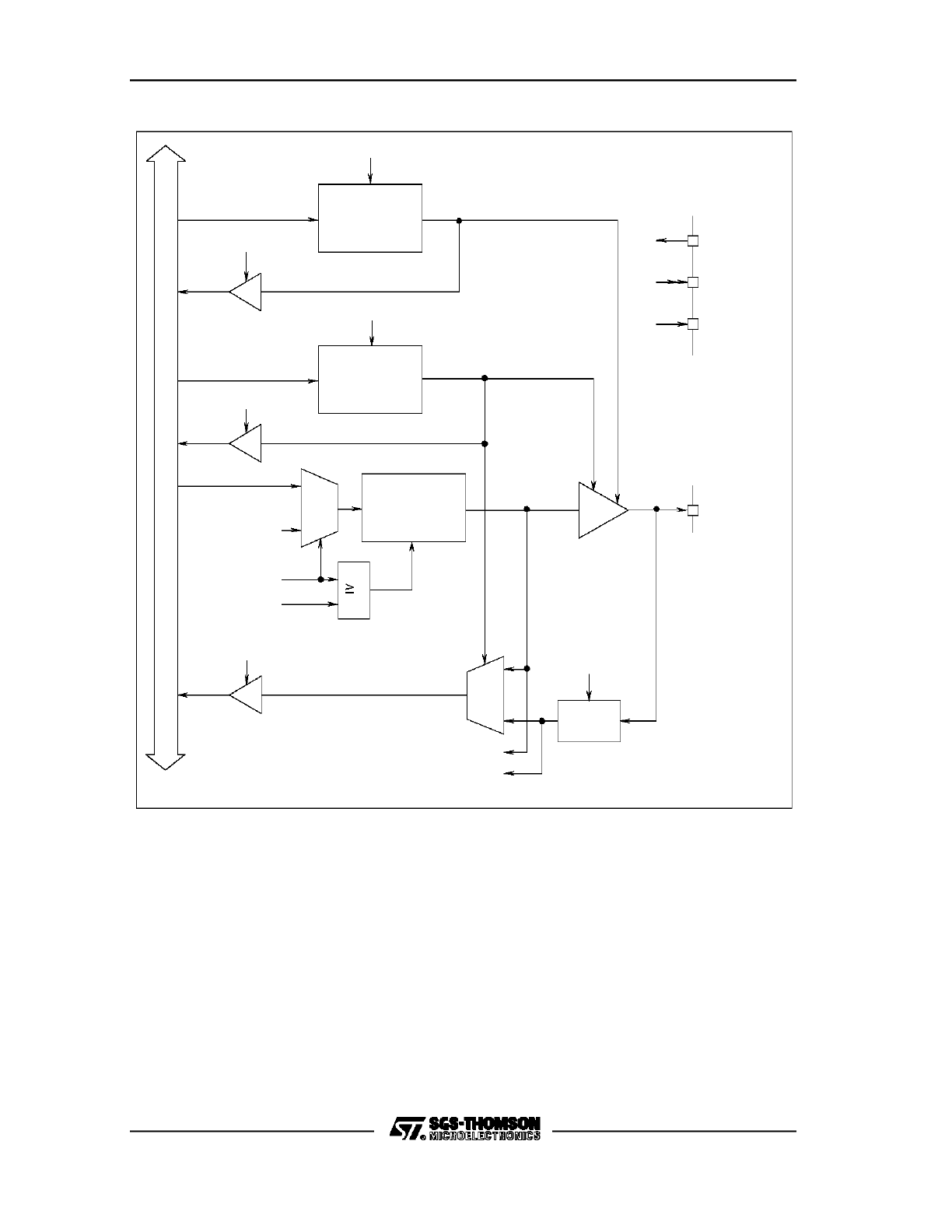

Figure 7. BUSCON Configuration Examples

BUSCON0, CS0

16M

12M

8M

4M

1M

0K

BUSCON2

BUSCON0,CS0

(Range 4K, Start 0K) CS0

0K

4K

8K

16K

32K

VR001898

Non-Segmented Mode

Segment Mode

4K, CS2

BUSCON4

4MByte

CS4

CS1

4MByte

BUSCON1

BUSCON3

4MByte

CS3

BUSCON0

48K

64K

BUSCON1

BUSCON2

BUSCON0

BUSCON3

BUSCON4

(Range 8K, Start 16K) CS0

Range 8K

Start 24K, CS3

Start 8K, CS2

Range 8K

Range 4K

Start 4K, CS1

Start 32K, CS4

Range 32K

Example

Example

C167 FAMILY PRELIMINARY USER MANUAL

43/180

3.3

Chip Selects

In order to save external glue logic mostly required for the generation of separate

chip select signals for external devices such as memories or peripherals, on-chip

automatic chip select signal generation is implemented in the C167. For this purpose,

each BUSCON register (also the new BUSCON0 register) is designated a port line

(see Chapter 11), which provides a chip select signal as an alternate function. When

a chip select output is enabled for a BUSCONx register (see Chapter 3.5 for

enabling/disabling chip selects), the associated output pin will go to a low level each

time an external access to an address in the specified range for this BUSCONx

register is performed. The pin returns to a high level for any access outside of the

specified range and for internal accesses.

Each BUSCONx register is assigned a chip select line CSx#. Chip selects

CS1#..CS4# will go active (if enabled) when an external access within the address

range specified through the associated ADDRSELx register is performed. Chip select

line CS0#, which is associated to the BUSCON0 register, will go active (if enabled)

for

any

external

access

outside

the

ranges

specified

through

registers

ADDRSEL1..4.

For chip selects CS1#..CS4#, two different options exist, selectable through bits 15,

CSWENx, and 14, CSRENx, of the respective BUSCON1..4 registers. This is

illustrated in the following table (see also Figures 8 and 9). These options are

described in detail in the next sections. Note that for the BUSCON0 chip select line

CS0#, these options are not available. The reason is that if CS0# is enabled during

reset (see Chapter 3.5), it must go active directly after reset to enable fetching of the

first instructions. There is no way to additionally select whether CS0# should operate

as address or read/write chip select directly after reset. Furthermore, since

BUSCON0 and CS0# are nearly in all cases used to access code memory, such a

chip select option is not useful.

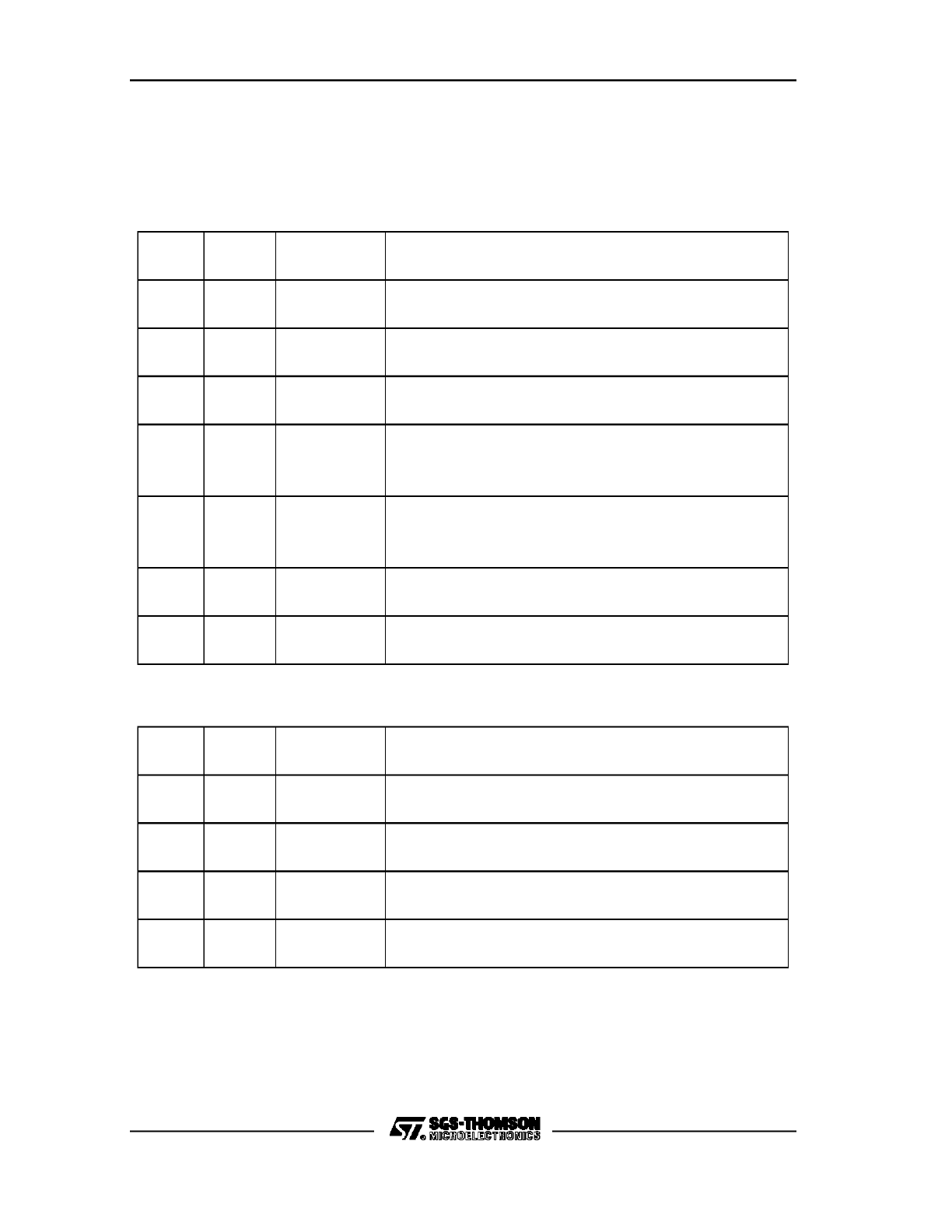

CSWENx

CSRENx

Chip Select Operation (Chip Selects CS1#..CS4#)

0

0

Address Chip Select

0

1

Read Chip Select

1

0

Write Chip Select

1

1

Read/Write Chip Select

Note that the chip selects, whether Address or Read/Write Chip Selects, will not be

generated for internal accesses, even if the access is to an address within the range

specified through an ADDRSEL register.

C167 FAMILY PRELIMINARY USER MANUAL

44/180

In order to avoid undefined levels of pins used as chip select lines, internal pullup

devices of about 50 KOhm are implemented at these pins. This pullups are switched

on during reset (either hardware, software, or watchdog timer reset), such that these

lines are held at a high level. After the reset sequence has been finished, the pullup

devices are switched off. The lines selected for chip select operation are then be

automatically switched to the output mode and drive the appropriate level. The pins

not configured for chip select operation will return to the high-impedance state.

When an HOLD# is requested by an external device, then besides switching the

address and data bus to the high impedance mode, the C167 also turns the chip

select signals off when generating the acknowledge signal HLDA#. This enables the

external master to not only control the address and data bus, but to also use the

same chip select lines to access the individual external devices connected to the

bus. The chip selects can be turned off in such a case in two ways, controlled

through the respective Open Drain Control register (see section 11.6) for the port: If

the respective control bit ODPx.y is ’0’, the chip select line will be held high through

switching on the internal pullup device at this pin. If ODPx.y = 1, this pullup device will

not be activated, the pin will float to the high-impedance state. Either an external

pullup device has to be connected in this case or the external master is capable of

pulling the lines to an appropriate level.

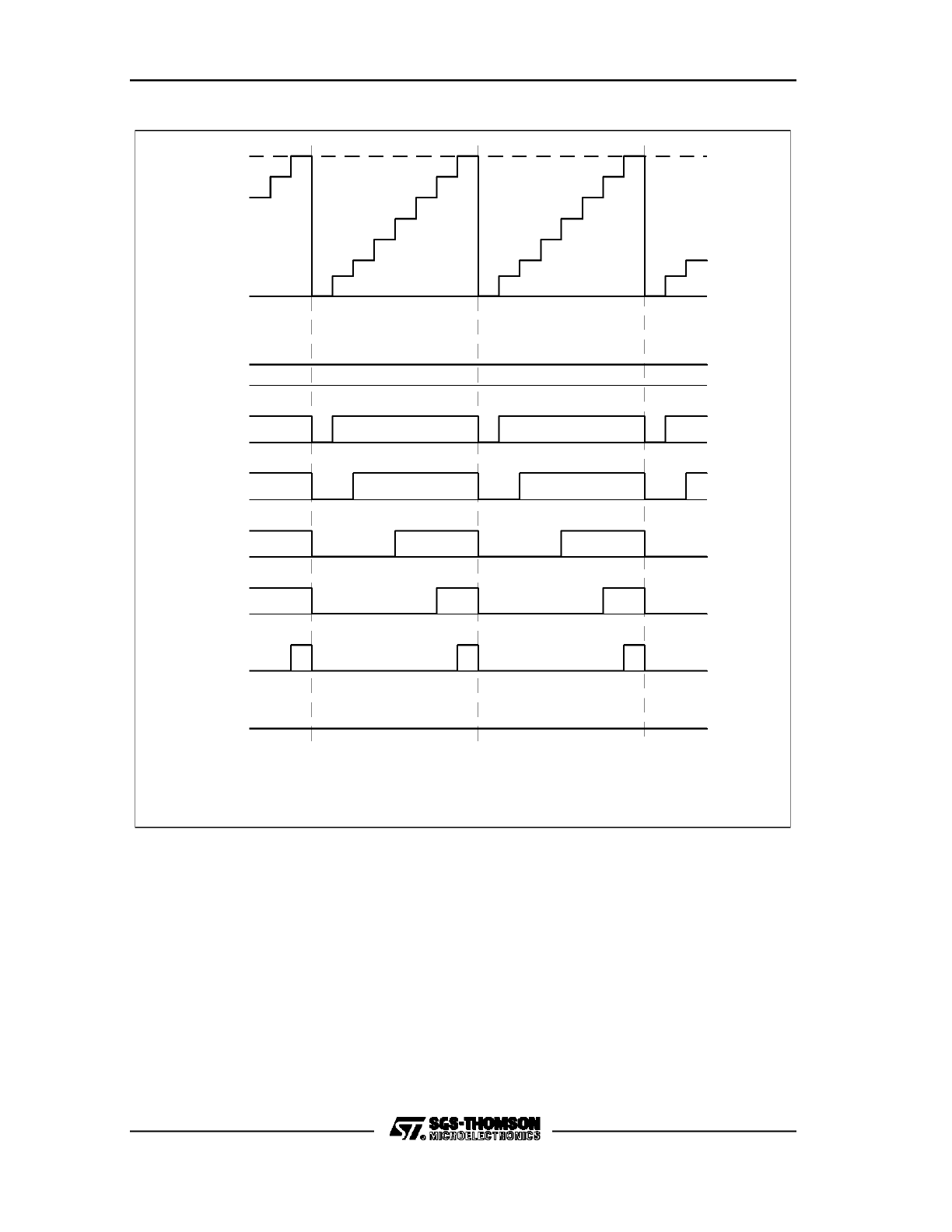

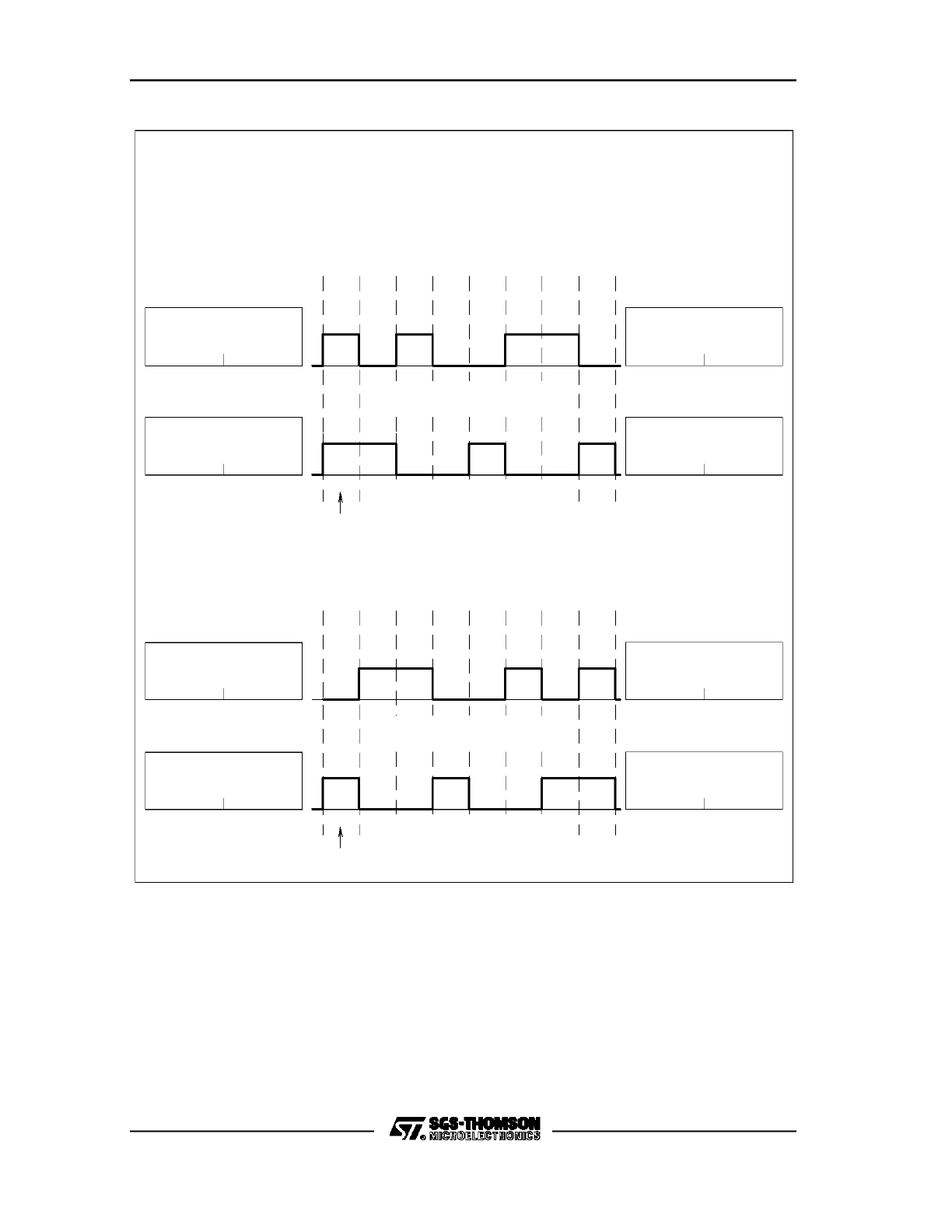

3.3.1 Address Chip Selects

A chip select, which is generated by decoding the address lines, and which is

activated for the whole duration of an external bus cycle, is named an Address Chip

Select in the context of this paper. This is done to distinguish it from the Read/Write

Chip Selects described in the next section.

The activation of an Address Chip Select is selected with CSWENx = CSRENx = 0

(default after reset) in the BUSCON registers (Note that for CS0#, this is the only

option; the respective bits in BUSCON0 are reserved). When an access within the

address range specified by the associated ADDRSEL register is performed, the

respective chip select line CSx# (x= 0..4) will go to a low level with the falling edge of

ALE, and remain at this level until an access outside of this range is made. It will then

be deactivated again with the falling edge of ALE of the bus cycle accessing the new

range. No spurious spikes will be generated on the chip select lines. Figure 8 shows

the timing of the address chip select signals.

C167 FAMILY PRELIMINARY USER MANUAL

45/180

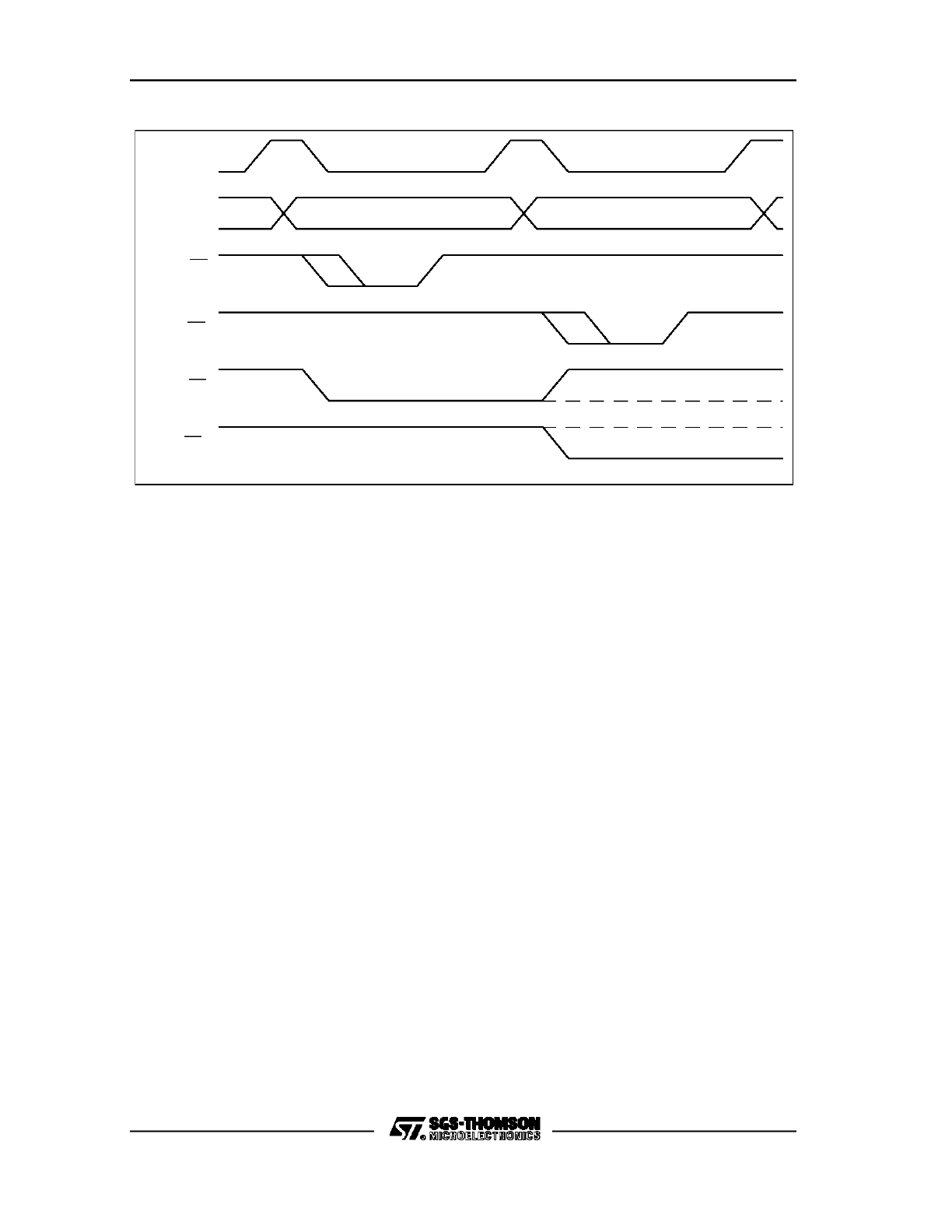

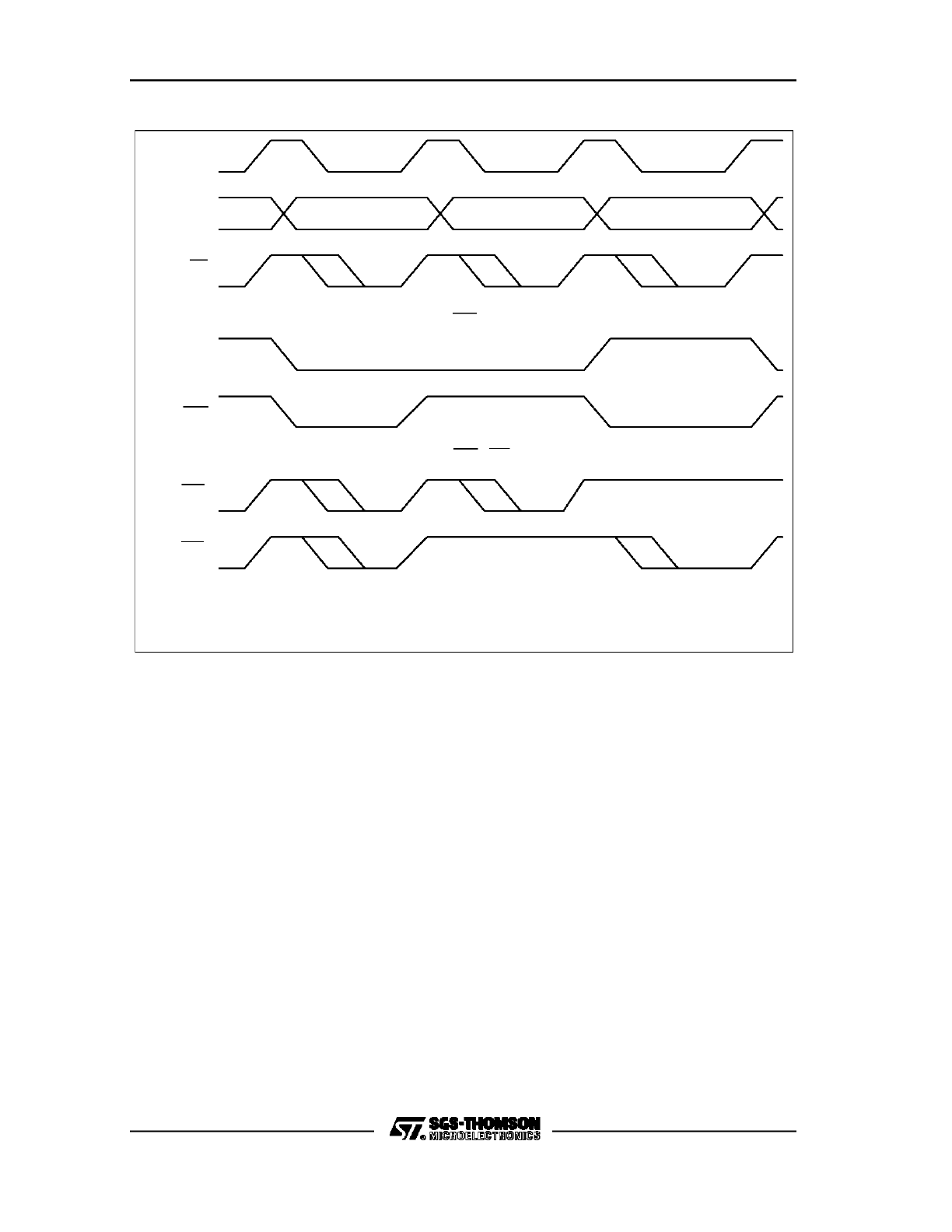

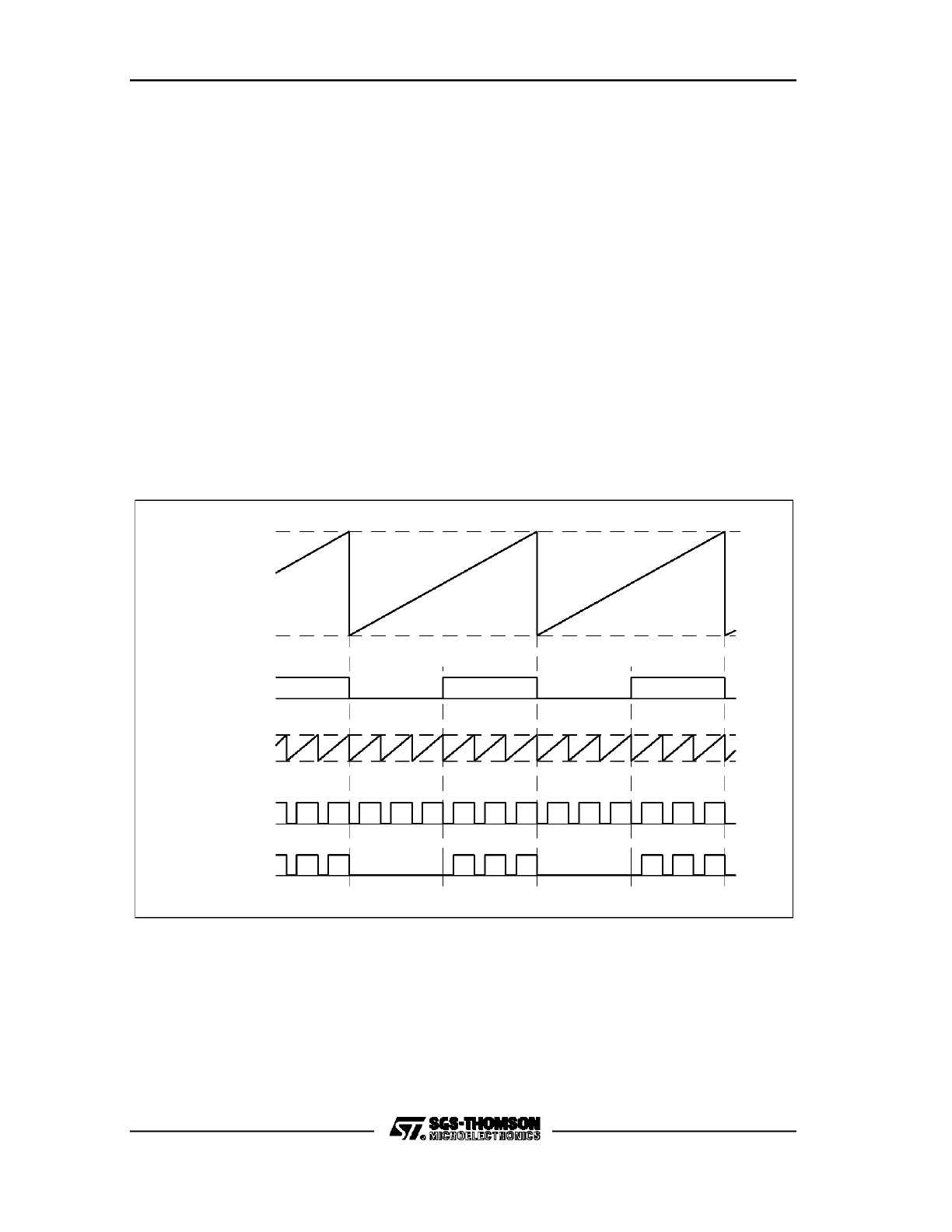

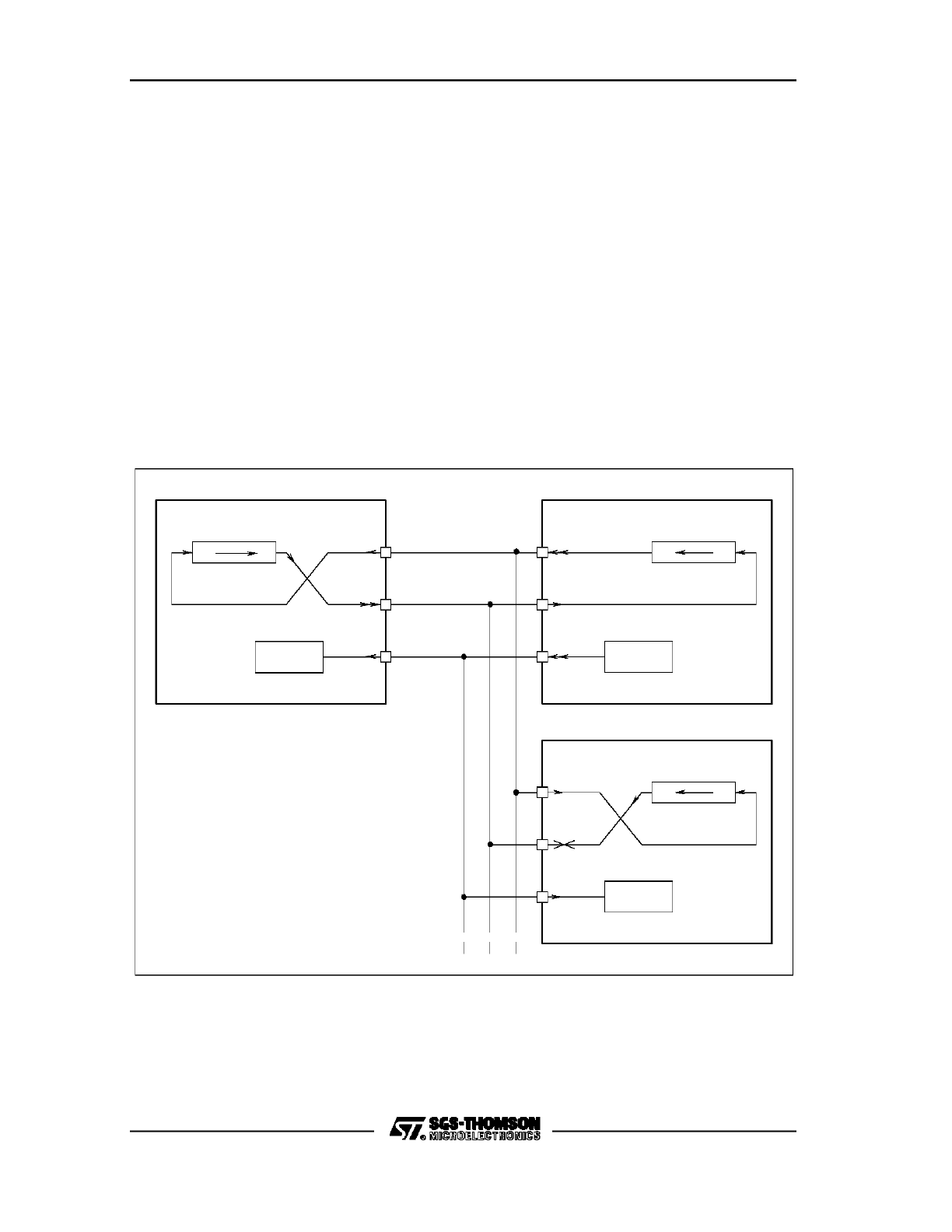

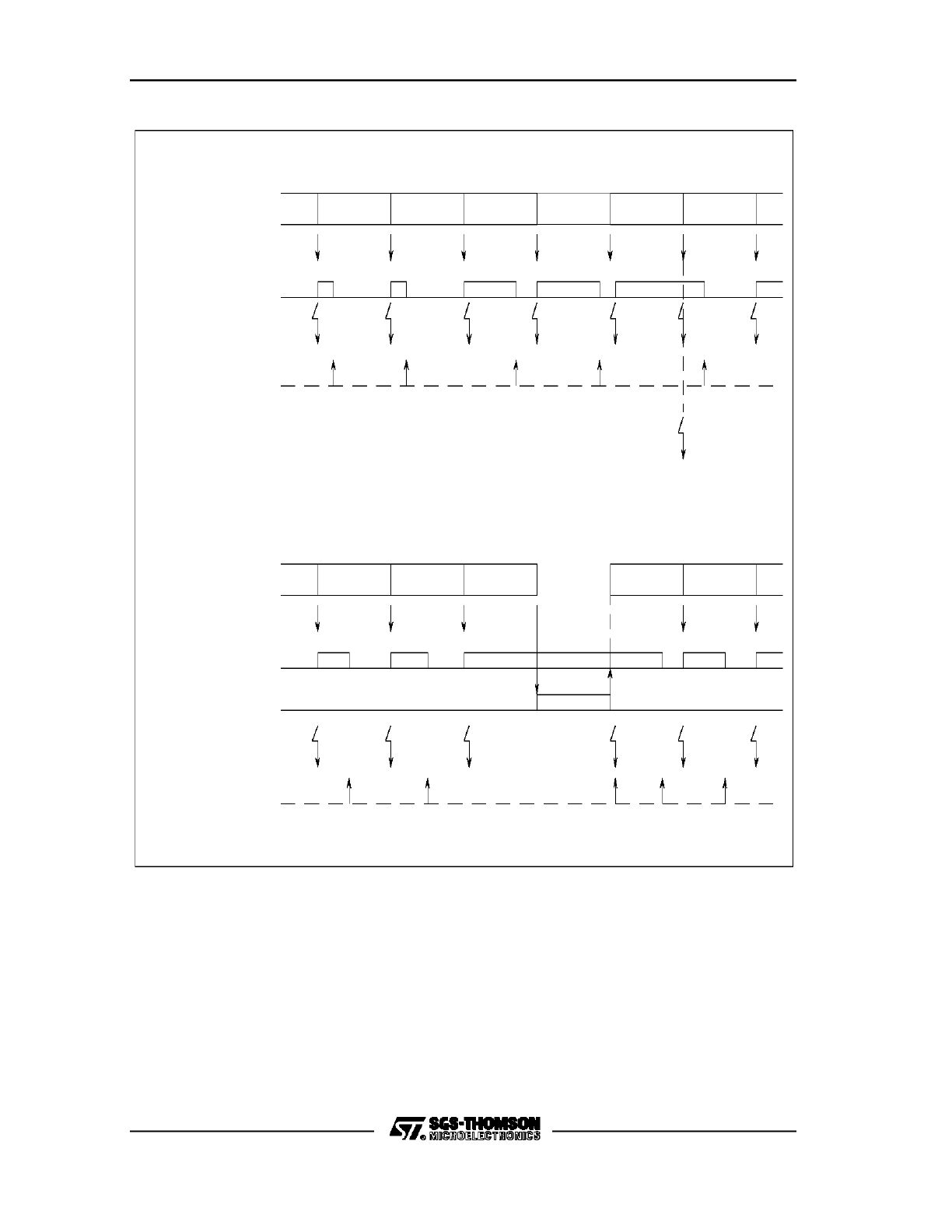

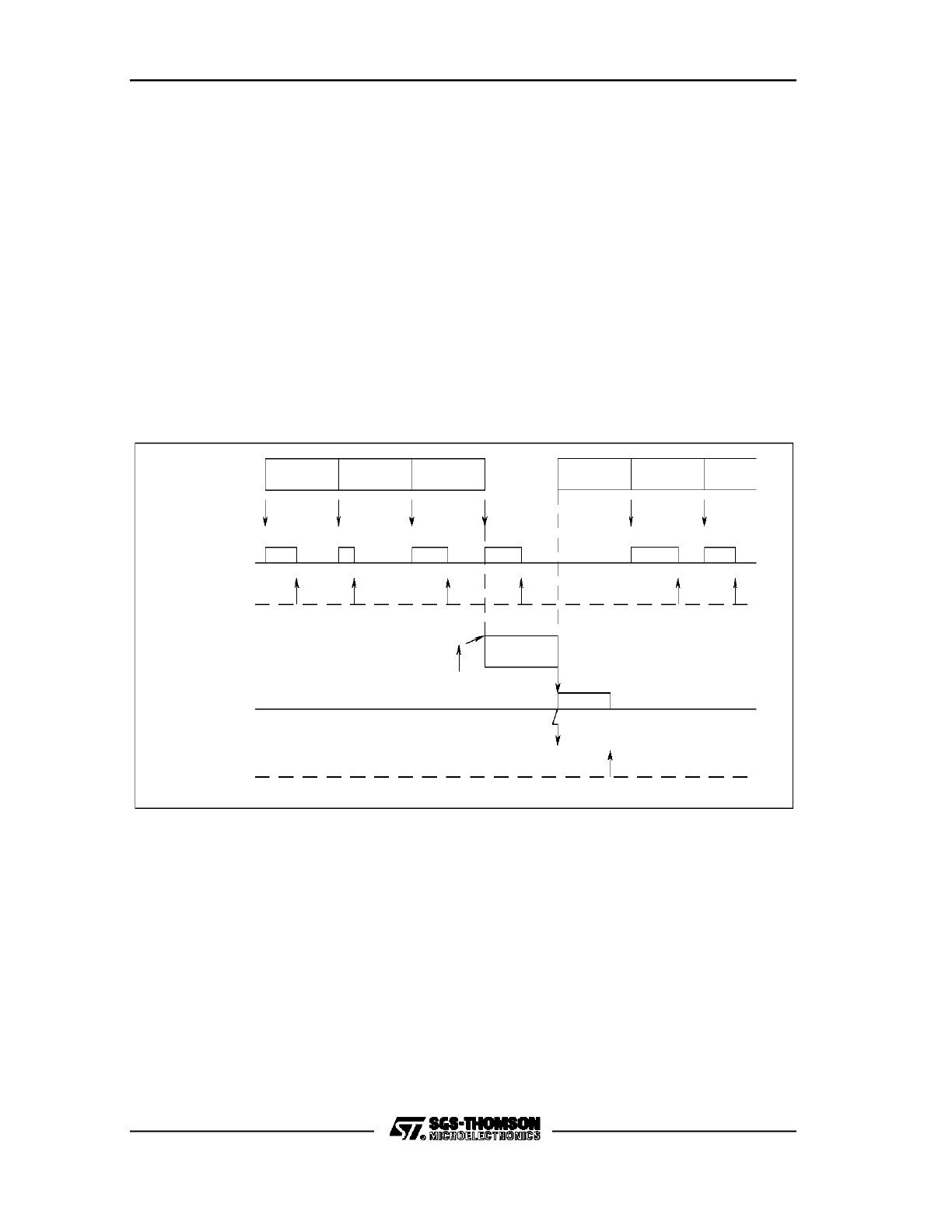

Figure 8. Address Chip Select Operation (MUX-Bus Example)

VR001894

ALE

CSy

ADDRESS

BUS

RD

WR

CSx

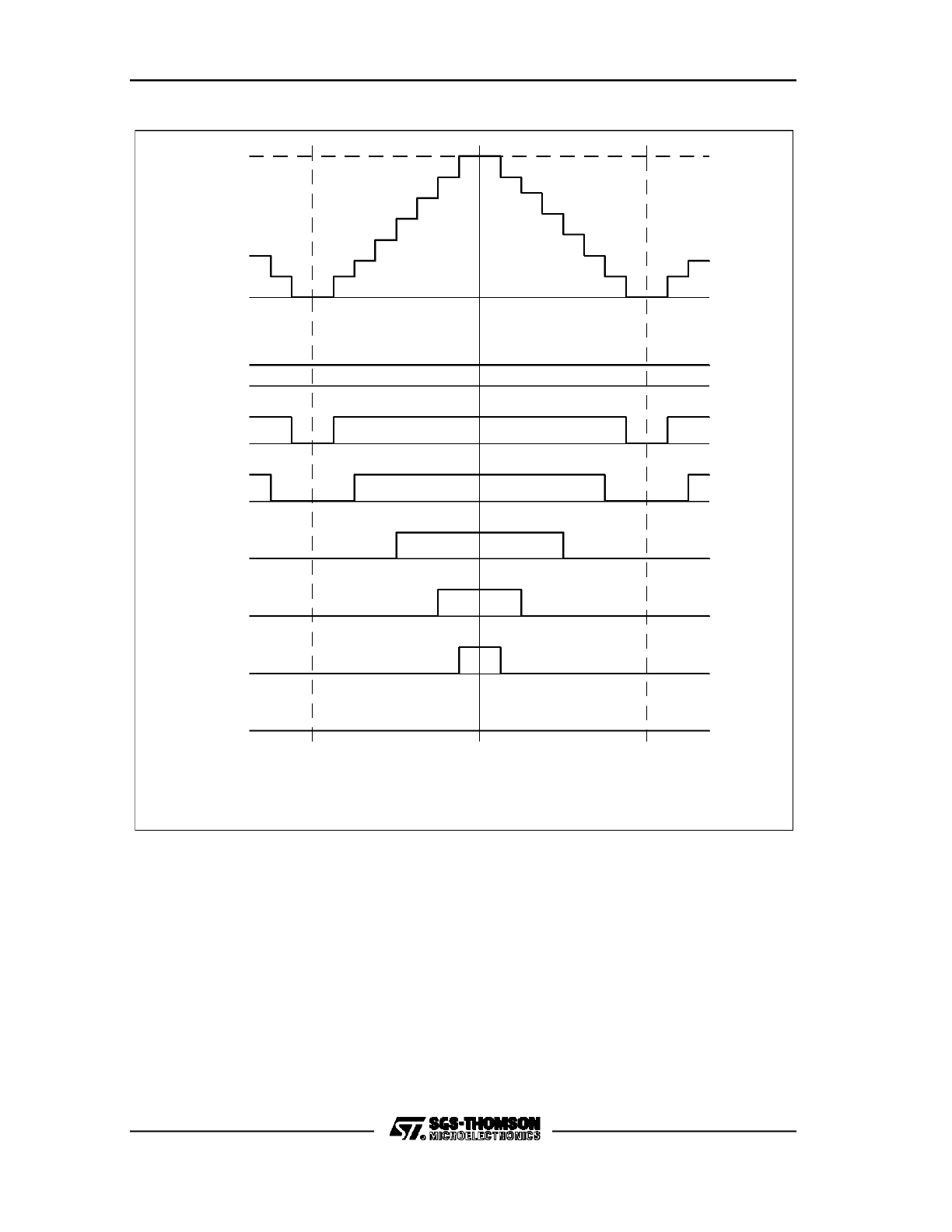

3.3.2 Read/Write Chip Selects

For accessing external devices such as latches or direction drivers, which often only

have one enable input, another chip select option is implemented. This option allows

to internally gate the chip select signal derived from the addresses with the read or

write signal. This means, for example, that a write chip select signal will only be

generated when writing to a specific address range, not for a read access to this

range, and that it has the same timing characteristics as the write signal. Figure 9

shows the timing for these read/write chip select signals. There are three selectable

options. The chip select can be generated either only for read accesses (CSRENx =

1, Read Chip Select), or only for write accesses (CSWENx = 1, Write Chip Select), or

for both, read and write accesses (CSRENx & CSWENx = 1, Read/Write Chip

Select). This feature saves external glue logic when accessing devices with only one

enable input. Figure 10 shows two examples for this.

C167 FAMILY PRELIMINARY USER MANUAL

46/180

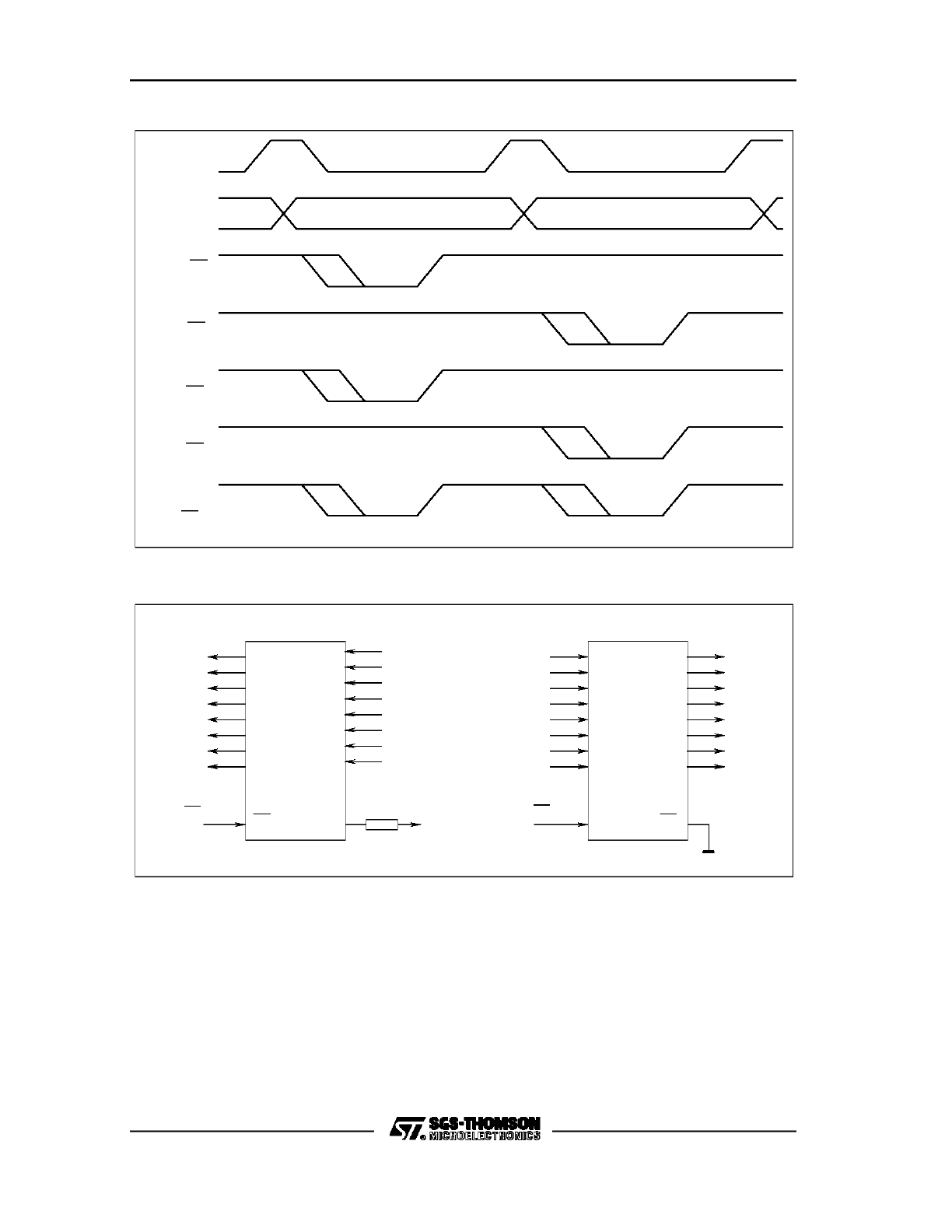

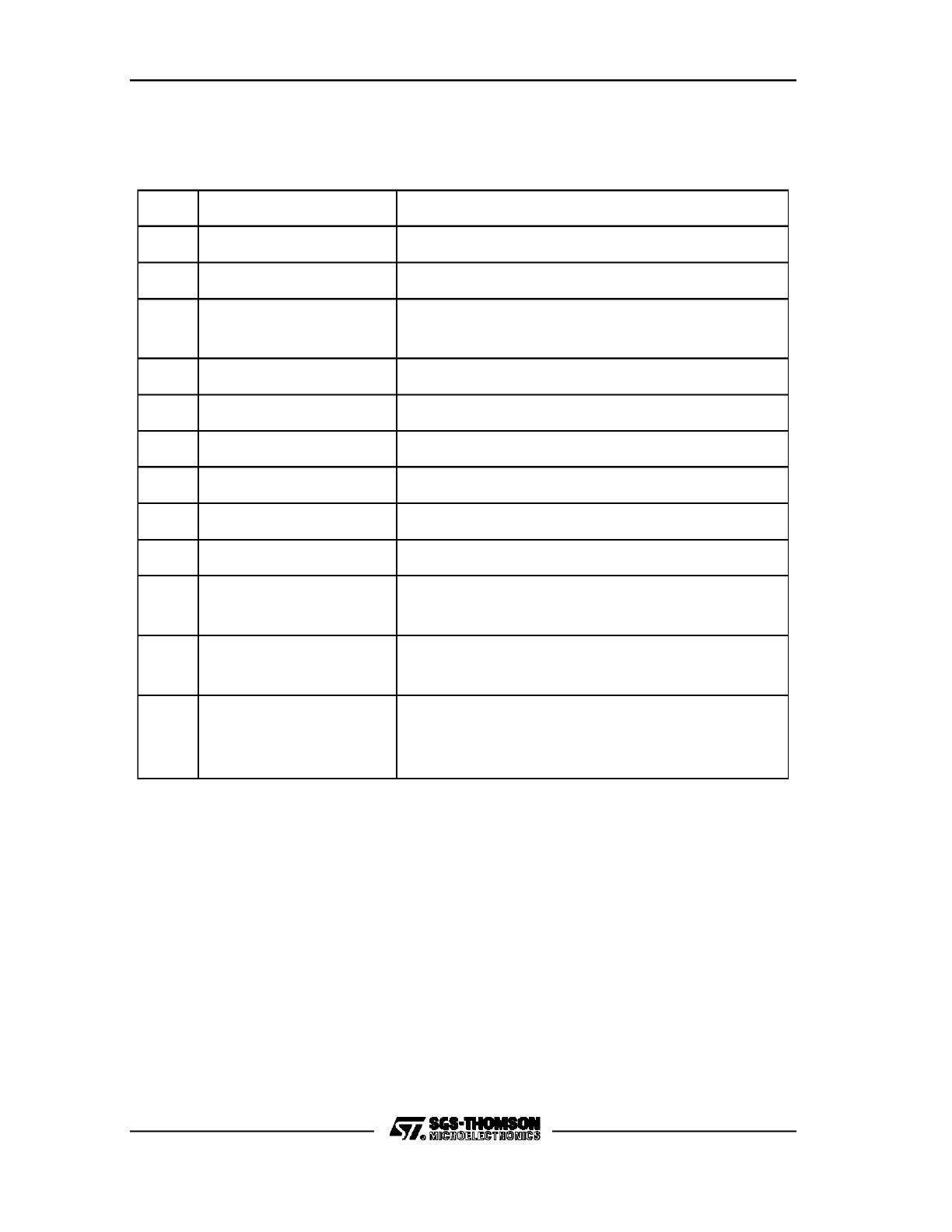

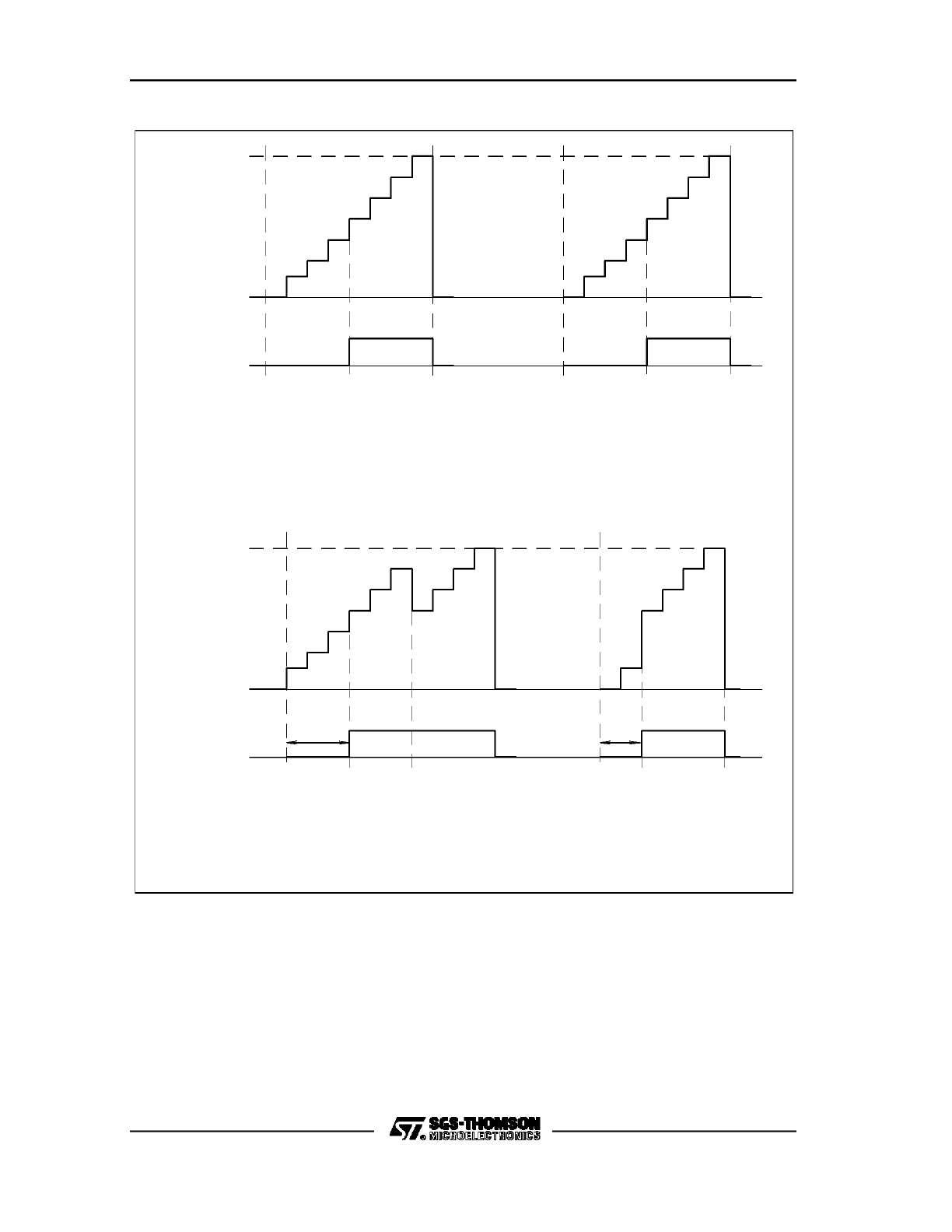

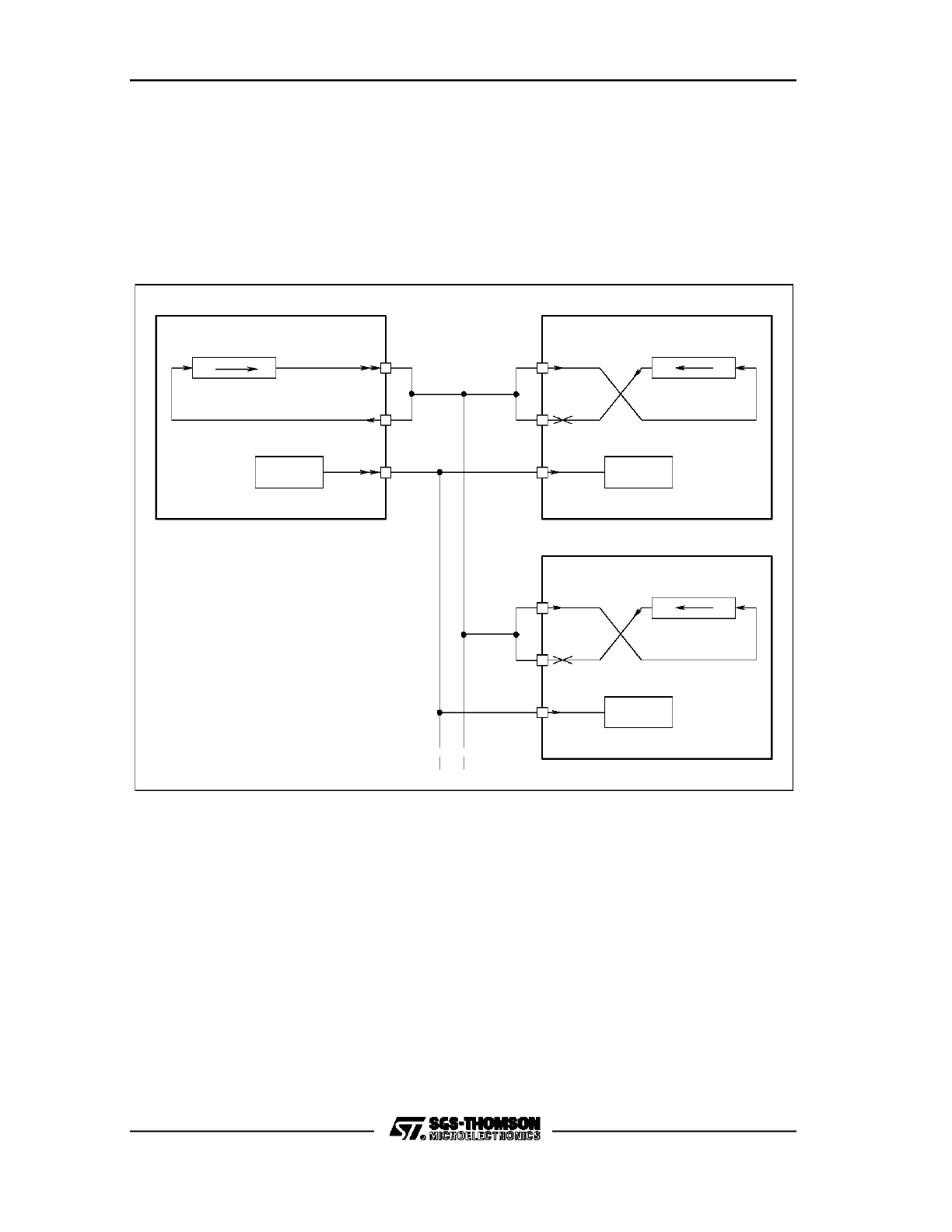

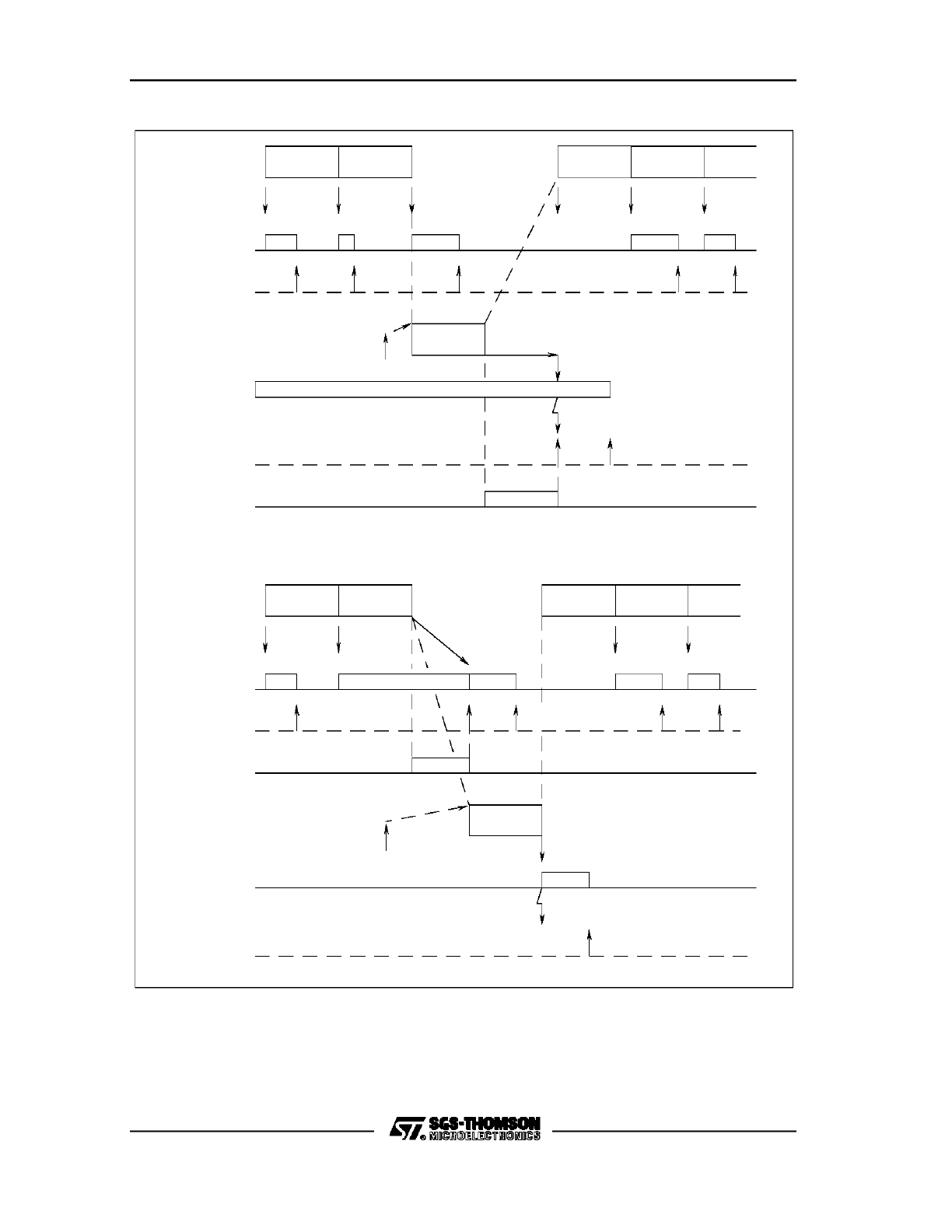

Figure 9. Read / Write Chip Select Operation (MUX-Bus Example)

VR0A1894

ALE

ADDRESS

BUS

RD

WR

CSx

READ

WRITE

CSx

CSx

WRITE

READ/

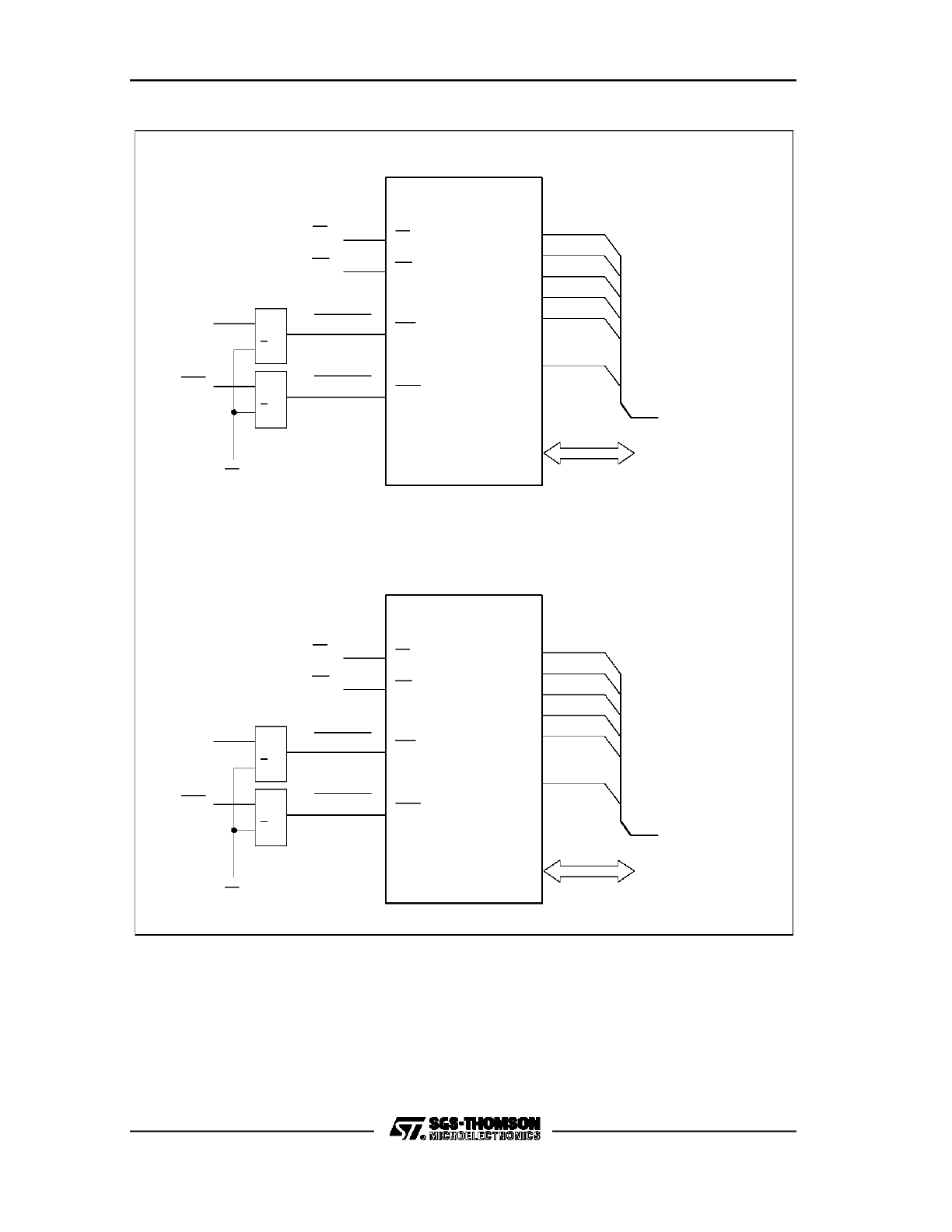

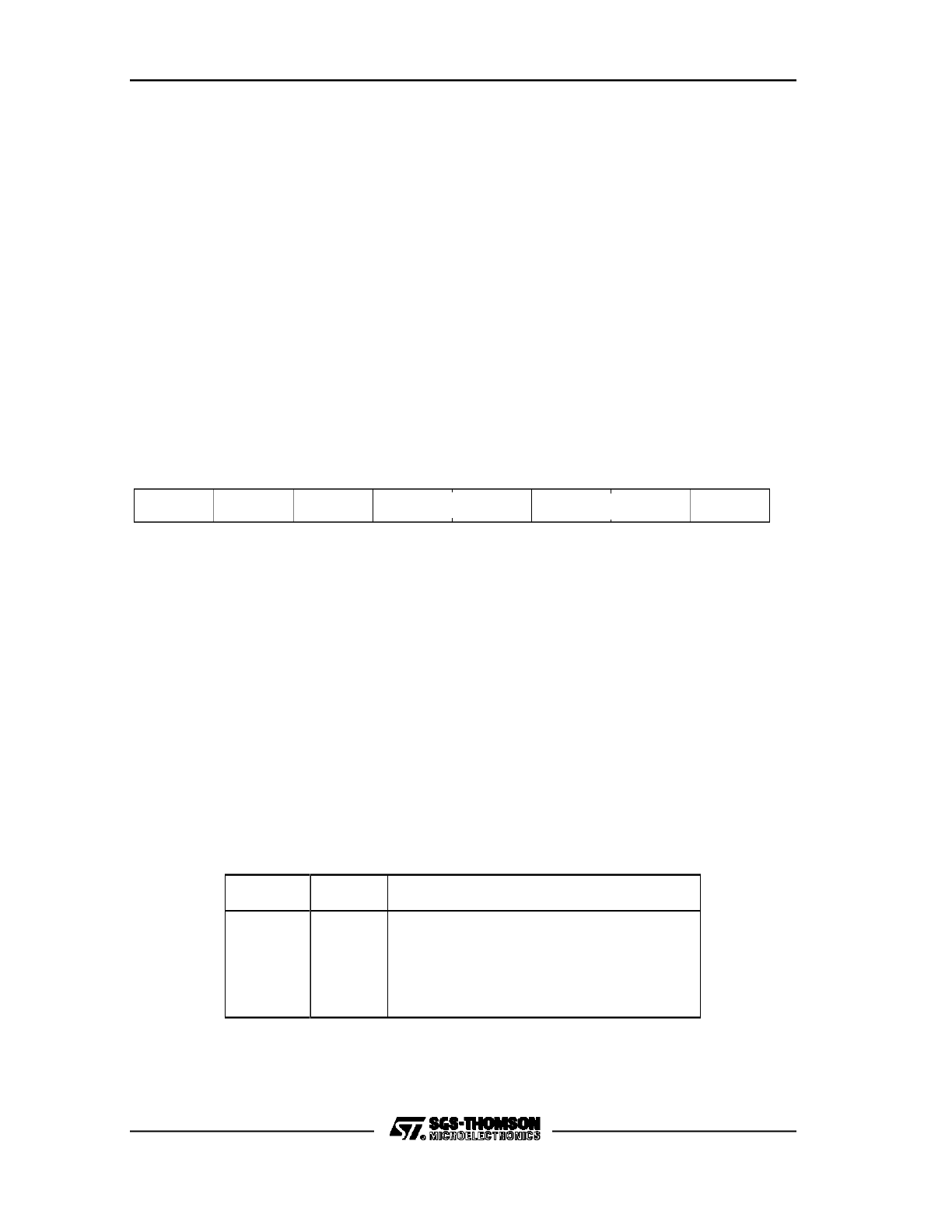

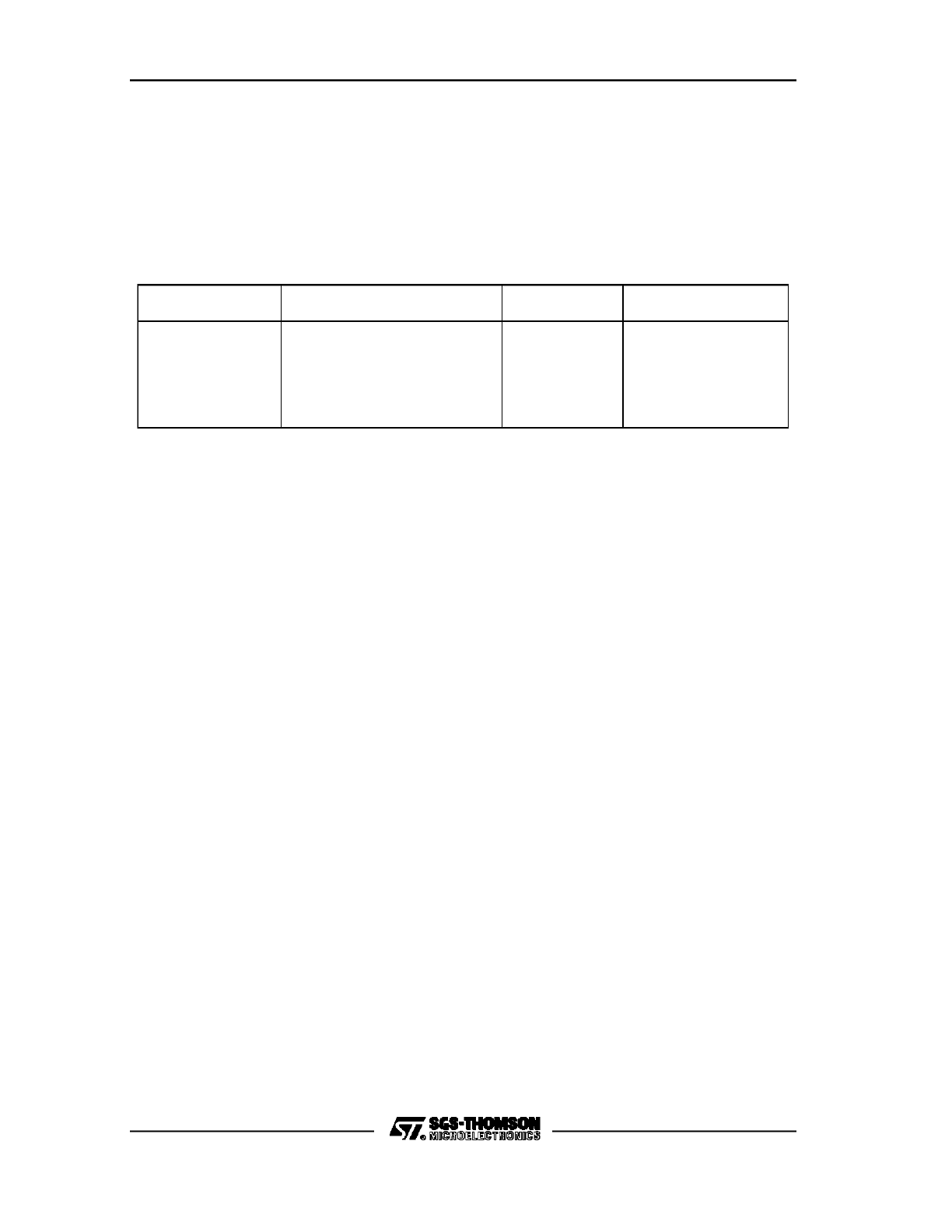

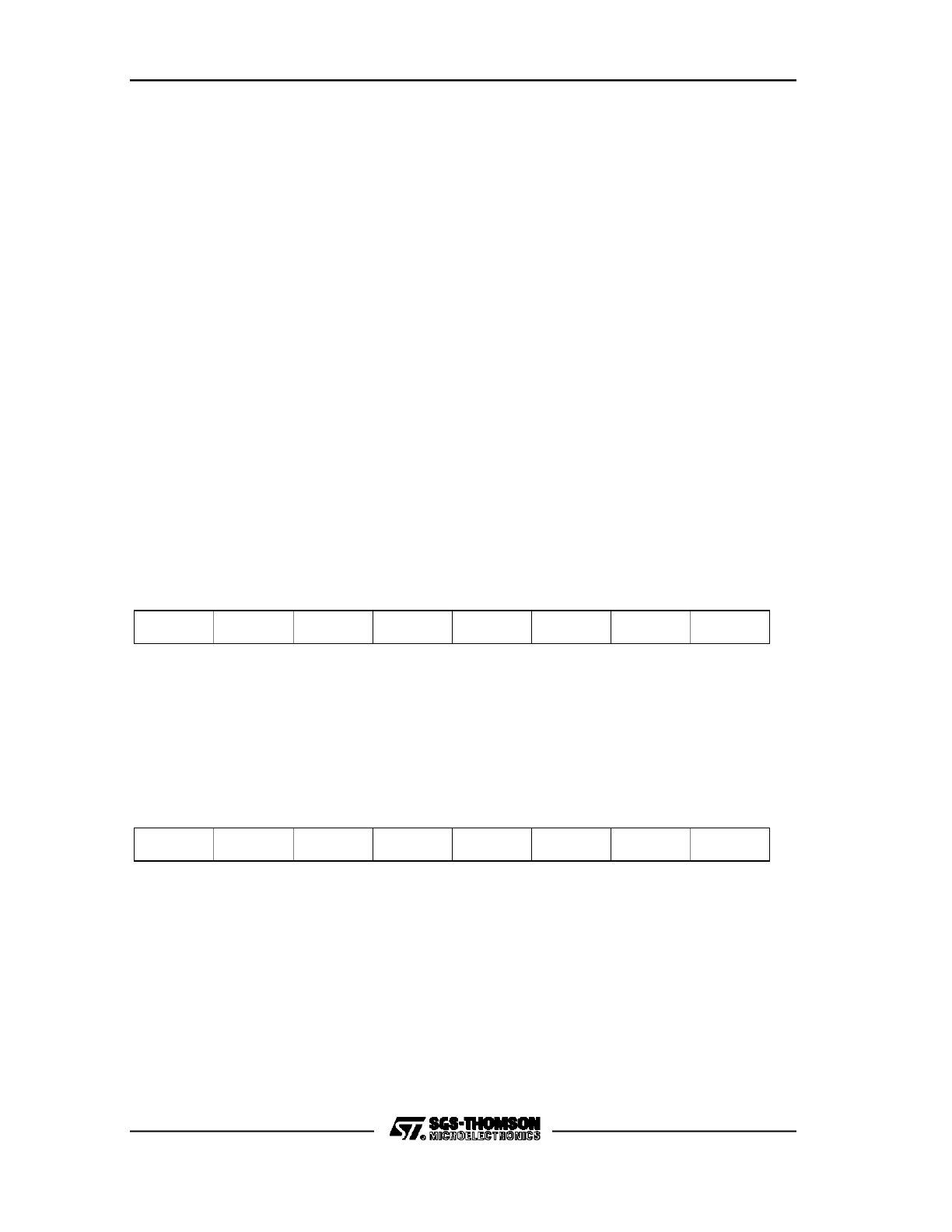

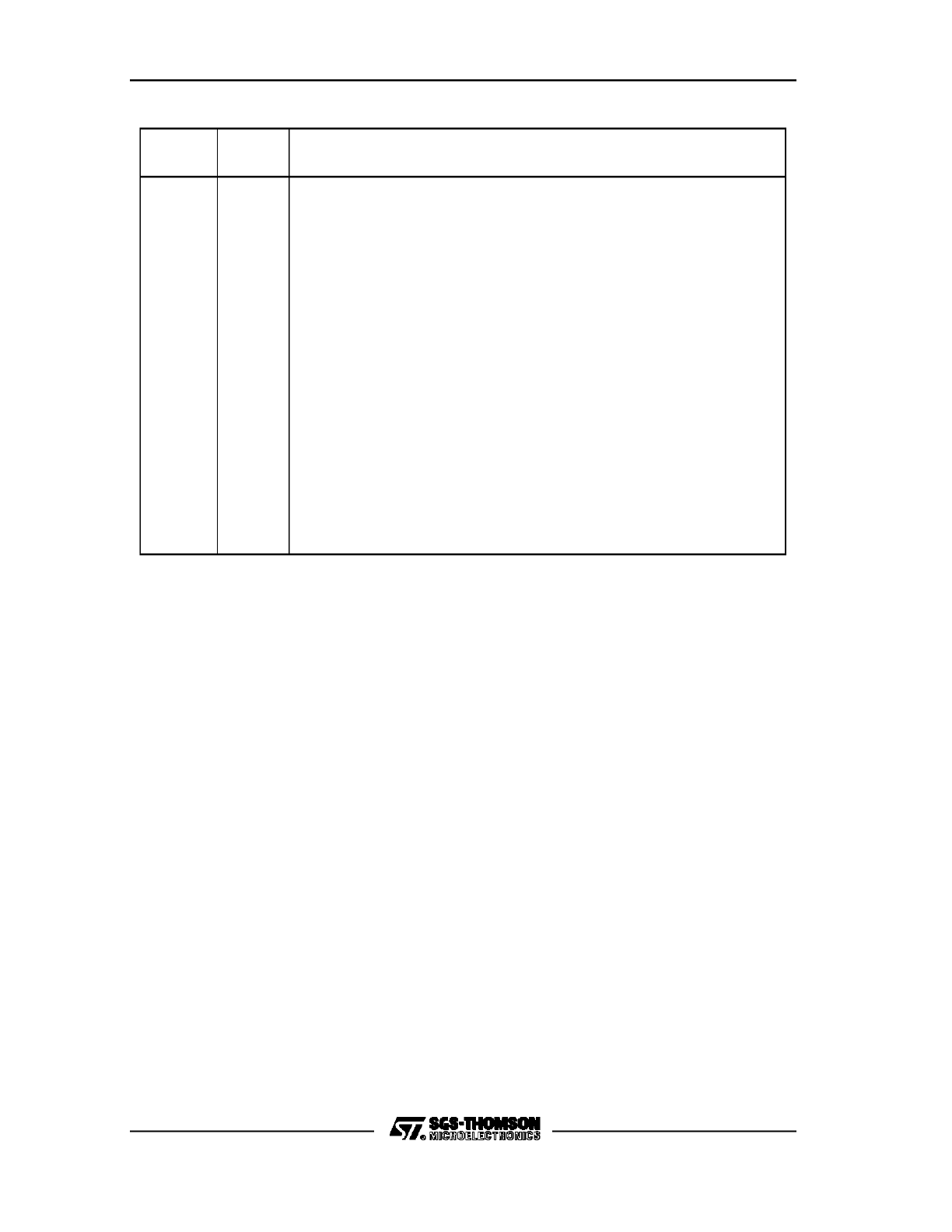

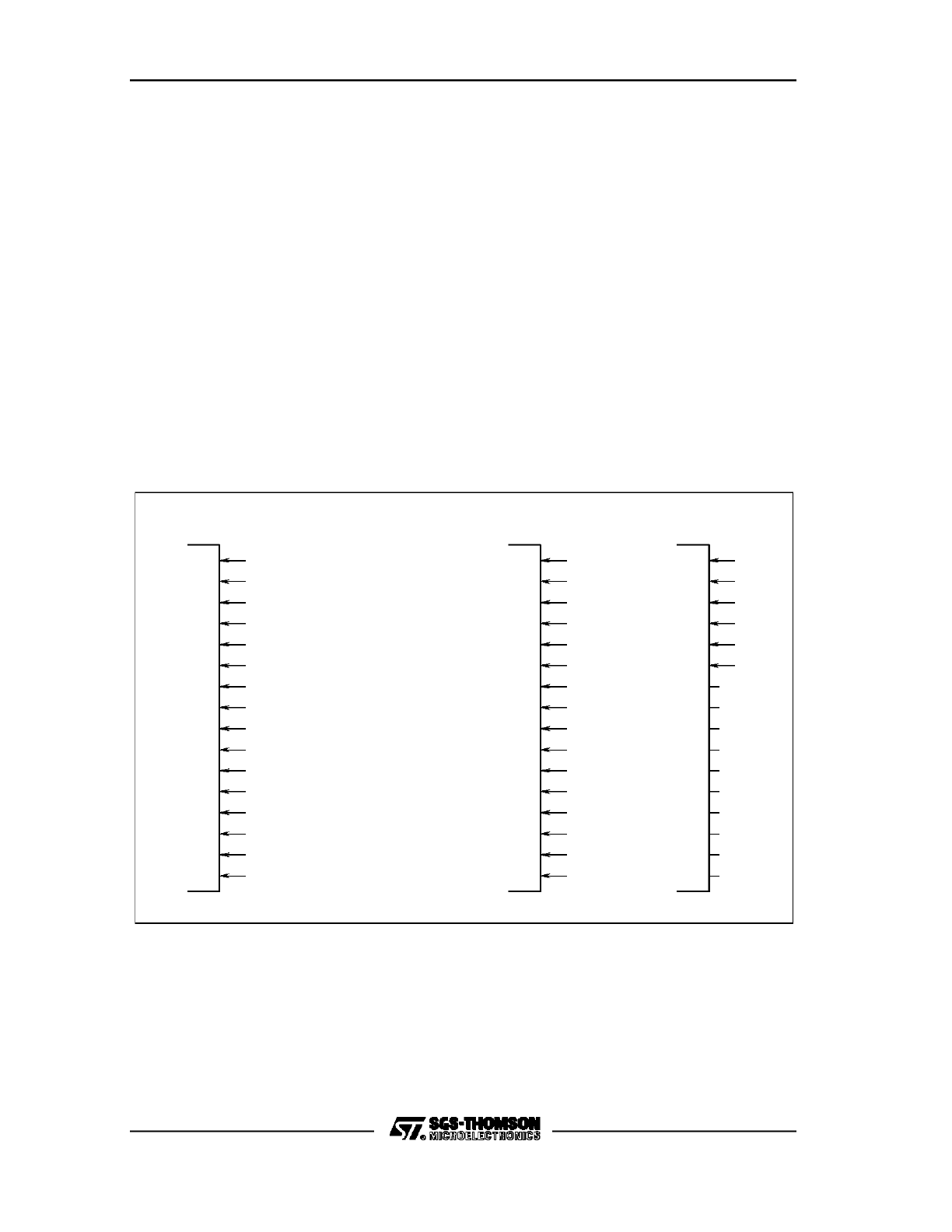

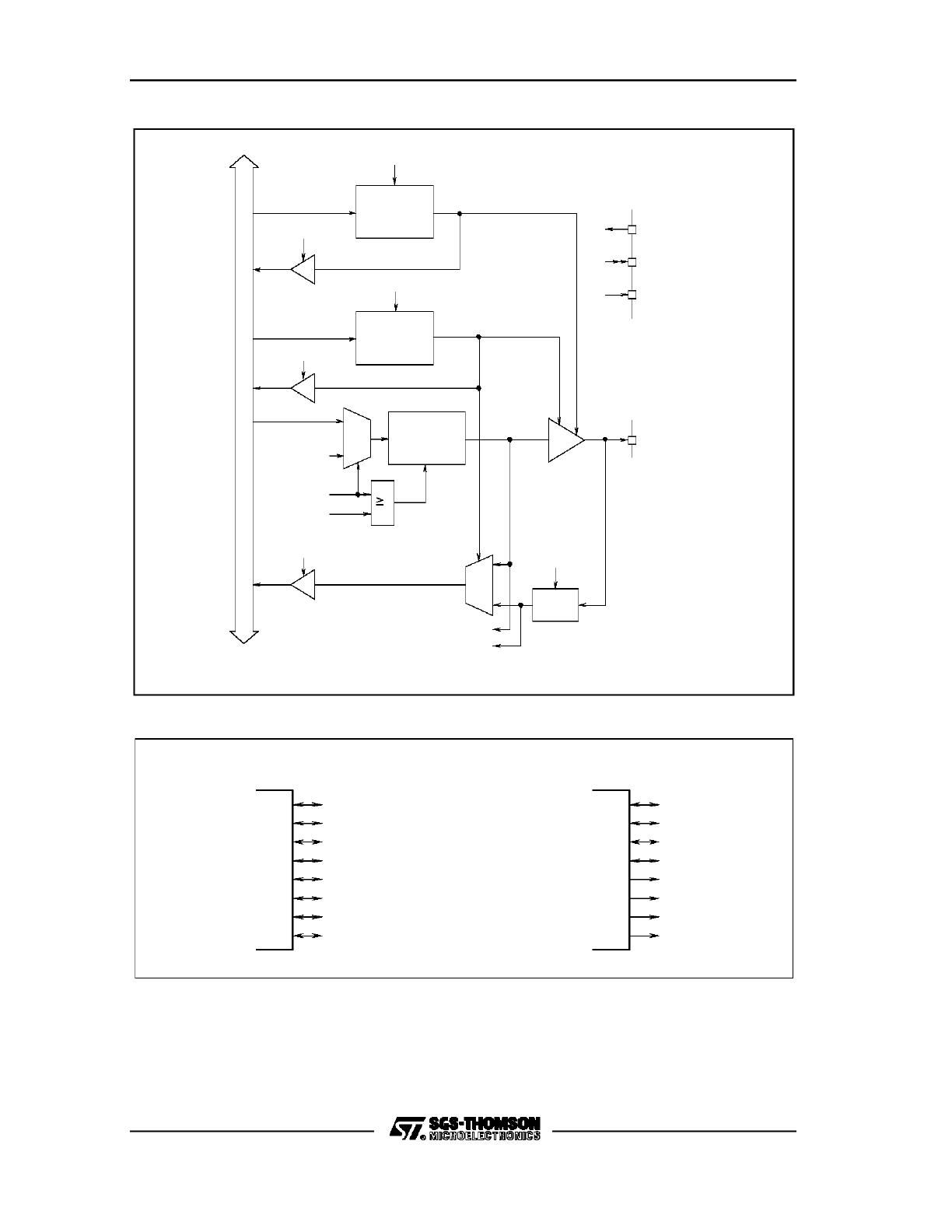

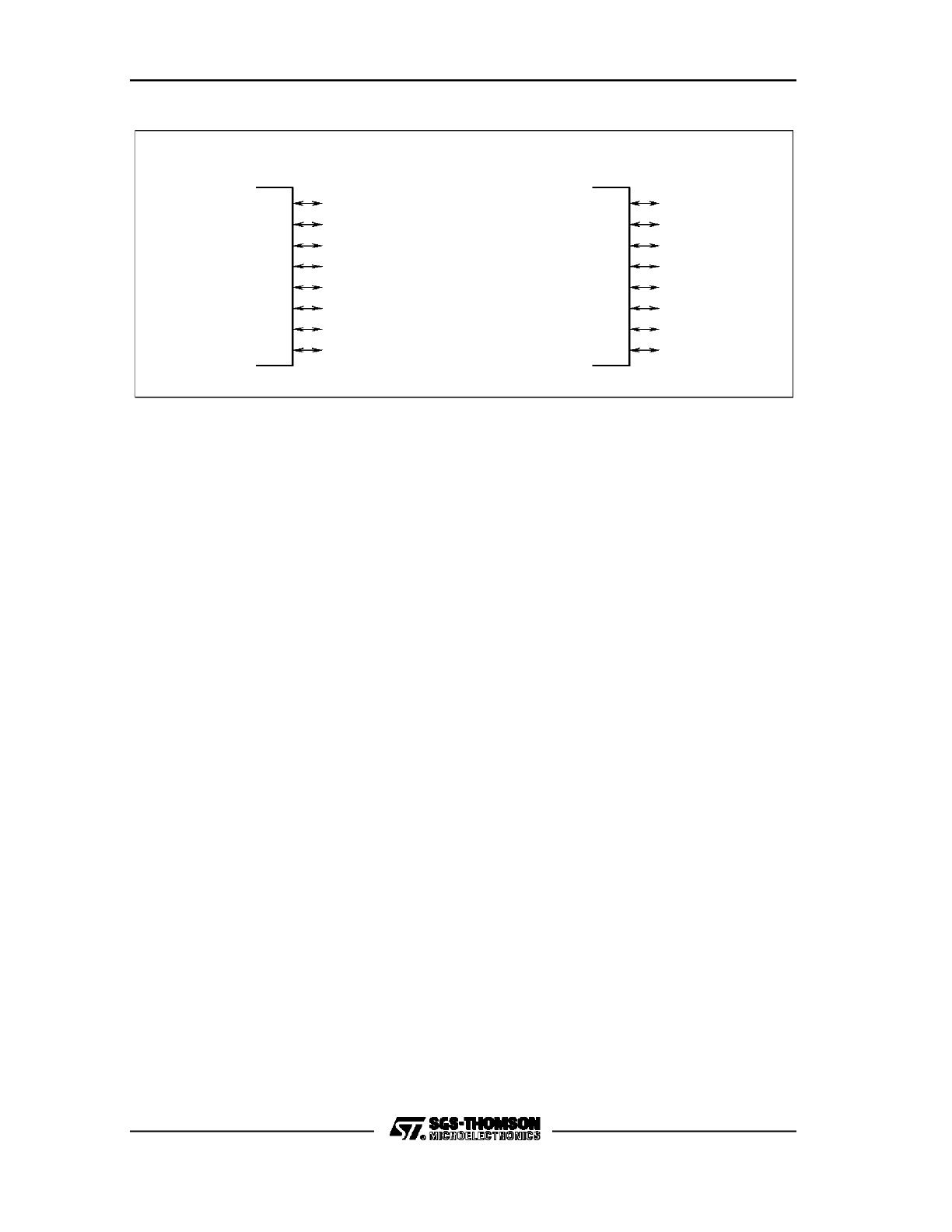

Figure 10. Read / Write Chip Select Examples

8-Bit

Latch

e.g.

HC573

OC

C

Data

Output

D7...D0

Read CS

e.g.

Input

Data

DIP-

C

OC

HC574

e.g.

Latch

8-Bit

Switches

D7...D0

Data

Input

e.g.

D7...D0

Output

Data

Write CS

+5V

VR001895

a: Read Chip Select Example

b: Write Chip Select Example

Note: When the WRH#/WRL# option (see next chapter) is selected, the Write or

Read/Write Chip Select will go active if any of the WRH# or WRL# signals goes

active. There will be no distinction between writing to the low byte, to the high byte, or

to both. The read/write chip selects will also be affected by the read/write delay

control RWDCx of a BUSCONx register.

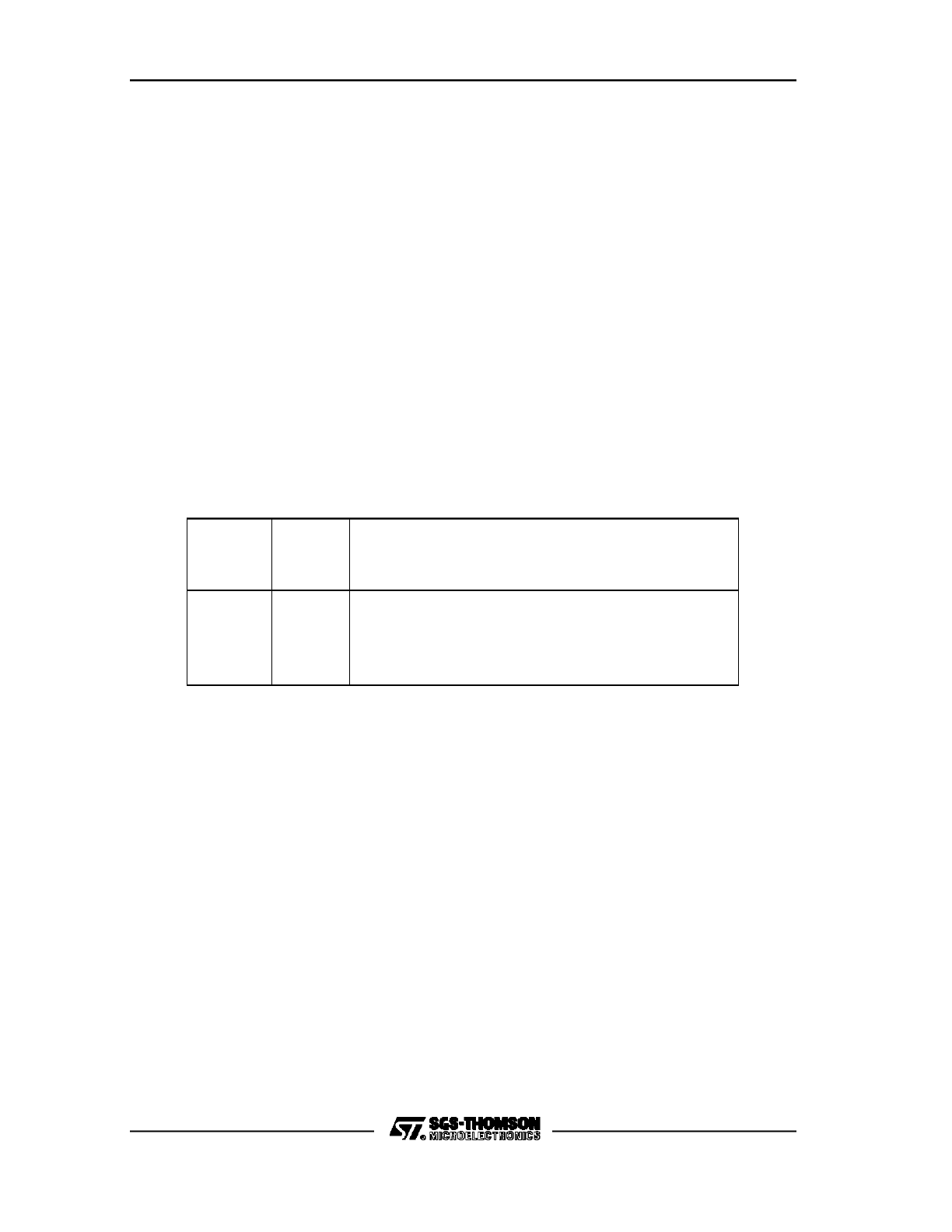

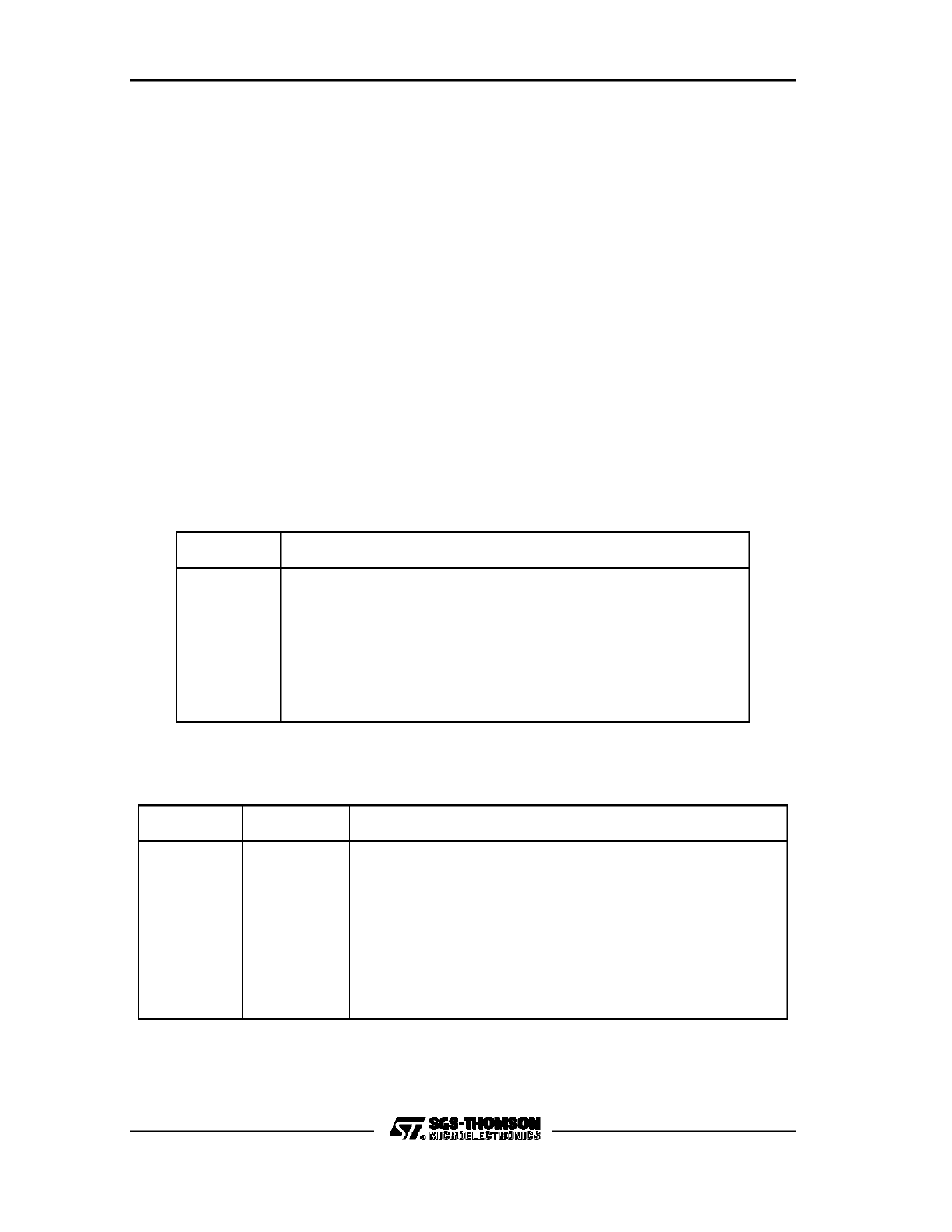

3.4

Byte High Enable or Write High , Write Low Operation

C167 FAMILY PRELIMINARY USER MANUAL

47/180

When writing bytes to external word-wide memories or peripherals (regardless

whether they are true word-wide devices or two 8-bit devices in parallel), a distinction

has to be made between writing to the low or to the high byte, or to both. For this

purpose, the address line A0 and the Byte High Enable signal BHE# are used to

properly select either half or both halfs of the device. Figure 11 shows an example for

this connection, where the chip select signal is gated with A0 and BHE# (see also the

ST10 User Manual).

C167 FAMILY PRELIMINARY USER MANUAL

48/180

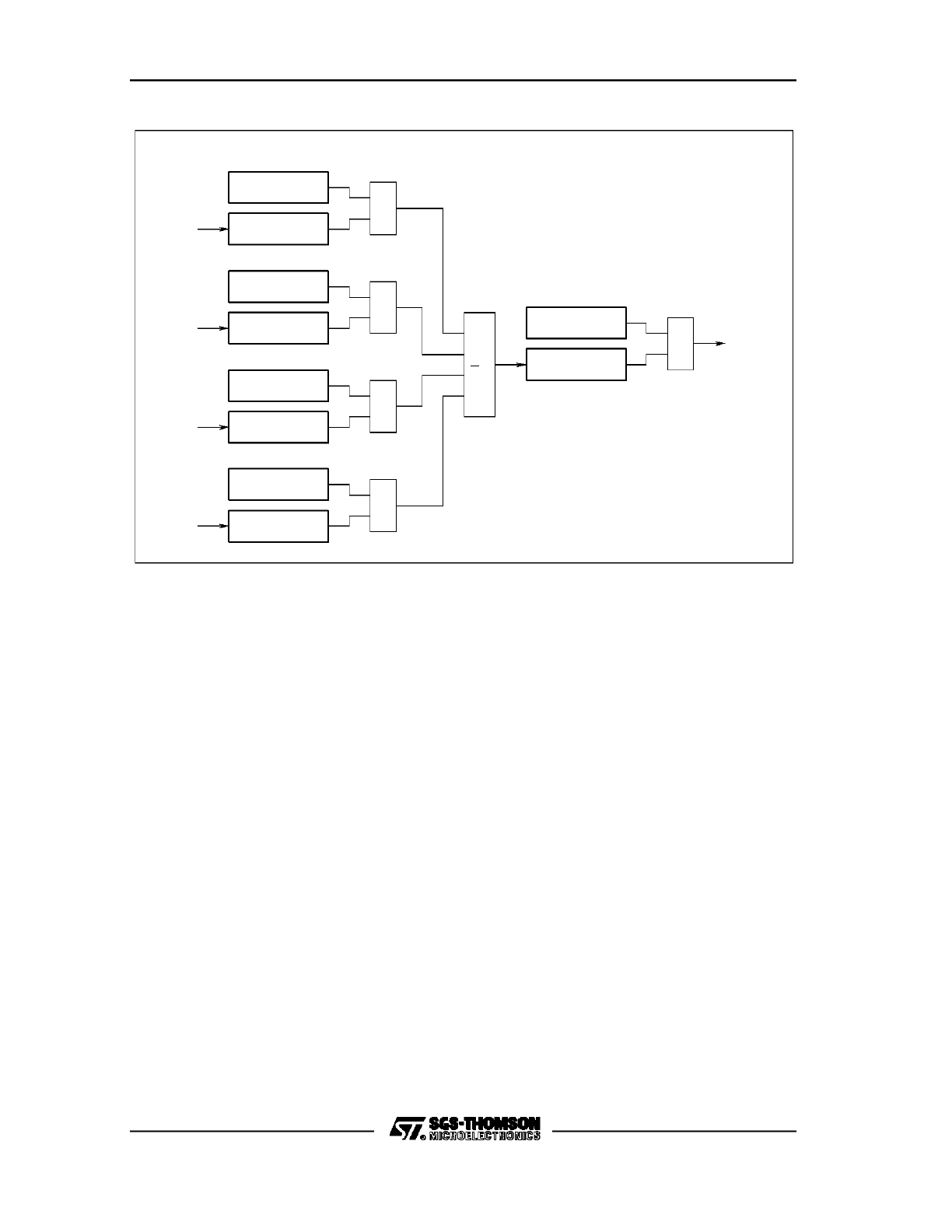

Figure 11. Connection Possibilities of an External Read / Write Device

RD

WR

> 1

CS-LOW

CS-HIGH

1

>

A0

BHE

CS

(from Decoder)

WR

RD

CSL

CSH

A1

A2

A0

A1

A3

A2

A4

A3

A5

A4

An-1

An

16-Bit Device

D0...D15

D0...D15

Data Bus

a: Separate Chip Select Inputs

b: Separate Write Strobe Inputs

Data Bus

D0...D15

D0...D15

16-Bit Device

An

An-1

A4

A5

A3

A4

A2

A3

A1

A0

A2

A1

WRH

WRL

RD

CS

(from Decoder)

WR

BHE

A0

> 1

WR-HIGH

WR-LOW

1

>

CS

RD

Address Bus

Address Bus

VR001896

C167 FAMILY PRELIMINARY USER MANUAL

49/180

Besides devices with two chip select inputs, which can be connected via the method

described above, there exist a number of external 16-bit devices which have only

one chip select input, but two separate write inputs: a Write Low Byte (WRL#) and a

Write High Byte (WRH#) input. Connecting these devices can be done as illustrated

in Figure 11b.

As it can be seen, both methods require external glue logic, and it is very desirable to

save these gates and have integrated solutions instead. To integrate separate chip

selects for low or high byte instead of BHE# and A0 (Figure 11a) would require

double the number of chip selects and pins, which are not available in the C167.

Integrating the second method, however, does not require additional pins, since the

write signals run parallel to all read/write devices. Thus, this method was chosen for

implementation. The C167 will incorporate an option to automatically generate a

WRL# and WRH# signal instead of WR# and BHE#. This option can be selected via

the control bit WRCFG, Write Configuration (SYSCON.7). When this bit is set, the

WR# pin will be configured as a Write Low Byte (WRL#) strobe, and the BHE# pin as

a Write High Byte (WRH#) strobe. The following table shows the resulting

relationship:

WR#/

WRL#

BHE#/

WRH#

Operation

0

0

Write to a word (Low and High byte)

0

1

Write to the low byte

1

0

Write to the high byte

1

1

No write access (either read or no access)

Figure 12 shows the timing of these signals compared to the default mode (WR# and

BHE#). Note that after reset, the default mode is the WR#/BHE# operation. If the

BYTDIS bit (BHE# Pin Disable bit, SYSCON.9) is set, also the WRH# operation, if