2017 Microchip Technology Inc.

DS20005845A-page 1

HV507

Features

• Up to 300V Output Voltage

• Low-power Level Shifting from 5V to 300V

• Shift Register Speed:

- 8 MHz at V

DD

= 5V

• Latched Data Outputs

• Output Polarity and Blanking

• CMOS-compatible Inputs

• Forward and Reverse Shifting Options

Applications

• Display Driver

• Print Head Driver

• Microelectromechanical Systems Applications

General Description

The HV507 is a low-voltage to high-voltage

serial-to-parallel converter with 64 push-pull outputs.

This device is designed as a printer driver for

electrostatic applications. It can also be used in any

application requiring multiple-output high-voltage

low-current sourcing-and-sinking capabilities.

The device consists of a 64-bit Shift register,

64 latches and control logic to perform the polarity

select and blanking of the outputs. A DIR pin controls

the direction of data shift through the device. With the

DIR grounded, D

IO

A is data in and D

IO

B is data out.

Data is shifted from HV

OUT

64 to HV

OUT

1. When DIR is

at logic high, D

IO

B is data in and D

IO

A is data out. The

data is then shifted from HV

OUT

1 to HV

OUT

64 through

the Shift register on the low-to-high transition of the

clock. Data output buffers are provided for cascading

devices. The operation of the shift register is not

affected by the latch enable (LE), blanking (BL) and

polarity (POL) inputs. Transfer of data from the Shift

register to the latch occurs when the LE is high. The

data in the latch is stored during LE transition from high

to low.

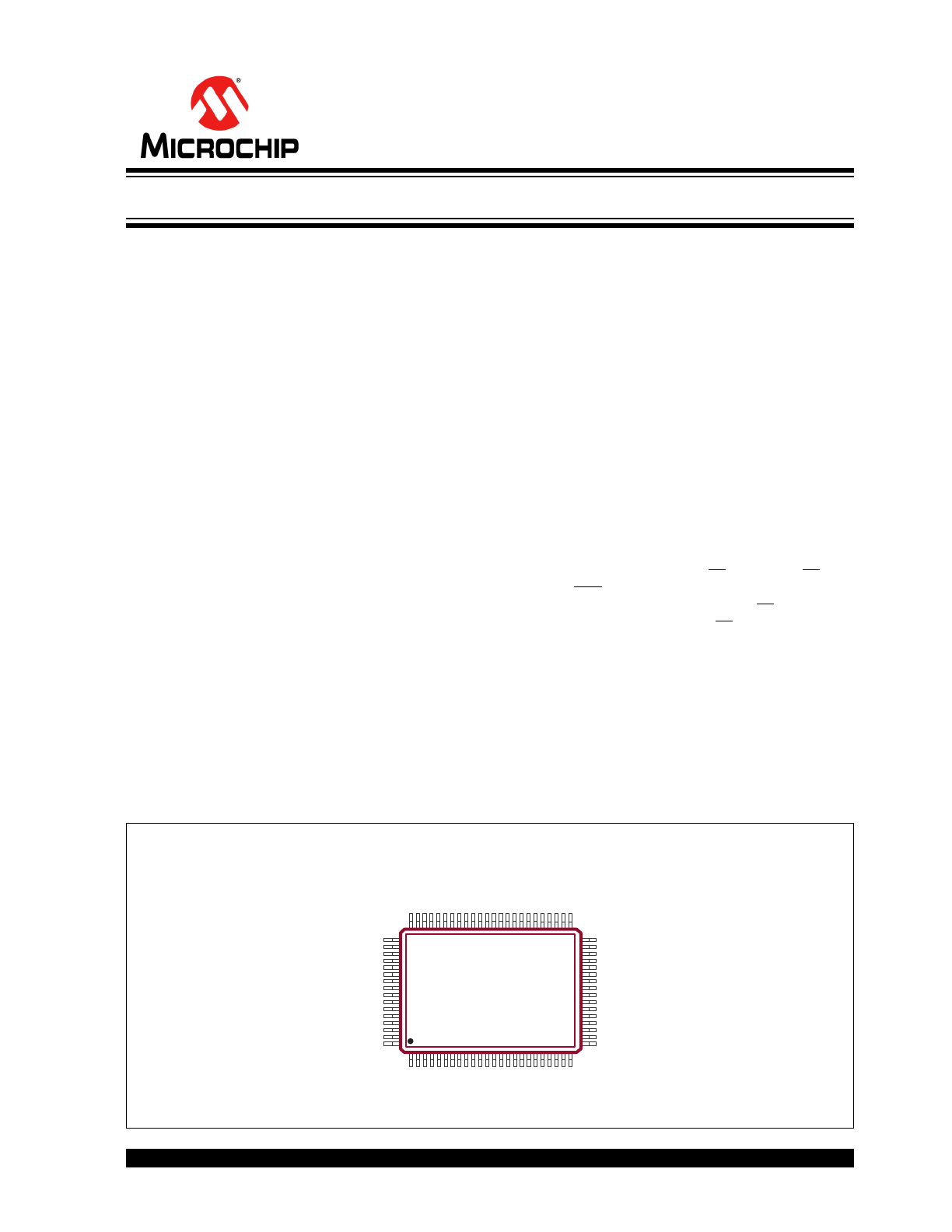

Package Type

See

Table 2-1

for pin information.

80-lead PQFP

(Top view)

1

80

64-Channel Serial-to-Parallel Converter with High-Voltage Push-Pull Outputs

HV

OUT

2

•

•

•

60 Additional

Outputs

•

•

•

HV

OUT

63

POL

BL

Latch Enable

CLOCK

64

Latches

V

PP

HV

OUT

1

DIR

HV

OUT

64

D

IO

B

L/T

L/T

L/T

L/T

L/T = Level Translator

D

IO

A

64 bit

Static Shift

Register

HV507

DS20005845A-page 2

2017 Microchip Technology Inc.

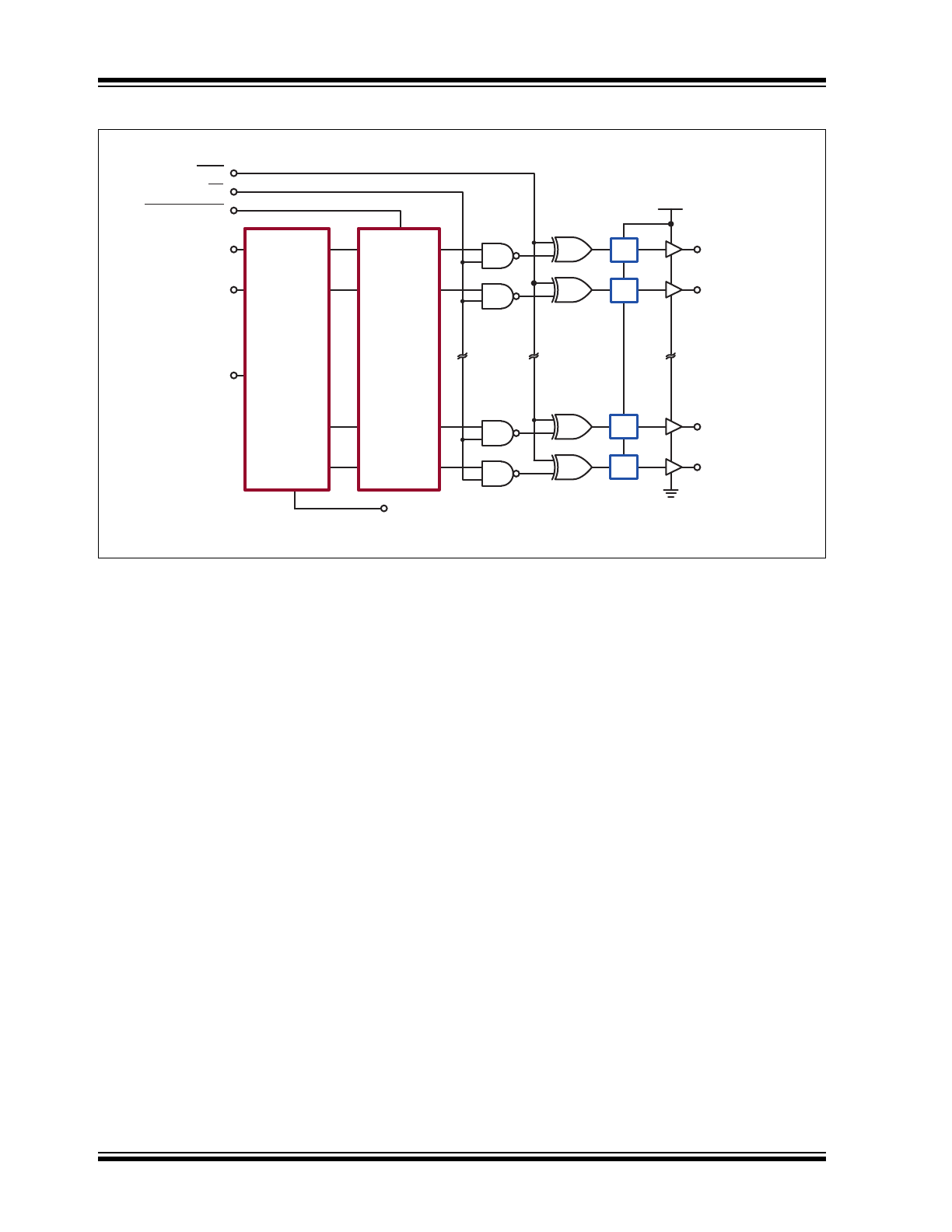

Functional Block Diagram

2017 Microchip Technology Inc.

DS20005845A-page 3

HV507

Typical Application Circuit

HV507

DS20005845A-page 4

2017 Microchip Technology Inc.

1.0

ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings†

Low-supply Voltage, V

DD

........................................................................................................................... –0.5V to +6V

High-supply Voltage, V

PP

.......................................................................................................................... V

DD

to +320V

Logic Input Levels ............................................................................................................................ –0.5V to V

DD

+0.5V

Ground Current (

Note 2

) ......................................................................................................................................... 0.5A

High-voltage Supply Current (

Note 1

) ..................................................................................................................... 0.5A

Operating Ambient Temperature, T

A

........................................................................................................ 0°C to +70°C

Storage Temperature, T

S

.................................................................................................................... –65°C to +150°C

Continuous Total Power Dissipation:

80-lead PQFP (

Note 2

) ......................................................................................................................... 1200 mW

† Notice: Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the

device. This is a stress rating only, and functional operation of the device at those or any other conditions above those

indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for

extended periods may affect device reliability.

Note 1: Connection to all power and ground pads is required. Duty cycle is limited by the total power dissipated in

the package.

2: For operations above 25°C ambient, derate linearly to 70°C at 26.7 mW/°C.

RECOMMENDED OPERATING CONDITIONS

Parameter

Sym.

Min.

Typ.

Max.

Unit

Conditions

Logic Supply Voltage

V

DD

4.5

5

5.5

V

High-voltage Supply Voltage

V

PP

60

—

300

V

High-level Input Voltage

V

IH

V

DD

–0.9V

—

V

DD

V

Low-level Input Voltage

V

IL

0

—

0.9

V

DC ELECTRICAL CHARACTERISTICS

Electrical Specifications: For V

DD

= 5V, V

PP

= 300V and T

A

= 25°C.

Parameter

Sym.

Min.

Typ.

Max.

Unit

Conditions

V

DD

Supply Current

I

DD

—

—

15

mA

f

CLK

= 8 MHz,

f

DATA

= 4 MHz, LE = low

Quiescent V

DD

Supply Current

I

DDQ

—

—

200

µA

All V

IN

= 0V or V

DD

High-voltage Supply Current

I

PP

—

—

0.5

mA

V

PP

= 300V, all outputs

high

—

—

0.5

mA

V

PP

= 300V, all outputs

low

High-level Logic Input Current

I

IH

—

—

10

µA

V

IN

= V

DD

Low-level Logic Input Current

I

IL

—

—

–10

µA

V

IN

= 0V

High-level Output

HV

OUT

V

OH

265

—

—

V

V

PP

= 300V,

IHV

OUT

= –1 mA,

ID

OUT

= –100 µA

Data Out

V

DD

–1

—

—

V

Low-level Output

HV

OUT

V

OL

—

—

35

V

V

DD

= 5V,

IHV

OUT

= 1 mA,

ID

OUT

= 100 µA

Data Out

—

—

1

V

HV

OUT

Clamp Voltage

V

OC

—

—

V

PP

+ 1.5

V

I

OL

= 1 mA

—

—

–30

V

I

OL

= –1 mA

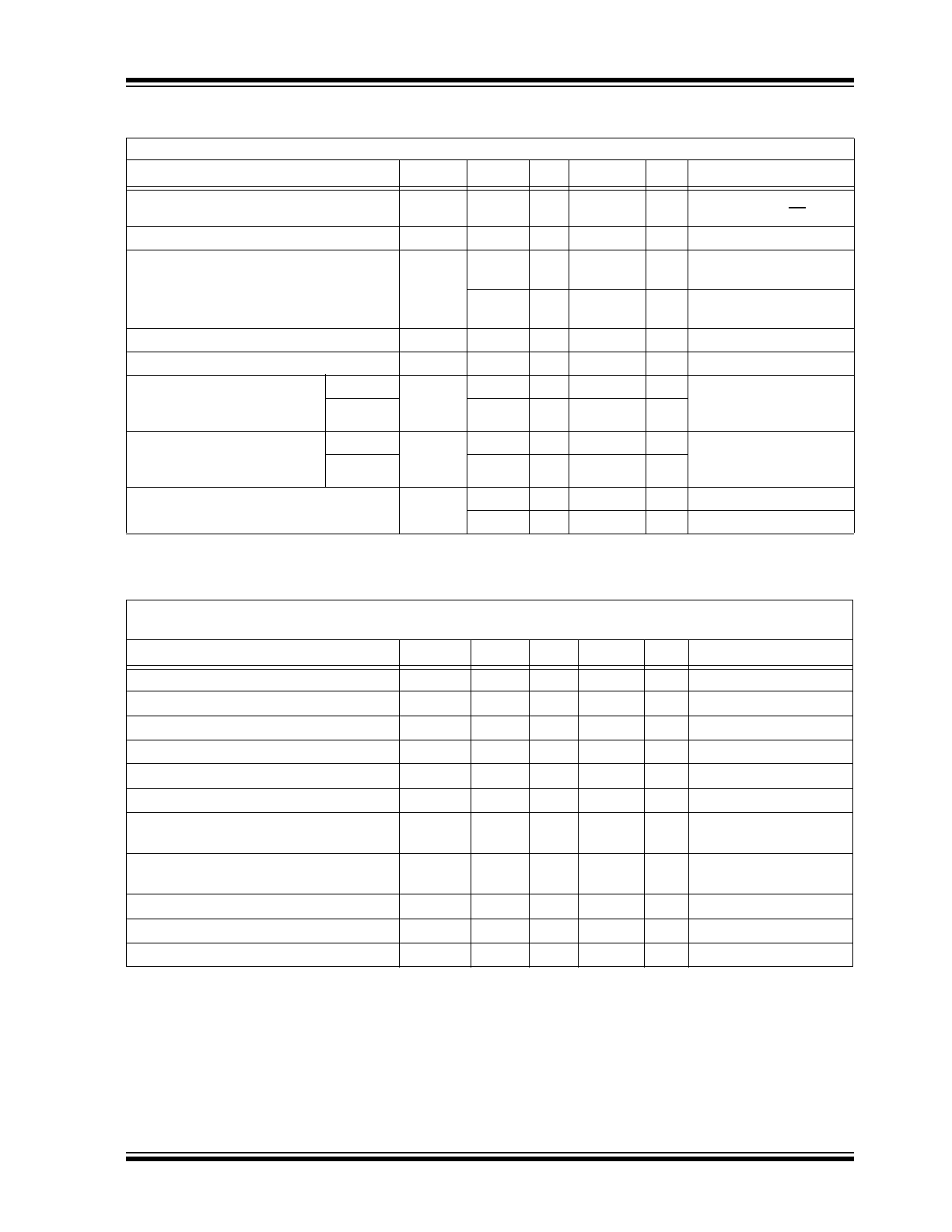

AC ELECTRICAL CHARACTERISTICS

Electrical Specifications: For V

DD

= 5V, V

PP

= 300V and T

A

= 25°C. Shift register speed can be as low as DC as

long as data set-up and hold time meet the specifications.

Parameter

Sym.

Min.

Typ.

Max.

Unit

Conditions

Clock Frequency

f

CLK

—

—

8

MHz

Clock Width High or Low

t

WL

, t

WH

62

—

—

ns

Data Set-up Time before Clock Rises

t

SU

35

—

—

ns

Data Hold Time after Clock Rises

t

H

30

—

—

ns

Time from Latch Enable to HV

OUT

t

ON

, t

OFF

—

—

4

ns

C

L

= 20 pF

Latch Enable Pulse Width

t

WLE

80

—

—

ns

Delay Time Clock to Latch Enable Low to

High

t

DLE

35

—

—

ns

Latch Enable Set-up Time before Clock

Rises

t

SLE

40

—

—

ns

Delay Time Clock to Data Low to High

t

DLH

—

—

125

ns

C

L

= 20 pF

Delay Time Clock to Data High to Low

t

DHL

—

—

125

ns

C

L

= 20 pF

All Logic Inputs

t

r

, t

f

—

—

5

ns

2017 Microchip Technology Inc.

DS20005845A-page 5

HV507

TEMPERATURE SPECIFICATIONS

Parameter

Sym.

Min.

Typ.

Max.

Unit

Conditions

TEMPERATURE RANGE

Operating Ambient Temperature

T

A

0

—

+70

°C

Storage Temperature

T

S

–65

—

+150

°C

PACKAGE THERMAL RESISTANCE

80-lead PQFP

JA

—

37

—

°C/W

HV507

DS20005845A-page 6

2017 Microchip Technology Inc.

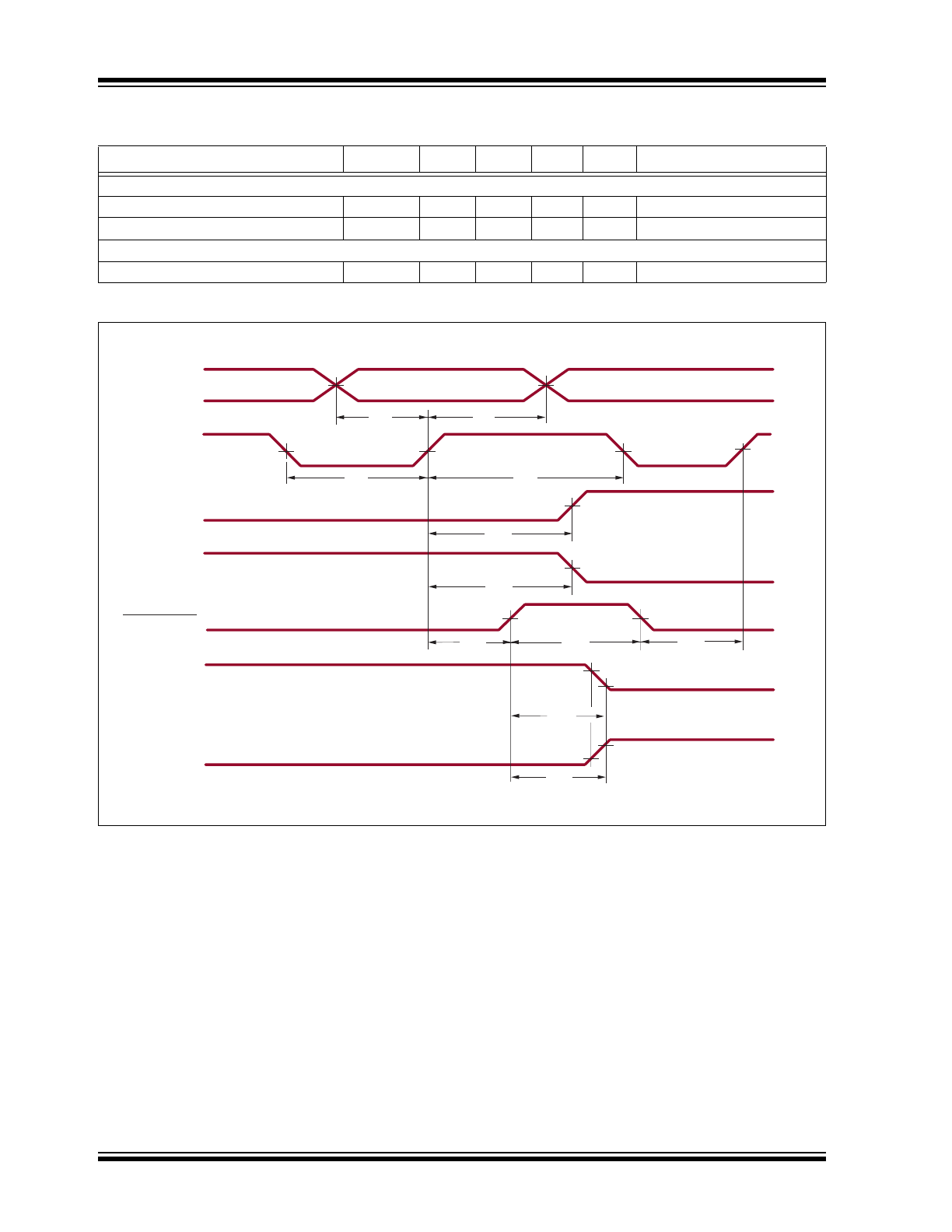

Timing Waveforms

Latch Enable

HV

OUT

w/ S/R LOW

Data Valid

50%

50%

Data In

(D

IO

A/D

IO

B)

CLK

t

SU

t

H

t

WL

t

WH

50%

50%

t

DLH

t

DHL

50%

t

WLE

t

DLE

t

SLE

50%

50%

t

ON

10%

90%

90%

10%

t

OFF

V

IH

V

IL

V

IH

V

IL

V

OH

V

OL

V

OH

V

OL

V

OH

V

OL

V

OH

V

OL

V

OH

V

OL

Data Out

(D

IO

A/D

IO

B)

HV

OUT

w/ S/R HIGH

2017 Microchip Technology Inc.

DS20005845A-page 7

HV507

2.0

PIN DESCRIPTION

The details on the pins of HV507 are listed on

Table 2-1

. Refer to

Package Type

for the location of

pins.

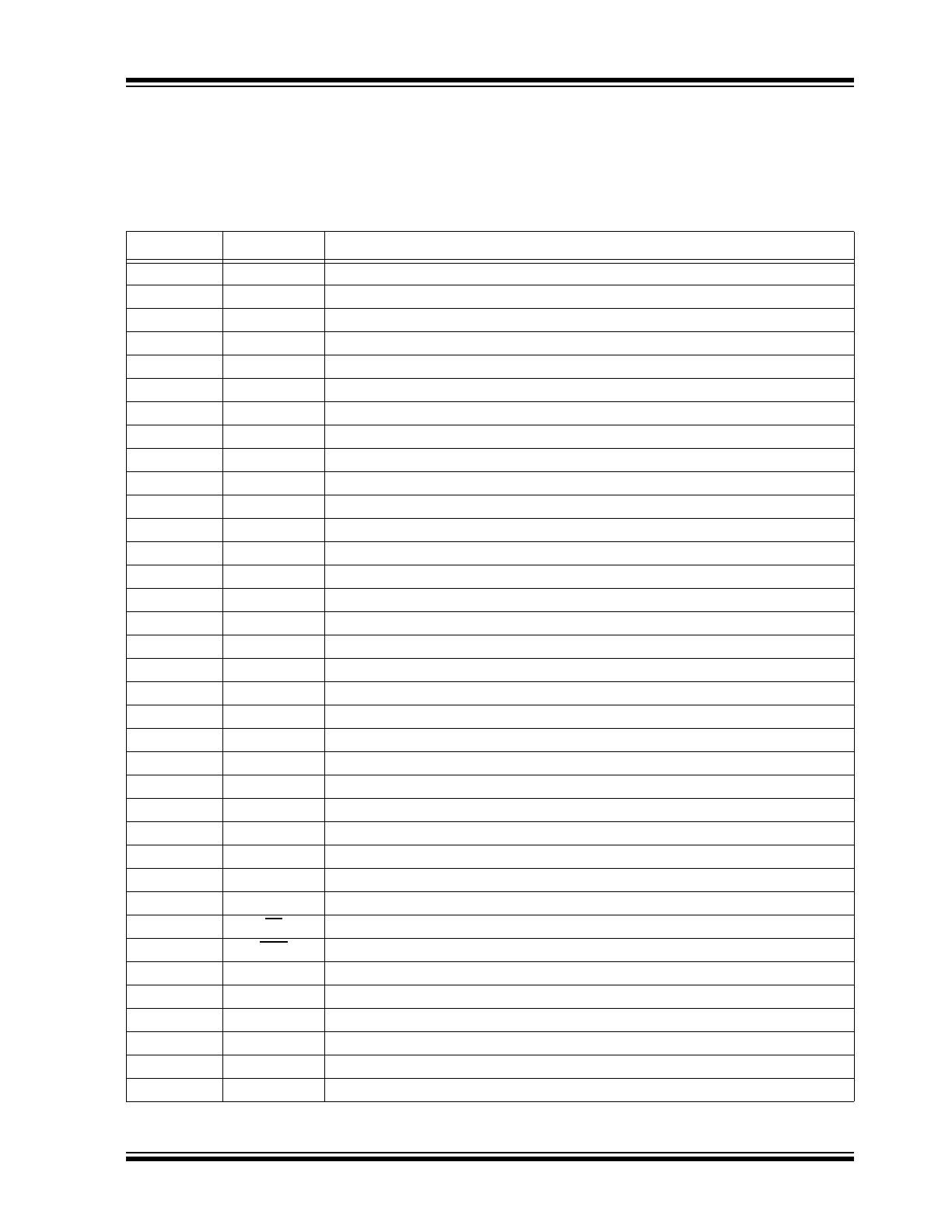

TABLE 2-1:

PIN FUNCTION TABLE

Pin Number

Pin Name

Description

1

HVOUT41

High-voltage output

2

HVOUT42

High-voltage output

3

HVOUT43

High-voltage output

4

HVOUT44

High-voltage output

5

HVOUT45

High-voltage output

6

HVOUT46

High-voltage output

7

HVOUT47

High-voltage output

8

HVOUT48

High-voltage output

9

HVOUT49

High-voltage output

10

HVOUT50

High-voltage output

11

HVOUT51

High-voltage output

12

HVOUT52

High-voltage output

13

HVOUT53

High-voltage output

14

HVOUT54

High-voltage output

15

HVOUT55

High-voltage output

16

HVOUT56

High-voltage output

17

HVOUT57

High-voltage output

18

HVOUT58

High-voltage output

19

HVOUT59

High-voltage output

20

HVOUT60

High-voltage output

21

HVOUT61

High-voltage output

22

HVOUT62

High-voltage output

23

HVOUT63

High-voltage output

24

HVOUT64

High-voltage output

25

VPP

High-voltage power supply

26

DIOA

Serial Data Input/Output A

27

NC

No connection

28

NC

No connection

29

BL

Blanking

30

POL

Polarity

31

VDD

Low-voltage power supply

32

DIR

Direction

33

GND

Logic voltage ground

34

HVGND

High-voltage power supply

35

NC

No connection

36

NC

No connection

HV507

DS20005845A-page 8

2017 Microchip Technology Inc.

37

CLK

Data Shift Register Clock. Inputs are shifted into the Shift register on the positive

edge of the clock.

38

LE

Latch Enable

39

DIOB

Serial Data Input/Output B

40

VPP

High-voltage power supply

41

HVOUT1

High-voltage output

42

HVOUT2

High-voltage output

43

HVOUT3

High-voltage output

44

HVOUT4

High-voltage output

45

HVOUT5

High-voltage output

46

HVOUT6

High-voltage output

47

HVOUT7

High-voltage output

48

HVOUT8

High-voltage output

49

HVOUT9

High-voltage output

50

HVOUT10

High-voltage output

51

HVOUT11

High-voltage output

52

HVOUT12

High-voltage output

53

HVOUT13

High-voltage output

54

HVOUT14

High-voltage output

55

HVOUT15

High-voltage output

56

HVOUT16

High-voltage output

57

HVOUT17

High-voltage output

58

HVOUT18

High-voltage output

59

HVOUT19

High-voltage output

60

HVOUT20

High-voltage output

61

HVOUT21

High-voltage output

62

HVOUT22

High-voltage output

63

HVOUT23

High-voltage output

64

HVOUT24

High-voltage output

65

HVOUT25

High-voltage output

66

HVOUT26

High-voltage output

67

HVOUT27

High-voltage output

68

HVOUT28

High-voltage output

69

HVOUT29

High-voltage output

70

HVOUT30

High-voltage output

71

HVOUT31

High-voltage output

72

HVOUT32

High-voltage output

73

HVOUT33

High-voltage output

74

HVOUT34

High-voltage output

75

HVOUT35

High-voltage output

76

HVOUT36

High-voltage output

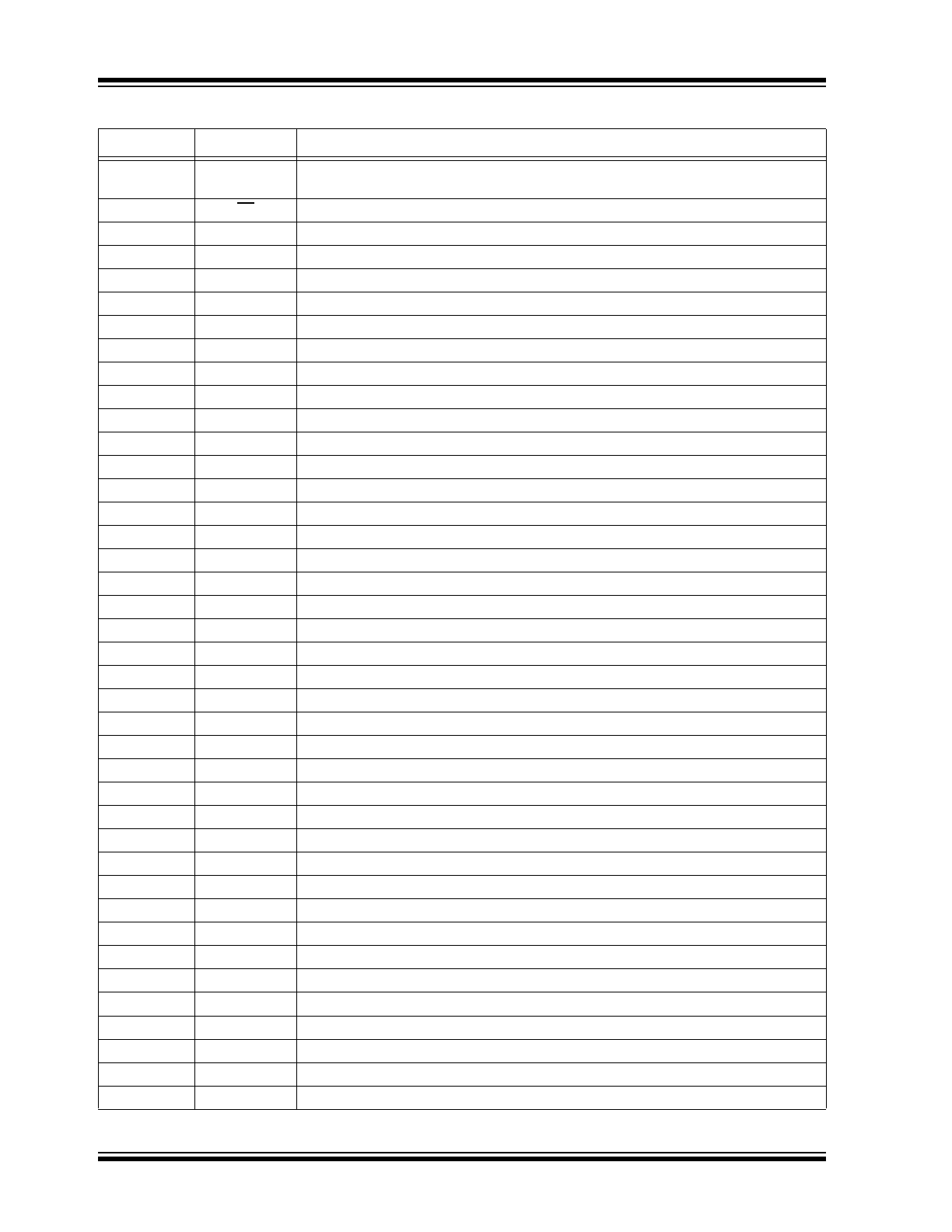

TABLE 2-1:

PIN FUNCTION TABLE (CONTINUED)

Pin Number

Pin Name

Description

2017 Microchip Technology Inc.

DS20005845A-page 9

HV507

77

HVOUT37

High-voltage output

78

HVOUT38

High-voltage output

79

HVOUT39

High-voltage output

80

HVOUT40

High-voltage output

TABLE 2-1:

PIN FUNCTION TABLE (CONTINUED)

Pin Number

Pin Name

Description

HV507

DS20005845A-page 10

2017 Microchip Technology Inc.

3.0

FUNCTIONAL DESCRIPTION

Follow the steps in

Table 3-1

to power up and power

down the HV507.

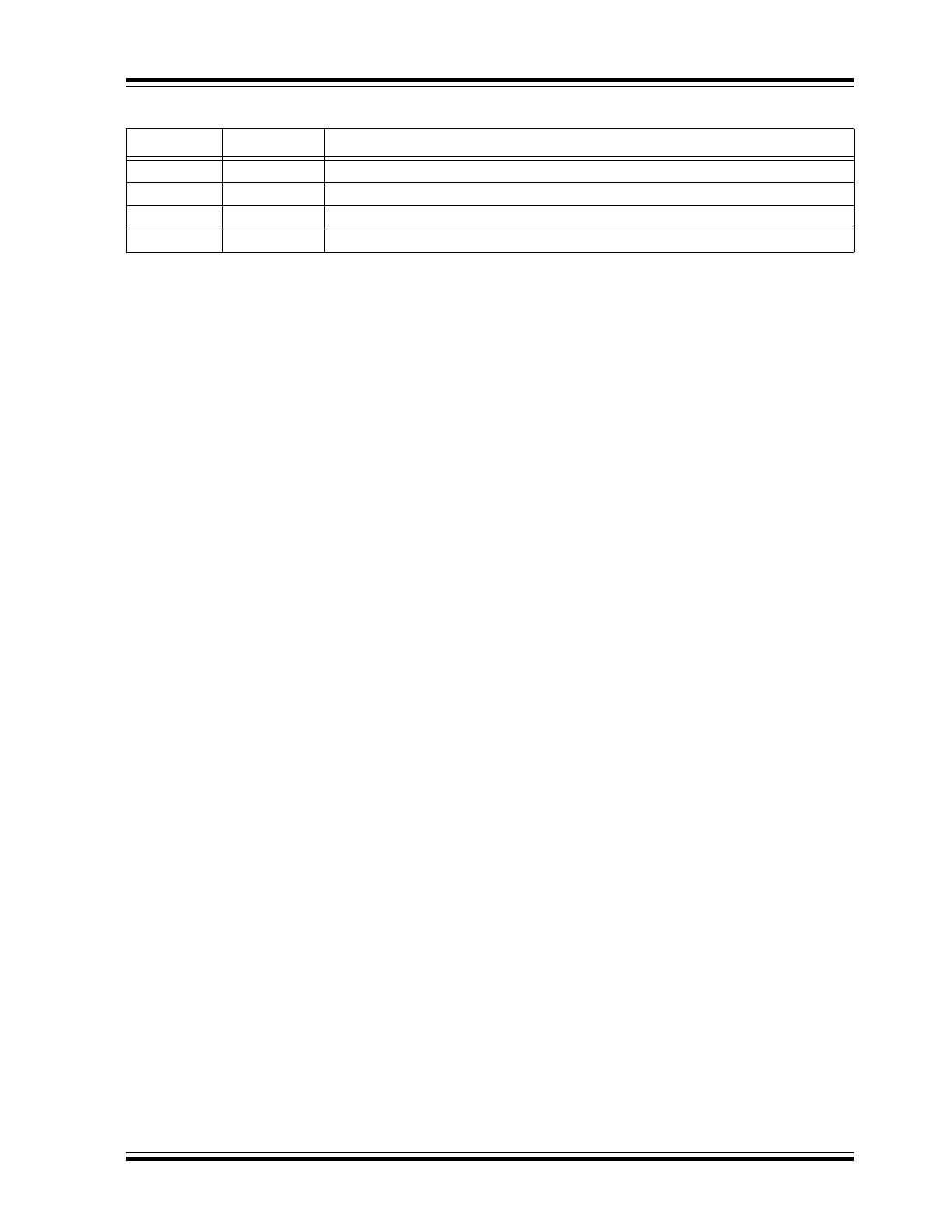

TABLE 3-1:

POWER-UP AND POWER-DOWN SEQUENCE

Power-up

Power-down

Step

Description

Step

Description

1

Connect ground.

1

Remove V

PP.

(

Note 1

)

2

Apply V

DD.

2

Remove all inputs.

3

Set all inputs (Data, CLK, Enable, etc.) to a known state.

3

Remove V

DD.

4

Apply V

PP.

(

Note 1

)

4

Disconnect ground.

Note 1: The V

PP

should not drop below V

DD

or float during operation.

TABLE 3-2:

Function

Inputs

Outputs

Data CLK

LE

BL

POL DIR

Shift Register

High-voltage Output

Data Out

1

2...64

1

2...64

*

All On

X

X

X

L

L

X

*

*...*

H

H...H

*

All Off

X

X

X

L

H

X

*

*...*

L

L...L

*

Invert Mode

X

X

L

H

L

X

*

*...*

*

*...*

*

Load S/R

H or L

↑

L

H

H

X

H or L

*...*

*

*...*

*

Store Data in

Latches

X

X

↓

H

H

X

*

*...*

*

*...*

*

X

X

↓

H

L

X

*

*...*

*

*...*

*

Transparent

Latch Mode

L

↑

H

H

H

X

L

*...*

L

*...*

*

H

↑

H

H

H

X

H

*...*

H

*...*

*

I/O Relation

D

IO

A

↑

X

X

X

L

Q

N

→

Q

N+1

—

D

IO

B

D

IO

B

↑

X

X

X

H

Q

N

→

Q

N+1

—

D

IO

A

Note: H = High-logic level

L = Low-logic level

X = Irrelevant

↑ = Low-to-high transition

↓ = High-to-low transition

* = Dependent on the previous stage’s state before the last CLK or last LE high

TRUTH FUNCTION TABLE

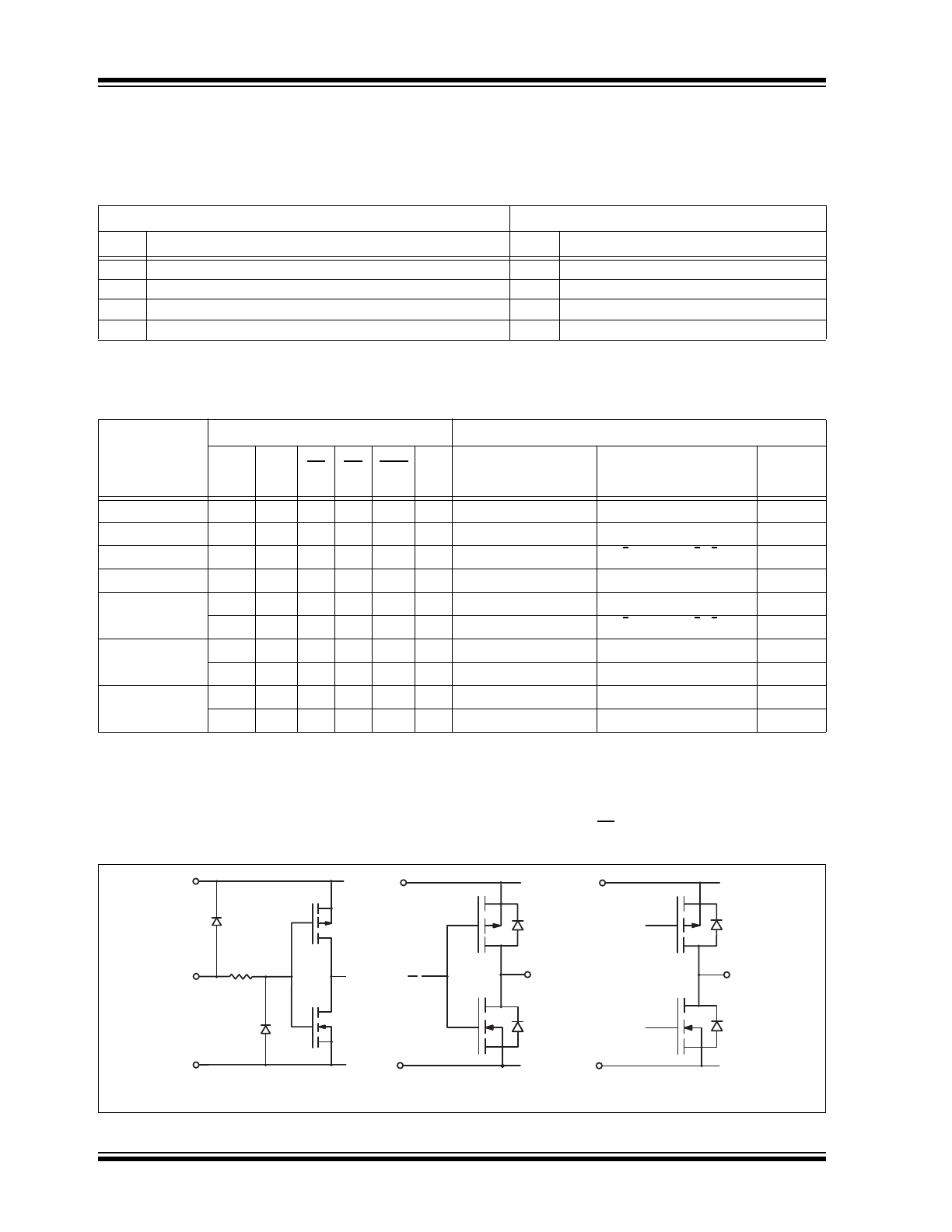

VDD

Input

GND

VPP

HVGND

HV

OUT

Logic Inputs

GND

Data Out

Logic Data Output

High Voltage Outputs

VDD

FIGURE 3-1:

Input and Output Equivalent Circuits.