2005 - 2016 Microchip Technology Inc.

DS00002105A-page 1

Highlights

• USB-IF “Hi-Speed” certified to the Universal Serial

Bus Specification Rev. 2.0

• Interface compliant with the UTMI+ Specification,

Rev. 1.0

• Functional as a host or device PHY

• Supports HS, FS, and LS data rates

• Supports FS pre-amble for FS hubs with a LS

device attached (UTMI+ Level 3)

• Supports HS SOF and LS keep alive pulse

• Low Latency Hi-Speed Receiver (43 Hi-Speed

clocks Max)

• Internal 1.8 volt regulators allow operation from a

single 3.3 volt supply

• Internal short circuit protection of DP and DM

lines to VBUS or ground

• Integrated 24MHz Crystal Oscillator supports

either crystal operation or 24MHz external clock

input

• Internal PLL for 480MHz Hi-Speed USB operation

• Supports Hi-Speed USB and legacy USB 1.1

devices

• 55mA Unconfigured Current (typical) - ideal for

bus powered applications

• 83uA suspend current (typical) - ideal for battery

powered applications

• Full Commercial operating temperature range

from 0

C to +70

C

• 40 pin QFN RoHS compliant package

(6 x 6 x 0.9mm height)

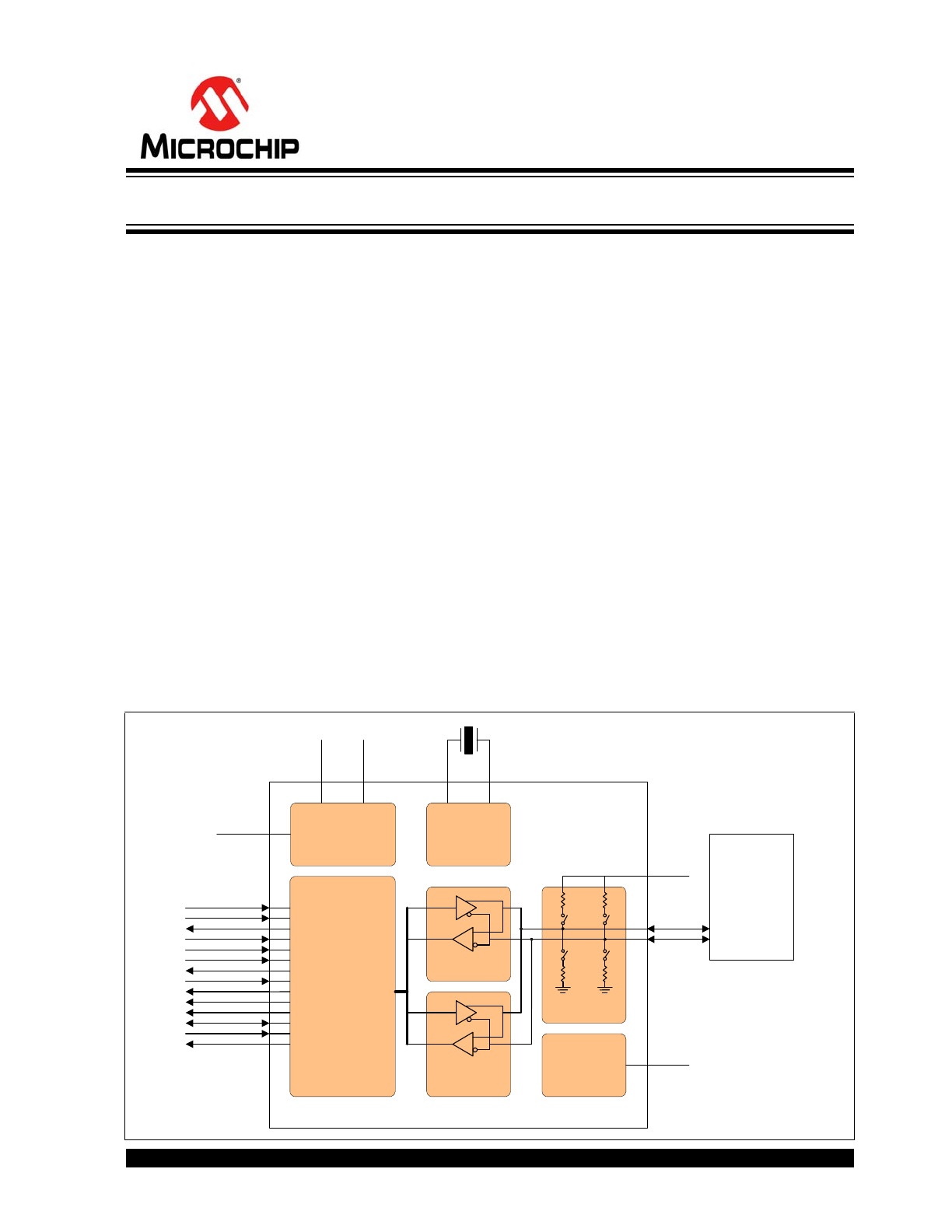

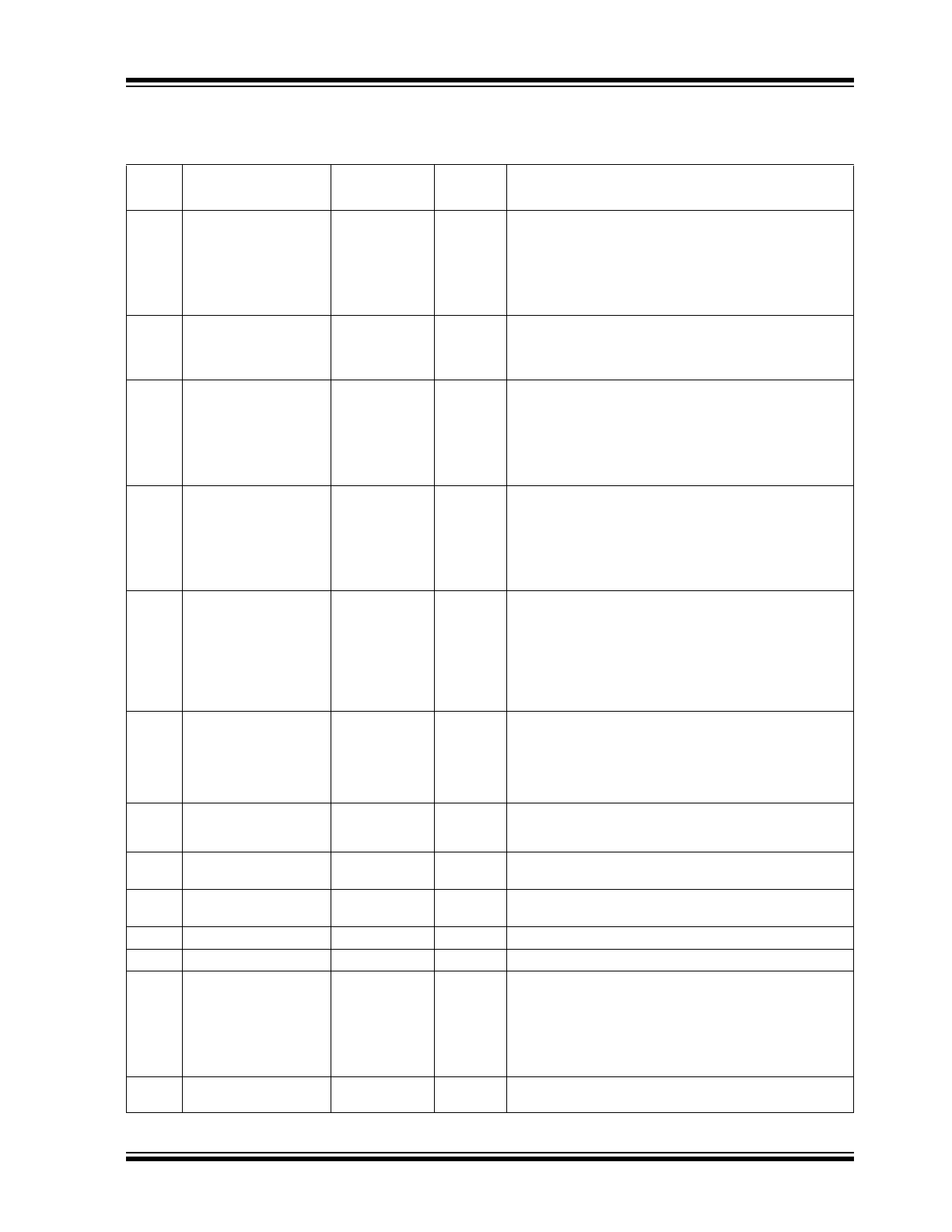

Functional Overview

The USB3450 is a highly integrated USB transceiver

system. It contains a complete Hi-Speed PHY with the

UTMI+ industry standard interface to support fast time

to market for a USB controller. The USB3450 is com-

posed of the functional blocks shown below.

USB3450 Block Diagram

UTMI+

Digital

24 MHz

XTAL

Internal

Regulator &

POR

Bias

Gen.

XCVRSEL[1:0]

VDD3.3

XTAL &

PLL

XI

VDD3.3

DP

DM

USB3450

V

DD1

.8

VD

DA1.

8

m

XO

RBIAS

Mini-AB

USB

Connector

HS XCVR

FS/LS

XCVR

Resistors

Rp

u_

dp

R

pd_d

m

Rp

d_d

p

Rp

u_

dm

TERMSEL

TXREADY

SUSPENDN

TXVALID

RESET

RXACTIVE

OPMODE[1:0]

CLKOUT

LINESTATE[1:0]

HOSTDISC

DATA[7:0]

HOST

RXERROR

USB3450

Hi-Speed USB Host or Device PHY With UTMI+ Interface

USB3450

DS00002105A-page 2

2005 - 2016 Microchip Technology Inc.

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at

docerrors@microchip.com

. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for cur-

rent devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the

revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site;

http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are

using.

Customer Notification System

Register on our web site at

www.microchip.com

to receive the most current information on all of our products.

2005 - 2016 Microchip Technology Inc.

DS00002105A-page 3

USB3450

Table of Contents

1.0 General Description ........................................................................................................................................................................ 4

2.0 Pin Configuration and Pin Definitions ............................................................................................................................................. 6

3.0 Limiting Values .............................................................................................................................................................................. 10

4.0 Electrical Characteristics ............................................................................................................................................................... 11

5.0 Detailed Functional Overview ....................................................................................................................................................... 14

6.0 Application Notes .......................................................................................................................................................................... 21

7.0 Package Outline ............................................................................................................................................................................ 33

Appendix A: Data Sheet Revision History ........................................................................................................................................... 35

The Microchip Web Site ...................................................................................................................................................................... 36

Customer Change Notification Service ............................................................................................................................................... 36

Customer Support ............................................................................................................................................................................... 36

Product Identification System ............................................................................................................................................................. 37

USB3450

DS00002105A-page 4

2005 - 2016 Microchip Technology Inc.

1.0

GENERAL DESCRIPTION

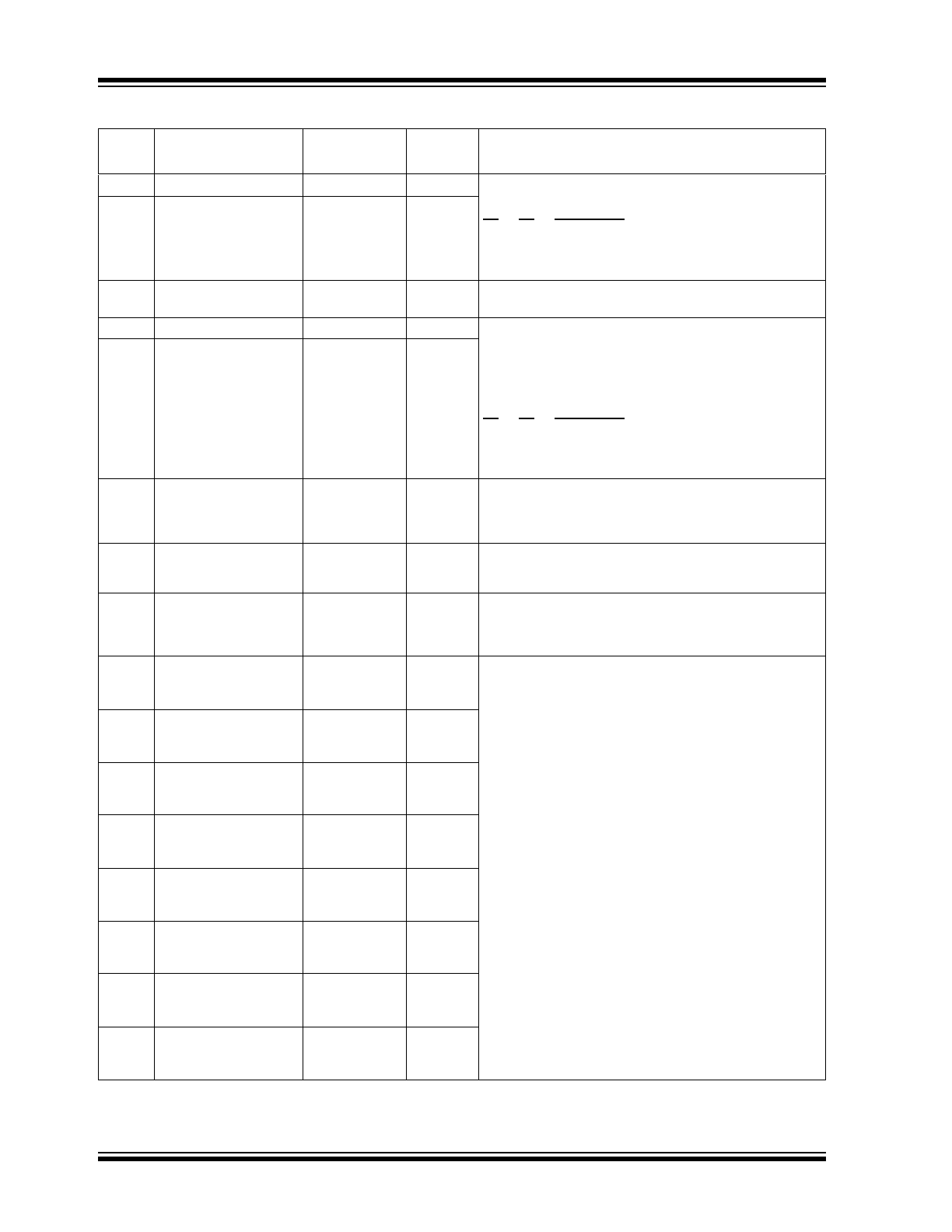

The USB3450 is a stand-alone Hi-Speed USB Physical Layer Transceiver (PHY). The USB3450 uses a UTMI+ interface

to connect to an SOC or ASIC or FPGA. Microchip’s advanced proprietary technology minimizes power dissipation,

resulting in maximum battery life for portable applications. The USB3450 is a flexible solution for adding USB to new

designs without integrating the analog PHY block.

The USB3450 provides a fully compliant Hi-Speed interface, and supports Hi-Speed (HS), Full-Speed (FS), and Low-

Speed (LS) USB. The USB3450 supports all levels of the UTMI+ specification as shown in

Figure 1-2

.

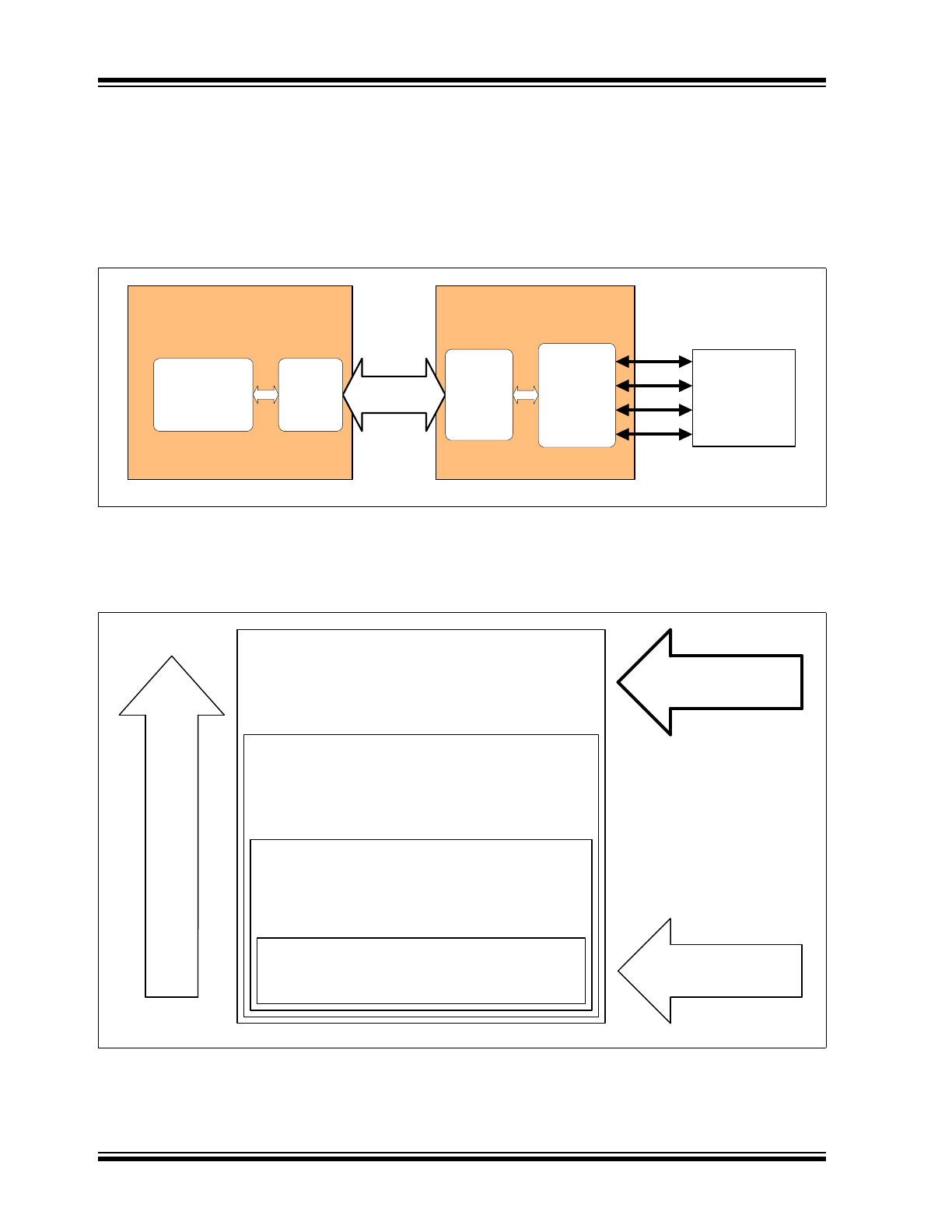

FIGURE 1-1:

BASIC UTMI+ USB DEVICE BLOCK DIAGRAM

FIGURE 1-2:

UTMI+ LEVEL 3 SUPPORT

SOC/FPGA/ASIC

Including Device Controller

USB3450

Hi-

Speed

Analog

USB

Connector

(Standard

or Mini)

DM

V

BUS

DP

ID

Hi-Speed

USB App.

UTMI+

Interface

UTMI+

Digital

Logic

UTMI+

Link

UTMI+ Level 0

Hi-Speed Peripherals Only

AD

DED

FEA

T

URE

S

USB3450

USB3500

UTMI+ Level 3

Hi-Speed Peripheral, host controllers, On-

the-Go devices

(HS, FS, LS, preamble packet)

UTMI+ Level 2

Hi-Speed Peripheral, host controllers, On-

the-Go devices

(HS, FS, and LS but no preamble packet)

UTMI+ Level 1

Hi-Speed Peripheral, host controllers,

and On-the-Go devices

(HS and FS Only)

USB3280

USB3250

2005 - 2016 Microchip Technology Inc.

DS00002105A-page 5

USB3450

1.1

Applications

The USB3450 is targeted for any application where a high speed USB connection is desired.

The USB3450 is well suited for:

• Cell Phones

• MP3 Players

• Scanners

• Set Top Boxes

• Printers

• External Hard Drives

• Still and Video Cameras

• Portable Media Players

• Entertainment Devices

1.2

Reference Documents

• Universal Serial Bus Specification, Revision 2.0, April 27, 2000

• Hi-Speed Transceiver Macrocell Interface (UTMI) Specification, Version 1.02, May 27, 2000

• UTMI+ Specification, Revision 1.0, February 2, 2004

USB3450

DS00002105A-page 6

2005 - 2016 Microchip Technology Inc.

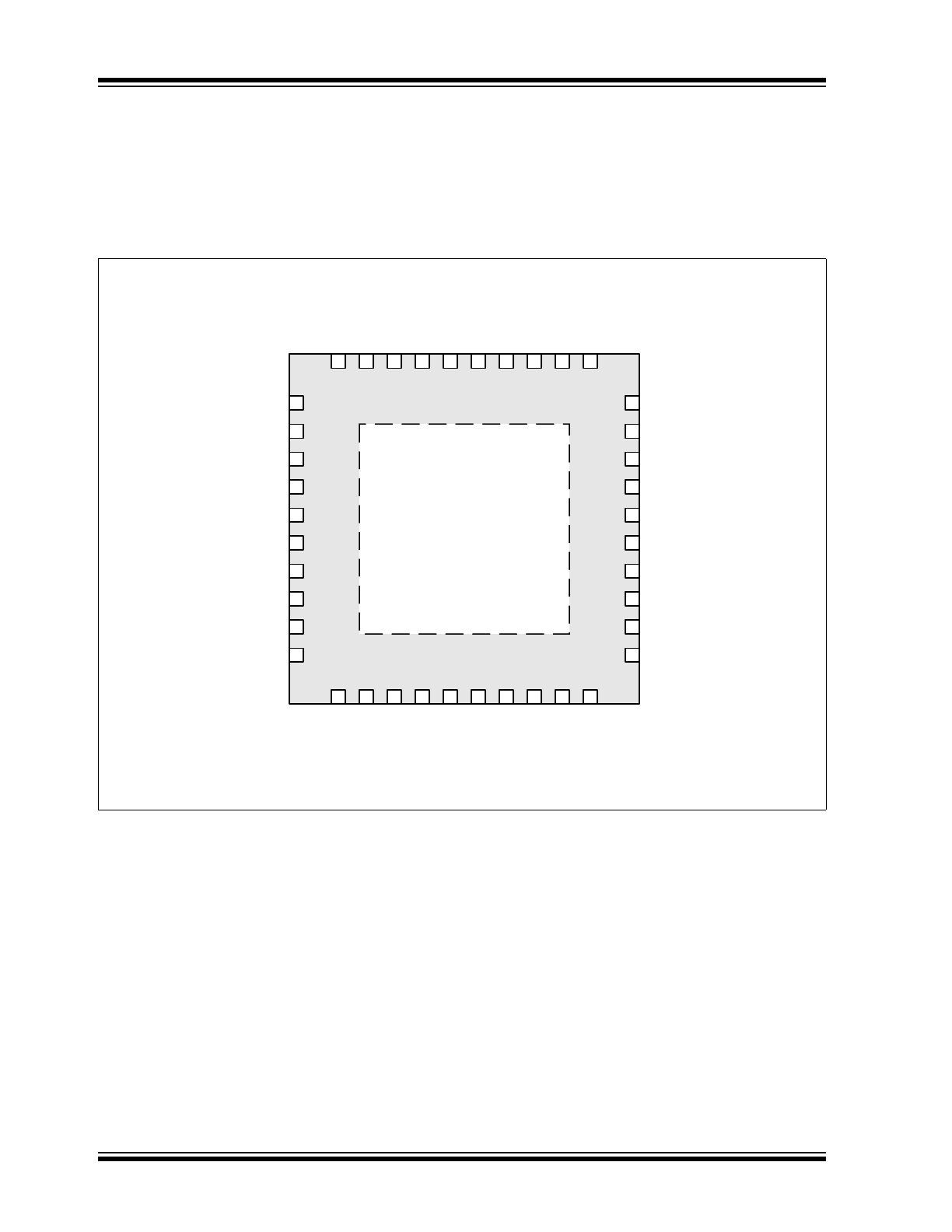

2.0

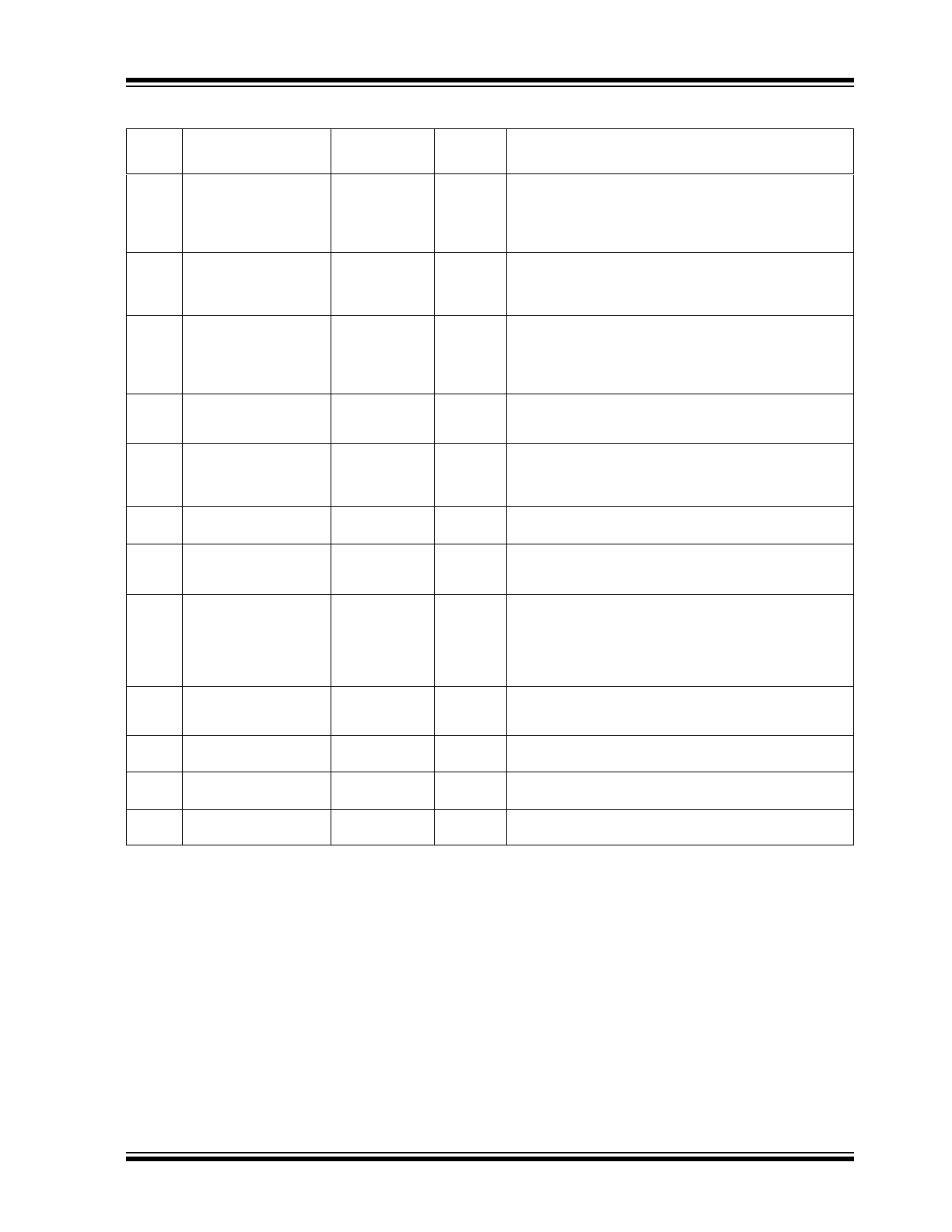

PIN CONFIGURATION AND PIN DEFINITIONS

The USB3450 is offered in a 40 pin QFN package. The pin definitions and locations are documented below.

2.1

USB3450 Pin Locations

The flag of the QFN package must be connected to ground.

FIGURE 2-1:

USB3450 PINOUT - TOP VIEW

XCVRS

E

L1

L

INE

ST

A

T

E[

0]

L

INE

ST

A

T

E[

1]

OP

MO

DE

[1

]

OP

MO

DE

[0

]

VDD3

.3

RXA

C

T

IVE

CL

KO

U

T

VDD1

.8

VDD3

.3

DATA[1]

DATA[0]

DATA[2]

DATA[3]

DATA[4]

DATA[5]

DATA[6]

DATA[7]

RXVALID

HOSTDISC

RBIAS

VDD3

.3

VDD3

.3

VDDA

1.

8

XI

XO

VDD1

.8

VDD3

.3

RXER

ROR

HOST

DM

DP

VDD3.3

RESET

TXVALID

SUSPENDN

TXREADY

TERMSEL

XCVRSEL0

NC

10

15

16

17

18

19

11

12

13

14

20

21

22

24

25

26

27

28

29

30

23

34

33

32

31

40

39

38

37

36

35

1

2

3

4

5

6

7

8

9

USB3450

Hi-Speed USB

UTMI+ PHY

40 Pin QFN

GND FLAG

2005 - 2016 Microchip Technology Inc.

DS00002105A-page 7

USB3450

2.2

Pin Definitions

TABLE 2-1:

USB3450 PIN DEFINITIONS

Pin

Name

Direction,

Type

Active

Level

Description

1

XCVRSEL[0]

Input

N/A

Transceiver Select. These signals select between the

FS and HS transceivers:

Transceiver select.

00: HS

01: FS

10: LS

11: LS data, FS rise/fall times

2

TERMSEL

Input

N/A

Termination Select. This signal selects between the

FS and HS terminations:

0: HS termination enabled

1: FS termination enabled

3

TXREADY

Output

High

Transmit Data Ready. If TXVALID is asserted, the Link

must always have data available for clocking into the

TX Holding Register on the rising edge of CLKOUT.

TXREADY is an acknowledgment to the Link that the

transceiver has clocked the data from the bus and is

ready for the next transfer on the bus. If TXVALID is

negated, TXREADY can be ignored by the Link.

4

SUSPENDN

Input

Low

Suspend. Places the transceiver in a mode that draws

minimal power from supplies. In host mode, R

PU

is

removed during suspend. In device mode, R

PD

is

controlled by TERMSEL. In suspend mode the clocks

are off.

0: PHY in suspend mode

1: PHY in normal operation

5

TXVALID

Input

High

Transmit Valid. Indicates that the DATA bus is valid for

transmit. The assertion of TXVALID initiates the

transmission of SYNC on the USB bus. The negation

of TXVALID initiates EOP on the USB.

Control inputs (OPMODE[1:0],

TERMSEL,XCVERSEL) must not be changed on the

de-assertion or assertion of TXVALID.

6

RESET

Input

High

Reset. Reset all state machines. After coming out of

reset, must wait 5 rising edges of clock before

asserting TXValid for transmit.

Assertion of Reset: May be asynchronous to CLKOUT

De-assertion of Reset: Must be synchronous to

CLKOUT

7

VDD3.3

N/A

N/A

3.3V PHY Supply. Provides power for Hi-Speed

Transceiver, UTMI+ Digital, Digital I/O, and

Regulators.

8

DP

I/O,

Analog

N/A

D+ pin of the USB cable.

9

DM

I/O,

Analog

N/A

D- pin of the USB cable.

10

NC

N/A

N/A

No Connect.

11

VDD3.3

N/A

N/A

3.3V PHY Supply.

12

XCVRSEL[1]

Input

N/A

Transceiver Select. These signals select between the

FS and HS transceivers:

Transceiver select.

00: HS

01: FS

10: LS

11: LS data, FS rise/fall times

13

RXACTIVE

Output

High

Receive Active. Indicates that the receive state

machine has detected Start of Packet and is active.

USB3450

DS00002105A-page 8

2005 - 2016 Microchip Technology Inc.

14

OPMODE[1]

Input

N/A

Operational Mode. These signals select between the

various operational modes:

[1] [0] Description

0 0 0: Normal Operation

0 1 1: Non-driving (all terminations removed)

1 0 2: Disable bit stuffing and NRZI encoding

1 1 3: Reserved

15

OPMODE[0]

Input

N/A

16

CLKOUT

Output,

CMOS

N/A

60MHz reference clock output. All UTMI+ signals are

driven synchronous to this clock.

17

LINESTATE[1]

Output

N/A

Line State. These signals reflect the current state of

the USB data bus in FS mode. Bit [0] reflects the state

of DP and bit [1] reflects the state of DM. When the

device is suspended or resuming from a suspended

state, the signals are combinatorial. Otherwise, the

signals are synchronized to CLKOUT.

[1] [0] Description

0 0 0: SEO

0 1 1: J State

1 0 2: K State

1 1 3: SE1

18

LINESTATE[0]

Output

N/A

19

VDD1.8

N/A

N/A

1.8V regulator output for digital circuitry on chip. Place

a 0.1uF capacitor near this pin and connect the

capacitor from this pin to ground. Connect pin 19 to

pin 34.

20

VDD3.3

N/A

N/A

3.3V PHY Supply. Provides power for Hi-Speed

Transceiver, UTMI+ Digital, Digital I/O, and

Regulators.

21

HOSTDISC

Output

High Host

Disconnect.

Indicates that a downstream device

has been disconnected from this host PHY when

operating in HS host mode. Automatically reset to 0b

when Low Power Mode is entered.

22

DATA[7]

I/O,

CMOS,

Pull-low

N/A

8-bit bi-directional data bus. Data[7] is the MSB and

Data[0] is the LSB.

23

DATA[6]

I/O,

CMOS,

Pull-low

N/A

24

DATA[5]

I/O,

CMOS,

Pull-low

N/A

25

DATA[4]

I/O,

CMOS,

Pull-low

N/A

26

DATA[3]

I/O,

CMOS,

Pull-low

N/A

27

DATA[2]

I/O,

CMOS,

Pull-low

N/A

28

DATA[1]

I/O,

CMOS,

Pull-low

N/A

29

DATA[0]

I/O,

CMOS,

Pull-low

N/A

TABLE 2-1:

USB3450 PIN DEFINITIONS (CONTINUED)

Pin

Name

Direction,

Type

Active

Level

Description

2005 - 2016 Microchip Technology Inc.

DS00002105A-page 9

USB3450

30

RXVALID

Output

High

Receive Data Valid. Indicates that the DATA bus has

received valid data. The Receive Data Holding

Register is full and ready to be unloaded. The Link is

expected to register the DATA bus on the rising edge

of CLKOUT.

31

HOST

Input

N/A

Host Pull-down Select. This signal enables the 15k

Ohm pull-down resistor on the DM line.

0: Pull-down resistor not connected to DM

1: Pull-down resistor connected to DM

32

RXERROR

Output

High

Receive Error. This output is clocked with the same

timing as the receive DATA lines and can occur at

anytime during a transfer.

0: Indicates no error.

1: Indicates a receive error has been detected.

33

VDD3.3

N/A

N/A

3.3V PHY Supply. Provides power for Hi-Speed

Transceiver, UTMI+ Digital, Digital I/O, and

Regulators.

34

VDD1.8

N/A

N/A

1.8V regulator output for digital circuitry on chip. Place

a 4.7uF low ESR capacitor near this pin and connect

the capacitor from this pin to ground. Connect pin 34

to pin 19. See

Section 5.6.1, "Internal Regulators"

.

35

XO

Output,

Analog

N/A

Crystal pin. If using an external clock on XI this pin

should be floated.

36

XI

Input,

Analog

N/A

Crystal pin. A 24MHz crystal is supported. The crystal

is placed across XI and XO. An external 24MHz clock

source may be driven into XI in place of a crystal.

37

VDDA1.8

N/A

N/A

1.8V regulator output for analog circuitry on chip.

Place a 0.1uF capacitor near this pin and connect the

capacitor from this pin to ground. In parallel, place a

4.7uF low ESR capacitor near this pin and connect the

capacitor from this pin to ground. See

Section 5.6.1,

"Internal Regulators"

.

38

VDD3.3

N/A

N/A

3.3V PHY Supply. Provides power for Hi-Speed

Transceiver, UTMI+ Digital, Digital I/O, and

Regulators.

39

VDD3.3

N/A

N/A

3.3V PHY Supply. Should be connected directly to pin

39.

40

RBIAS

Analog,

CMOS

N/A

External 1% bias resistor. Requires a 12KΩ resistor to

ground.

GND FLAG

Ground

N/A

Ground. The flag must be connected to the ground

plane.

TABLE 2-1:

USB3450 PIN DEFINITIONS (CONTINUED)

Pin

Name

Direction,

Type

Active

Level

Description

USB3450

DS00002105A-page 10

2005 - 2016 Microchip Technology Inc.

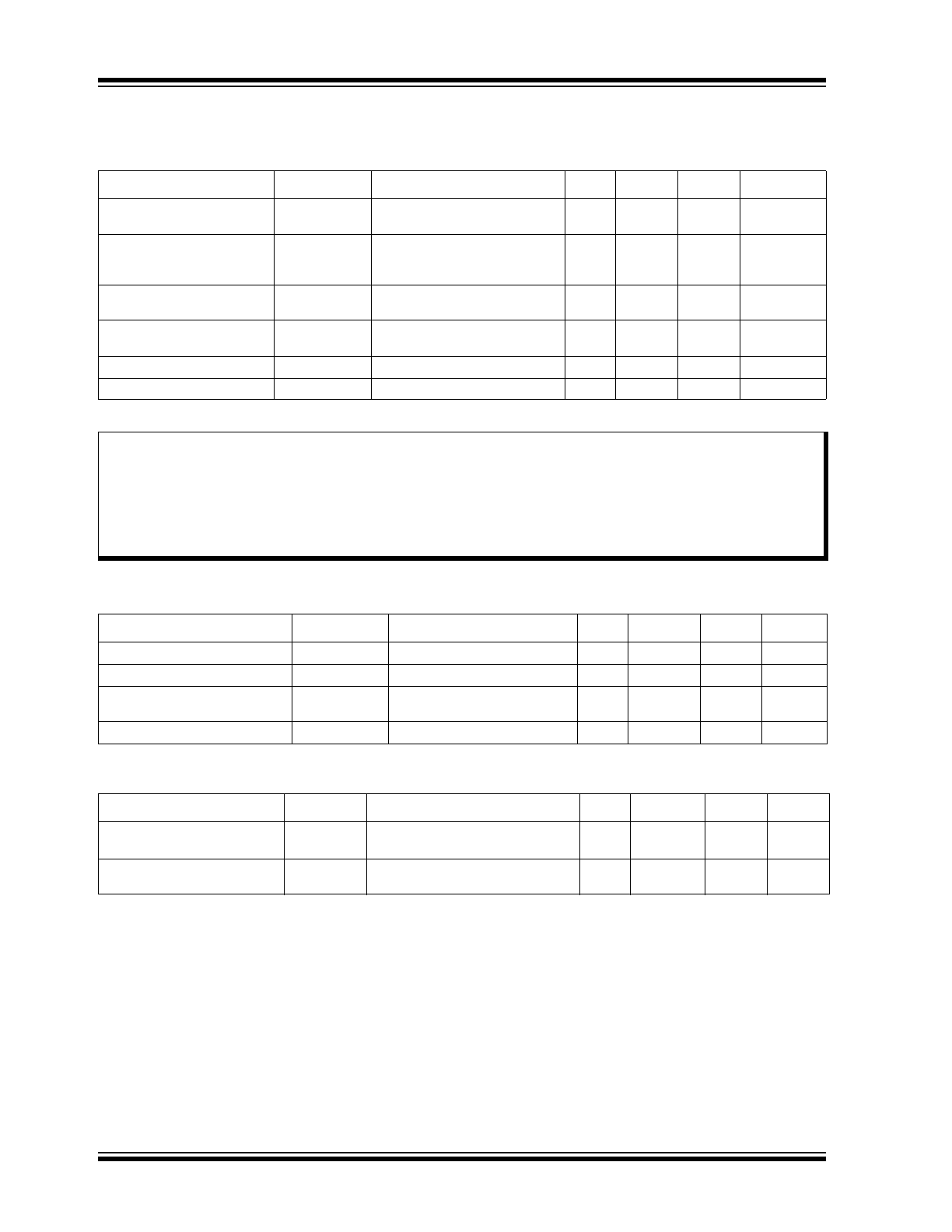

3.0

LIMITING VALUES

TABLE 3-1:

MAXIMUM RATINGS

Parameter

Symbol

Conditions

MIN

TYP MAX Units

Maximum VBUS, ID, DP,

and DM voltage to GND

V

MAX_5V

-0.5

+5.5

V

Maximum VDD1.8 and

VDDA1.8 voltage to

Ground

V

MAX_1.8V

-0.5

2.5

V

Maximum 3.3V supply

voltage to Ground

V

MAX_3.3V

-0.5

4.0

V

Maximum I/O voltage to

Ground

V

MAX_IN

-0.5

4.0

V

Operating Temperature

T

MAX_OP

0

70

C

Storage Temperature

T

MAX_STG

-55

150

C

Note:

Stresses above those listed could cause damage to the device. This is a stress rating only and functional

operation of the device at any other condition above those indicated in the operation sections of this spec-

ification is not implied. When powering this device from laboratory or system power supplies, it is important

that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies

exhibit voltage spikes on their outputs when the AC power is switched on or off. In addition, voltage tran-

sients on the AC power line may appear on the DC output. If this possibility exists, it is suggested that a

clamp circuit be used.

TABLE 3-2:

RECOMMENDED OPERATING CONDITIONS

Parameter

Symbol

Conditions

MIN

TYP MAX

Units

3.3V Supply Voltage

V

DD3.3

3.0

3.3

3.6

V

Input Voltage on Digital Pins V

I

0.0

V

DD3.3

V

Input Voltage on Analog I/O

Pins (DP, DM)

V

I(I/O)

0.0

V

DD3.3

V

Ambient Temperature

T

A

0

+70

o

C

TABLE 3-3:

RECOMMENDED EXTERNAL CLOCK CONDITIONS

Parameter

Symbol

Conditions

MIN

TYP MAX

Units

System Clock Frequency

XI driven by the external clock;

and no connection at XO

24

(±

100ppm

)

MHz

System Clock Duty Cycle

XI driven by the external clock;

and no connection at XO

45

50

55

%