2007 - 2016 Microchip Technology Inc.

DS000002248A-page 1

Highlights

• Integrated USB 2.0 Compatible 2-Port Hub

- High-Speed (480Mbits/s), Full-Speed

(12Mbits/s) and Low-Speed (1.5Mbits/s)

compatible

- Full power management with ganged power

control

- Detects Bus-Power/Self-Power source and

changes mode automatically

• Complete USB Specification 2.0 Compatibility

- Includes USB 2.0 Transceivers

• VID/PID/DID, and Port Configuration for Hub via:

- Single Serial I

2

C EEPROM

- SMBus Slave Port

• Default VID/PID/DID, allows functionality when

configuration EEPROM is absent

• Hardware Strapping options allow for configura-

tion without an external EEPROM or SMBus Host

• On-Board 24MHz Crystal Driver Circuit or 24 MHz

external clock driver

• Internal PLL for 480MHz USB 2.0 Sampling

• Internal 1.8V Linear Voltage Regulator

• Integrated USB termination and Pull-up/Pull-down

resistors

• Internal Short Circuit protection of USB differential

signal pins

• Basic single-color LED support

• 1.8 Volt Low Power Core Operation

• 3.3 Volt I/O with 5V Input Tolerance

• 36-Pin QFN or 48-Pin TQFP RoHS compliant

package

USB2502

2-Port USB 2.0 Hub Controller

USB2502

DS000002248A-page 2

2007 - 2016 Microchip Technology Inc.

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at

docerrors@microchip.com

. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for cur-

rent devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the

revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site;

http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are

using.

Customer Notification System

Register on our web site at

www.microchip.com

to receive the most current information on all of our products.

2007 - 2016 Microchip Technology Inc.

DS000002248A-page 3

USB2502

Table of Contents

1.0 Introduction ..................................................................................................................................................................................... 4

2.0 Pin Table 2-Port .............................................................................................................................................................................. 5

3.0 Pin Configuration 2-Port Hub .......................................................................................................................................................... 6

4.0 2-Port Hub Block Diagram .............................................................................................................................................................. 8

5.0 Functional Block Description ......................................................................................................................................................... 12

6.0 XNOR Test .................................................................................................................................................................................... 29

7.0 DC Parameters ............................................................................................................................................................................. 30

8.0 AC Specifications .......................................................................................................................................................................... 33

9.0 Package Outlines .......................................................................................................................................................................... 34

Appendix A: Data Sheet Revision History ........................................................................................................................................... 36

The Microchip Web Site ...................................................................................................................................................................... 37

Customer Change Notification Service ............................................................................................................................................... 37

Customer Support ............................................................................................................................................................................... 37

Product Identification System ............................................................................................................................................................. 38

USB2502

DS000002248A-page 4

2007 - 2016 Microchip Technology Inc.

1.0

INTRODUCTION

The Microchip 2-Port Hub is fully compliant with the USB 2.0 Specification and will attach to a USB host as a Full-Speed

Hub or as a Full-/High-Speed Hub. The 2-Port Hub supports Low-Speed, Full-Speed, and High-Speed (if operating as

a High-Speed Hub) downstream devices on all of the enabled downstream ports.

The Hub works with an external USB power distribution switch device to control V

BUS

switching to downstream ports,

and to limit current and sense over-current conditions.

All required resistors on the USB ports are integrated into the Hub. This includes all series termination resistors on D+

and D– pins and all required pull-down and pull-up resistors on D+ and D– pins. The over-current sense inputs for the

downstream facing ports have internal pull-up resistors.

Throughout this document the upstream facing port of the hub will be referred to as the upstream port, and the down-

stream facing ports will be called the downstream ports.

1.1

OEM Selectable Features

A default configuration is available in the USB2502 following a reset. This configuration may be sufficient for some appli-

cations. Strapping option pins make it possible to modify a limited sub-set of the configuration options.

The USB2502 may also be configured by an external EEPROM or a microcontroller. When using the microcontroller

interface, the Hub appears as an SMBus slave device. If the Hub is pin-strapped for external EEPROM configuration

but no external EEPROM is present, then a value of ‘0’ will be written to all configuration data bit fields (the hub will

attach to the host with all ‘0’ values).

The 2-Port Hub supports several OEM selectable features:

• Operation as a Self-Powered USB Hub or as a Bus-Powered USB Hub.

• Operation as a Dynamic-Powered Hub (Hub operates as a Bus-Powered device if a local power source is not

available and switches to Self-Powered operation when a local power source is available).

• Optional OEM configuration via I

2

C EEPROM or via the industry standard SMBus interface from an external

SMBus Host.

• Compound device support (port is permanently hardwired to a downstream USB peripheral device).

• Hardware strapping options enable configuration of the following features.

- Non-Removable Ports

- Port Power Polarity (active high or active low logic)

2007 - 2016 Microchip Technology Inc.

DS000002248A-page 5

USB2502

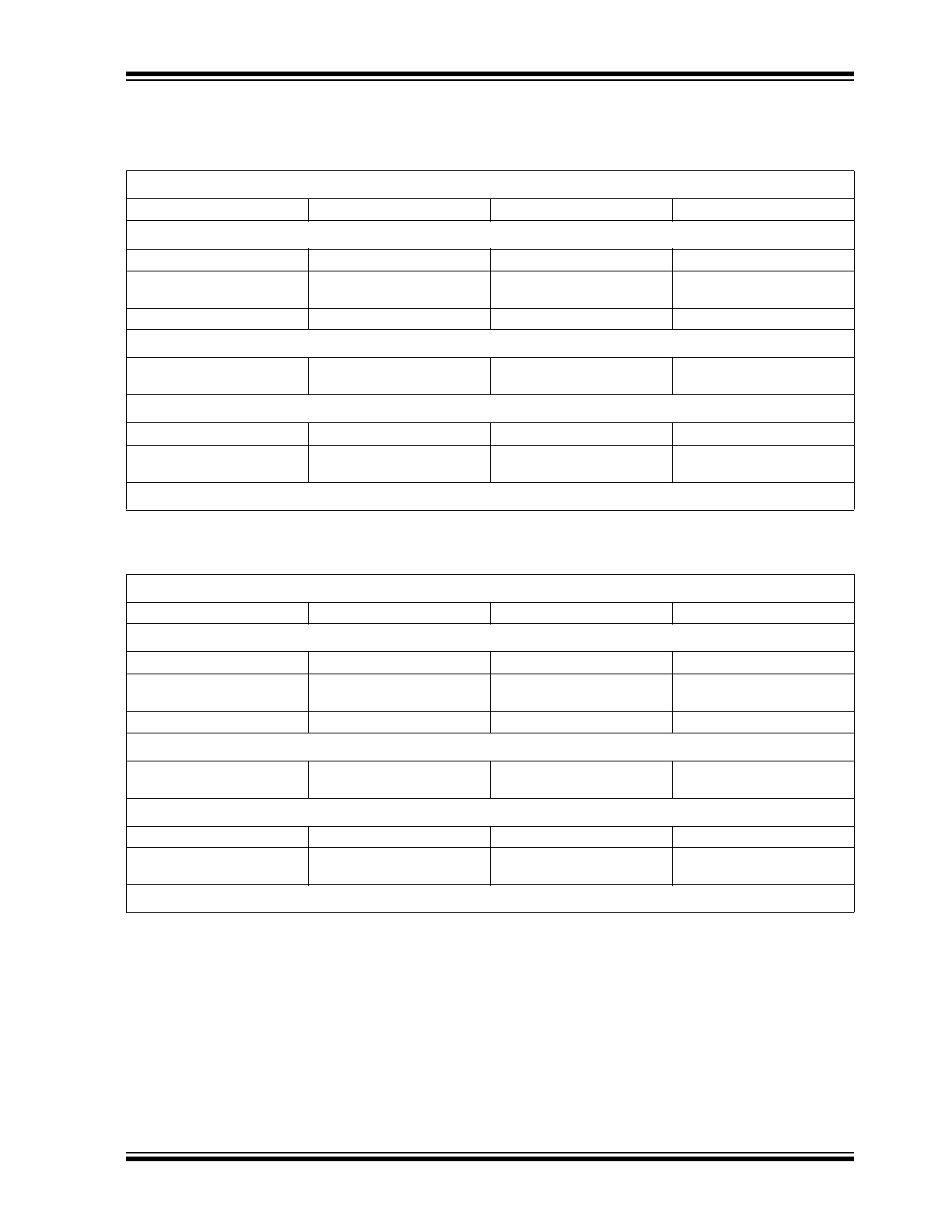

2.0

PIN TABLE 2-PORT

TABLE 2-1:

2-PORT PIN TABLE FOR 36-QFN

UPSTREAM USB 2.0 INTERFACE (3 PINS)

USBDP0

USBDN0

VBUS_DET

2-PORT USB 2.0 INTERFACE (10 PINS)

USBDP1

USBDN1

USBDP2

USBDN2

GR1/

NON_REM0

GR2/

NON_REM1

PRTPWR_POL

RBIAS

PRTPWR

OCS_N

SERIAL PORT INTERFACE (3 PINS)

SDA/SMBDATA

SCL/SMBCLK/

CFG_SEL0

CFG_SEL1

MISC (7 PINS)

XTAL1/CLKIN

XTAL2

RESET_N

SELF_PWR

ATEST/

REG_EN

CLKIN_EN

TEST

POWER, GROUND (13 PINS)

TABLE 2-2:

2-PORT PIN TABLE FOR 48-TQFP

UPSTREAM USB 2.0 INTERFACE (3 PINS)

USBDP0

USBDN0

VBUS_DET

2-PORT USB 2.0 INTERFACE (10 PINS)

USBDP1

USBDN1

USBDP2

USBDN2

GR1/

NON_REM0

GR2/

NON_REM1

PRTPWR_POL

RBIAS

PRTPWR

OCS_N

SERIAL PORT INTERFACE (3 PINS)

SDA/SMBDATA

SCL/SMBCLK

CFG_SEL0

CFG_SEL1

MISC (7 PINS)

XTAL1/CLKIN

XTAL2

RESET_N

SELF_PWR

ATEST/

REG_EN

CLKIN_EN

TEST

POWER, GROUND AND NO CONNECT (25 PINS)

USB2502

DS000002248A-page 6

2007 - 2016 Microchip Technology Inc.

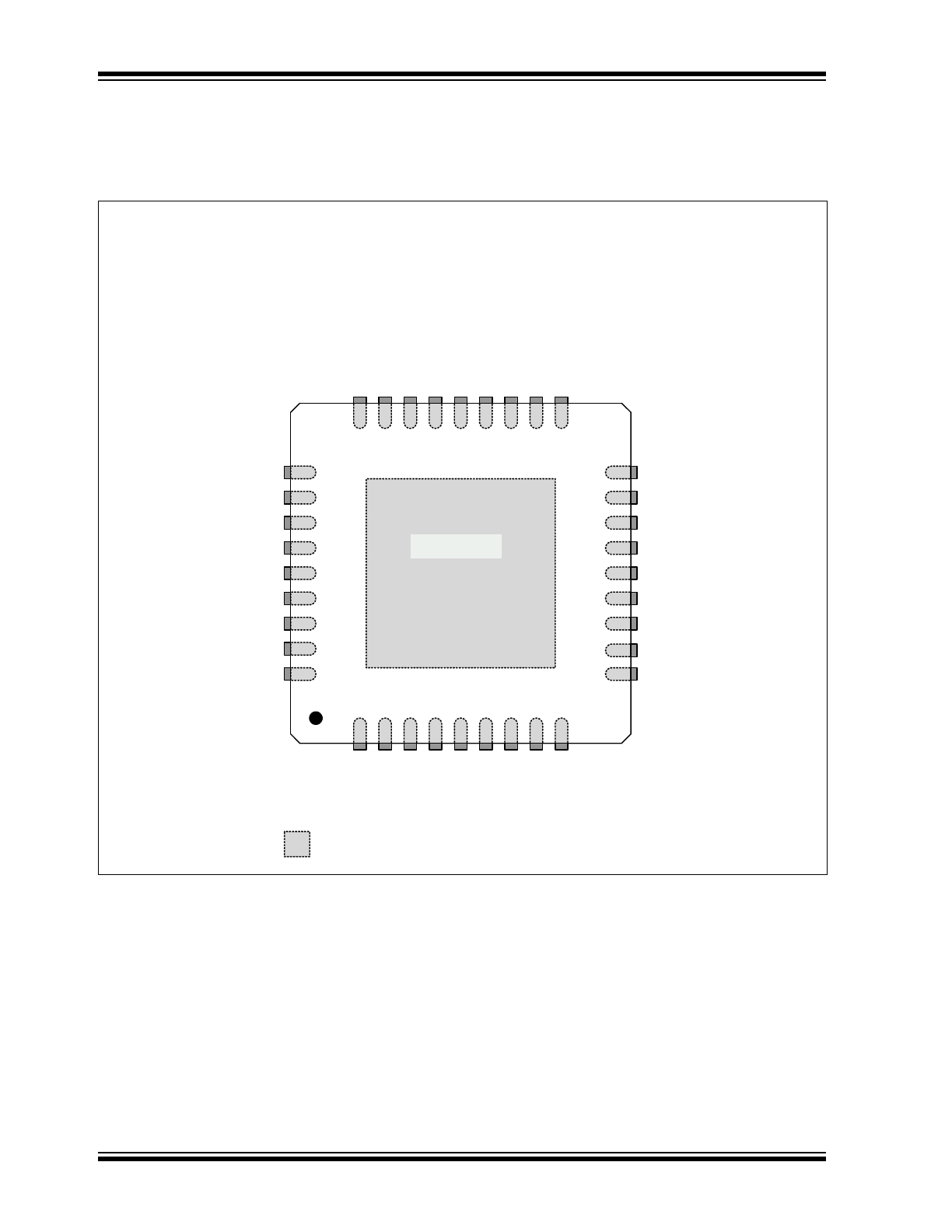

3.0

PIN CONFIGURATION 2-PORT HUB

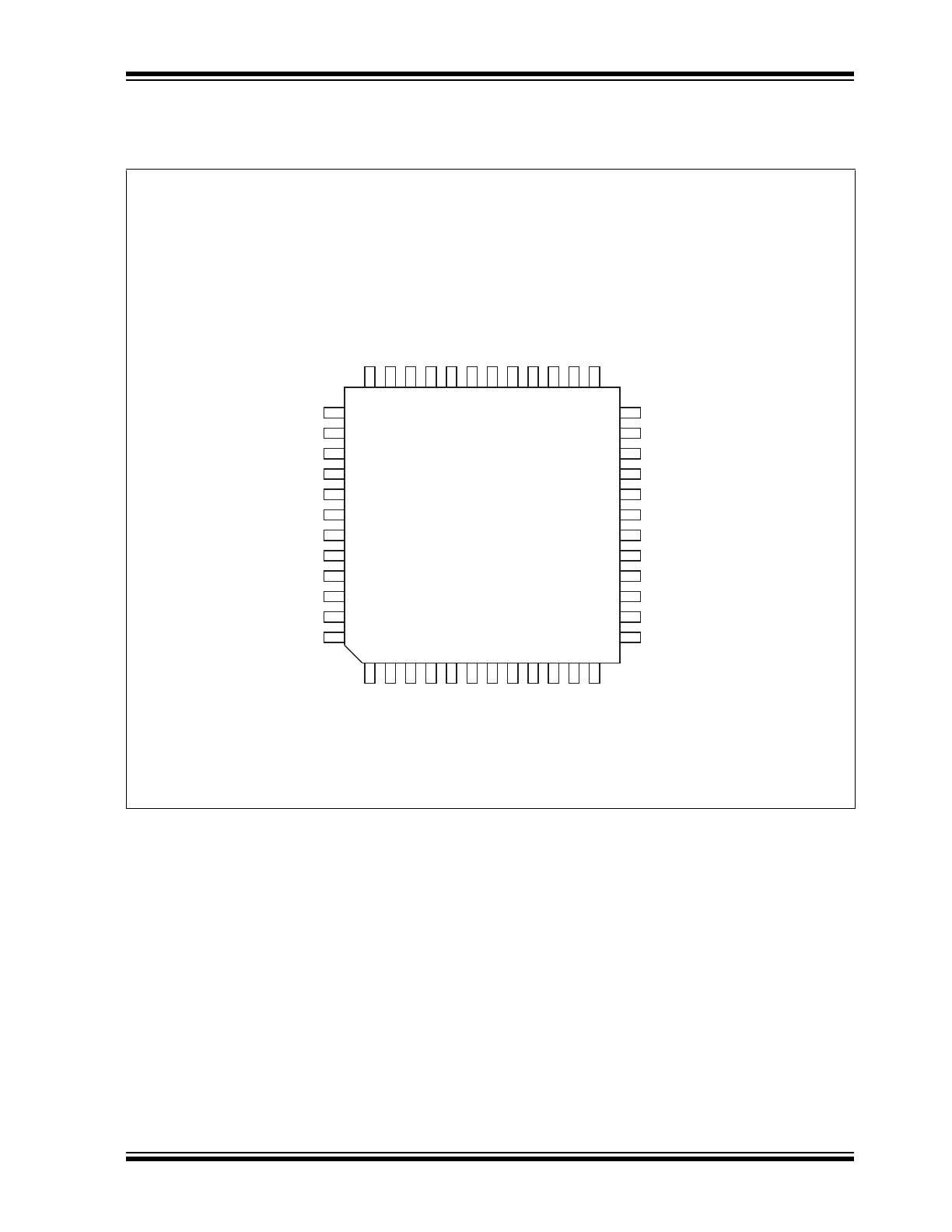

FIGURE 3-1:

2-PORT 36-PIN QFN

Thermal Slug

(must be connected to VSS)

SMSC

USB2502

(Top View QFN-36)

Indicates pins on the bottom of the device.

VDD

A

3

3

1

USBDP

0

2

USBDN0

3

VSS

4

USBDN1

5

USBDP

1

6

VDD

A

3

3

7

USBDP

2

8

USBDN2

9

18

VDD18

17

VSS

16

SELF_PWR

15

OCS_N

14

PRTPWR

13

PRTPWR_POL

12

GR2/NON_REM1

11

GR1/NON_REM0

10

VSS

VDD33CR

28

VSS

29

XTAL1/CLKIN

31

VDDA18PLL

32

VDDA33PLL

33

VSS

36

RBIAS

35

ATEST/REG_EN

34

XTAL2

30

26

VSS

25

VBUS_DET

24

R

E

SET

_

N

23

TEST

2

2

CL

KIN_

EN

21

CFG_SEL1

20

SCL/SM

BCLK

/CFG_SEL0

19

SDA

/SM

BDA

T

A

27

VD

D1

8

MICROCHIP

2007 - 2016 Microchip Technology Inc.

DS000002248A-page 7

USB2502

FIGURE 3-2:

2-PORT 48-PIN TQFP

VDD33CR

VSS

XTAL2

XTAL1/CLKIN

VDDA18PLL

VDDA33PLL

VDD18

VSS

GR1/NON_REM0

GR2/NON_REM1

SELF_PWR

PRTPWR_POL

PRTPWR

VDDA33

ATEST/REG_EN

RBIAS

VSS

OCS_N

USBDP0

USBDN0

VSS

VSS

USBDN1

USBDP1

VDDA33

VDDA33

USBDP2

USBDN2

VSS

NC

NC

VDD18

VSS

VSS

VBUS_DET

RESET

TEST

CLKIN_EN

CFG_SEL1

SCL/SMBCLK/CFG_SEL0

SDA/SMBDA

T

A

NC

NC

NC

NC

VDD33CR

VSS

VDDA18PLL

USB2502

48-TQFP

USB2502

DS000002248A-page 8

2007 - 2016 Microchip Technology Inc.

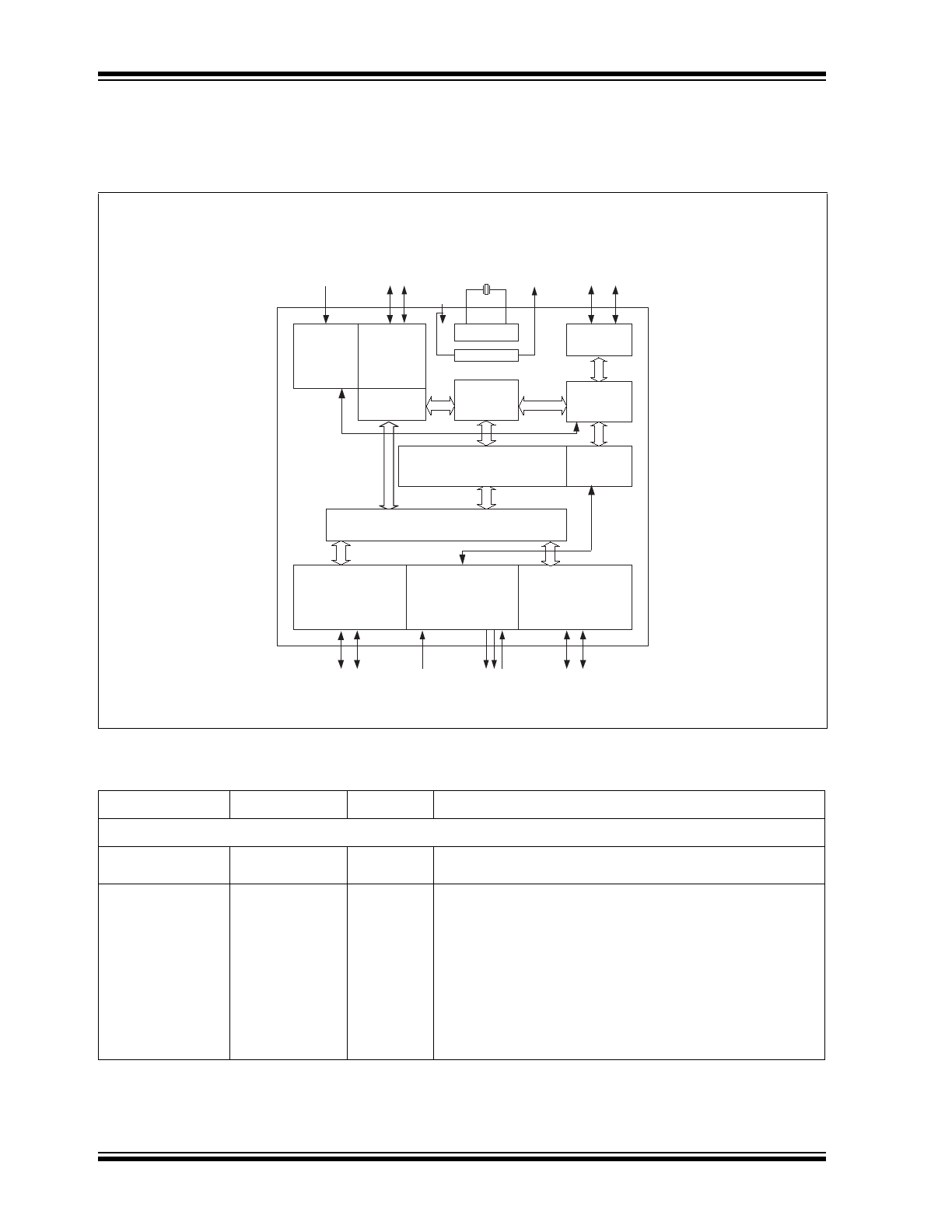

4.0

2-PORT HUB BLOCK DIAGRAM

FIGURE 4-1:

2-PORT BLOCK DIAGRAM

TABLE 4-1:

2-PORT HUB PIN DESCRIPTIONS

Name

Symbol

Type

Function

UPSTREAM USB 2.0 INTERFACE

USB Bus Data

USBDN0

USBDP0

IO-U

These pins connect to the upstream USB bus data signals.

Detect Upstream

VBUS Power

VBUS_DET

I/O8

Detects state of Upstream VBUS power. The Microchip Hub

monitors VBUS_DET to determine when to assert the internal

D+ pull-up resistor (signaling a connect event).

When designing a detachable hub, this pin must be

connected to the VBUS power pin of the USB port that is

upstream of the hub. (Use of a weak pull-down resistor is

recommended.)

For self-powered applications with a permanently attached

host, this pin must be pulled-up to either 3.3V or 5.0V

(typically VDD33).

Upstream

V

BUS

3.3V

Upstream

PHY

Upstream

USB Data

Repeater

Controller

SIE

Serial

Interface

PLL

24 MHz

Crystal

To EEPROM or

SMBus Master

Routing Logic

SCK

SD

Port

Controller

Downstream PHY #1

OC Sense

Switch Driver

LED Driver

Strapping Options

Downstream PHY #2

Downstream

USB Data

OC

Sense

Switch/LED

Driver/optís

Downstream

USB Data

Bus-Power

Detect

1.8V

Transaction Translator

1.8V Reg

2007 - 2016 Microchip Technology Inc.

DS000002248A-page 9

USB2502

2-PORT USB 2.0 HUB INTERFACE

High-Speed USB

Data

USBDN[2:1]

USBDP[2:1]

IO-U

These pins connect to the downstream USB peripheral

devices attached to the Hub’s ports.

USB Power Enable

PRTPWR

O8

Enables power to USB peripheral devices (downstream).

The active signal level of the PRTPWR pin is determined by

the Power Polarity Strapping function of the PRTPWR_POL

pin.

Port [2:1] Green

LED

&

Port Non-

Removable

strapping option.

GR[2:1]/

NON_REM[1:0]

I/O8

Green indicator LED for ports 2 and 1. Will be active low

when LED support is enabled via EEPROM or SMBus.

If the hub is configured by the internal default configuration,

these pins will be sampled at the rising edge of RESET_N

(see the applicable RESET_N timing table in

Section 5.6.1

)

to determine if ports [2:1] contain permanently attached (non-

removable) devices. Also, the active state of the LED’s will be

determined as follows:

NON_REM[1:0] = ‘00’, All ports are removable,

GR2 is active high,

GR1 is active high.

NON_REM1:0] = ‘01’, Port 1 is non-removable,

GR2 is active high,

GR1 is active low.

NON_REM[1:0] = ‘10’, Ports 1 & 2 are non-removable,

GR2 is active low,

GR1 is active high.

NON_REM[1:0] = ‘11’, Ports 1 & 2 are non-removable,

GR2 is active low,

GR1 is active low.

Port Power Polarity

strapping.

PRTPWR_POL

I/O8

Port Power Polarity strapping determination for the active

signal polarity of the PRTPWR pin.

While RESET_N is asserted, the logic state of this pin will

(though the use of internal combinatorial logic) determine the

active state of the PRTPWR pin in order to ensure that

downstream port power is not inadvertently enabled to

inactive ports during a hardware reset.

On the rising edge of RESET_N (see the applicable

RESET_N timing table in

Section 5.6.1

), the logic value will

be latched internally, and will retain the active signal polarity

for the PRTPWR pin.

‘1’ = PRTPWR pin has an active ‘high’ polarity

‘0’ = PRTPWR pin has an active ‘low’ polarity

Over Current

Sense

OCS_N

IPU

Input from external current monitor indicating an over-current

condition. {Note: Contains internal pull-up to 3.3V supply}

USB Transceiver

Bias

RBIAS

I-R

A 12.0k

(resistor is attached from ground to this pin

to set the transceiver’s internal bias settings.

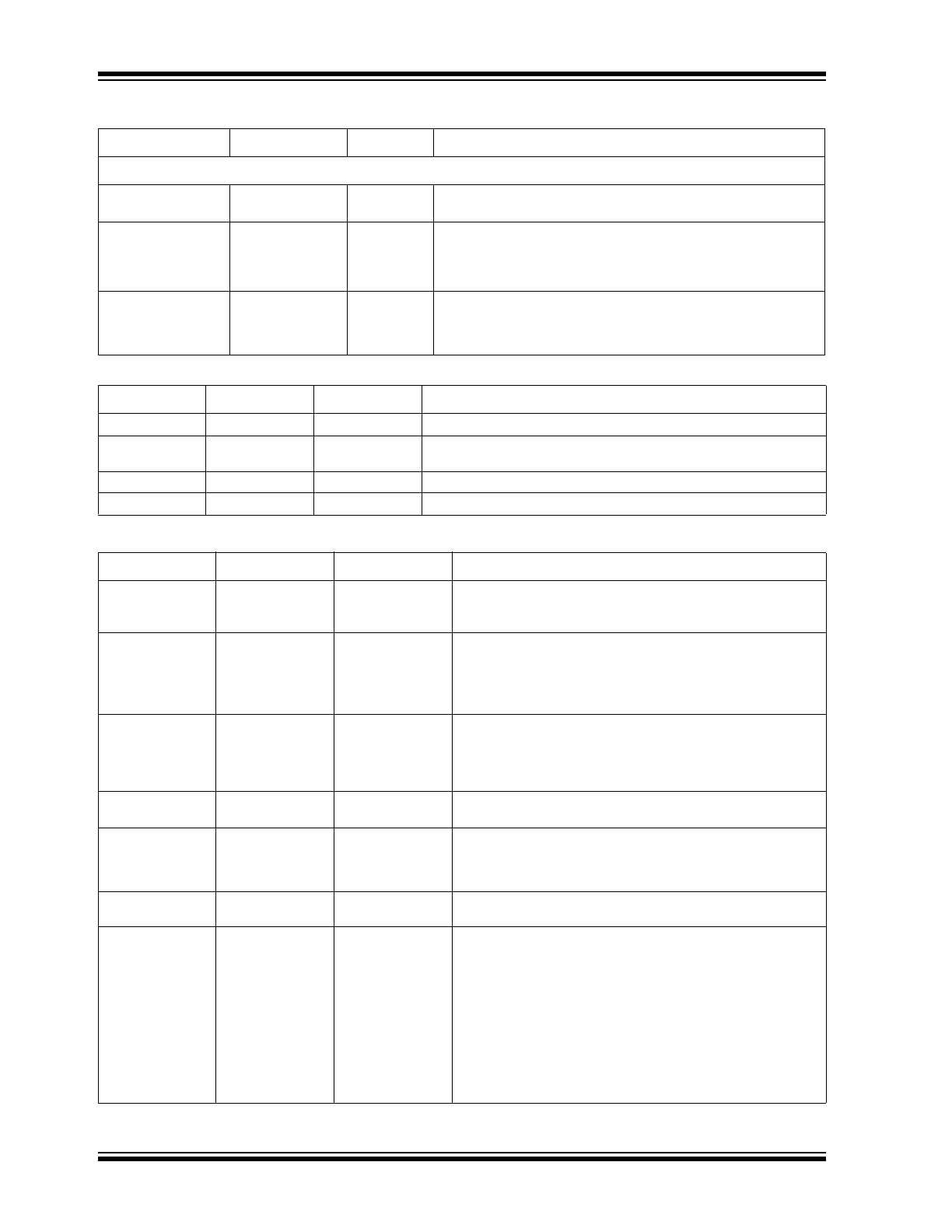

TABLE 4-1:

2-PORT HUB PIN DESCRIPTIONS (CONTINUED)

Name

Symbol

Type

Function

USB2502

DS000002248A-page 10

2007 - 2016 Microchip Technology Inc.

SERIAL PORT INTERFACE

Serial Data/SMB

Data

SDA/SMBDATA

IOSD12

(Serial Data)/(SMB Data) signal.

Serial Clock/SMB

Clock

&

Config Select 0

SCL/SMBCLK/

CFG_SEL0

IOSD12

(Serial Clock)/(SMB Clock) signal. This multifunction pin is

read on the rising edge of RESET_N (see the applicable

RESET_N timing table in

Section 5.6.1

) and will determine

the hub configuration method as described in

Table 4-2

.

Configuration

Programming

Select

CFG_SEL1

I

This pin is read on the rising edge of RESET_N (see the

applicable RESET_N timing table in

Section 5.6.1

) and will

determine the hub configuration method as described in

Table 4-2

.

TABLE 4-2:

SMBUS OR EEPROM INTERFACE BEHAVIOR

CFG_SEL1

CFG_SEL0

SMBus or EEPROM Interface Behavior

0

0

Reserved

0

1

Configured as an SMBus slave for external download of user-

defined descriptors. SMBus slave address is 0101100

1

0

Internal Default Configuration via strapping options.

1

1

2-wire (I

2

C) EEPROMS are supported,

TABLE 4-3:

MISCELLANEOUS PINS

Name

Symbol

Type

Function

Crystal

Input/External

Clock Input

XTAL1/

CLKIN

ICLKx

24MHz crystal or external clock input.

This pin connects to either one terminal of the crystal or to

an external 24MHz clock when a crystal is not used.

Crystal Output

XTAL2

OCLKx

24MHz Crystal

This is the other terminal of the crystal, or left unconnected

when an external clock source is used to drive

XTAL1/CLKIN. It must not be used to drive any external

circuitry other than the crystal circuit.

Clock Input

Enable

CLKIN_EN

I

Clock In Enable:

Low = XTAL1 and XTAL2 pins configured for use with

external crystal

High = XTAL1 pin configured as CLKIN, and must be

driven by an external CMOS clock.

RESET Input

RESET_N

IS

This active low signal is used by the system to reset the

chip. The minimum active low pulse is 1us.

Self-Power /

Bus-Power

Detect

SELF_PWR

I

Detects availability of local self-power source.

Low = Self/local power source is NOT available (i.e., Hub

gets all power from Upstream USB VBus).

High = Self/local power source is available.

TEST Pin

TEST

IPD

Used for testing the chip. User must treat as a no-connect

or connect to ground.

Analog Test

&

Internal 1.8V

voltage regulator

enable

ATEST/

REG_EN

AIO

This signal is used for testing the analog section of the

chip, and to enable or disable the internal 1.8v regulator.

This pin must be connected to VDDA33 to enable the

internal 1.8V regulator, or to VSS to disable the internal

regulator.

When the internal regulator is enabled, the 1.8V power

pins must be left unconnected, except for the required

bypass capacitors.When the PHY is in test mode, the

internal regulator is disabled and the ATEST pin functions

as a test pin.

TABLE 4-1:

2-PORT HUB PIN DESCRIPTIONS (CONTINUED)

Name

Symbol

Type

Function