2014-2018 Microchip Technology Inc.

DS00001691C-page 1

Features

• Integrated USB 2.0 Compatible 3-Port Hub

• Advanced power saving features:

- 1

A Typical Standby Current

- Port goes into power saving state when no

devices are connected downstream

- Port is shut down when port is disabled

- Digital core shutdown in Bypass and Standby

Modes

• Provides USB Battery Charger Detection for:

- USB-IF Battery Charging 1.1 compliant Dedi-

cated Charging Ports (DCP)

- USB-IF Battery Charging 1.1 compliant

Charging Downstream Port (CDP)

- Standard Downstream Port (SDP); that is,

USB host or downstream hub port

- Downstream Hub Ports Support USB-IF Bat-

tery Charging 1.1 as Charging Downstream

Port (CDP)

• Supports either Single-TT or Multi-TT configura-

tions for Full-Speed and Low-Speed connections

(when connected to a High-Speed host)

• Bypass Switch for low power single port operation

- Battery charging detection using a PMIC

- Stereo and mono/mic audio

- USB1.1 Data

• Enhanced configuration options available through

serial I

2

C Slave Port

- VID/PID/DID

- String Descriptors

- Configuration options for Hub

• Internal Default configuration option when serial

I

2

C host is not available

• MultiTRAK

TM

- Dedicated Transaction Translator per port

• PortMap

- Configurable port mapping and disable

sequencing

• PortSwap

- Configurable differential intra-pair signal

swapping

• PHYBoost

- Programmable USB transceiver drive

strength for recovering signal integrity

• VariSense

TM

- Programmable USB receiver sensitivity

• flexPWR

®

Technology

- Low current design ideal for battery powered

applications

- Internal supply switching provides low power

modes

• External 12, 19.2, 26, or 38.4 MHz clock input

• Internal 3.3V & 1.2V Voltage Regulators for single

supply operation

- External VBAT and 1.8V dual supply input

option

• Internal Short Circuit protection of USB differential

signal pins

• ±5kV HBM ESD Protection

• 25-pin WLCS (1.95mm x 1.95mm Wafer Level

Chip Scale) Package - 0.4mm ball pitch

Target Applications

The USB3803 is targeted for applications where more

than one USB port is required. As mobile devices add

more features and the systems become more complex,

it is necessary to have more than one USB port to com-

municate with internal and peripheral devices.

• Mobile Phones

• Ultra Mobile PCs

• Tablet Computers

• Digital Still Cameras

• Digital Video Camcorders

• Gaming Consoles

• PDAs

• Portable Media Players

• GPS Personal Navigation Devices

• Media Players/Viewers

USB3803

USB 2.0 High-Speed Hub Controller Optimized

for Portable Applications

USB3803

DS00001691C-page 2

2014-2018 Microchip Technology Inc.

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at

docerrors@microchip.com

. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for cur-

rent devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the

revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site;

http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are

using.

Customer Notification System

Register on our web site at

www.microchip.com

to receive the most current information on all of our products.

2014-2018 Microchip Technology Inc.

DS00001691C-page 3

USB3803

Table of Contents

1.0 General Description ........................................................................................................................................................................ 4

2.0 Acronyms and Definitions ............................................................................................................................................................... 7

3.0 USB3803 Pin Definitions ................................................................................................................................................................. 8

4.0 Modes of Operation ...................................................................................................................................................................... 15

5.0 Configuration Options ................................................................................................................................................................... 21

6.0 Serial Slave Interface .................................................................................................................................................................... 40

7.0 USB Descriptors ........................................................................................................................................................................... 44

8.0 Battery Charging ........................................................................................................................................................................... 63

9.0 Integrated Power Regulators ........................................................................................................................................................ 69

10.0 Specifications .............................................................................................................................................................................. 70

11.0 Application Reference ................................................................................................................................................................. 78

12.0 Package Outlines, Tape & Reel Drawings, Package Marking .................................................................................................... 82

Appendix A: Revision History .............................................................................................................................................................. 87

The Microchip Web Site ...................................................................................................................................................................... 88

Customer Change Notification Service ............................................................................................................................................... 88

Customer Support ............................................................................................................................................................................... 88

Product Identification System ............................................................................................................................................................. 89

USB3803

DS00001691C-page 4

2014-2018 Microchip Technology Inc.

1.0

GENERAL DESCRIPTION

The USB3803 is a family of low-power, USB 2.0 hub controllers with three downstream ports. “USB3803” is a generic

term referring to the entire family, which includes the following devices:

• USB3803C

• USB3803Ci

The USB3803 is available in two temperature ranges (commercial and industrial) and is recommended for new designs.

The USB3803 device includes an integrated USB bypass switch. This device-specific feature is called out independently

throughout the document.

Table 1-1

provides a summary of the feature differences between USB3803C and

USB3803Ci:

The USB3803 can attach to an upstream port as a full-speed hub or as a full-/hi-speed hub and supports low-speed,

full-speed, and hi-speed (if operating as a hi-speed hub) downstream devices on all of the enabled downstream ports.

The USB3803 has been specifically optimized for mobile embedded applications. The pin-count has been reduced by

optimizing the USB3803 for mobile battery-powered embedded systems where power consumption, small package

size, minimal BOM, and battery charger detection capabilities are critical design requirements. Standby mode and

Bypass mode power has been minimized. Instead of a dedicated crystal, reference clock inputs are aligned to mobile

applications. Flexible integrated power regulators ease integration into battery powered devices. Automatic battery

charger detection is available on the upstream port. All required resistors on the USB ports are integrated into the hub.

This includes all series termination resistors on D+ and D– pins and all required pull-down and pull-up resistors on D+

and D– pins.

The integrated USB switch allows the USB3803 to bypass the USB Hub and directly connect the upstream and Port 3

downstream USB port for operational modes that do not require Hi-Speed media transfers. The bypass switch enables

multiple connectivity options to the USB port while preserving the high speed signal quality in USB Hub Mode.

The USB3803 integrated battery charger detection circuitry supports USB-IF 1.1 charger detection methods. These cir-

cuits are used to detect the attachment and type of a USB Charger and provide an interrupt output to the portable device

indicating that charger information is available to be read from USB3803 status registers via the serial interface.

The USB3803 includes programmable features such as:

MultiTRAK

TM

Technology which utilizes a dedicated Transaction Translator (TT) per port to maintain consistent full-

speed data throughput regardless of the number of active downstream connections. MultiTRAK

TM

outperforms conven-

tional USB 2.0 hubs with a single TT in USB full-speed data transfers.

PortMap which provides flexible port mapping and disable sequences. The downstream ports of a USB3803 hub can

be reordered or disabled in any sequence to support multiple platform designs with minimum effort. For any port that is

disabled, the USB3803 hub controllers automatically reorder the remaining ports to match the USB host controller’s port

numbering scheme.

PortSwap which adds per-port programmability to USB differential-pair pin locations. PortSwap allows direct alignment

of USB signals (D+/D-) to connectors to avoid uneven trace length or crossing of the USB differential signals on the

PCB.

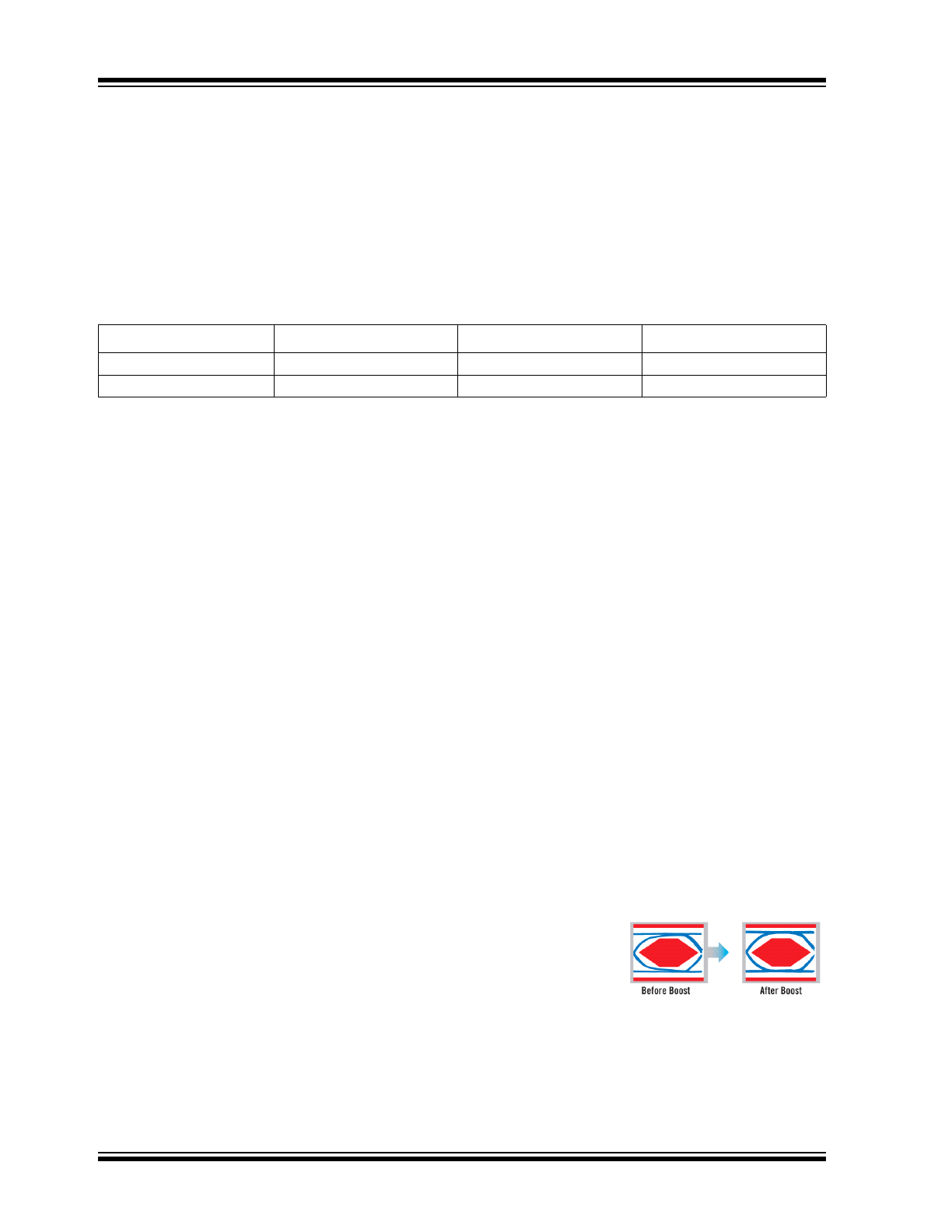

PHYBoost which provides programmable levels of Hi-Speed USB signal drive

strength in the upstream and downstream port transceivers. PHYBoost attempts to

restore USB signal integrity in a compromised system environment. The graphic on

the right shows an example of Hi-Speed USB eye diagrams before and after PHY-

Boost signal integrity restoration.

VariSense

TM

which controls the USB receiver sensitivity enabling programmable lev-

els of USB signal receive sensitivity. This capability allows operation in a sub-optimal system environment, such as

when a captive USB cable is used.

TABLE 1-1:

USB3803 FAMILY DIFFERENCES

Part Number

USB Bypass Switch

0°C to +70°C

-40°C to +85°C

USB3803C

X

X

USB3803Ci

X

X

2014-2018 Microchip Technology Inc.

DS00001691C-page 5

USB3803

1.1

Customer Selectable Features

A default configuration is available in the USB3803 following a reset. This configuration may be sufficient for most appli-

cations. The USB3803 hub may also be configured by an external microcontroller. When using the microcontroller inter-

face, the hub appears as an I

2

C slave device.

The USB3803 hub supports customer selectable features including:

• Optional customer configuration via I

2

C

• Compound devices on a port-by-port basis

• Customizable vendor ID, product ID, and device ID

• Configurable downstream port power-on time reported to the host

• Indication of the maximum current that the hub consumes from the USB upstream port

• Indication of the maximum current required for the hub controller

• Configurable as a Self-Powered and Bus-Powered Hub

• Custom string descriptors (up to 30 characters):

- Product string

- Manufacturer string

- Serial number string

• When available, I

2

C configurable options for default configuration may include:

- Downstream ports as non-removable ports

- Downstream ports as disabled ports

- USB signal drive strength

- USB receiver sensitivity

- USB differential pair pin location

USB3803

DS00001691C-page 6

2014-2018 Microchip Technology Inc.

1.1.1

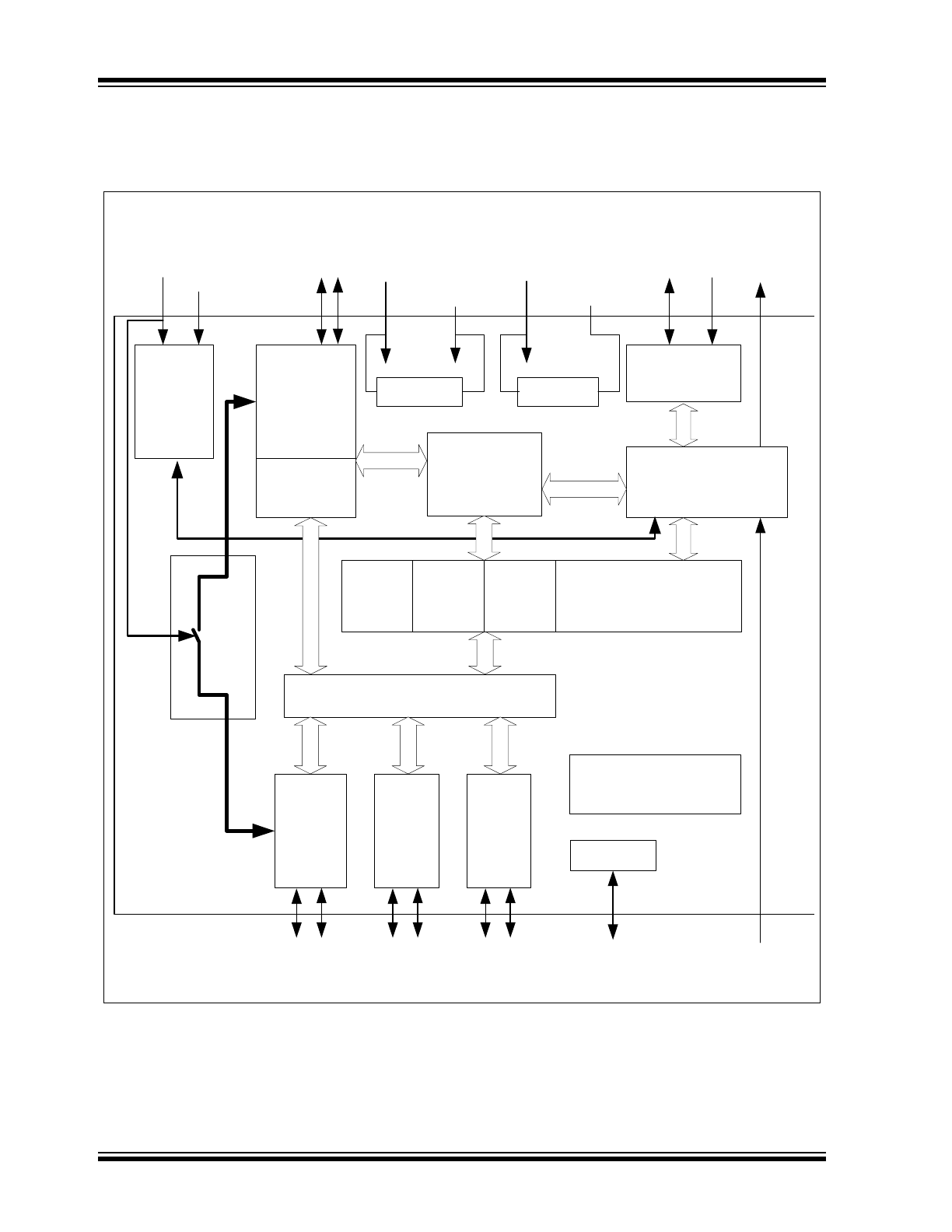

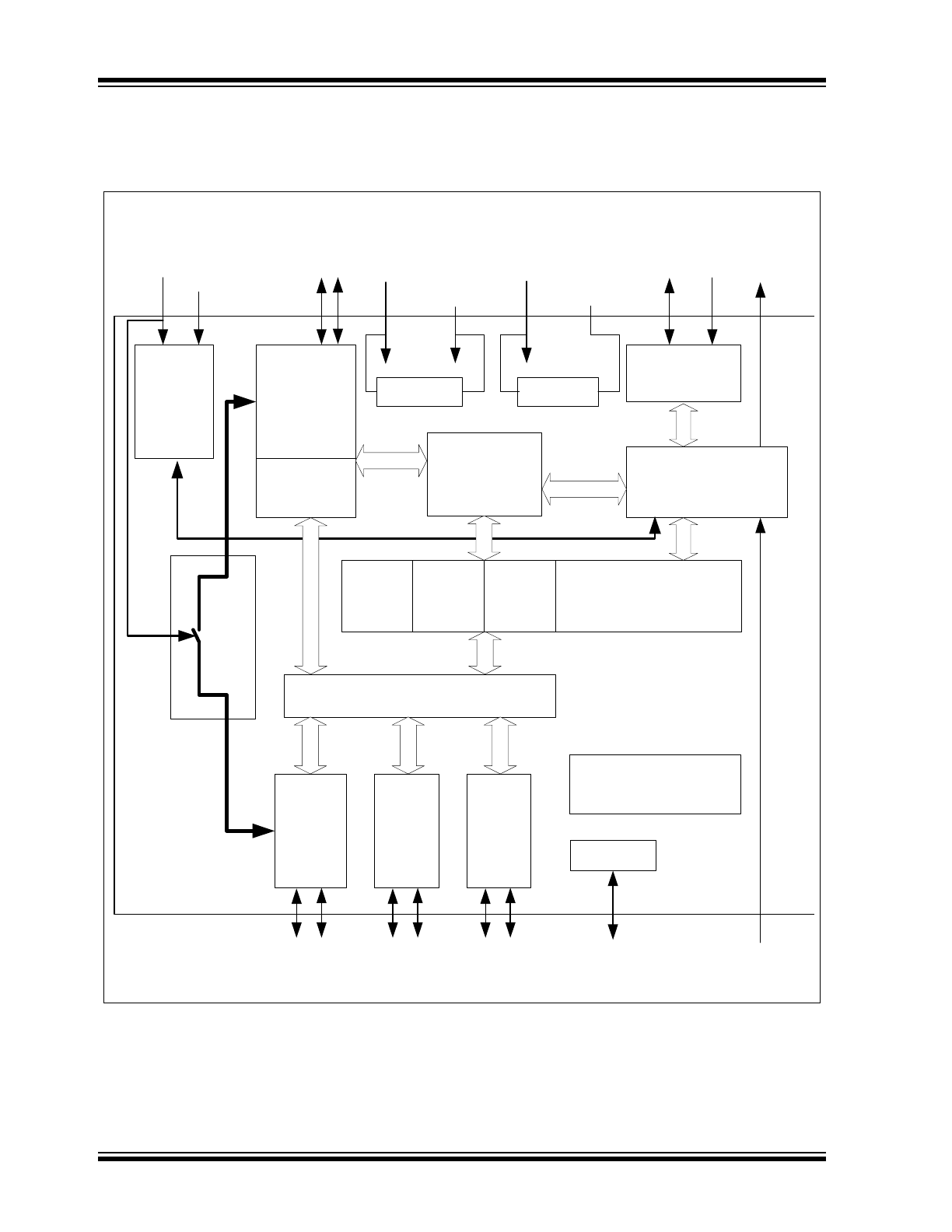

BLOCK DIAGRAM

FIGURE 1-1:

USB3803 BLOCK DIAGRAM

B

y

pa

ss

Swi

tc

h

From PMIC/SOC

VDD33_BYP

Upstream

PHY

USB

Upstream

Repeater

Controller

SIE

Serial

Interface

PLL

REF_CLK

To I2C Master

Routing & Port Re-Ordering Logic

SCL

SDA

Port Controller

PHY#3

Bypass/

USB Data

Downstream

Mode

Control

-

Standby

Bypass

Hub Mode

VDD12_BYP

TT #3

TT #2

TT #1

PHY#2

PHY#1

USB Data

Downstream

USB Data

Downstream

1.2V Reg

RESET_N

BYPASS_N

VBAT

Upstream Battery

Charger Detection

HUB_CONNECT

3.3V Reg

VDD_CORE_REG

INT_N

2014-2018 Microchip Technology Inc.

DS00001691C-page 7

USB3803

2.0

ACRONYMS AND DEFINITIONS

2.1

Acronyms

EP:

Endpoint

FS:

Full-Speed

HS: Hi-Speed

I

2

C: Inter-Integrated Circuit

LS:

Low-Speed

2.2 Reference Documents

1.

USB Engineering Change Notice dated December 29th, 2004, UNICODE UTF-16LE For String Descriptors

2.

Universal Serial Bus Specification, Revision 2.0, Dated April 27th, 2000

3.

Battery Charging Specification, Revision 1.1, Release Candidate 10, Dated Sept. 22, 2008

4.

High-Speed Inter-Chip USB Electrical Specification, Version 1.0, Dated Sept. 23, 2007

USB3803

DS00001691C-page 8

2014-2018 Microchip Technology Inc.

3.0

USB3803 PIN DEFINITIONS

3.1

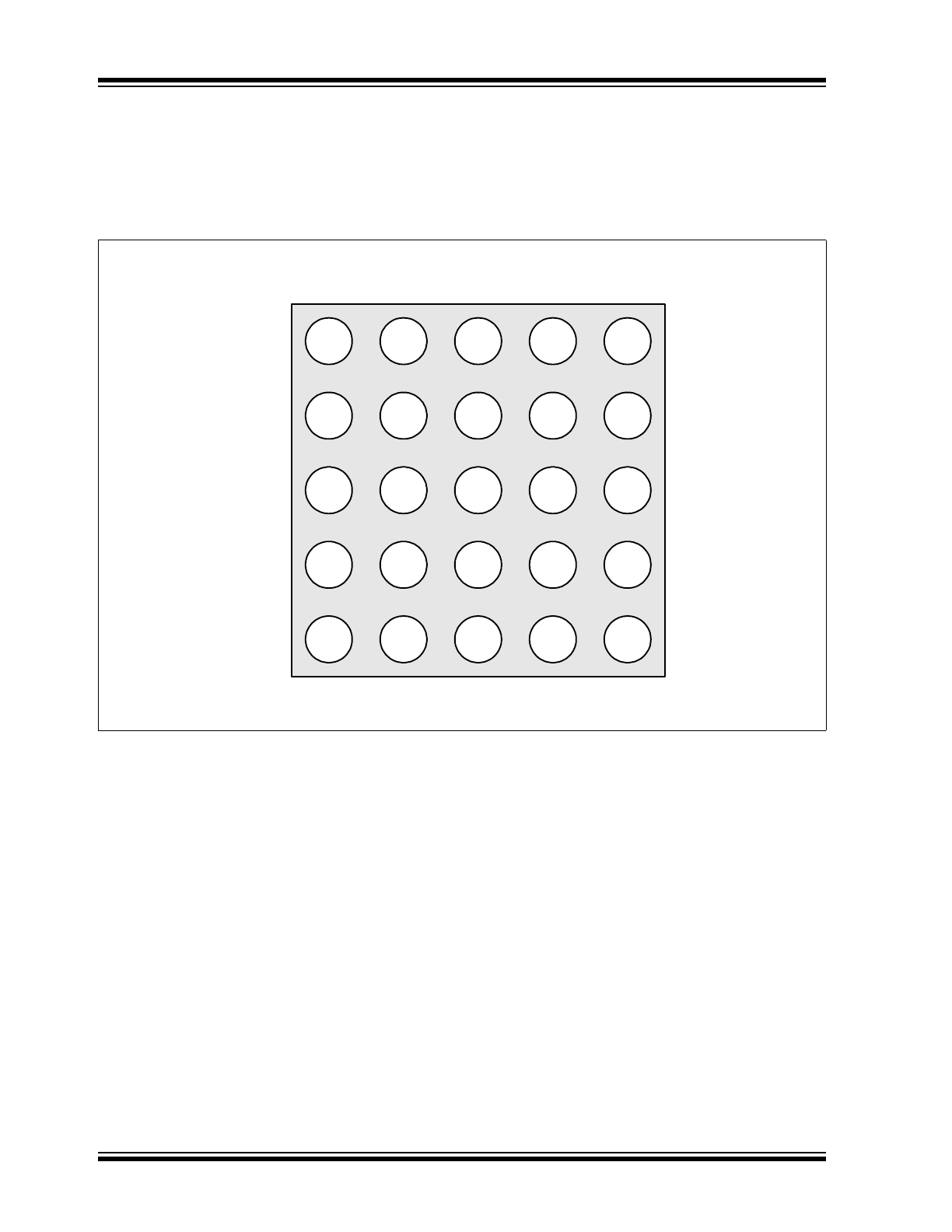

Pin Configuration

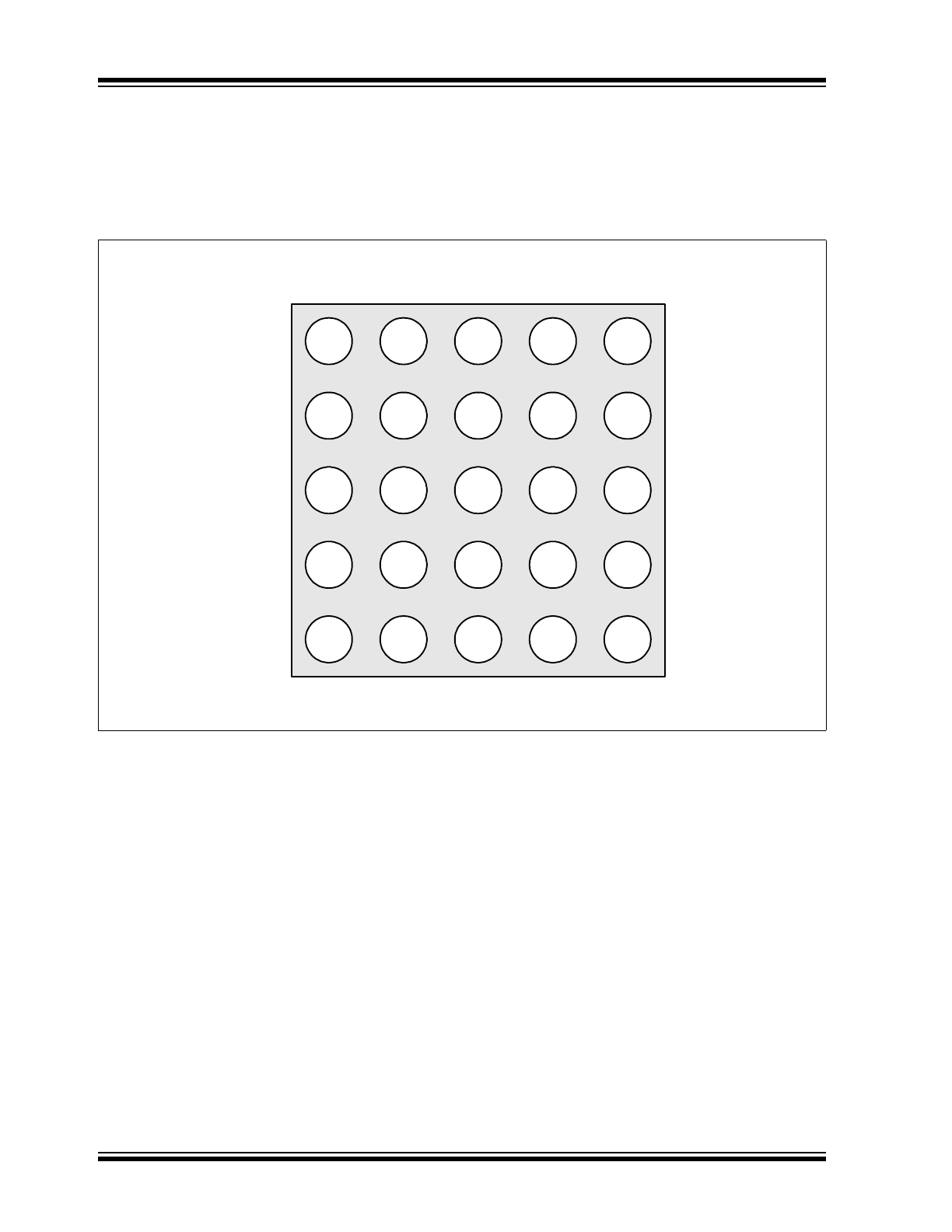

The illustration below shows the package diagram.

FIGURE 3-1:

USB3803 25-BALL PACKAGE

A

E

D

C

B

1

5

4

3

2

TOP VIEW

2014-2018 Microchip Technology Inc.

DS00001691C-page 9

USB3803

3.2

Signal Definitions

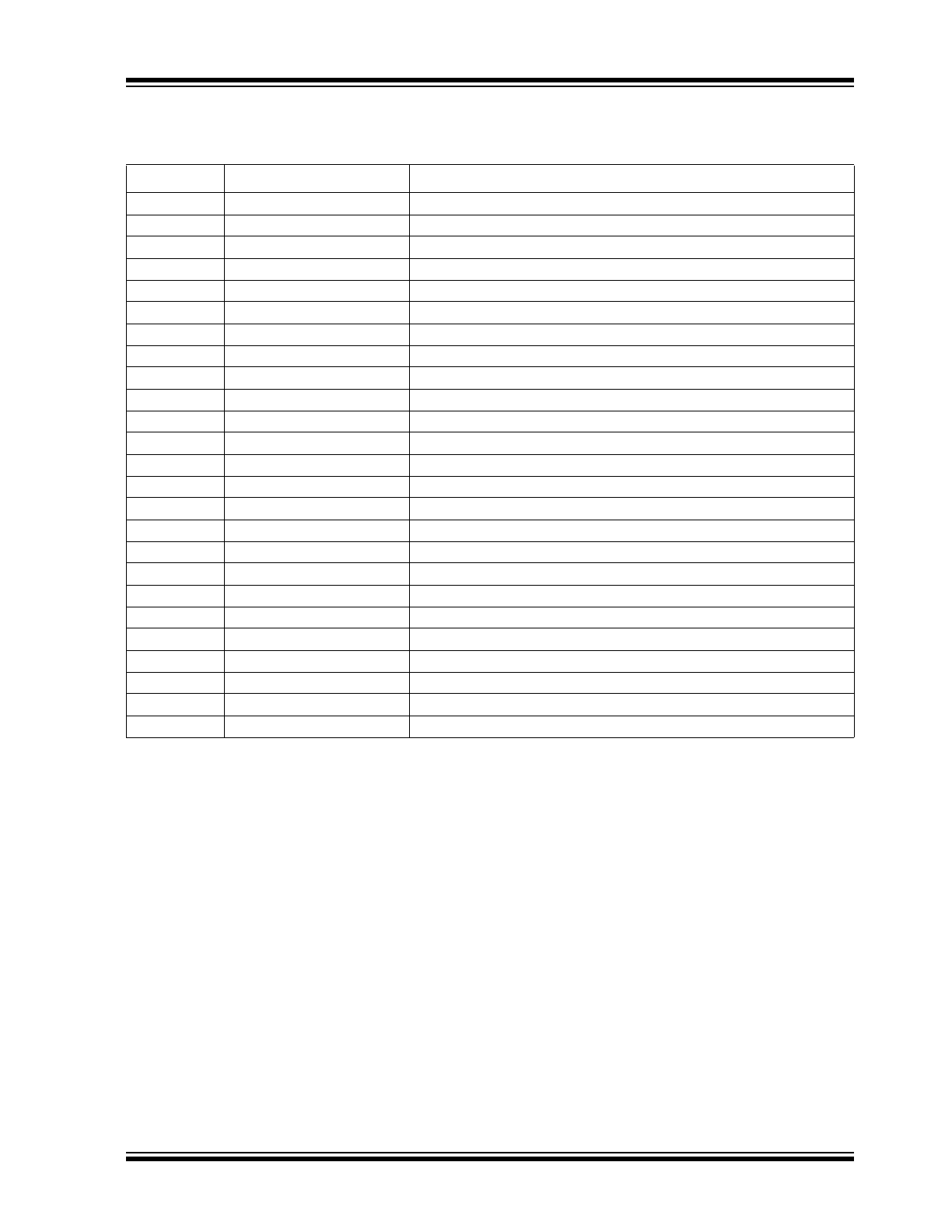

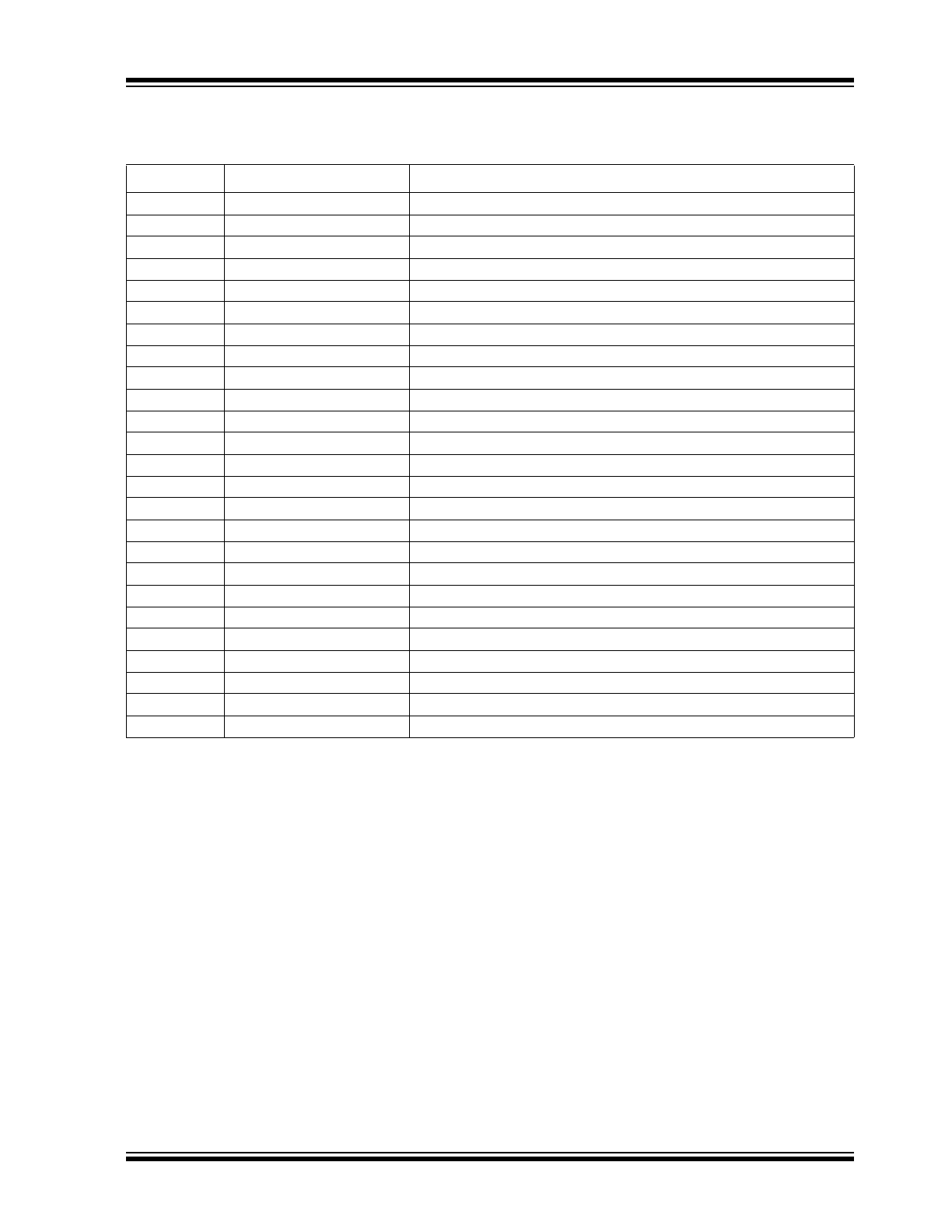

TABLE 3-1:

SIGNAL DEFINITIONS

WLCSP Pin

Name

Description

E2

USBUP_DP

Upstream D+ data pin of the USB Interface

E1

USBUP_DM

Upstream D- data pin of the USB Interface

A5

BYPASS_N

Control signal to select between HUB MODE and BYPASS MODE

C4

I2C_ASEL0

I

2

C Address Select Bit 0

B4

I2C_ASEL1

I

2

C Address Select Bit 1

A1

USBDN1_DP

USB downstream Port 1 D+ data pin

B1

USBDN1_DM

USB downstream Port 1 D- data pin

C2

USBDN2_DP

USB downstream Port 2 D+ data pin

D2

USBDN2_DM

USB downstream Port 2 D- data pin

C1

USBDN3_DP

USB downstream Port 3 D+ data pin

D1

USBDN3_DM

USB downstream Port 3 D- data pin

E5

SCL

I

2

C clock input

D5

SDA

I

2

C bi-directional data pin

E3

RESET_N

Active low reset signal

B5

HUB_CONNECT

Hub Connect

C5

INT_N

Active low interrupt signal

D4

REF_SEL1

Reference Clock Select 1 input

E4

REF_SEL0

Reference Clock Select 0 input

B3

REFCLK

Reference Clock input

A4

RBIAS

Bias Resistor pin

D3

VDD12_BYP

1.2V Regulator

A2

VDD33_BYP

3.3V Regulator

B2

VBAT

Voltage input from the battery supply

A3

VDD_CORE_REG

Power supply input to 1.2V regulator for digital logic core

C3

VSS

Ground

USB3803

DS00001691C-page 10

2014-2018 Microchip Technology Inc.

3.3

Pin Descriptions

This section provides a detailed description of each signal. The signals are arranged in functional groups according to

their associated interface.

The terms assertion and negation are used. This is done to avoid confusion when working with a mixture of “active low”

and “active high” signal. The term “assert” or “assertion” indicates that a signal is active, independent of whether that

level is represented by a high or low voltage. The term “negate” or “negation” indicates that a signal is inactive.

3.3.1

PIN DEFINITION

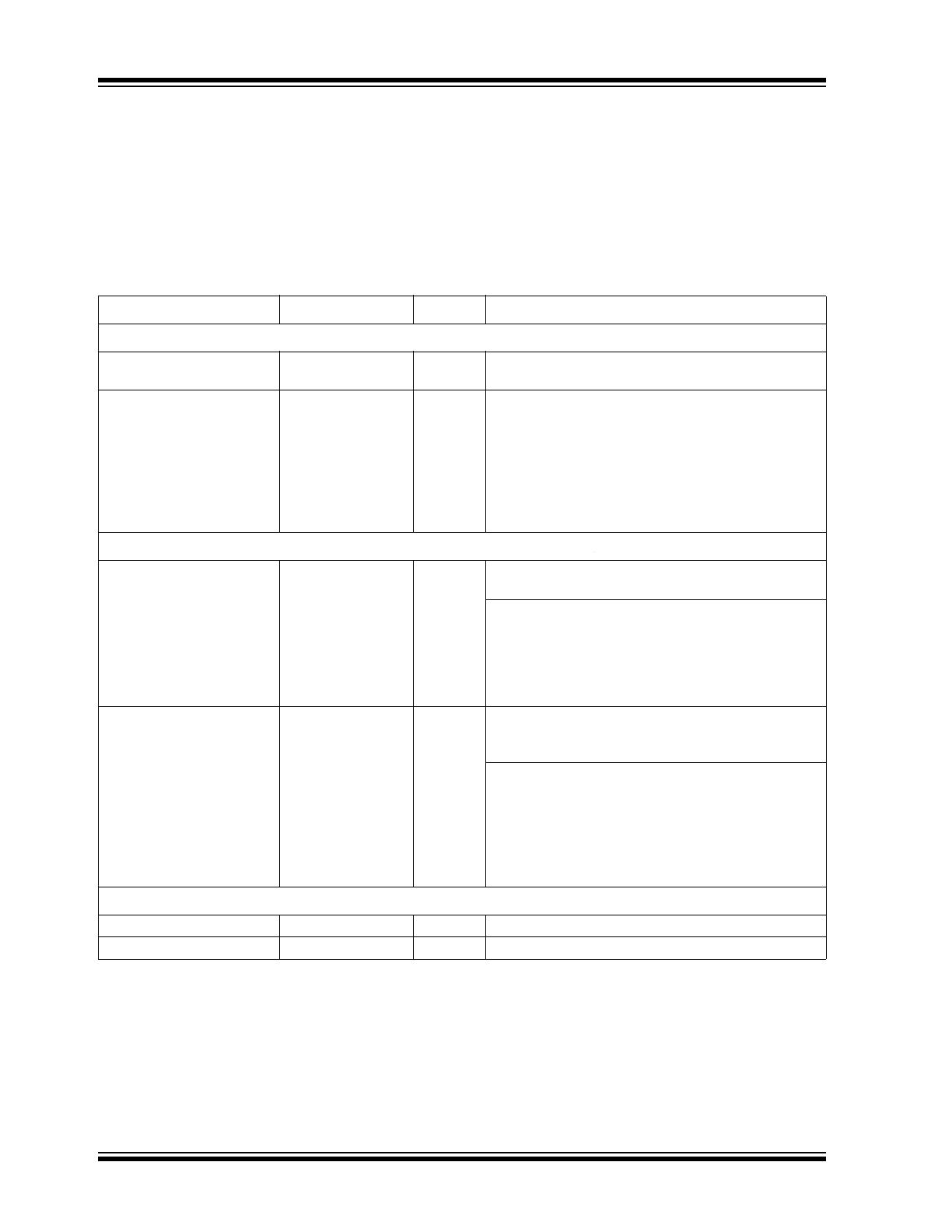

TABLE 3-2:

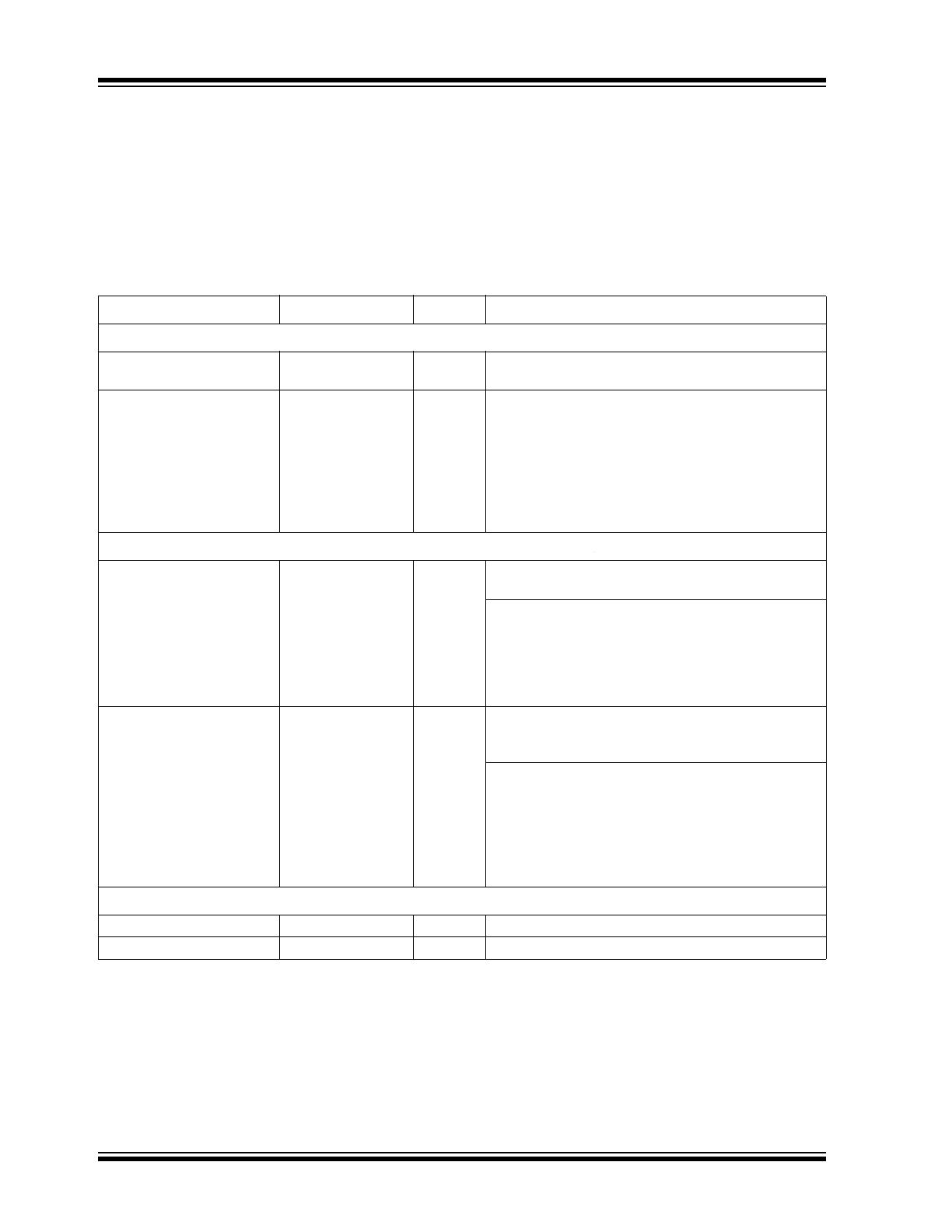

PIN DESCRIPTIONS

Name

Symbol

Type

Description

Upstream USB 2.0 / Bypass Interface

USB Bus Data

USBUP_DP

USBUP_DM

A-I/O

These pins connect to the upstream USB bus data

signals (Host port or upstream hub)

Bypass Select for Analog

Switch

BYPASS_N

I

Control signal to select between Hub Mode and

Bypass Mode. When asserted low, the device transi-

tions to Bypass Mode, connects the Bypass Port to

the upstream USB Port, places Port 1 and Port 2 in

high impedance state, and places the core logic in a

reduced power state. When negated high, the device

transitions to HUB MODE and enables operation as a

USB hub.

Downstream USB 2.0 / Bypass Interface

High-Speed USB Data

&

Port Disable Strap Option

USBDN_DP[2:1]

&

USBDN_DM[2:1]

A-I/O

These pins connect to the downstream USB periph-

eral devices attached to the hub’s ports

Downstream Port Disable Strap option:

This pin is sampled at RESET_N negation to deter-

mine if the port is disabled.

Both USB data pins for the corresponding port must

be tied to VDD33_BYP to disable the associated

downstream port.

HS USB Data

&

Bypass Port

USBDN_DP[3]

&

USBDN_DM[3]

A-I/O

When BYPASS_N is negated high, these pins con-

nect to the downstream USB peripheral devices

attached to the hub’s ports.

There is no downstream Port Disable Strap option on

these ports.

When BYPASS_N is asserted low, USBDN_DP[3]

and USBDN_DM[3] respectively are connected

through the analog switch to the upstream port

USBUP_DP and USBUP_DM. PortSwap setting has

no effect in Bypass Mode.

Serial Port Interface

Serial Data

SDA

I/OD

I

2

C Serial Data

Serial Clock

SCL

I

Serial Clock (SCL)

2014-2018 Microchip Technology Inc.

DS00001691C-page 1

Features

• Integrated USB 2.0 Compatible 3-Port Hub

• Advanced power saving features:

- 1

A Typical Standby Current

- Port goes into power saving state when no

devices are connected downstream

- Port is shut down when port is disabled

- Digital core shutdown in Bypass and Standby

Modes

• Provides USB Battery Charger Detection for:

- USB-IF Battery Charging 1.1 compliant Dedi-

cated Charging Ports (DCP)

- USB-IF Battery Charging 1.1 compliant

Charging Downstream Port (CDP)

- Standard Downstream Port (SDP); that is,

USB host or downstream hub port

- Downstream Hub Ports Support USB-IF Bat-

tery Charging 1.1 as Charging Downstream

Port (CDP)

• Supports either Single-TT or Multi-TT configura-

tions for Full-Speed and Low-Speed connections

(when connected to a High-Speed host)

• Bypass Switch for low power single port operation

- Battery charging detection using a PMIC

- Stereo and mono/mic audio

- USB1.1 Data

• Enhanced configuration options available through

serial I

2

C Slave Port

- VID/PID/DID

- String Descriptors

- Configuration options for Hub

• Internal Default configuration option when serial

I

2

C host is not available

• MultiTRAK

TM

- Dedicated Transaction Translator per port

• PortMap

- Configurable port mapping and disable

sequencing

• PortSwap

- Configurable differential intra-pair signal

swapping

• PHYBoost

- Programmable USB transceiver drive

strength for recovering signal integrity

• VariSense

TM

- Programmable USB receiver sensitivity

• flexPWR

®

Technology

- Low current design ideal for battery powered

applications

- Internal supply switching provides low power

modes

• External 12, 19.2, 26, or 38.4 MHz clock input

• Internal 3.3V & 1.2V Voltage Regulators for single

supply operation

- External VBAT and 1.8V dual supply input

option

• Internal Short Circuit protection of USB differential

signal pins

• ±5kV HBM ESD Protection

• 25-pin WLCS (1.95mm x 1.95mm Wafer Level

Chip Scale) Package - 0.4mm ball pitch

Target Applications

The USB3803 is targeted for applications where more

than one USB port is required. As mobile devices add

more features and the systems become more complex,

it is necessary to have more than one USB port to com-

municate with internal and peripheral devices.

• Mobile Phones

• Ultra Mobile PCs

• Tablet Computers

• Digital Still Cameras

• Digital Video Camcorders

• Gaming Consoles

• PDAs

• Portable Media Players

• GPS Personal Navigation Devices

• Media Players/Viewers

USB3803

USB 2.0 High-Speed Hub Controller Optimized

for Portable Applications

USB3803

DS00001691C-page 2

2014-2018 Microchip Technology Inc.

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at

docerrors@microchip.com

. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for cur-

rent devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the

revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site;

http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are

using.

Customer Notification System

Register on our web site at

www.microchip.com

to receive the most current information on all of our products.

2014-2018 Microchip Technology Inc.

DS00001691C-page 3

USB3803

Table of Contents

1.0 General Description ........................................................................................................................................................................ 4

2.0 Acronyms and Definitions ............................................................................................................................................................... 7

3.0 USB3803 Pin Definitions ................................................................................................................................................................. 8

4.0 Modes of Operation ...................................................................................................................................................................... 15

5.0 Configuration Options ................................................................................................................................................................... 21

6.0 Serial Slave Interface .................................................................................................................................................................... 40

7.0 USB Descriptors ........................................................................................................................................................................... 44

8.0 Battery Charging ........................................................................................................................................................................... 63

9.0 Integrated Power Regulators ........................................................................................................................................................ 69

10.0 Specifications .............................................................................................................................................................................. 70

11.0 Application Reference ................................................................................................................................................................. 78

12.0 Package Outlines, Tape & Reel Drawings, Package Marking .................................................................................................... 82

Appendix A: Revision History .............................................................................................................................................................. 87

The Microchip Web Site ...................................................................................................................................................................... 88

Customer Change Notification Service ............................................................................................................................................... 88

Customer Support ............................................................................................................................................................................... 88

Product Identification System ............................................................................................................................................................. 89

USB3803

DS00001691C-page 4

2014-2018 Microchip Technology Inc.

1.0

GENERAL DESCRIPTION

The USB3803 is a family of low-power, USB 2.0 hub controllers with three downstream ports. “USB3803” is a generic

term referring to the entire family, which includes the following devices:

• USB3803C

• USB3803Ci

The USB3803 is available in two temperature ranges (commercial and industrial) and is recommended for new designs.

The USB3803 device includes an integrated USB bypass switch. This device-specific feature is called out independently

throughout the document.

Table 1-1

provides a summary of the feature differences between USB3803C and

USB3803Ci:

The USB3803 can attach to an upstream port as a full-speed hub or as a full-/hi-speed hub and supports low-speed,

full-speed, and hi-speed (if operating as a hi-speed hub) downstream devices on all of the enabled downstream ports.

The USB3803 has been specifically optimized for mobile embedded applications. The pin-count has been reduced by

optimizing the USB3803 for mobile battery-powered embedded systems where power consumption, small package

size, minimal BOM, and battery charger detection capabilities are critical design requirements. Standby mode and

Bypass mode power has been minimized. Instead of a dedicated crystal, reference clock inputs are aligned to mobile

applications. Flexible integrated power regulators ease integration into battery powered devices. Automatic battery

charger detection is available on the upstream port. All required resistors on the USB ports are integrated into the hub.

This includes all series termination resistors on D+ and D– pins and all required pull-down and pull-up resistors on D+

and D– pins.

The integrated USB switch allows the USB3803 to bypass the USB Hub and directly connect the upstream and Port 3

downstream USB port for operational modes that do not require Hi-Speed media transfers. The bypass switch enables

multiple connectivity options to the USB port while preserving the high speed signal quality in USB Hub Mode.

The USB3803 integrated battery charger detection circuitry supports USB-IF 1.1 charger detection methods. These cir-

cuits are used to detect the attachment and type of a USB Charger and provide an interrupt output to the portable device

indicating that charger information is available to be read from USB3803 status registers via the serial interface.

The USB3803 includes programmable features such as:

MultiTRAK

TM

Technology which utilizes a dedicated Transaction Translator (TT) per port to maintain consistent full-

speed data throughput regardless of the number of active downstream connections. MultiTRAK

TM

outperforms conven-

tional USB 2.0 hubs with a single TT in USB full-speed data transfers.

PortMap which provides flexible port mapping and disable sequences. The downstream ports of a USB3803 hub can

be reordered or disabled in any sequence to support multiple platform designs with minimum effort. For any port that is

disabled, the USB3803 hub controllers automatically reorder the remaining ports to match the USB host controller’s port

numbering scheme.

PortSwap which adds per-port programmability to USB differential-pair pin locations. PortSwap allows direct alignment

of USB signals (D+/D-) to connectors to avoid uneven trace length or crossing of the USB differential signals on the

PCB.

PHYBoost which provides programmable levels of Hi-Speed USB signal drive

strength in the upstream and downstream port transceivers. PHYBoost attempts to

restore USB signal integrity in a compromised system environment. The graphic on

the right shows an example of Hi-Speed USB eye diagrams before and after PHY-

Boost signal integrity restoration.

VariSense

TM

which controls the USB receiver sensitivity enabling programmable lev-

els of USB signal receive sensitivity. This capability allows operation in a sub-optimal system environment, such as

when a captive USB cable is used.

TABLE 1-1:

USB3803 FAMILY DIFFERENCES

Part Number

USB Bypass Switch

0°C to +70°C

-40°C to +85°C

USB3803C

X

X

USB3803Ci

X

X

2014-2018 Microchip Technology Inc.

DS00001691C-page 5

USB3803

1.1

Customer Selectable Features

A default configuration is available in the USB3803 following a reset. This configuration may be sufficient for most appli-

cations. The USB3803 hub may also be configured by an external microcontroller. When using the microcontroller inter-

face, the hub appears as an I

2

C slave device.

The USB3803 hub supports customer selectable features including:

• Optional customer configuration via I

2

C

• Compound devices on a port-by-port basis

• Customizable vendor ID, product ID, and device ID

• Configurable downstream port power-on time reported to the host

• Indication of the maximum current that the hub consumes from the USB upstream port

• Indication of the maximum current required for the hub controller

• Configurable as a Self-Powered and Bus-Powered Hub

• Custom string descriptors (up to 30 characters):

- Product string

- Manufacturer string

- Serial number string

• When available, I

2

C configurable options for default configuration may include:

- Downstream ports as non-removable ports

- Downstream ports as disabled ports

- USB signal drive strength

- USB receiver sensitivity

- USB differential pair pin location

USB3803

DS00001691C-page 6

2014-2018 Microchip Technology Inc.

1.1.1

BLOCK DIAGRAM

FIGURE 1-1:

USB3803 BLOCK DIAGRAM

B

y

pa

ss

Swi

tc

h

From PMIC/SOC

VDD33_BYP

Upstream

PHY

USB

Upstream

Repeater

Controller

SIE

Serial

Interface

PLL

REF_CLK

To I2C Master

Routing & Port Re-Ordering Logic

SCL

SDA

Port Controller

PHY#3

Bypass/

USB Data

Downstream

Mode

Control

-

Standby

Bypass

Hub Mode

VDD12_BYP

TT #3

TT #2

TT #1

PHY#2

PHY#1

USB Data

Downstream

USB Data

Downstream

1.2V Reg

RESET_N

BYPASS_N

VBAT

Upstream Battery

Charger Detection

HUB_CONNECT

3.3V Reg

VDD_CORE_REG

INT_N

2014-2018 Microchip Technology Inc.

DS00001691C-page 7

USB3803

2.0

ACRONYMS AND DEFINITIONS

2.1

Acronyms

EP:

Endpoint

FS:

Full-Speed

HS: Hi-Speed

I

2

C: Inter-Integrated Circuit

LS:

Low-Speed

2.2 Reference Documents

1.

USB Engineering Change Notice dated December 29th, 2004, UNICODE UTF-16LE For String Descriptors

2.

Universal Serial Bus Specification, Revision 2.0, Dated April 27th, 2000

3.

Battery Charging Specification, Revision 1.1, Release Candidate 10, Dated Sept. 22, 2008

4.

High-Speed Inter-Chip USB Electrical Specification, Version 1.0, Dated Sept. 23, 2007

USB3803

DS00001691C-page 8

2014-2018 Microchip Technology Inc.

3.0

USB3803 PIN DEFINITIONS

3.1

Pin Configuration

The illustration below shows the package diagram.

FIGURE 3-1:

USB3803 25-BALL PACKAGE

A

E

D

C

B

1

5

4

3

2

TOP VIEW

2014-2018 Microchip Technology Inc.

DS00001691C-page 9

USB3803

3.2

Signal Definitions

TABLE 3-1:

SIGNAL DEFINITIONS

WLCSP Pin

Name

Description

E2

USBUP_DP

Upstream D+ data pin of the USB Interface

E1

USBUP_DM

Upstream D- data pin of the USB Interface

A5

BYPASS_N

Control signal to select between HUB MODE and BYPASS MODE

C4

I2C_ASEL0

I

2

C Address Select Bit 0

B4

I2C_ASEL1

I

2

C Address Select Bit 1

A1

USBDN1_DP

USB downstream Port 1 D+ data pin

B1

USBDN1_DM

USB downstream Port 1 D- data pin

C2

USBDN2_DP

USB downstream Port 2 D+ data pin

D2

USBDN2_DM

USB downstream Port 2 D- data pin

C1

USBDN3_DP

USB downstream Port 3 D+ data pin

D1

USBDN3_DM

USB downstream Port 3 D- data pin

E5

SCL

I

2

C clock input

D5

SDA

I

2

C bi-directional data pin

E3

RESET_N

Active low reset signal

B5

HUB_CONNECT

Hub Connect

C5

INT_N

Active low interrupt signal

D4

REF_SEL1

Reference Clock Select 1 input

E4

REF_SEL0

Reference Clock Select 0 input

B3

REFCLK

Reference Clock input

A4

RBIAS

Bias Resistor pin

D3

VDD12_BYP

1.2V Regulator

A2

VDD33_BYP

3.3V Regulator

B2

VBAT

Voltage input from the battery supply

A3

VDD_CORE_REG

Power supply input to 1.2V regulator for digital logic core

C3

VSS

Ground

USB3803

DS00001691C-page 10

2014-2018 Microchip Technology Inc.

3.3

Pin Descriptions

This section provides a detailed description of each signal. The signals are arranged in functional groups according to

their associated interface.

The terms assertion and negation are used. This is done to avoid confusion when working with a mixture of “active low”

and “active high” signal. The term “assert” or “assertion” indicates that a signal is active, independent of whether that

level is represented by a high or low voltage. The term “negate” or “negation” indicates that a signal is inactive.

3.3.1

PIN DEFINITION

TABLE 3-2:

PIN DESCRIPTIONS

Name

Symbol

Type

Description

Upstream USB 2.0 / Bypass Interface

USB Bus Data

USBUP_DP

USBUP_DM

A-I/O

These pins connect to the upstream USB bus data

signals (Host port or upstream hub)

Bypass Select for Analog

Switch

BYPASS_N

I

Control signal to select between Hub Mode and

Bypass Mode. When asserted low, the device transi-

tions to Bypass Mode, connects the Bypass Port to

the upstream USB Port, places Port 1 and Port 2 in

high impedance state, and places the core logic in a

reduced power state. When negated high, the device

transitions to HUB MODE and enables operation as a

USB hub.

Downstream USB 2.0 / Bypass Interface

High-Speed USB Data

&

Port Disable Strap Option

USBDN_DP[2:1]

&

USBDN_DM[2:1]

A-I/O

These pins connect to the downstream USB periph-

eral devices attached to the hub’s ports

Downstream Port Disable Strap option:

This pin is sampled at RESET_N negation to deter-

mine if the port is disabled.

Both USB data pins for the corresponding port must

be tied to VDD33_BYP to disable the associated

downstream port.

HS USB Data

&

Bypass Port

USBDN_DP[3]

&

USBDN_DM[3]

A-I/O

When BYPASS_N is negated high, these pins con-

nect to the downstream USB peripheral devices

attached to the hub’s ports.

There is no downstream Port Disable Strap option on

these ports.

When BYPASS_N is asserted low, USBDN_DP[3]

and USBDN_DM[3] respectively are connected

through the analog switch to the upstream port

USBUP_DP and USBUP_DM. PortSwap setting has

no effect in Bypass Mode.

Serial Port Interface

Serial Data

SDA

I/OD

I

2

C Serial Data

Serial Clock

SCL

I

Serial Clock (SCL)