2004 Microchip Technology Inc.

DS21908A-page 1

MCP6S91/2/3

Features

• Multiplexed Inputs: 1 or 2 channels

• 8 Gain Selections:

- +1, +2, +4, +5, +8, +10, +16 or +32 V/V

• Serial Peripheral Interface (SPI

™

)

• Rail-to-Rail Input and Output

• Low Gain Error: ±1% (max.)

• Offset Mismatch Between Channels: 0 µV

• High Bandwidth: 1 to 18 MHz (typ.)

• Low Noise: 10 nV/

√

Hz @ 10 kHz (typ.)

• Low Supply Current: 1.0 mA (typ.)

• Single Supply: 2.5V to 5.5V

• Extended Temperature Range: -40°C to +125°C

Typical Applications

• A/D Converter Driver

• Multiplexed Analog Applications

• Data Acquisition

• Industrial Instrumentation

• Test Equipment

• Medical Instrumentation

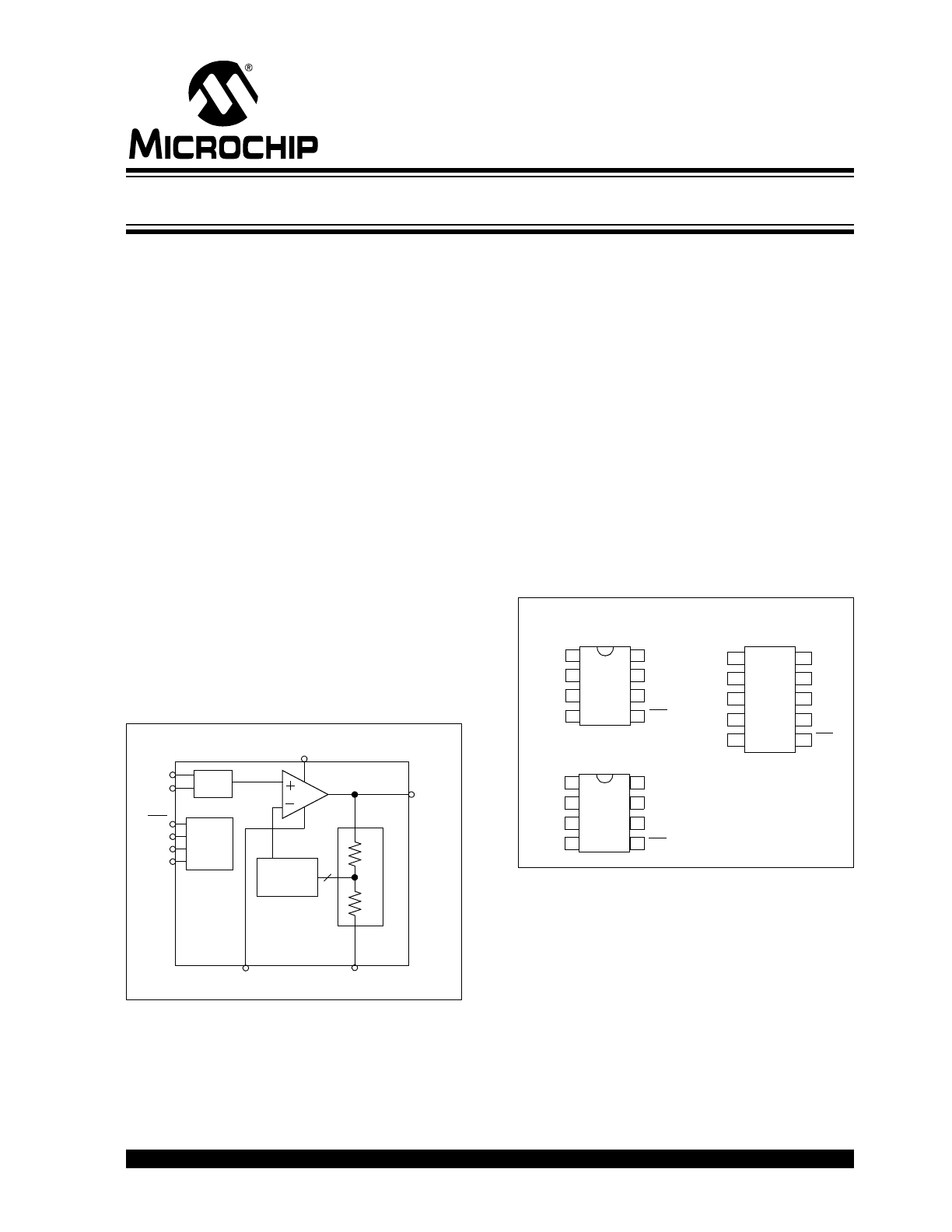

Block Diagram

Description

The Microchip Technology Inc. MCP6S91/2/3 are

analog Programmable Gain Amplifiers (PGAs). They

can be configured for gains from +1 V/V to +32 V/V and

the input multiplexer can select one of up to two chan-

nels through a SPI port. The serial interface can also

put the PGA into shutdown to conserve power. These

PGAs are optimized for high-speed, low offset voltage

and single-supply operation with rail-to-rail input and

output capability. These specifications support single-

supply applications needing flexible performance or

multiple inputs.

The one-channel MCP6S91 and the two-channel

MCP6S92 are available in 8-pin PDIP, SOIC and MSOP

packages. The two-channel MCP6S93 is available in a

10-pin MSOP package. All parts are fully specified from

-40°C to +125°C.

Package Types

V

OUT

V

REF

V

DD

CS

SI

SO

SCK

CH1

CH0

V

SS

8

R

F

R

G

MUX

SPI™

Logic

Gain

Switches

R

e

si

sto

r La

dde

r (R

LA

D

)

V

REF

CH0

V

SS

SI

SCK

1

2

3

4

8

7

6

5

V

DD

CS

V

OUT

MCP6S91

PDIP, SOIC, MSOP

CH1

CH0

V

SS

SI

SCK

1

2

3

4

8

7

6

5

V

DD

CS

V

OUT

MCP6S92

PDIP, SOIC, MSOP

CH0

V

OUT

CH1

CS

1

2

3

4

10

9

8

7 SI

SCK

5

6

V

REF

V

DD

SO

V

SS

MCP6S93

MSOP

Single-Ended, Rail-to-Rail I/O, Low-Gain PGA

2004 Microchip Technology Inc.

DS21908A-page 2

MCP6S91/2/3

1.0

ELECTRICAL

CHARACTERISTICS

Absolute Maximum Ratings †

V

DD

– V

SS

........................................................................7.0V

All inputs and outputs..................... V

SS

– 0.3V to V

DD

+ 0.3V

Difference Input voltage ....................................... |V

DD

– V

SS

|

Output Short Circuit Current ..................................continuous

Current at Input Pin

.............................................................±

2 mA

Current at Output and Supply Pins

................................ ±

30 mA

Storage temperature .....................................-65°C to +150°C

Junction temperature .................................................. +150°C

ESD protection on all pins (HBM; MM)

................ ≥

4 kV; 200V

† Notice: Stresses above those listed under “Maximum

Ratings” may cause permanent damage to the device. This is

a stress rating only and functional operation of the device at

those or any other conditions above those indicated in the

operational listings of this specification is not implied.

Exposure to maximum rating conditions for extended periods

may affect device reliability.

PIN FUNCTION TABLE

Name

Function

V

OUT

Analog Output

CH0, CH1 Analog Inputs

V

REF

External Reference Pin

V

SS

Negative Power Supply

CS

SPI Chip Select

SI

SPI Serial Data Input

SO

SPI Serial Data Output

SCK

SPI Clock Input

V

DD

Positive Power Supply

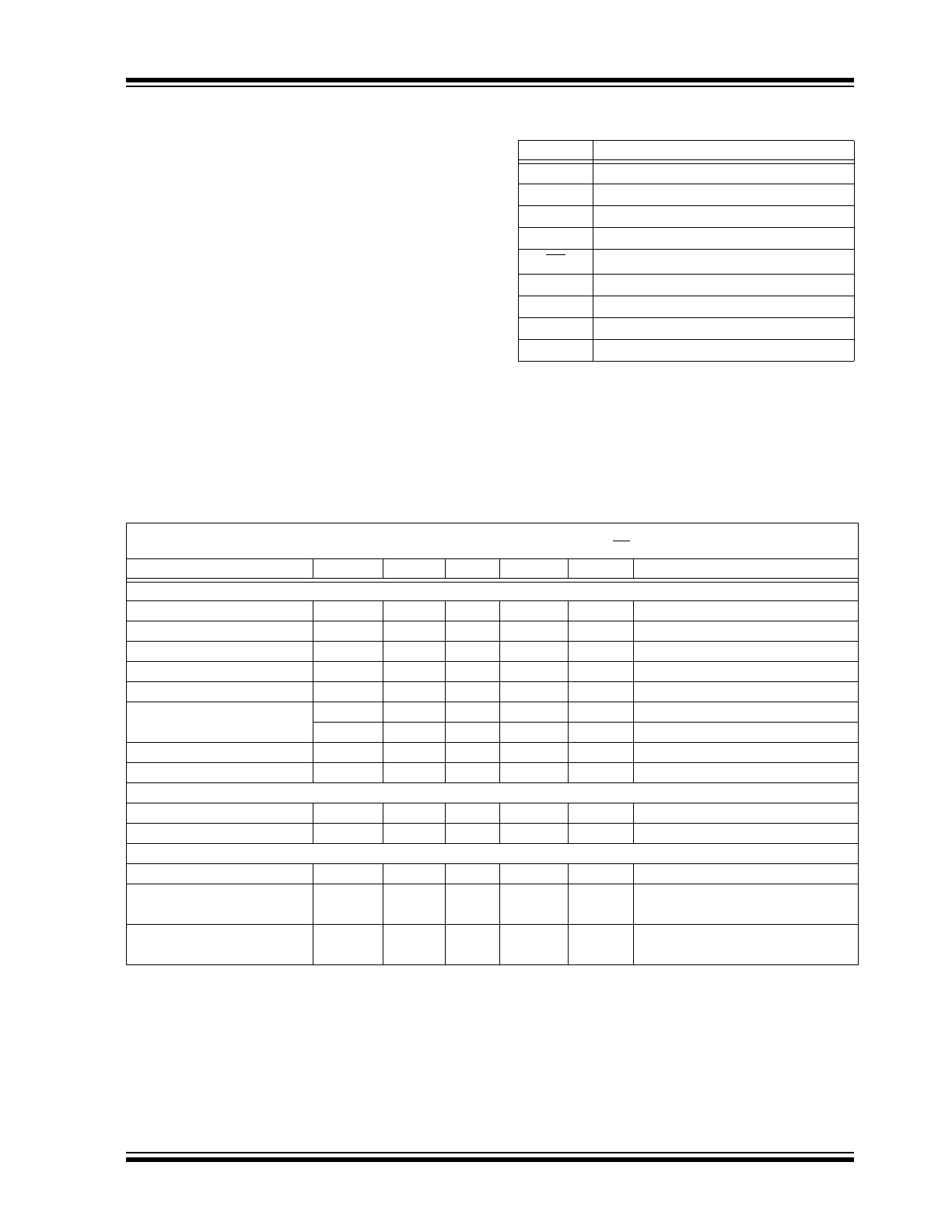

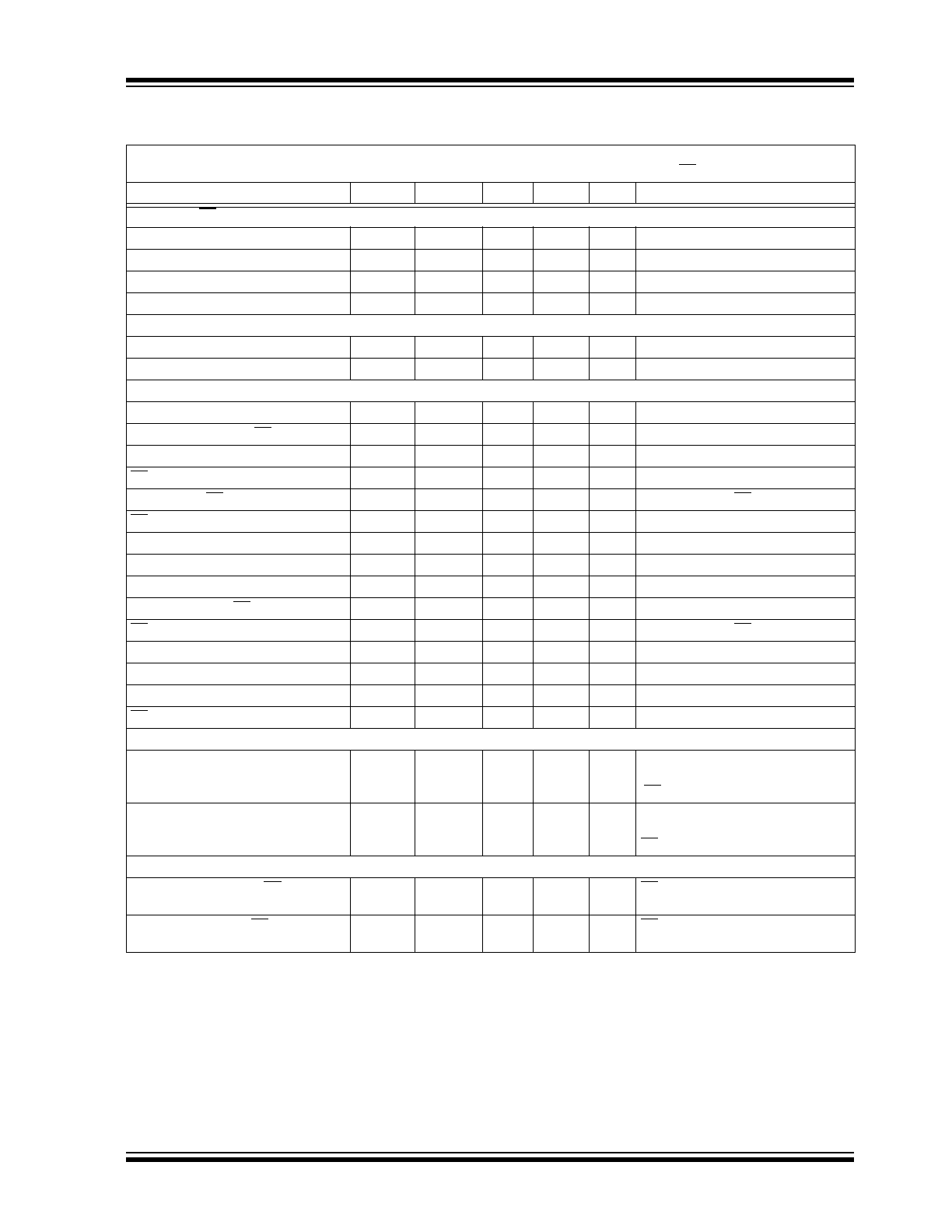

DC CHARACTERISTICS

Electrical Specifications: Unless otherwise indicated, T

A

= +25°C, V

DD

= +2.5V to +5.5V, V

SS

= GND, V

REF

= V

SS

, G = +1 V/V,

Input = CH0 = (0.3V)/G, CH1 = 0.3V, R

L

= 10 k

Ω

to V

DD

/2, SI and SCK are tied low and CS is tied high.

Parameters

Sym

Min

Typ

Max

Units

Conditions

Amplifier Inputs (CH0, CH1)

Input Offset Voltage

V

OS

-4

—

+4

mV

G = +1

Input Offset Voltage Mismatch

∆

V

OS

—

0

—

µV

Between inputs (CH0, CH1)

Input Offset Voltage Drift

∆

V

OS

/

∆

T

A

—

±1.8

—

µV/°C

T

A

= -40°C to +125°C

Power Supply Rejection Ratio

PSRR

70

90

—

dB

G = +1 (Note 1)

Input Bias Current

I

B

—

±1

—

pA

CHx = V

DD

/2

Input Bias Current at

Temperature

I

B

—

30

—

pA

CHx = V

DD

/2, T

A

= +85°C

I

B

—

600

—

pA

CHx = V

DD

/2, T

A

= +125°C

Input Impedance

Z

IN

—

10

13

||7

—

Ω

||pF

Input Voltage Range

V

IVR

V

SS

−

0.3

—

V

DD

+ 0.3

V

(Note 2)

Reference Input (V

REF

)

Input Impedance

Z

IN_REF

—

(5/G)||6

—

k

Ω

||pF

Voltage Range

V

IVR_REF

V

SS

—

V

DD

V

(Note 2)

Amplifier Gain

Nominal Gains

G

—

1 to 32

—

V/V

+1, +2, +4, +5, +8, +10, +16 or +32

DC Gain Error

G = +1

g

E

-0.2

—

+0.2

%

V

OUT

≈

0.3V to V

DD

−

0.3V

G

≥

+2

g

E

-1.0

—

+1.0

%

V

OUT

≈

0.3V to V

DD

−

0.3V

DC Gain Drift

G = +1

∆

G/

∆

T

A

—

±0.0002

—

%/°C

T

A

= -40°C to +125°C

G

≥

+2

∆

G/

∆

T

A

—

±0.0004

—

%/°C

T

A

= -40°C to +125°C

Note

1:

R

LAD

(R

F

+R

G

in Figure 4-1) connects V

REF

, V

OUT

and the inverting input of the internal amplifier. The MCP6S92 has

V

REF

tied internally to V

SS

, so V

SS

is coupled to the internal amplifier and the PSRR spec describes PSRR+ only. It is

recommended that the MCP6S92’s V

SS

pin be tied directly to ground to avoid noise problems.

2:

The MCP6S92’s V

IVR

and V

IVR_REF

are not tested in production; they are set by design and characterization.

3:

I

Q

includes current in R

LAD

(typically 60 µA at V

OUT

= 0.3V). Both I

Q

and I

Q_SHDN

exclude digital switching currents.

2004 Microchip Technology Inc.

DS21908A-page 3

MCP6S91/2/3

Ladder Resistance

Ladder Resistance

R

LAD

3.4

4.9

6.4

k

Ω

(Note 1)

Ladder Resistance across

Temperature

∆

R

LAD

/

∆

T

A

—

+0.028

—

%/°C

T

A

= -40°C to +125°C (Note 1)

Amplifier Output

DC Output Non-linearity G = +1

V

ONL

—

±0.18

—

% of FSR V

OUT

≈

0.3V to V

DD

−

0.3V, V

DD

= 5.0V

G

≥

+2

V

ONL

—

±0.050

—

% of FSR V

OUT

≈

0.3V to V

DD

−

0.3V, V

DD

= 5.0V

Maximum Output Voltage Swing

V

OH_ANA

,

V

OL_ANA

V

SS

+ 20

—

V

DD

– 100

mV

G

≥

+2; 0.5V output overdrive

V

SS

+ 60

—

V

DD

– 60

G

≥

+2; 0.5V output overdrive,

V

REF

= V

DD

/2

Short Circuit Current

I

SC

—

±25

—

mA

Power Supply

Supply Voltage

V

DD

2.5

—

5.5

V

Minimum Valid Supply Voltage

V

DD_VAL

—

0.4

2.0

V

Register data still valid

Quiescent Current

I

Q

0.4

1.0

1.6

mA

I

O

= 0 (Note 3)

Quiescent Current, Shutdown

Mode

I

Q_SHDN

—

30

—

pA

I

O

= 0 (Note 3)

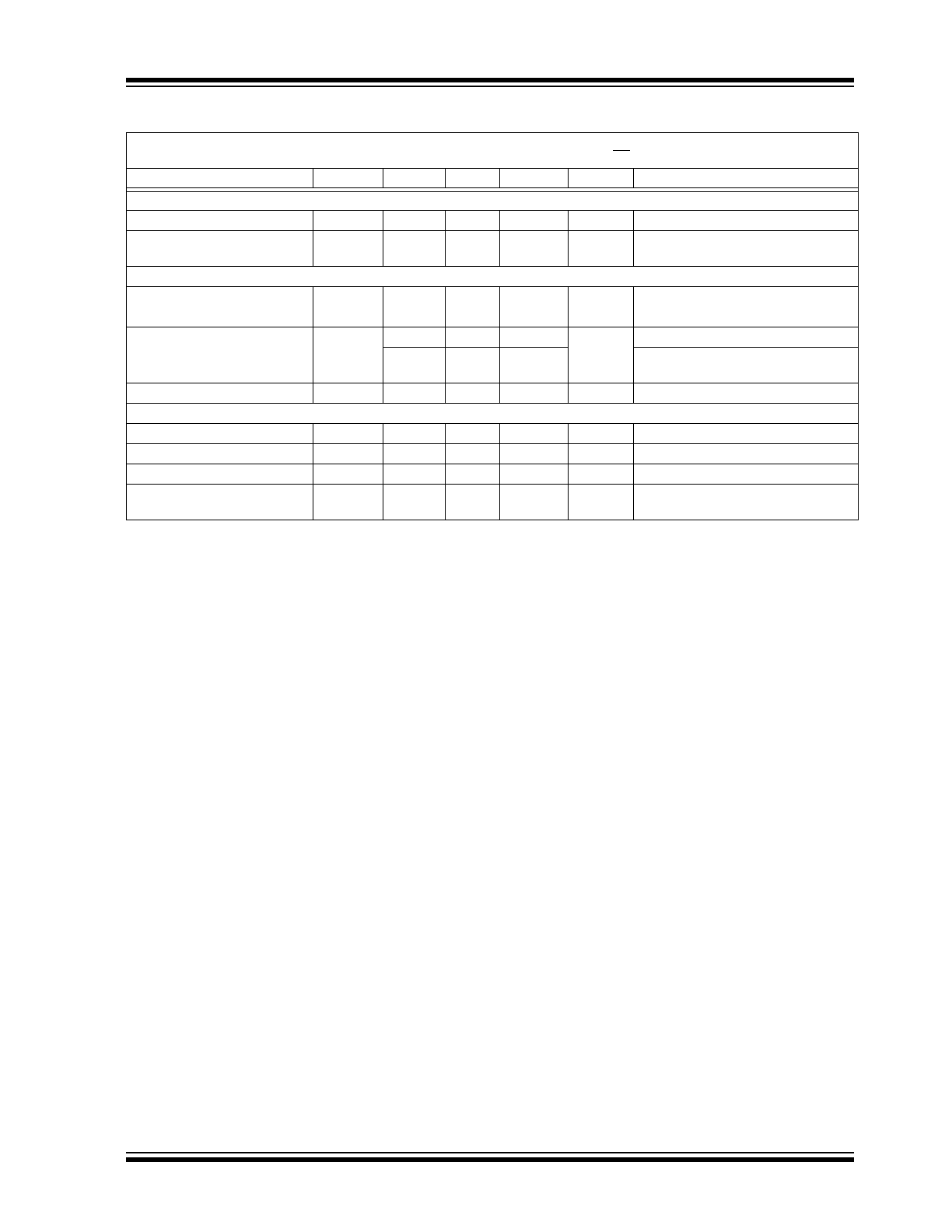

DC CHARACTERISTICS (CONTINUED)

Electrical Specifications: Unless otherwise indicated, T

A

= +25°C, V

DD

= +2.5V to +5.5V, V

SS

= GND, V

REF

= V

SS

, G = +1 V/V,

Input = CH0 = (0.3V)/G, CH1 = 0.3V, R

L

= 10 k

Ω

to V

DD

/2, SI and SCK are tied low and CS is tied high.

Parameters

Sym

Min

Typ

Max

Units

Conditions

Note

1:

R

LAD

(R

F

+R

G

in Figure 4-1) connects V

REF

, V

OUT

and the inverting input of the internal amplifier. The MCP6S92 has

V

REF

tied internally to V

SS

, so V

SS

is coupled to the internal amplifier and the PSRR spec describes PSRR+ only. It is

recommended that the MCP6S92’s V

SS

pin be tied directly to ground to avoid noise problems.

2:

The MCP6S92’s V

IVR

and V

IVR_REF

are not tested in production; they are set by design and characterization.

3:

I

Q

includes current in R

LAD

(typically 60 µA at V

OUT

= 0.3V). Both I

Q

and I

Q_SHDN

exclude digital switching currents.

2004 Microchip Technology Inc.

DS21908A-page 4

MCP6S91/2/3

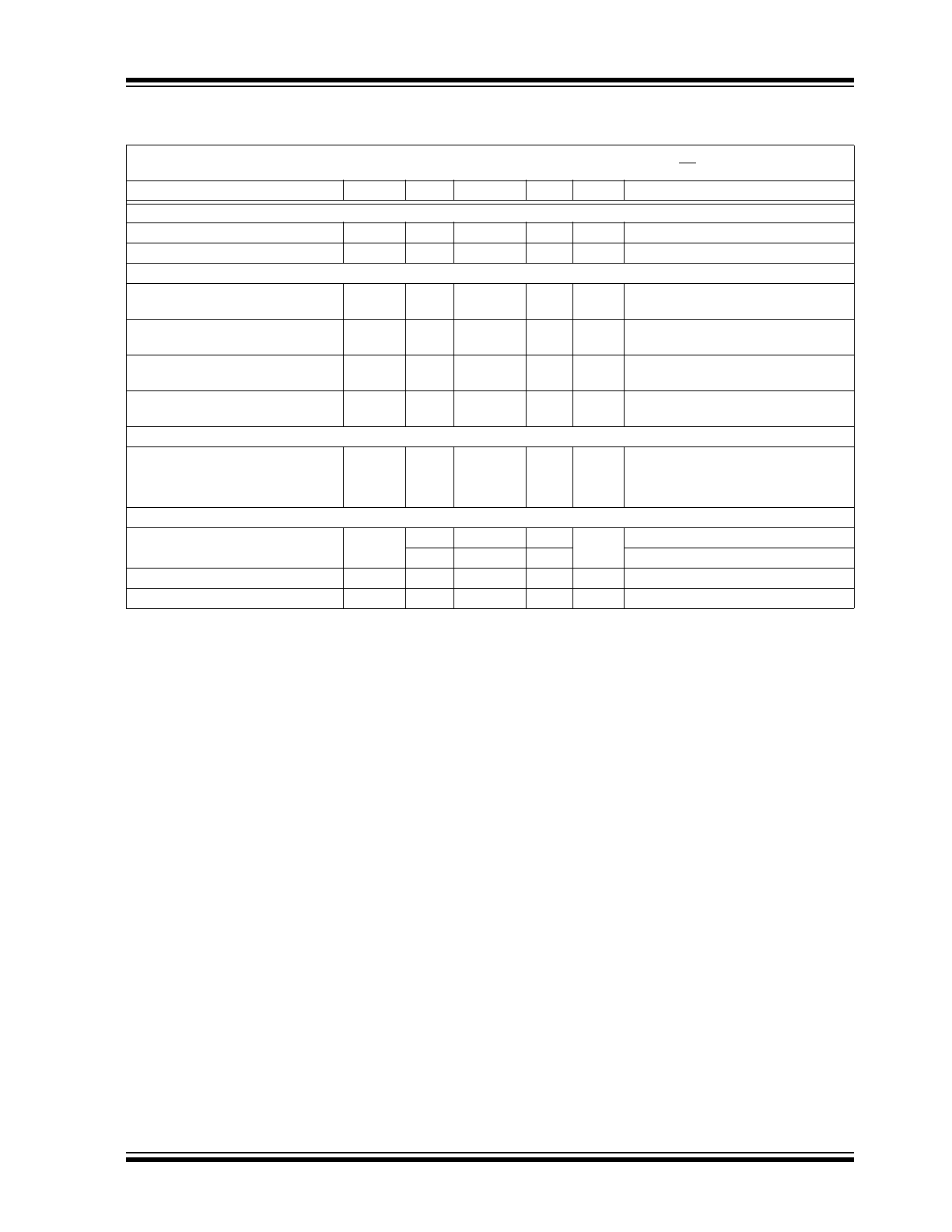

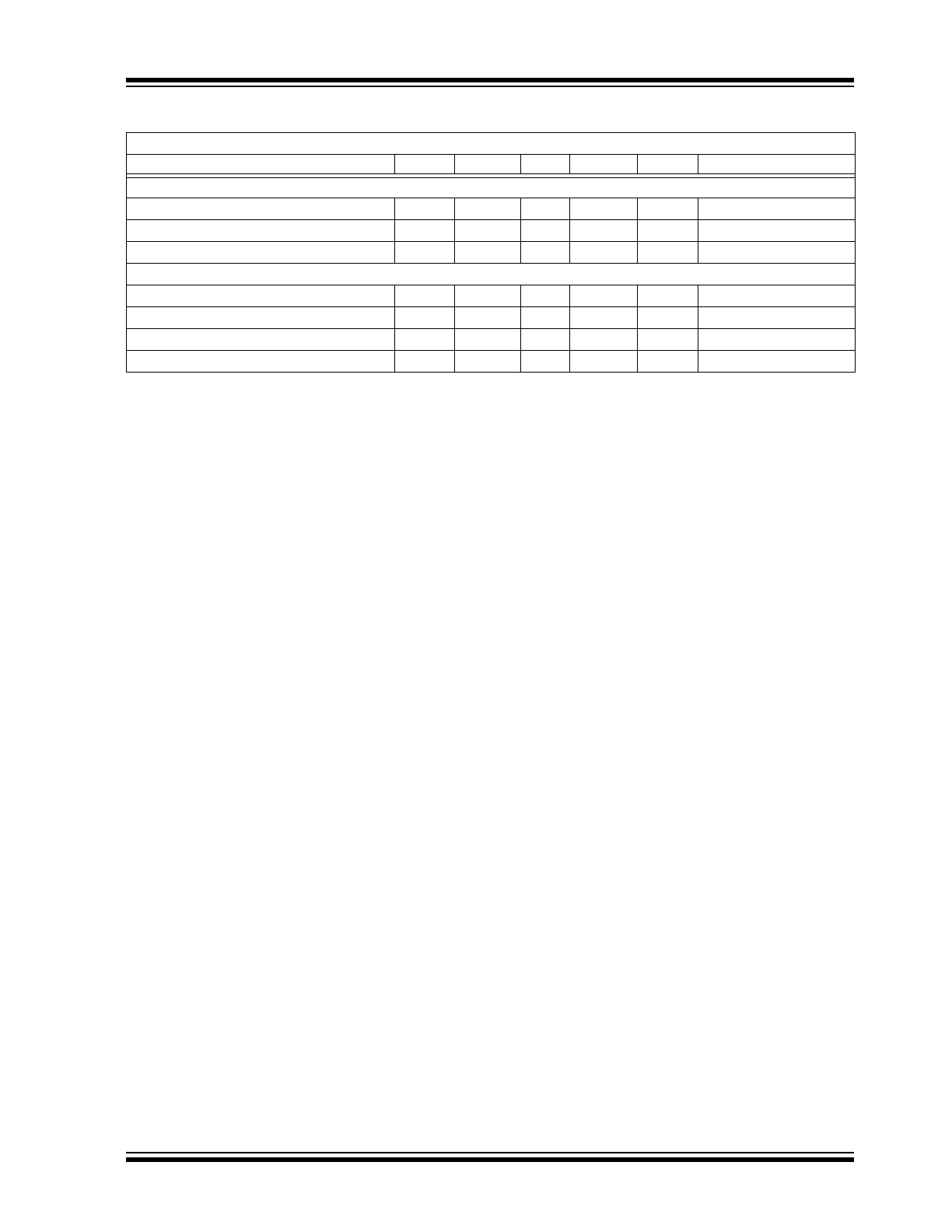

AC CHARACTERISTICS

Electrical Specifications: Unless otherwise indicated, T

A

= +25°C, V

DD

= +2.5V to +5.5V, V

SS

= GND, V

REF

= V

SS

, G = +1 V/V,

Input = CH0 = (0.3V)/G, CH1 = 0.3V, R

L

= 10 k

Ω

to V

DD

/2, C

L

= 60 pF, SI and SCK are tied low and CS is tied high.

Parameters

Sym

Min

Typ

Max

Units

Conditions

Frequency Response

-3 dB Bandwidth

BW

—

1 to 18

—

MHz

All gains; V

OUT

< 100 mV

P-P

(Note 1)

Gain Peaking

GPK

—

0

—

dB

All gains; V

OUT

< 100 mV

P-P

Total Harmonic Distortion plus Noise

f = 20 kHz, G = +1 V/V

THD+N

—

0.0011

—

%

V

OUT

= 1.5V ± 1.0 V

PK

, V

DD

= 5.0V,

BW = 80 kHz, R

L

= 10 k

Ω

to 1.5V

f = 20 kHz, G = +1 V/V

THD+N

—

0.0089

—

%

V

OUT

= 2.5V ± 1.0 V

PK

, V

DD

= 5.0V,

BW = 80 kHz

f = 20 kHz, G = +4 V/V

THD+N

—

0.0045

—

%

V

OUT

= 2.5V ± 1.0 V

PK

, V

DD

= 5.0V,

BW = 80 kHz

f = 20 kHz, G = +16 V/V

THD+N

—

0.028

—

%

V

OUT

= 2.5V ± 1.0 V

PK

, V

DD

= 5.0V,

BW = 80 kHz

Step Response

Slew Rate

SR

—

4.0

—

V/µs

G = 1, 2

—

11

—

V/µs

G = 4, 5, 8, 10

—

22

—

V/µs

G = 16, 32

Noise

Input Noise Voltage

E

ni

—

4.5

—

µV

P-P

f = 0.1 Hz to 10 Hz (Note 2)

—

30

—

f = 0.1 Hz to 200 kHz (Note 2)

Input Noise Voltage Density

e

ni

—

10

—

nV/

√

Hz f = 10 kHz (Note 2)

Input Noise Current Density

i

ni

—

4

—

fA/

√

Hz

f = 10 kHz

Note

1:

See Table 4-1 for a list of typical numbers and Figure 2-25 for the frequency response versus gain.

2:

E

ni

and e

ni

include ladder resistance noise. See Figure 2-12 for e

ni

versus G data.

2004 Microchip Technology Inc.

DS21908A-page 5

MCP6S91/2/3

DIGITAL CHARACTERISTICS

Electrical Specifications: Unless otherwise indicated, T

A

= 25°C, V

DD

= +2.5V to +5.5V, V

SS

= GND, V

REF

= V

SS

, G = +1 V/V,

Input = CH0 = (0.3V)/G, CH1 = 0.3V, R

L

= 10 k

Ω

to V

DD

/2, C

L

= 60 pF, SI and SCK are tied low and CS is tied high.

Parameters

Sym

Min

Typ

Max

Units

Conditions

SPI Inputs (CS, SI, SCK)

Logic Threshold, Low

V

IL

0

—

0.3V

DD

V

Input Leakage Current

I

IL

-1.0

—

+1.0

µA

Logic Threshold, High

V

IH

0.7 V

DD

—

V

DD

V

Amplifier Output Leakage Current

—

-1.0

—

1.0

µA

In Shutdown mode

SPI Output (SO, for MCP6S93)

Logic Threshold, Low

V

OL_DIG

V

SS

—

V

SS

+0.4

V

I

OL

= 2.1 mA, V

DD

= 5V

Logic Threshold, High

V

OH_DIG

V

DD

– 0.5

—

V

DD

V

I

OH

= -400 µA

SPI Timing

Pin Capacitance

C

PIN

—

10

—

pF

All digital I/O pins

Input Rise/Fall Times (CS, SI, SCK)

t

RFI

—

—

2

µs

(Note 1)

Output Rise/Fall Times (SO)

t

RFO

—

5

—

ns

MCP6S93

CS High Time

t

CSH

40

—

—

ns

SCK Edge to CS Fall Setup Time

t

CS0

10

—

—

ns

SCK edge when CS is high

CS Fall to First SCK Edge Setup Time

t

CSSC

40

—

—

ns

SCK Frequency

f

SCK

—

—

10

MHz

V

DD

= 5V (Note 2)

SCK High Time

t

HI

40

—

—

ns

SCK Low Time

t

LO

40

—

—

ns

SCK Last Edge to CS Rise Setup Time

t

SCCS

30

—

—

ns

CS Rise to SCK Edge Setup Time

t

CS1

100

—

—

ns

SCK edge when CS is high

SI Setup Time

t

SU

40

—

—

ns

SI Hold Time

t

HD

10

—

—

ns

SCK to SO Valid Propagation Delay

t

DO

—

—

80

ns

MCP6S93

CS Rise to SO Forced to Zero

t

SOZ

—

—

80

ns

MCP6S93

Channel and Gain Select Timing

Channel Select Time

t

CH

—

1.5

—

µs

CHx = 0.6V, CHy = 0.3V, G = 1,

CHx to CHy select,

CS = 0.7 V

DD

to V

OUT

90% point

Gain Select Time

t

G

—

1

—

µs

CHx = CHy = 0.3V,

G = 5 to G = 1 select,

CS = 0.7 V

DD

to V

OUT

90% point

Shutdown Mode Timing

Out of Shutdown mode (CS goes high)

to Amplifier Output Turn-on Time

t

ON

—

3.5

10

µs

CS = 0.7 V

DD

to V

OUT

90% point

Into Shutdown mode (CS goes high) to

Amplifier Output High-Z Turn-off Time

t

OFF

—

1.5

—

µs

CS = 0.7 V

DD

to V

OUT

90% point

Note

1:

Not tested in production. Set by design and characterization.

2:

When using the device in the daisy-chain configuration, maximum clock frequency is determined by a combination of

propagation delay time (t

DO

≤

80 ns), data input set-up time (t

SU

≥

40 ns), SCK high time (t

HI

≥

40 ns) and SCK rise and

fall times of 5 ns. Maximum f

SCK

is therefore

≈

5.8 MHz.

2004 Microchip Technology Inc.

DS21908A-page 6

MCP6S91/2/3

TEMPERATURE CHARACTERISTICS

Electrical Specifications: Unless otherwise indicated, V

DD

= +2.5V to +5.5V, V

SS

= GND.

Parameters

Sym

Min

Typ

Max

Units

Conditions

Temperature Ranges

Specified Temperature Range

T

A

-40

—

+125

°C

(Note 1)

Operating Temperature Range

T

A

-40

—

+125

°C

Storage Temperature Range

T

A

-65

—

+150

°C

Thermal Package Resistances

Thermal Resistance, 8L-PDIP

θ

JA

—

85

—

°C/W

Thermal Resistance, 8L-SOIC

θ

JA

—

163

—

°C/W

Thermal Resistance, 8L-MSOP

θ

JA

—

206

—

°C/W

Thermal Resistance, 10L-MSOP

θ

JA

—

143

—

°C/W

Note 1:

Operation in this range must not cause T

J

to exceed Maximum Junction Temperature (+150°C).

2004 Microchip Technology Inc.

DS21908A-page 7

MCP6S91/2/3

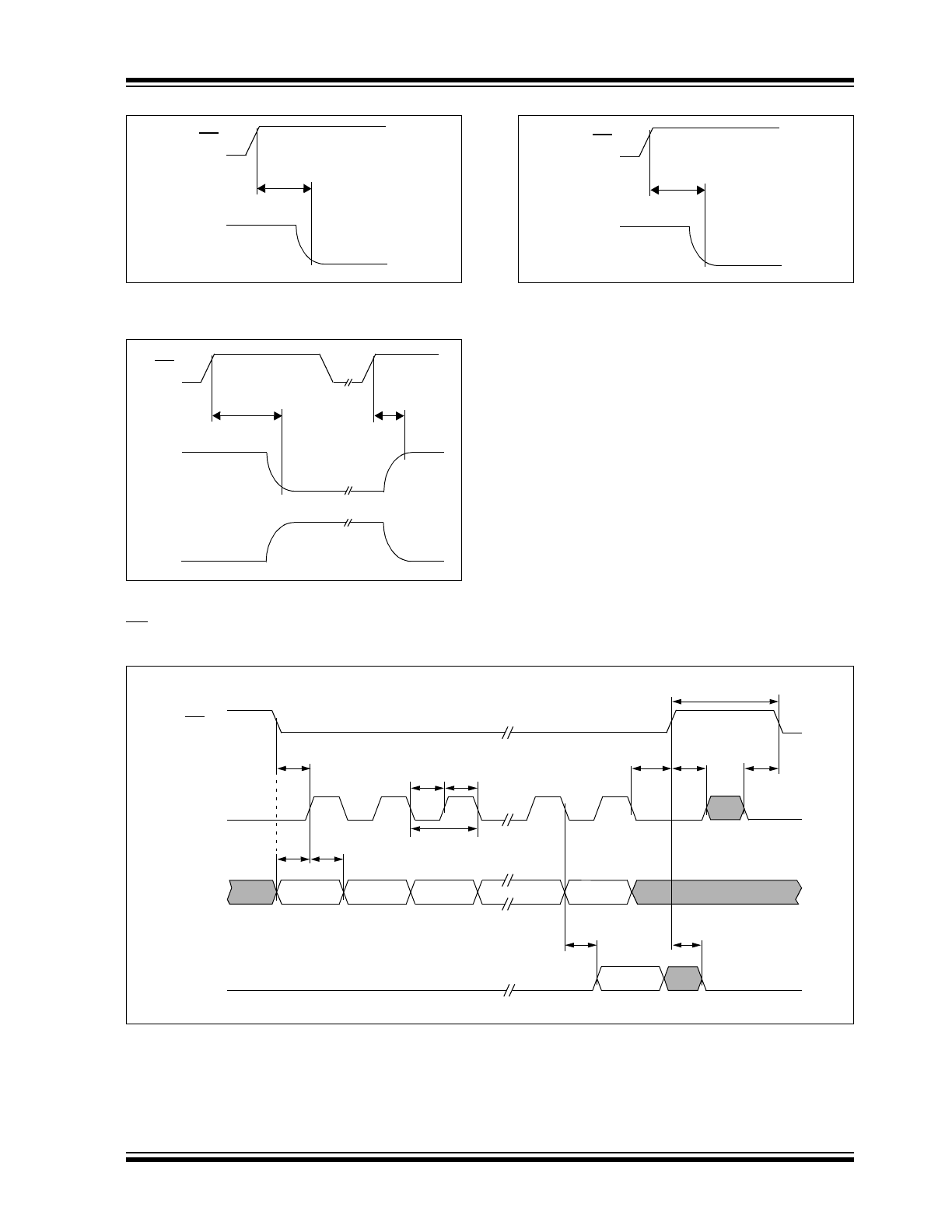

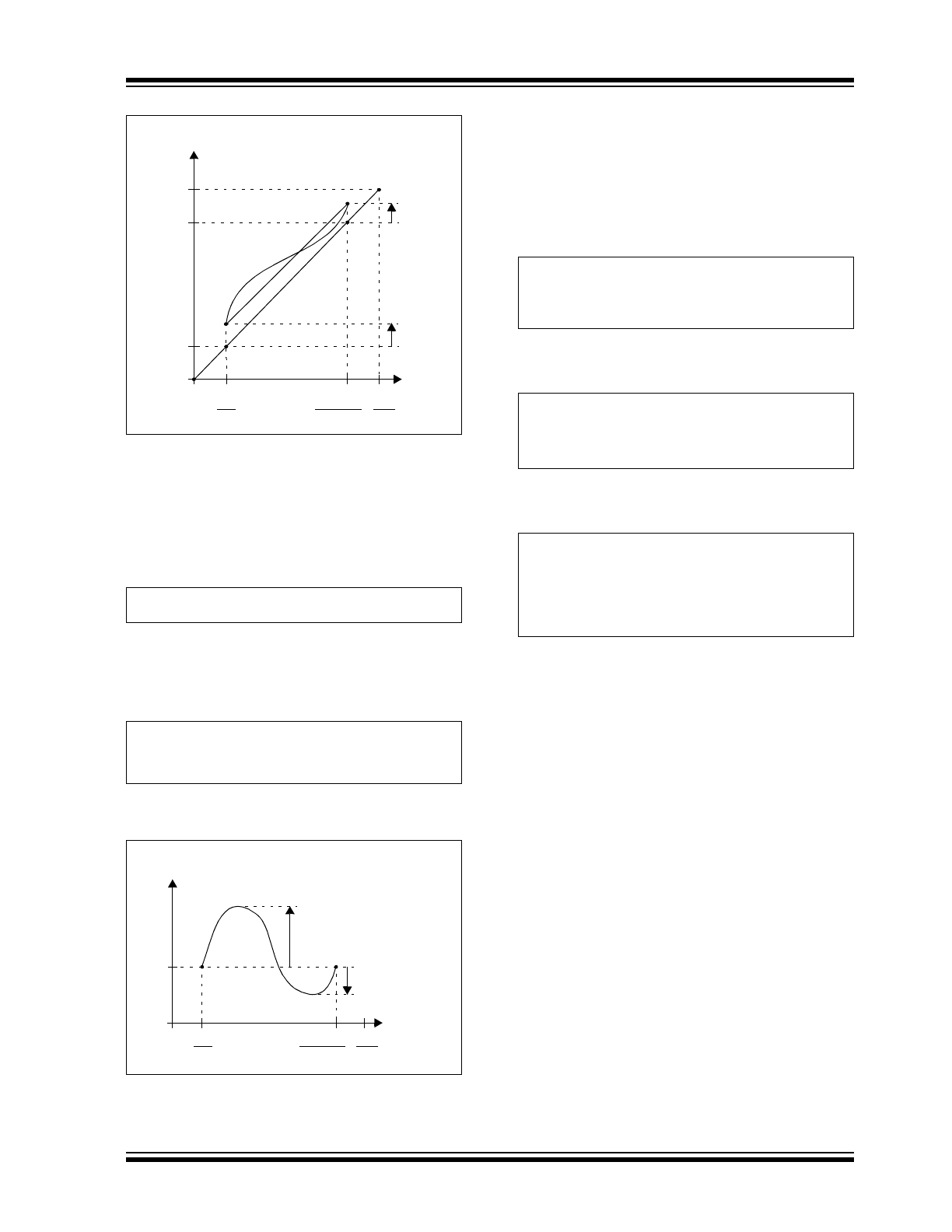

FIGURE 1-1:

Channel Select Timing

Diagram.

FIGURE 1-2:

PGA Shutdown Timing

Diagram (must enter correct commands before

CS goes high).

FIGURE 1-3:

Gain Select Timing

Diagram.

FIGURE 1-4:

Detailed SPI™ Serial Interface Timing; SPI 0,0 Mode.

CS

V

OUT

t

CH

0.6V

0.3V

CS

t

OFF

V

OUT

t

ON

Hi-Z

Hi-Z

I

SS

30 pA (typ.)

1.0 mA (typ.)

0.3V

CS

V

OUT

t

G

1.5V

0.3V

CS

SCK

SI

t

SU

t

HD

t

CSSC

t

SCCS

t

CSH

SO

(first 16 bits out are always zeros)

t

DO

t

SOZ

t

LO

t

HI

1/f

SCK

t

CS0

t

CS1

2004 Microchip Technology Inc.

DS21908A-page 8

MCP6S91/2/3

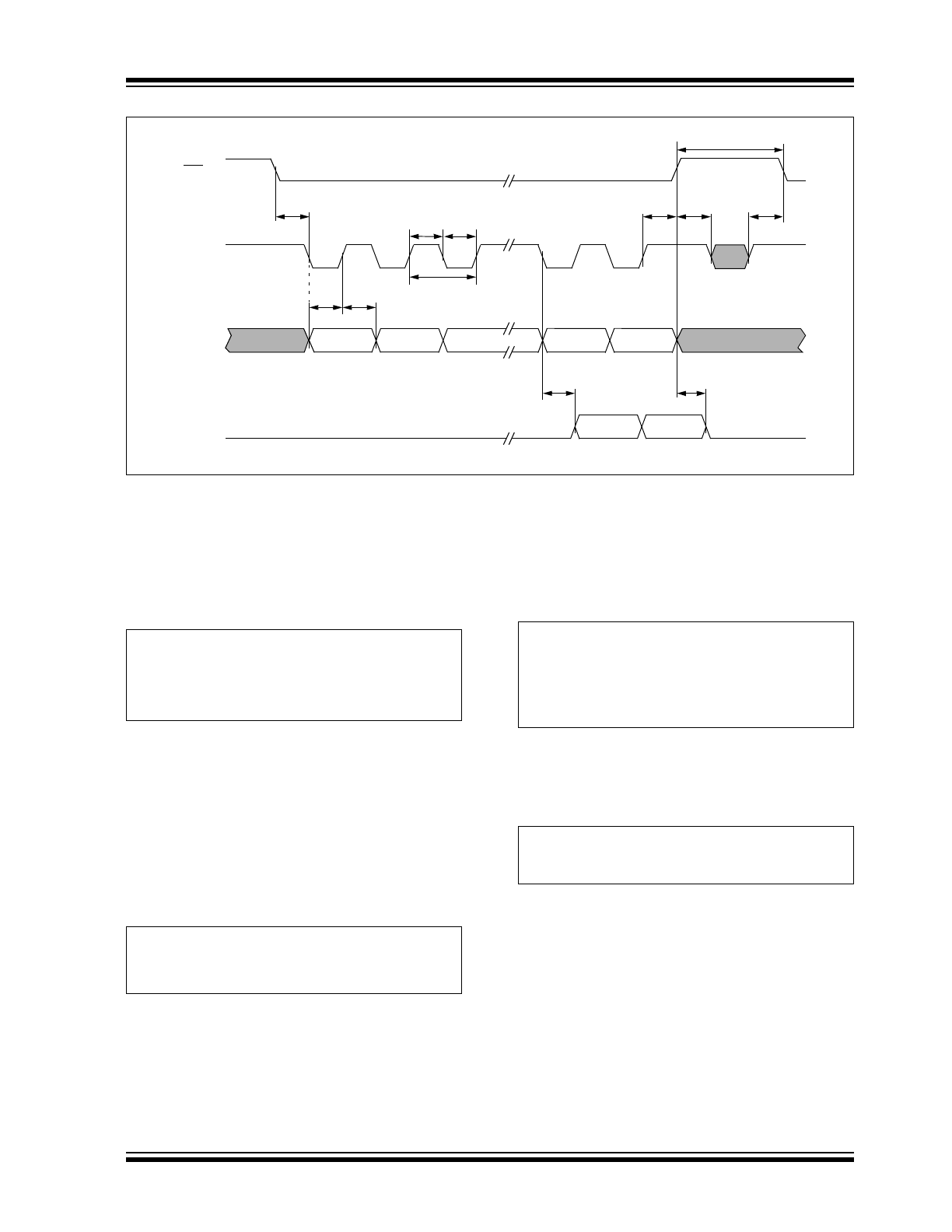

FIGURE 1-5:

Detailed SPI™ Serial Interface Timing; SPI 1,1 Mode.

1.1

DC Output Voltage Specs / Model

1.1.1

IDEAL MODEL

The ideal PGA output voltage (V

OUT

) is:

EQUATION 1-1:

(see Figure 1-6). This equation holds when there are

no gain or offset errors and when the V

REF

pin is tied to

a low-impedance source (<< 0.1

Ω

) at ground potential

(V

SS

= 0V).

1.1.2

LINEAR MODEL

The PGA’s linear region of operation, including offset

and gain errors, is modeled by the line V

O_LIN

shown in

Figure 1-6.

EQUATION 1-2:

The end points of this line are at V

O_ID

= 0.3V and

V

DD

– 0.3V. Figure 1-6 shows the relationship between

the gain and offset specifications referred to in the

electrical specifications as follows:

EQUATION 1-3:

The DC Gain Drift (

∆

G/

∆

T

A

) can be calculated from the

change in g

E

across temperature. This is shown in the

following equation:

EQUATION 1-4:

CS

SCK

SI

t

SU

t

HD

t

CSSC

t

SCCS

SO

(first 16 bits out are always zeros)

t

DO

t

SOZ

t

HI

t

LO

1/f

SCK

t

CS1

t

CSH

t

CS0

Where:

G is the nominal gain

V

O_ID

G

VIN

=

V

REF

V

SS

0V

=

=

V

O_LIN

G 1

g

E

+

(

)

V

IN

0.3V

G

-----------

V

OS

+

–

0.3V

+

=

V

REF

V

SS

0V

=

=

g

E

100%

V

2

V

1

–

G V

DD

0.6V

–

(

)

--------------------------------------

=

V

OS

V

1

G 1

g

E

+

(

)

-------------------------

=

G

+1

=

G

∆

T

A

∆

⁄

g

E

∆

T

A

∆

----------

=

2004 Microchip Technology Inc.

DS21908A-page 9

MCP6S91/2/3

FIGURE 1-6:

Output Voltage Model with

the standard condition V

REF

= V

SS

= 0V.

1.1.3

OUTPUT NON-LINEARITY

Figure 1-7 shows the Integral Non-Linearity (INL) of the

output voltage.

EQUATION 1-5:

The output non-linearity specification in the Electrical

Specifications (with units of: % of FSR) is related to

Figure 1-7 by:

EQUATION 1-6:

The Full-Scale Range (FSR) is V

DD

– 0.6V

(0.3V to V

DD

– 0.3V).

FIGURE 1-7:

Output Voltage INL with the

standard condition V

REF

= V

SS

= 0 V.

1.1.4

DIFFERENT V

REF

CONDITIONS

Some of the plots in Section 2.0 “Typical Performance

Curves”, have the conditions V

REF

= V

DD

/2 or

V

REF

= V

DD

. The equations and figures above are easily

modified for these conditions. The ideal V

OUT

equation

becomes:

EQUATION 1-7:

The complete linear model is:

EQUATION 1-8:

where the new V

IN

end points are:

EQUATION 1-9:

The equations for extracting the specifications do not

change.

0

0

0.3

V

DD

– 0.3

V

DD

V

O

U

T

V

OUT

(V)

V

IN

(V)

0.3

V

DD

– 0.3 V

DD

G

G

G

V

1

V

O

_I

D

V

O

_L

IN

V

2

INL

V

OUT

V

O_LIN

–

=

V

ONL

max V

3

V

4

,

(

)

V

DD

0.6V

–

------------------------------- 100%

⋅

=

0

INL (V)

V

IN

(V)

0.3

V

DD

– 0.3 V

DD

G

G

G

0

V

3

V

4

V

O_ID

V

REF

G V

IN

V

REF

–

(

)

+

=

V

DD

V

REF

V

SS

0V

=

>

≥

V

ON_LIN

G 1

g

E

+

(

)

V

IN

V

IN_L

V

OS

+

–

(

)

0.3V

+

=

V

R EF

V

SS

0V

=

=

V

IN_L

0.3V

V

REF

–

G

------------------------------

V

REF

+

=

V

IN_H

V

DD

0.3V

–

V

REF

–

G

-----------------------------------------------

V

REF

+

=

2004 Microchip Technology Inc.

DS21908A-page 10

MCP6S91/2/3

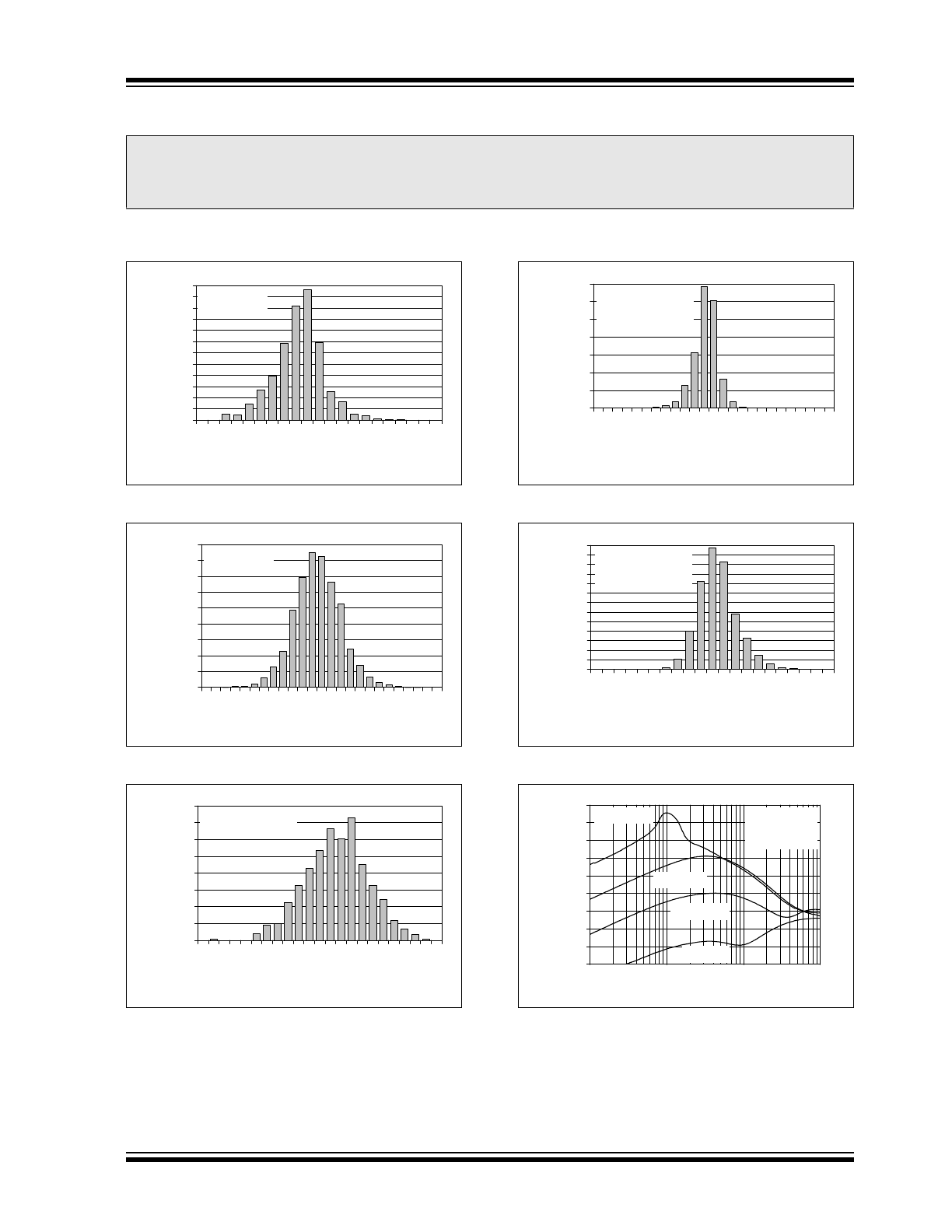

2.0

TYPICAL PERFORMANCE CURVES

Note: Unless otherwise indicated, T

A

= +25°C, V

DD

= +2.5V to +5.5V, V

SS

= GND, V

REF

= V

SS

, G = +1 V/V,

Input = CH0 = (0.3V)/G, CH1 = 0.3V, R

L

= 10 k

Ω

to V

DD

/2 and C

L

= 60 pF.

FIGURE 2-1:

DC Gain Error, G = +1.

FIGURE 2-2:

DC Gain Error, G

≥

+2.

FIGURE 2-3:

Ladder Resistance Drift.

FIGURE 2-4:

DC Gain Drift, G = +1.

FIGURE 2-5:

DC Gain Drift, G

≥

+2.

FIGURE 2-6:

Crosstalk vs. Frequency

(circuit in Figure 6-4).

Note:

The graphs and tables provided following this note are a statistical summary based on a limited number of

samples and are provided for informational purposes only. The performance characteristics listed herein

are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified

operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

0%

2%

4%

6%

8%

10%

12%

14%

16%

18%

20%

22%

24%

-0

.1

0

-0

.0

8

-0

.0

6

-0

.0

4

-0

.0

2

0.0

0

0.0

2

0.0

4

0.0

6

0.0

8

0.1

0

DC Gain Error (%)

P

e

rcen

tag

e

o

f O

ccur

re

nces

600 Samples

G = +1

0%

2%

4%

6%

8%

10%

12%

14%

16%

18%

-0

.6

-0

.5

-0

.4

-0

.3

-0

.2

-0

.1

0.0

0.1

0.2

0.3

0.4

0.5

0.6

DC Gain Error (%)

P

e

rcen

tag

e

o

f O

ccur

re

nce

s

600 Samples

G

≥

+2

0%

2%

4%

6%

8%

10%

12%

14%

16%

0

.019

0

.020

0

.021

0

.022

0

.023

0

.024

0

.025

0

.026

0

.027

0

.028

0

.029

0

.030

Ladder Resistance Drift (%/°C)

P

e

rc

ent

a

ge of Occu

rr

enc

e

s

597 Samples

T

A

= -40 to +125°C

0%

5%

10%

15%

20%

25%

30%

35%

-0.

0006

-0.

0005

-0.

0004

-0.

0003

-0.

0002

-0.

0001

0.

0000

0.

0001

0.

0002

0.

0003

0.

0004

0.

0005

0.

0006

DC Gain Drift (%/°C)

Pe

rce

n

ta

ge o

f O

ccur

re

nce

s

600 Samples

G = +1

T

A

= -40 to +125°C

0%

2%

4%

6%

8%

10%

12%

14%

16%

18%

20%

22%

24%

26%

-0.

0020

-0.

0016

-0.

0012

-0.

0008

-0.

0004

0.

0000

0.

0004

0.

0008

0.

0012

0.

0016

0.

0020

DC Gain Drift (%/°C)

Pe

rce

n

ta

ge o

f O

ccur

re

nce

s

600 Samples

G

≥

+2

T

A

= -40 to +125°C

-100

-90

-80

-70

-60

-50

-40

-30

-20

-10

1.E+05

1.E+06

1.E+07

1.E+08

Frequency (Hz)

C

ross

tal

k, In

pu

t R

e

fe

rr

ed

(d

B

)

V

DD

= 5.0V

G = +32 V/V

CH0 selected

R

S

= 1 k

Ω

R

S

= 0

Ω

R

S

= 100

Ω

R

S

= 10 k

Ω

100k

100M

10M

1M