2009 - 2015 Microchip Technology Inc.

DS00001996A-page 1

Highlights

• High Performance Embedded Controller (EC)

• ACPI 2.0 Compliant

• PC2001 Compliant

• LPC Interface

- Supports LPC Bus frequencies of 19MHz to

33MHz

- Multiplexed Command, Address and Data

Bus

- Serial IRQ Interface Compatible with Serial-

ized IRQ Support for PCI Systems

- PME Interface

• 3.3-Volt I/O

• 128-pin QFP RoHS Compliant Package

• System Watch Dog Timer (WDT)

• Battery Backed Resources

- Power-Fail Status Register

- VBat backed 64 byte memory

• Extreme Low S5

- Enables power saving by shutting down

standby voltage regulators in system S5 state

- System wake from power button press

- System wake from LAN

• Two EC-based SMBus 2.0 Host Controllers

- Allows Master or Dual Slave Operation

- Controllers are Fully Operational on Standby

Power

- DMA-driven I

2

C Network Layer

- I

2

C Datalink Compatibility Mode

- Multi-Master Capable

- Supports Clock Stretching

- Programmable Bus Speeds

- 400 KHz Capable

- Hardware Bus Access “Fairness” Interface

- Detects SMBus Time-outs

- One controller can be multiplexed onto a low

voltage SMBus

• PECI Interface 2.0

- Supports PECI REQUEST# and PECI

READY signaling

- Supports up to 2 CPUs and 4 domains

• Temperature reading from PCH over SMBus

• Temperature reading from AMD-TSI over SMBus

• Temperature Monitor

- Monitoring up to 2 Remote Thermal Diodes

plus an Anti-Parallel Remote Thermal Diode

- Built-in ADC supports temperature readings

from -63 degrees Celsius to +192 degrees

Celsius

–Supports monitoring of discrete diodes (3904 type

diodes)

–Supports monitoring substrate diodes (45nm &

65nm processor diodes)

- Temperature resolution is 0.125 degrees Cel-

sius

- Internal Ambient Temperature Measurement

- Out-of-limit Temperature Event reporting

• Bi-directional PROCHOT# Pin

- Interrupt generation for PROCHOT Assert

events

- May be used by AMTA and PTTA features to

adjust fan control limits

- May be configured to force fans on full

- Supports PROCHOT Assertions to external

CPU

- Supports PROCHOT Throttle Events to

external CPU

- Supports Interrupt Event to Host

• Voltage Monitor

- Monitoring VBAT, VTR,VCC and Vtt power

supplies

- Monitoring of one external voltage

- Limit comparison on monitored values

• PWM (Pulse width Modulation) Outputs (4)

- Multiple Clock Rates

- 16-bit ON and 16-bit OFF Counters

• Fan tachometer Inputs (4)

- Programmable to monitor standard tachome-

ter outputs or locked rotor alarm outputs

- Generate tachometer event when speed of

fan drops below programmed limit

• Internal clock sources

- A Ring Oscillator generates 64 MHz clock

- SIO clocks derived from a 96MHz PLL syn-

chronized to a 14.318MHz clock input

- Main ring generates 32kHz standby clock

when external 32.768KHz clock source is off

• Low Battery Warning

SCH5627P

Desktop Embedded Controller with Fan Control,

Hardware Monitoring and PECI

SCH5627P

DS00001996A-page 2

2009 - 2015 Microchip Technology Inc.

• LED Control

- Two LEDs to indicate system state

• Programmable Wake-up Event Interface

• General Purpose Input/Output Pins (60 total)

• System Management Interrupt (SMI)

• GLUE Logic

- 4 Buffered PCI Reset Outputs

- Power OK Signal Generation

- Power Sequencing

- Power Supply Turn On Circuitry

- Resume Reset Signal Generation

- Speaker output

- Intrusion Detection

• 2.88MB Super I/O Floppy Disk Controller

- Licensed CMOS 765B Floppy Disk Controller

- Software and Register Compatible with

Microchip's Proprietary 82077AA Compatible

Core

- Configurable Open Drain/Push-Pull Output

Drivers

- Supports Vertical Recording Format

- 16-Byte Data FIFO

- 100% IBM® Compatibility

- Detects All Overrun and Underrun Conditions

- Sophisticated Power Control Circuitry (PCC)

Including Multiple Powerdown Modes for

Reduced Power Consumption

- DMA Enable Logic

- Data Rate and Drive Control Registers

- 480 Address, Up to Eight IRQ and Four DMA

Options

• Enhanced Digital Data Separator

- 1 Mbps, 500 Kbps, 300 Kbps, 250 Kbps Data

Rates

- Programmable Precompensation Modes

• Keyboard Controller

- 8042 Software Compatible

- 8 Bit Microcomputer

- 2k Bytes of Program ROM

- 256 Bytes of Data RAM

- Four Open Drain Outputs Dedicated for Key-

board/Mouse Interface

- Asynchronous Access to Two Data Registers

and One Status Register

- Supports Interrupt and Polling Access

- 8 Bit Counter Timer

- Port 92 Support

- Fast Gate A20 and KRESET Outputs

• Serial Ports

- Two Full Function Serial Ports

- High Speed NS16C550A Compatible UARTs

with Send/Receive 16-Byte FIFOs

- Programmable Baud Rate Generator

- Modem Control Circuitry

- Any LPC Address Configurable. 15 IRQ

Options

• Multi-Mode™ Parallel Port with ChiProtect™

- Standard Mode IBM PC/XT

®,

PC/AT

®

, and

PS/2™ Compatible Bi-directional Parallel

Port

- Enhanced Parallel Port (EPP) Compatible -

EPP 1.7 and EPP 1.9 (IEEE 1284 Compliant)

- IEEE 1284 Compliant Enhanced Capabilities

Port (ECP)

- ChiProtect Circuitry for Protection

- 960 Addresses, Up to 15 IRQ and Four DMA

Options

2009 - 2015 Microchip Technology Inc.

DS00001996A-page 3

SCH5627P

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at

docerrors@microchip.com

. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for cur-

rent devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the

revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site;

http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are

using.

Customer Notification System

Register on our web site at

www.microchip.com

to receive the most current information on all of our products.

SCH5627P

DS00001996A-page 4

2009 - 2015 Microchip Technology Inc.

Table of Contents

1.0 Introduction ..................................................................................................................................................................................... 5

2.0 Pin Layout ...................................................................................................................................................................................... 6

3.0 Signal Descriptions ....................................................................................................................................................................... 13

4.0 Block Diagram ............................................................................................................................................................................... 25

5.0 Power, Clocks and Reset .............................................................................................................................................................. 27

6.0 Host Interface ................................................................................................................................................................................ 30

7.0 Logical Device Configuration ........................................................................................................................................................ 38

8.0 Keyboard Controller ...................................................................................................................................................................... 53

9.0 Serial Port (UART) ........................................................................................................................................................................ 64

10.0 Parallel Port ................................................................................................................................................................................. 82

11.0 Floppy Disk Controller ................................................................................................................................................................. 98

12.0 Embedded Memory Interface .................................................................................................................................................... 135

13.0 PME Support ............................................................................................................................................................................. 144

14.0 SMI Support .............................................................................................................................................................................. 146

15.0 Low Battery Detection ............................................................................................................................................................... 147

16.0 Runtime Registers ..................................................................................................................................................................... 149

17.0 Intruder Detection Support ........................................................................................................................................................ 169

18.0 Glue Logic Hardware ................................................................................................................................................................ 171

19.0 GPIO Interface .......................................................................................................................................................................... 182

20.0 JTAG and XNOR ....................................................................................................................................................................... 191

21.0 Electrical Specifications ............................................................................................................................................................ 202

22.0 Timing Diagrams ....................................................................................................................................................................... 208

23.0 Package Outline ........................................................................................................................................................................ 229

Appendix A: Data Sheet Revision History ......................................................................................................................................... 230

The Microchip Web Site .................................................................................................................................................................... 231

Customer Change Notification Service ............................................................................................................................................. 231

Customer Support ............................................................................................................................................................................. 231

Product Identification System ............................................................................................................................................................ 232

2009 - 2015 Microchip Technology Inc.

DS00001996A-page 5

SCH5627P

1.0

INTRODUCTION

The SCH5627P is a 3.3V PC 2001 compliant Super I/O controller with an LPC interface. All legacy drivers used for

Super I/O components are supported making this interface transparent to the supporting software. The LPC bus also

supports power management, such as wake-up and sleep modes.

The SCH5627P provides temperature monitoring with auto fan control. The temperature monitor is capable of monitor-

ing up to three external diodes, one internal ambient temperature sensor or retrieving temperatures from external pro-

cessors that implement the PECI Interface. This device offers programmable automatic fan control support based on

one or more of these measured temperatures. There are four pulse width modulation (PWM) outputs with

high fre-

quency support as well as four fan tachometer inputs. In addition, there is support for a bi-directional PROCHOT# pin

that may be used to generate an interrupt, adjust the programmed temperature limits in the auto fan control logic, or

force the PWM outputs on full. The RRCC feature provides a linear relationship of temperature to fan speed.

The Glue Logic includes various power management logic; including generation of RSMRST# and Power OK signal

generation. There are also two LEDs to indicate power status. The part also provides a low battery warning circuit.

The SCH5627P provides 60 General Purpose I/O control pins, which offer flexibility to the system designer.

The SCH5627P incorporates the following Super I/O components: a parallel port that is compatible with IBM PC/AT

architecture, as well as the IEEE 1284 EPP and ECP; two serial ports that are 16C550A UART compatible; a key-

board/mouse controller that uses an 8042 micro controller; and a floppy disk controller.

The SCH5627P is ACPI 1.0b/2.0 compatible and supports multiple low power-down modes. It incorporates sophisti-

cated power control circuitry (PCC), which includes keyboard and mouse wake-up events.

The SCH5627P incorporates a high-performance embedded microcontroller. The SCH5627P communicates with the

system host using the Intel® Low Pin Count bus.

The SCH5627P is directly powered by two separate suspend supply planes (VBAT and VTR) and senses a third runtime

power plane (VCC) to provide “instant on” and system power management functions. The SCH5627P also contains an

integrated VTR Reset Generator and a system power management interface that supports low-power states and can

drive state changes as a result of hardware wake events as defined by the SCH5627P wake interface.

SCH5627P

DS00001996A-page 6

2009 - 2015 Microchip Technology Inc.

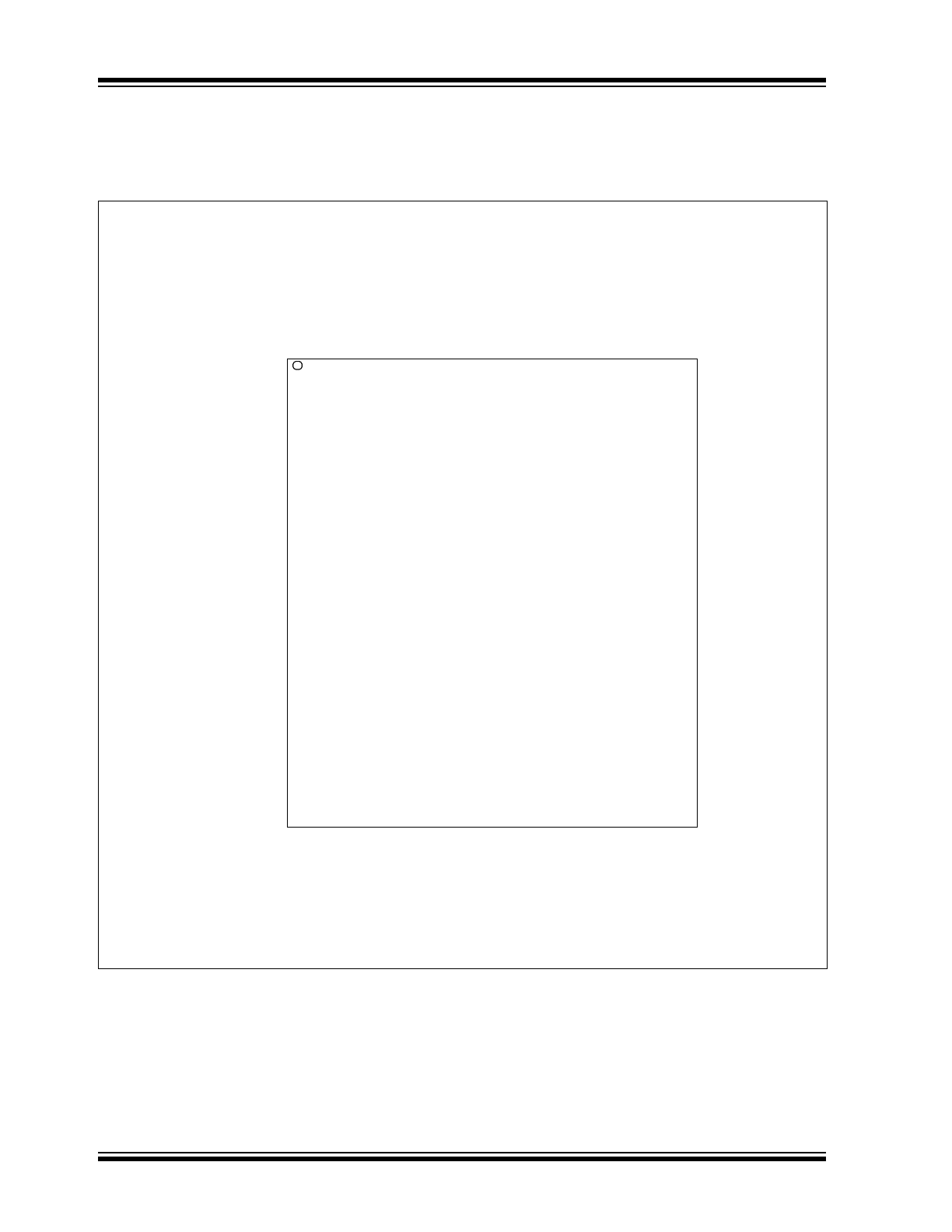

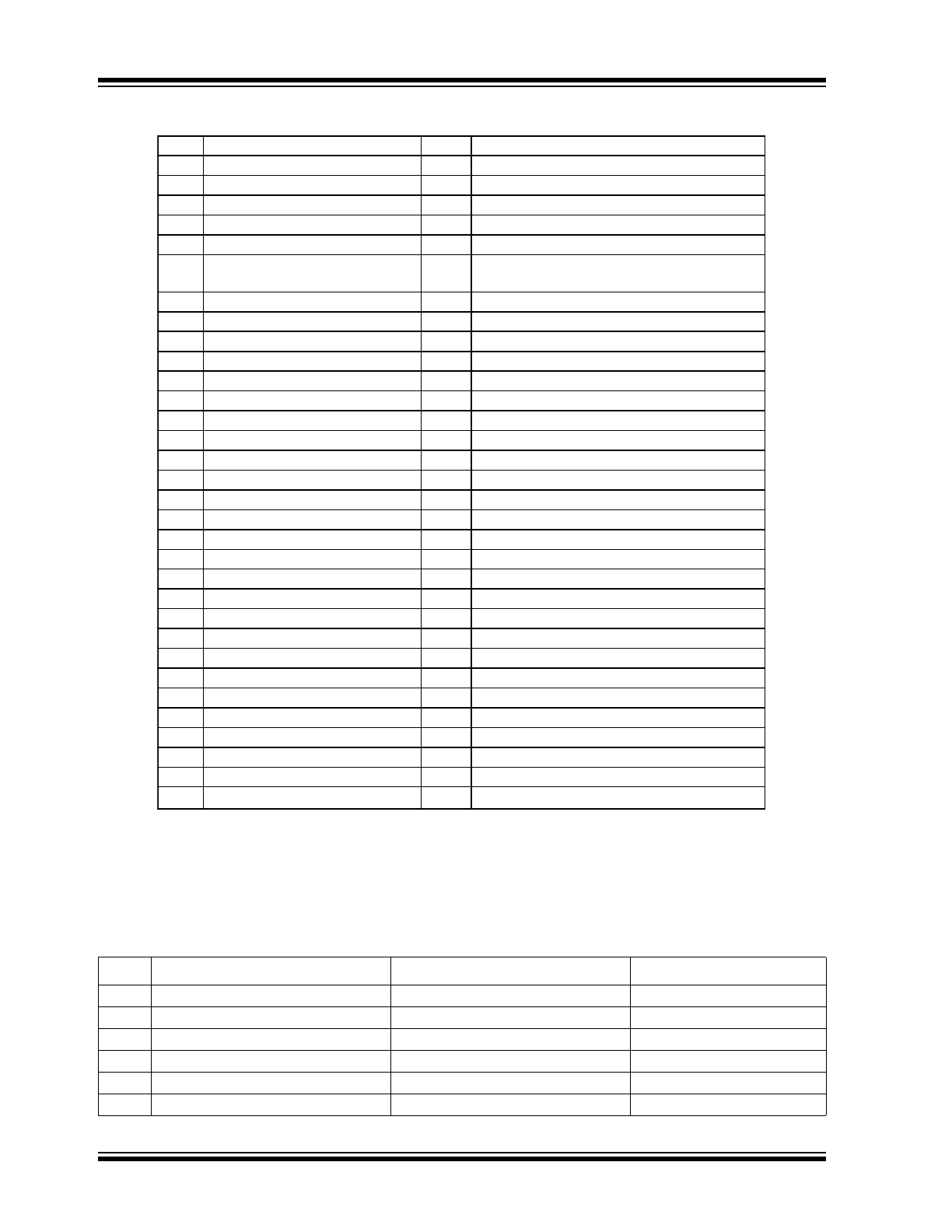

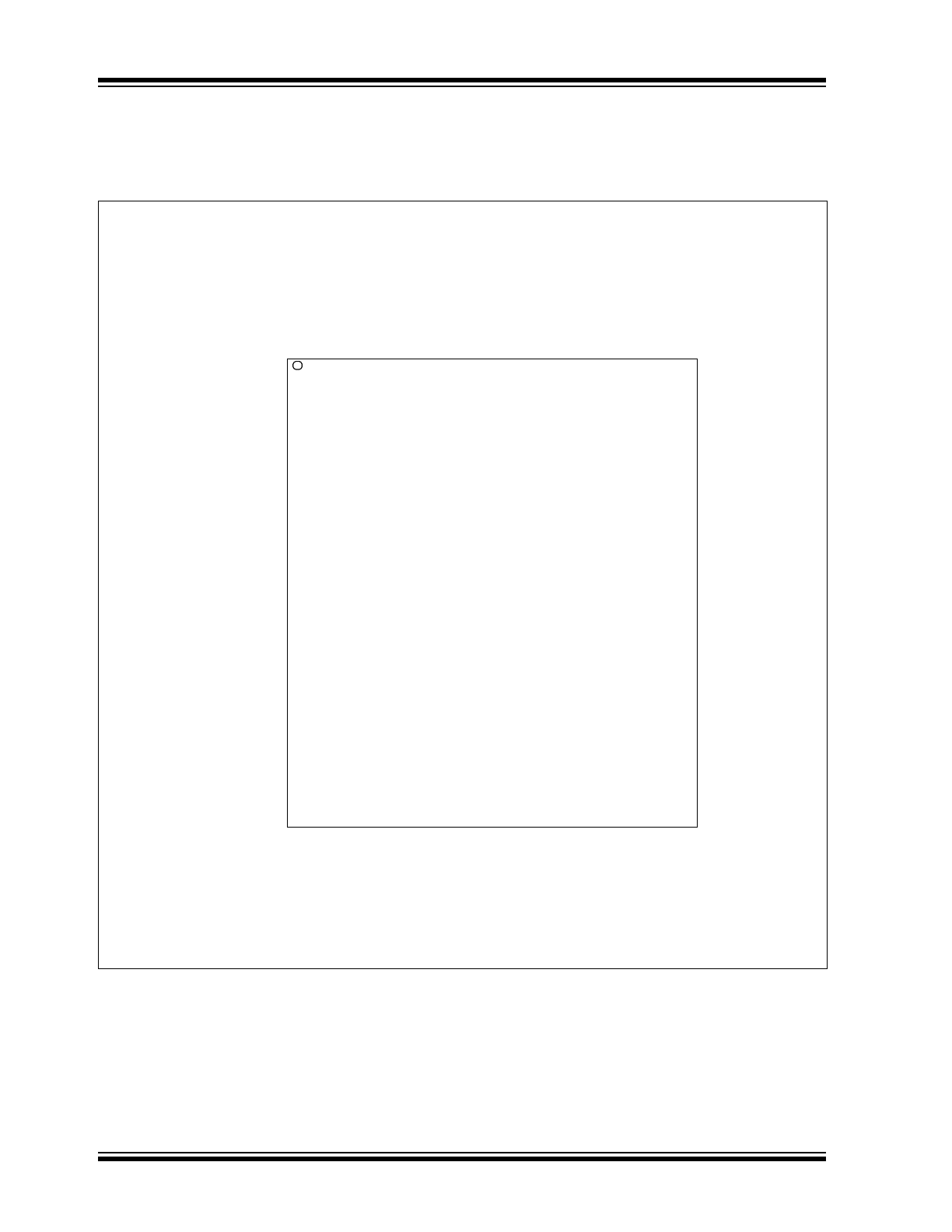

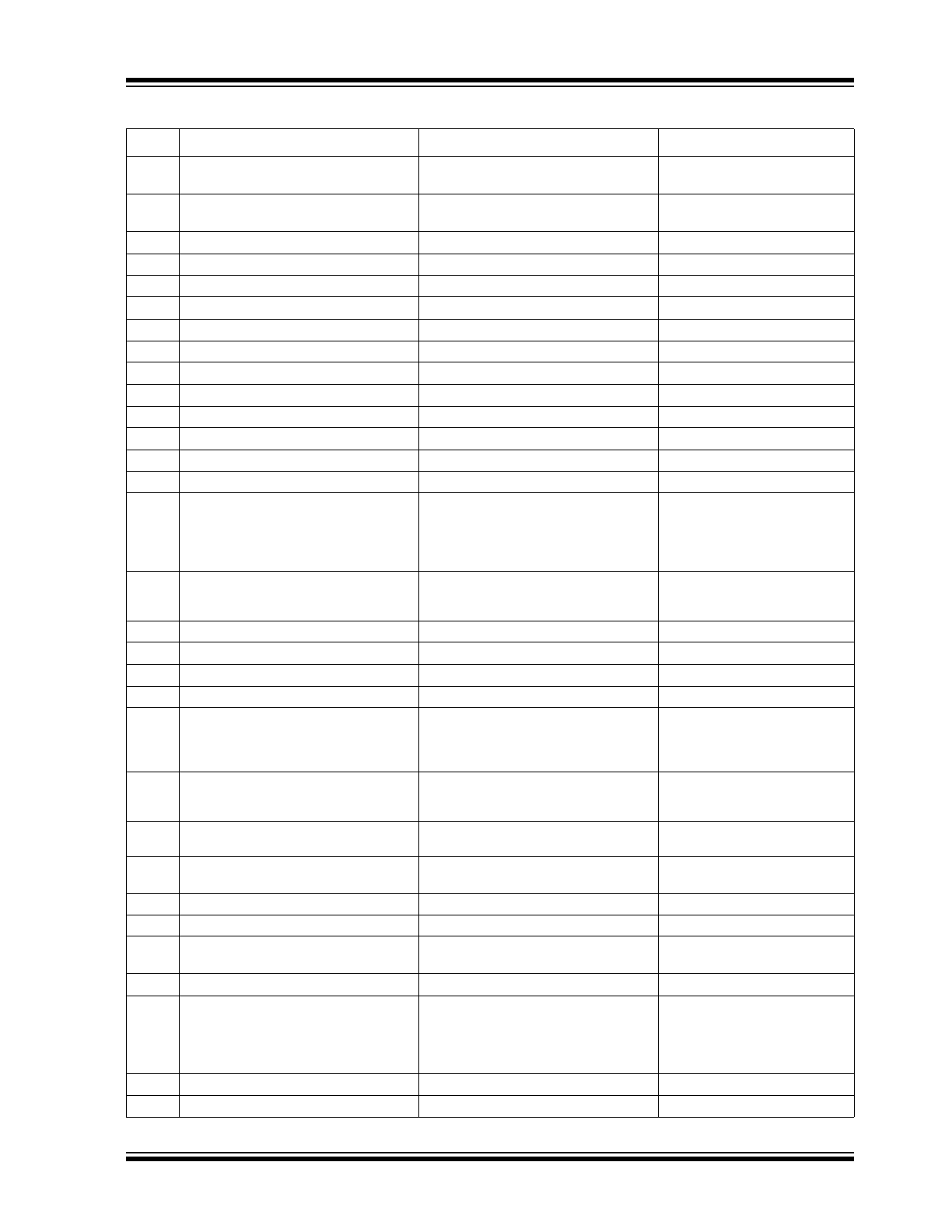

2.0

PIN LAYOUT

FIGURE 2-1:

SCH5627P PIN DIAGRAM

GP071 /

IO

_SM

I#

GP070 /

SP

EA

KE

R

TR

ST

#

PW

RG

D_

PS

/ G

P0

67

SLP

_S4_S

5# /

GP

066

SLP

_S3# /

GP065

VT

R

GP064 /

A20M

GP063 /

KB

D

R

ST

#

VS

S

MDA

T

MCL

K

KD

AT

KC

LK

GP062/

R

I2#

GP061 /

D

TR

2#

GP060 /

C

TS2#

GP057

/ T

XD

2

GP056 /

R

TS2#

GP055 /

R

XD

2

GP054 /

D

SR

2#

GP053 /

D

C

D

2#

VT

R

R

I1# /

GP

052

D

TR

1# [

TES

T_

EN

] /

G

P051

C

TS1# /

GP050

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SER_IRQ - 1

102 - GP047 / TXD1

CAP1 - 2

101 - RTS1# / GP046

VSS - 3

100 - RXD1 / GP045

GP000 / PWM4 - 4

99 - DSR1# / GP044 / MCCLK

GP001 / TACH4 - 5

98 - DCD1# / GP043 / MCDAT

VCC - 6

97 - STROBE#

GP002 / PCIRST_OUT3# - 7

96 - ALF#

GP003 / PCIRST_OUT4# - 8

95 - ERROR#

CLOCKI - 9

94 - INIT#

LAD0 - 10

93 - SLCTIN#

LAD1 - 11

92 - VSS

LAD2 - 12

91 - PD0 / TCK

LAD3 - 13

90 - PD1 / TDI

LFRAME# - 14

89 - PD2 / TDO

LDRQ# - 15

88 - PD3 / TMS

LRESET# / GP074 - 16

87 - PD4

GP004 - 17

86 - PD5

PCICLK - 18

85 - PD6

VSS - 19

84 - PD7

AVSS - 20

83 - ACK#

CLK32 - 21

82 - BUSY

GP005 / PECI_REQUEST# - 22

81 - PE

VBAT - 23

80 - SLCT

VTR - 24

79 - VTR

LED1# / GP006 - 25

78 - GP042 / DRVDEN0

LED2# / GP007 - 26

77 - GP041 / IO_PME#

SMBDAT2 / GP010 - 27

76 - INDEX#

SMBCLK2 / GP011 - 28

75 - MTR0#

GP012 / LAN_WAKE# - 29

74 - GP040 / SMBDAT1

GP013 / VSB_CTRL - 30

73 - DS0#

PECI VREF - 31

72 - GP036 / SMBCLK1

PECI / LVSMBCLK1 / GP072 - 32

71 - DIR#

PECI_READY / LVSMBDAT1 / GP073 - 33

70 - STEP#

VTR - 34

69 - LATCHED_BF_CUT / GP035

GP014 / INTRUSION# - 35

68 - WDATA#

PWRBTN# / GP015 - 36

67 - WGATE#

VSS - 37

66 - TRK0#

PROCHOT_IN# / PROCHOT_OUT# / GP016 - 38

65 -

WRTPRT#

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TA

C

H

1 /

G

P017

TA

C

H

2 /

G

P020

TA

C

H

3 /

G

P021

H

VSS

R

em

ot

e1+

R

em

ot

e1-

R

em

ot

e2A

+/

R

em

ot

e2B-

R

em

ot

e2A

-/R

em

ot

e2B+

HV

TR

V_

IN

GP

022 /

PW

M

1

GP

023 /

PW

M

2

GP

024 /

PW

M

3

GP025 /

PW

R

BT

N

_OU

T#

PC

IR

ST

_OU

T1# /

G

P026

PC

IR

ST

_OU

T2# /

G

P027

PS

_ON

# /

GP03

0

GP

031 /

B

AC

KF

EE

D

_C

U

T#

VT

R

GPO

32

PW

R

_GOOD

_3V

/

GP

033

R

SM

R

ST

# /

GP034

VS

S

DS

KC

H

G

#

HD

SE

L#

RDA

TA

#

12

8

12

7

12

6

12

5

12

0

11

9

11

8

11

7

12

4

12

3

12

2

12

1

11

2

11

1

11

0

10

9

11

6

11

5

11

4

11

3

39

40

41

42

10

4

10

3

10

8

10

7

10

6

10

5

49

50

43

44

45

46

47

48

63

64

57

58

61

62

59

60

55

56

128 Pin QFP

SCH5627P

51

52

53

54

2009 - 2015 Microchip Technology Inc.

DS00001996A-page 7

SCH5627P

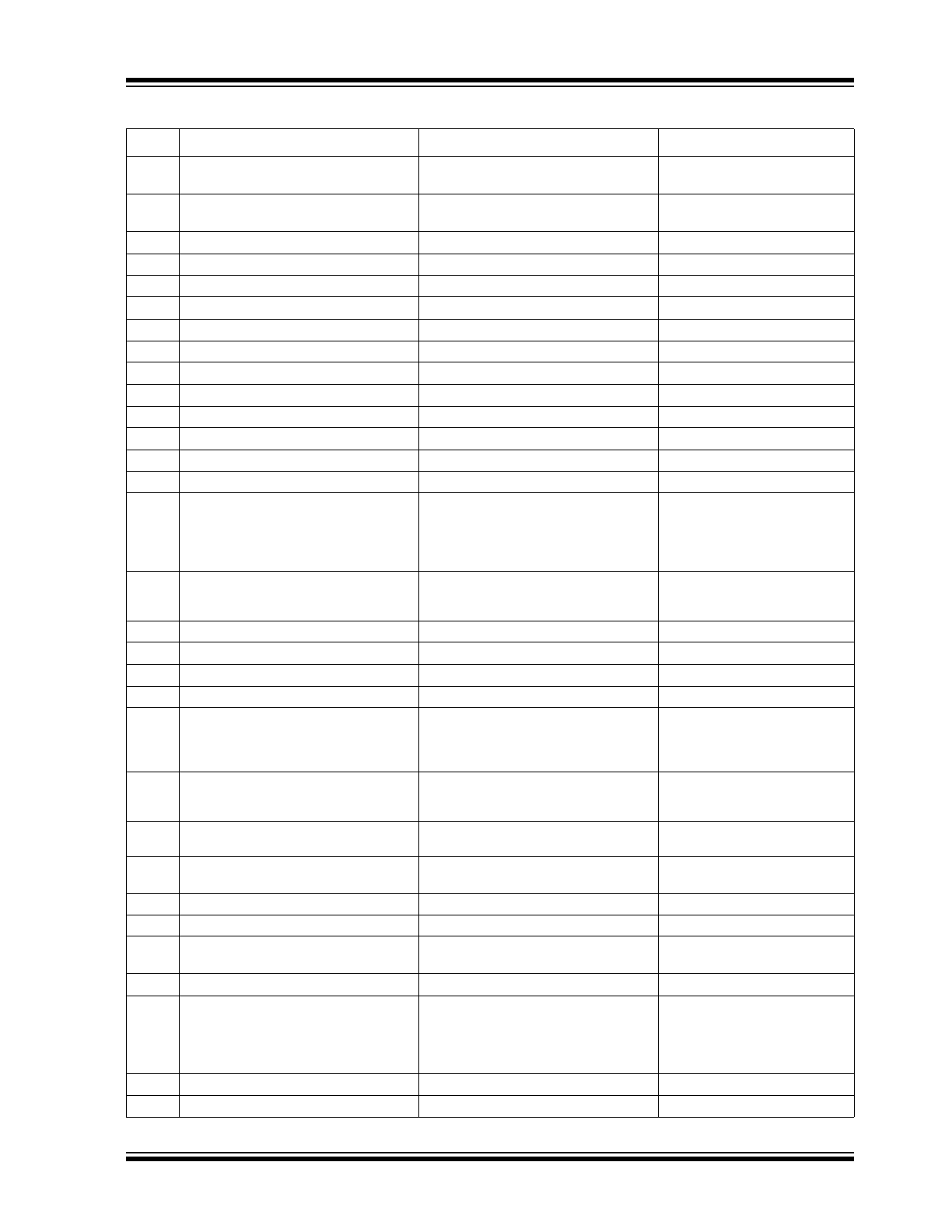

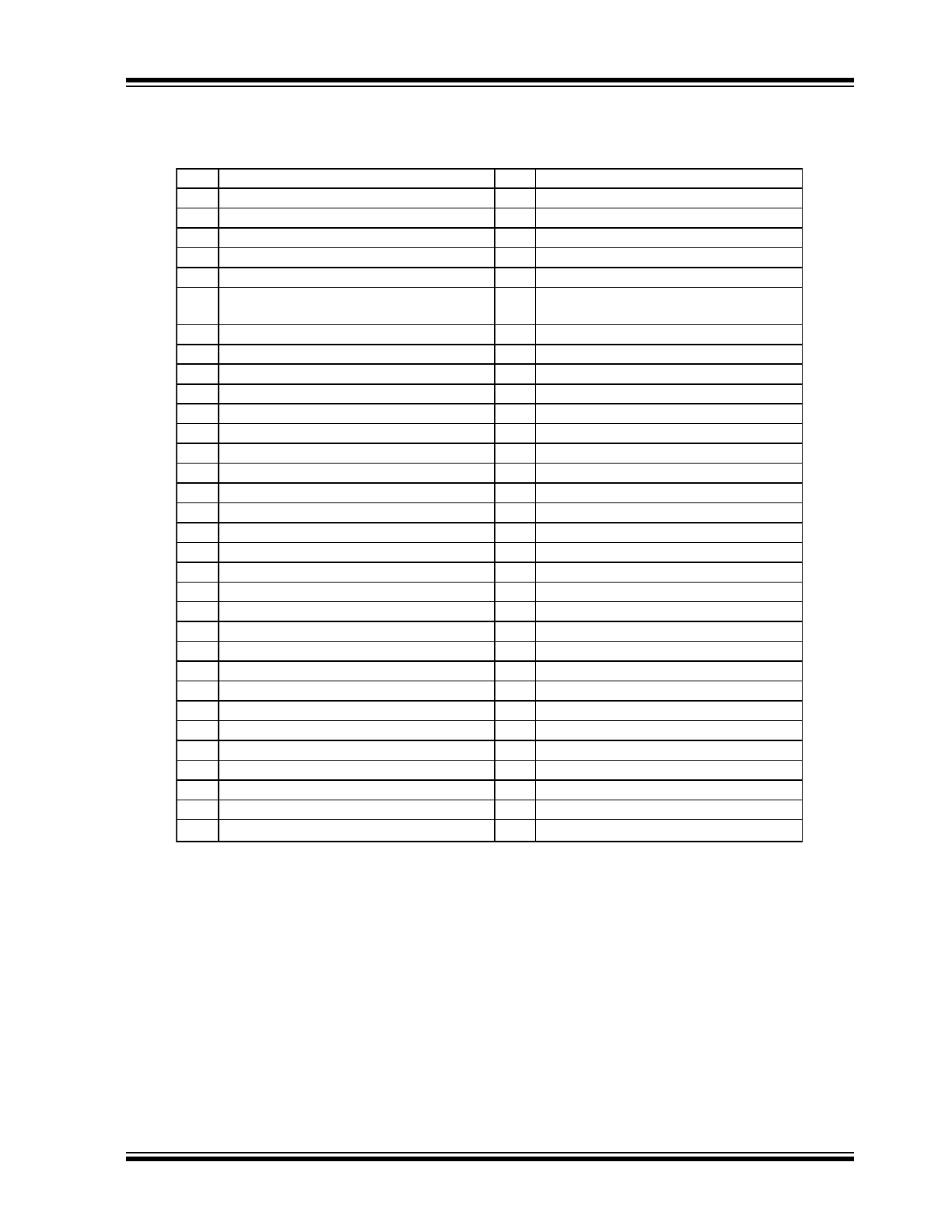

2.1

Pin Table

Pin #

Name

Pin #

Name

1

SER_IRQ

33

PECI_READY / LVSMBDAT1 / GP073

2

CAP1

34

VTR

3

VSS

35

GP014 / INTRUSION#

4

GP000 / PWM4

36

PWRBTN# / GP015

5

GP001 / TACH4

37

VSS

6

VCC

38

PROCHOT_IN# / PROCHOT_OUT# /

GP016

7

GP002 / PCIRST_OUT3#

39

TACH1 / GP017

8

GP003 / PCIRST_OUT4#

40

TACH2 / GP020

9

CLOCKI

41

TACH3 / GP021

10

LAD0

42

HVSS

11

LAD1

43

Remote1+

12

LAD2

44

Remote1-

13

LAD3

45

Remote2A+/Remote2B-

14

LFRAME#

46

Remote2A-/Remote2B+

15

LDRQ#

47

HVTR

16

LRESET# / GP074

48

V_IN

17

GP004

49

GP022 / PWM1

18

PCICLK

50

GP023 / PWM2

19

VSS

51

GP024 / PWM3

20

AVSS

52

GP025 / PWRBTN_OUT#

21

CLK32

53

PCIRST_OUT1# / GP026

22

GP005 / PECI_REQUEST#

54

PCIRST_OUT2# / GP027

23

VBAT

55

PS_ON# / GP030

24

VTR

56

GP031 / BACKFEED_CUT#

25

LED1# / GP006

57

VTR

26

LED2# / GP007

58

GPO32

27

SMBDAT2 / GP010

59

PWR_GOOD_3V / GP033

28

SMBCLK2 / GP011

60

RSMRST# / GP034

29

GP012 / LAN_WAKE#

61

VSS

30

GP013 / VSB_CTRL

62

DSKCHG#

31

PECI VREF

63

HDSEL#

32

PECI / LVSMBCLK1 / GP072

64

RDATA#

SCH5627P

DS00001996A-page 8

2009 - 2015 Microchip Technology Inc.

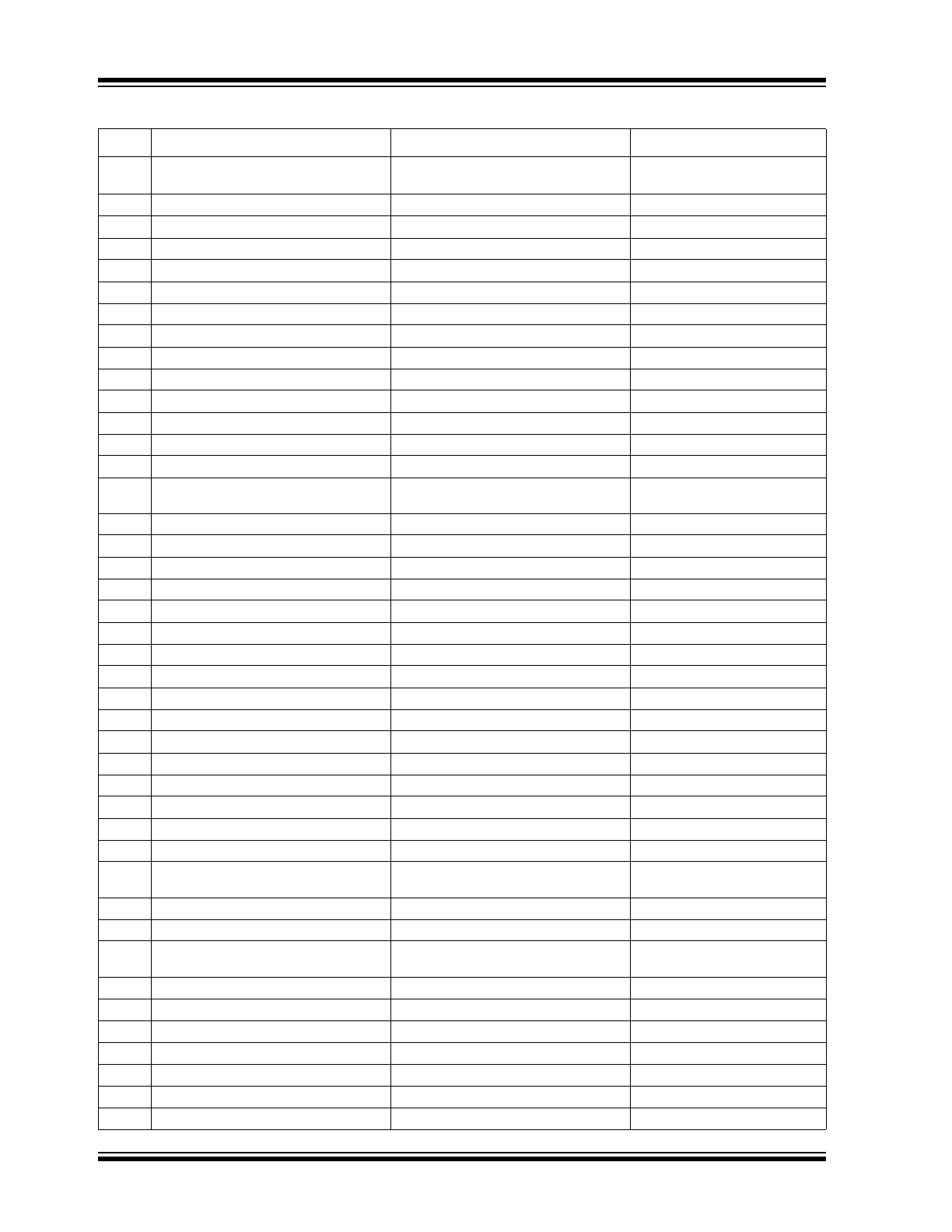

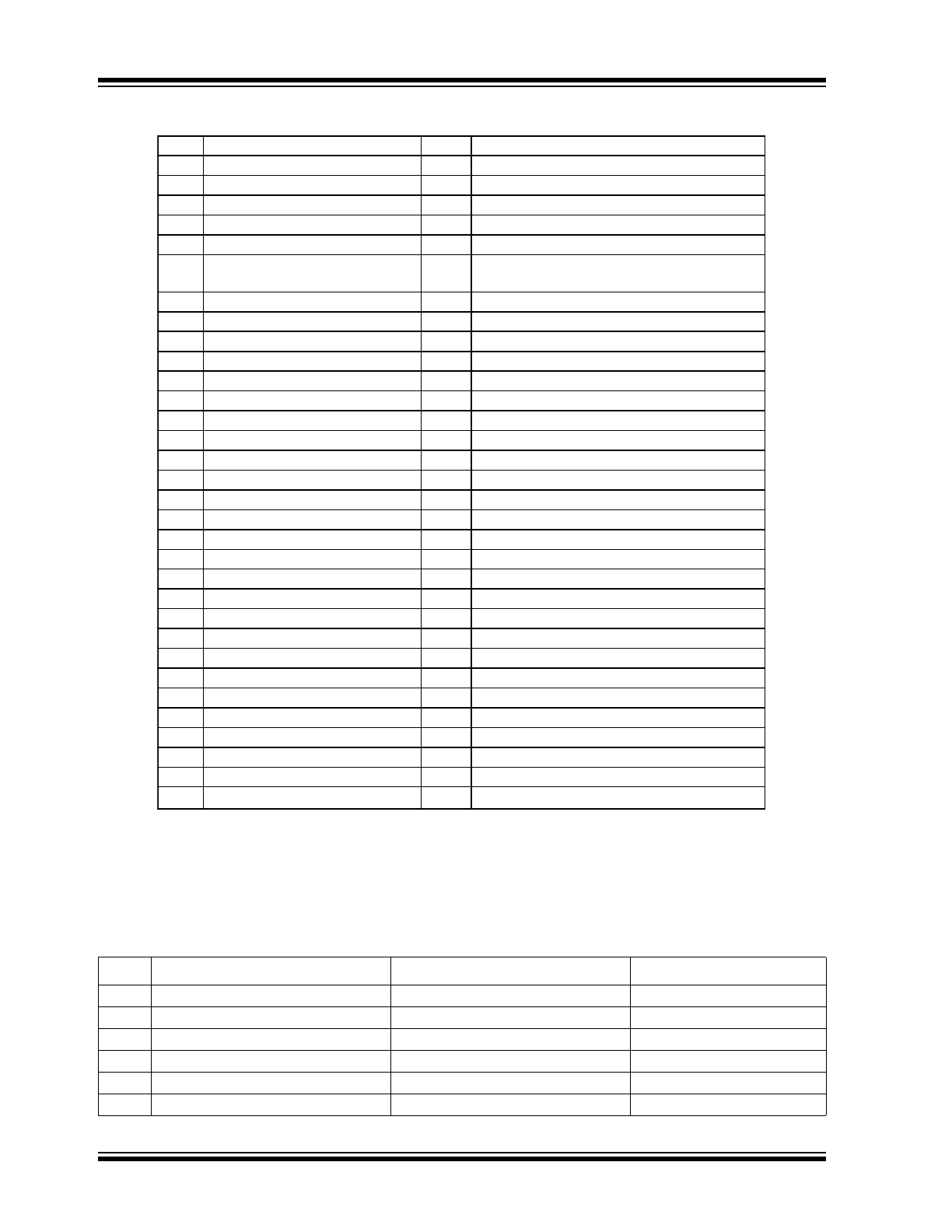

2.2

Changes from SCH5617

The following table lists pinout changes from the SCH5617. Because GPIO names have changed for all GPIOs, GPIO

name changes have not been listed in the DIFFERENCE column. In addition, there is no distinction between Host and

8051 GPIOs; all GPIO pins can be accessed by either the EC directly or by the Host indirectly through the EMI.

TABLE 2-1:

PIN CHANGES FROM THE SCH5617

Pin #

SCH5627P Pin Name

SCH5617 Pin Name

Difference

1

SER_IRQ

SER_IRQ

2

CAP1

CAP1

3

VSS

VSS

4

GP000 / PWM4

GP8051_1 / SMB_DATA_5V

SMB_DATA_5V eliminated

5

GP001) / TACH4

GP8051_3 / SMB_DATA_2P5V

SMB_DATA_2P5V eliminated

6

VCC

VCC

Pin #

Name

Pin #

Name

65

WRTPRT#

97

STROBE#

66

TRK0#

98

DCD1# / GP043 / MCDAT

67

WGATE#

99

DSR1# / GP044 / MCCLK

68

WDATA#

100

RXD1 / GP045

69

LATCHED_BF_CUT / GP035

101

RTS1# / GP046

70

STEP#

102

GP047 / TXD1

71

DIR#

103

CTS1# / GP050

72

GP036 / SMBCLK1

104

DTR1# [TEST_EN] /GP051

73

DS0#

105

RI1# / GP052

74

GP040 / SMBDAT1

106

VTR

75

MTR0#

107

GP053 / DCD2#

76

INDEX#

108

GP054 / DSR2#

77

GP041 / IO_PME#

109

GP055 / RXD2

78

GP042 / DRVDEN0

110

GP056 / RTS2#

79

VTR

111

GP057 / TXD2

80

SLCT

112

GP060 / CTS2#

81

PE

113

GP061 / DTR2#

82

BUSY

114

GP062/ RI2#

83

ACK#

115

KCLK

84

PD7

116

KDAT

85

PD6

117

MCLK

86

PD5

118

MDAT

87

PD4

119

VSS

88

PD3 / TMS

120

GP063 / KBDRST#

89

PD2 / TDO

121

GP064 / A20M

90

PD1 / TDI

122

VTR

91

PD0 / TCK

123

SLP_S3# / GP065

92

VSS

124

SLP_S4_S5# / GP066

93

SLCTIN#

125

PWRGD_PS / GP067

94

INIT#

126

TRST#

95

ERROR#

127

GP070 / SPEAKER

96

ALF#

128

GP071 / IO_SMI#

2009 - 2015 Microchip Technology Inc.

DS00001996A-page 9

SCH5627P

7

GP002 /

PCIRST_OUT3#

GP8051_2 / SMB_CLK_5V

SMB_CLK_5V eliminated

8

GP003 /

PCIRST_OUT4#

GP8051_4 / SMB_CLK_5V

SMB_CLK_2P5V eliminated

9

CLOCKI

CLOCKI

10

LAD0

LAD0

11

LAD1

LAD1

12

LAD2

LAD2

13

LAD3

LAD3

14

LFRAME#

LFRAME#

15

LDRQ#

LDRQ#

16

LRESET# / GP074

LRESET#

17

GP004

LPCPD#

LPCPD# eliminated

18

PCICLK

PCICLK

19

VSS

VSS

20

AVSS

AVSS

21

CLK32

LATCHED_BF_CUT/GP23/

GP8051_18

LATCHED_BF_CUT and

GPIO eliminated

(LATCHED_BF_CUT moved

to pin 69)

32K clock added

22

GP005 /

PECI_REQUEST#

TEST

.TEST eliminated,

PECI_REQUEST and GPIO

added

23

VBAT

VBAT

24

VTR

VTR

25

LED1 / GP006

LED3 / GP60

26

LED2 / GP007

LED2 / GP60

27

SMBDAT2 / GP010

SDAT_1 / GP42/ IO_SMI#

SMB Isolation eliminated,

IO_SMI# eliminated (moved

to pin 128);

SMB Dat added

28

SMBCLK2 / GP011

SDAT/ GP35 / LED1

SMB Isolation eliminated;

SMB Clock added

LED1 eliminated

29

GP012 / LAN_WAKE#

SCLK_1 / GP26

SMB Isolation eliminated,

LAN_WAKE# added

30

GP013 / VSB_CTRL

SCLK / GP25

SMB Isolation eliminated

VSB_CTRL added

31

PECI VREF

PECI VREF

32

PECI / LVSMBCLK1 / GP072

PECI

LVSMBCLK1 added

33

PECI_READY / LVSMBDAT1 /

GP073

PECI READY

LVSMBCLK1 added

34

VTR

VTR

35

GP014 /

INTRUSION

PROCHOT_OUT

PROCHOT_OUT eliminated

(PROCHOT_IN#, pin 38, now

bidirectional);

GPIO added, INTRUSION

added;

36

PWRBTN# / GP015

GP8051_47 / GP33

PWRBTN# added

37

VSS

VSS

TABLE 2-1:

PIN CHANGES FROM THE SCH5617 (CONTINUED)

Pin #

SCH5627P Pin Name

SCH5617 Pin Name

Difference

SCH5627P

DS00001996A-page 10

2009 - 2015 Microchip Technology Inc.

38

PROCHOT_IN# / PROCHOT_OUT#

/ GP016

PROCHOT_I#

PROCHOT function now

bidirectional

39

TACH1 / GP017

TACH1

GPIO added

40

TACH2 / GP020

TACH2

GPIO added

41

TACH3 / GP021

TACH3

GPIO added

42

HVSS

HVSS

43

Remote1+

Remote1+

44

Remote1-

Remote1-

45

Remote2+

Remote2+

46

Remote2-

Remote2-

47

HVTR

HVTR

48

V_IN

VIN1

49

GP022 / PWM1

PWM1

GPIO added

50

GP023 / PWM2

PWM2

GPIO added

51

GP024 / PWM3

PWM3

GPIO added

52

GP025 / PWRBTN_OUT#

IDE_RSTDRV# / GP75

PWRBTN_OUT# added,

IDE_RSTDRV# deleted

53

PCIRST_OUT1# / GP026

PCI_RST_SYS# / GP76

54

PCIRST_OUT2# / GP027

PCI_RST_SLOTS# / GP77

55

PS_ON#/ / GP030

PS_ON# / GP80

56

GP031 / BACKFEED_CUT#

BACKFEED_CUT# / GP81

57

VTR

VTR

58

GPO32

GP82

59

PWR_GOOD_3V / GP033

PWR_GOOD_3V / GP83

60

RSMRST# / GP034

RSMRST# / GP84

61

VSS

VSS

62

DSKCHG#

DSKCHG#

63

HDSEL#

HDSEL#

64

RDATA#

RDATA#

65

WRTPRT#

WRTPRT#

66

TRK0#

TRK0#

67

WGATE#

WGATE#

68

WDATA#

WDATA#

69

LATCHED_BF_CUT / GP035

CAP2

CAP2 eliminated

70

STEP#

STEP#

71

DIR#

DIR#

72

GP036 / SMBCLK1

GP22 / P12 / MRT1# / SCSI#

P12 / MTR1# / SCSI#

eliminated

73

DS0#

DS0#

74

GP040 / SMBDAT1

GP21/ P16 / DS1#

P16 / DS1# eliminated

75

MTR0#

MTR0#

76

INDEX#

INDEX#

77

GP041 / IO_PME#

GP41 / IO_PME#

78

GP042 / DRVDEN0

GP40 / DRVDEN0

79

VTR

VTR

TABLE 2-1:

PIN CHANGES FROM THE SCH5617 (CONTINUED)

Pin #

SCH5627P Pin Name

SCH5617 Pin Name

Difference

2009 - 2015 Microchip Technology Inc.

DS00001996A-page 1

Highlights

• High Performance Embedded Controller (EC)

• ACPI 2.0 Compliant

• PC2001 Compliant

• LPC Interface

- Supports LPC Bus frequencies of 19MHz to

33MHz

- Multiplexed Command, Address and Data

Bus

- Serial IRQ Interface Compatible with Serial-

ized IRQ Support for PCI Systems

- PME Interface

• 3.3-Volt I/O

• 128-pin QFP RoHS Compliant Package

• System Watch Dog Timer (WDT)

• Battery Backed Resources

- Power-Fail Status Register

- VBat backed 64 byte memory

• Extreme Low S5

- Enables power saving by shutting down

standby voltage regulators in system S5 state

- System wake from power button press

- System wake from LAN

• Two EC-based SMBus 2.0 Host Controllers

- Allows Master or Dual Slave Operation

- Controllers are Fully Operational on Standby

Power

- DMA-driven I

2

C Network Layer

- I

2

C Datalink Compatibility Mode

- Multi-Master Capable

- Supports Clock Stretching

- Programmable Bus Speeds

- 400 KHz Capable

- Hardware Bus Access “Fairness” Interface

- Detects SMBus Time-outs

- One controller can be multiplexed onto a low

voltage SMBus

• PECI Interface 2.0

- Supports PECI REQUEST# and PECI

READY signaling

- Supports up to 2 CPUs and 4 domains

• Temperature reading from PCH over SMBus

• Temperature reading from AMD-TSI over SMBus

• Temperature Monitor

- Monitoring up to 2 Remote Thermal Diodes

plus an Anti-Parallel Remote Thermal Diode

- Built-in ADC supports temperature readings

from -63 degrees Celsius to +192 degrees

Celsius

–Supports monitoring of discrete diodes (3904 type

diodes)

–Supports monitoring substrate diodes (45nm &

65nm processor diodes)

- Temperature resolution is 0.125 degrees Cel-

sius

- Internal Ambient Temperature Measurement

- Out-of-limit Temperature Event reporting

• Bi-directional PROCHOT# Pin

- Interrupt generation for PROCHOT Assert

events

- May be used by AMTA and PTTA features to

adjust fan control limits

- May be configured to force fans on full

- Supports PROCHOT Assertions to external

CPU

- Supports PROCHOT Throttle Events to

external CPU

- Supports Interrupt Event to Host

• Voltage Monitor

- Monitoring VBAT, VTR,VCC and Vtt power

supplies

- Monitoring of one external voltage

- Limit comparison on monitored values

• PWM (Pulse width Modulation) Outputs (4)

- Multiple Clock Rates

- 16-bit ON and 16-bit OFF Counters

• Fan tachometer Inputs (4)

- Programmable to monitor standard tachome-

ter outputs or locked rotor alarm outputs

- Generate tachometer event when speed of

fan drops below programmed limit

• Internal clock sources

- A Ring Oscillator generates 64 MHz clock

- SIO clocks derived from a 96MHz PLL syn-

chronized to a 14.318MHz clock input

- Main ring generates 32kHz standby clock

when external 32.768KHz clock source is off

• Low Battery Warning

SCH5627P

Desktop Embedded Controller with Fan Control,

Hardware Monitoring and PECI

SCH5627P

DS00001996A-page 2

2009 - 2015 Microchip Technology Inc.

• LED Control

- Two LEDs to indicate system state

• Programmable Wake-up Event Interface

• General Purpose Input/Output Pins (60 total)

• System Management Interrupt (SMI)

• GLUE Logic

- 4 Buffered PCI Reset Outputs

- Power OK Signal Generation

- Power Sequencing

- Power Supply Turn On Circuitry

- Resume Reset Signal Generation

- Speaker output

- Intrusion Detection

• 2.88MB Super I/O Floppy Disk Controller

- Licensed CMOS 765B Floppy Disk Controller

- Software and Register Compatible with

Microchip's Proprietary 82077AA Compatible

Core

- Configurable Open Drain/Push-Pull Output

Drivers

- Supports Vertical Recording Format

- 16-Byte Data FIFO

- 100% IBM® Compatibility

- Detects All Overrun and Underrun Conditions

- Sophisticated Power Control Circuitry (PCC)

Including Multiple Powerdown Modes for

Reduced Power Consumption

- DMA Enable Logic

- Data Rate and Drive Control Registers

- 480 Address, Up to Eight IRQ and Four DMA

Options

• Enhanced Digital Data Separator

- 1 Mbps, 500 Kbps, 300 Kbps, 250 Kbps Data

Rates

- Programmable Precompensation Modes

• Keyboard Controller

- 8042 Software Compatible

- 8 Bit Microcomputer

- 2k Bytes of Program ROM

- 256 Bytes of Data RAM

- Four Open Drain Outputs Dedicated for Key-

board/Mouse Interface

- Asynchronous Access to Two Data Registers

and One Status Register

- Supports Interrupt and Polling Access

- 8 Bit Counter Timer

- Port 92 Support

- Fast Gate A20 and KRESET Outputs

• Serial Ports

- Two Full Function Serial Ports

- High Speed NS16C550A Compatible UARTs

with Send/Receive 16-Byte FIFOs

- Programmable Baud Rate Generator

- Modem Control Circuitry

- Any LPC Address Configurable. 15 IRQ

Options

• Multi-Mode™ Parallel Port with ChiProtect™

- Standard Mode IBM PC/XT

®,

PC/AT

®

, and

PS/2™ Compatible Bi-directional Parallel

Port

- Enhanced Parallel Port (EPP) Compatible -

EPP 1.7 and EPP 1.9 (IEEE 1284 Compliant)

- IEEE 1284 Compliant Enhanced Capabilities

Port (ECP)

- ChiProtect Circuitry for Protection

- 960 Addresses, Up to 15 IRQ and Four DMA

Options

2009 - 2015 Microchip Technology Inc.

DS00001996A-page 3

SCH5627P

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at

docerrors@microchip.com

. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for cur-

rent devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the

revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site;

http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are

using.

Customer Notification System

Register on our web site at

www.microchip.com

to receive the most current information on all of our products.

SCH5627P

DS00001996A-page 4

2009 - 2015 Microchip Technology Inc.

Table of Contents

1.0 Introduction ..................................................................................................................................................................................... 5

2.0 Pin Layout ...................................................................................................................................................................................... 6

3.0 Signal Descriptions ....................................................................................................................................................................... 13

4.0 Block Diagram ............................................................................................................................................................................... 25

5.0 Power, Clocks and Reset .............................................................................................................................................................. 27

6.0 Host Interface ................................................................................................................................................................................ 30

7.0 Logical Device Configuration ........................................................................................................................................................ 38

8.0 Keyboard Controller ...................................................................................................................................................................... 53

9.0 Serial Port (UART) ........................................................................................................................................................................ 64

10.0 Parallel Port ................................................................................................................................................................................. 82

11.0 Floppy Disk Controller ................................................................................................................................................................. 98

12.0 Embedded Memory Interface .................................................................................................................................................... 135

13.0 PME Support ............................................................................................................................................................................. 144

14.0 SMI Support .............................................................................................................................................................................. 146

15.0 Low Battery Detection ............................................................................................................................................................... 147

16.0 Runtime Registers ..................................................................................................................................................................... 149

17.0 Intruder Detection Support ........................................................................................................................................................ 169

18.0 Glue Logic Hardware ................................................................................................................................................................ 171

19.0 GPIO Interface .......................................................................................................................................................................... 182

20.0 JTAG and XNOR ....................................................................................................................................................................... 191

21.0 Electrical Specifications ............................................................................................................................................................ 202

22.0 Timing Diagrams ....................................................................................................................................................................... 208

23.0 Package Outline ........................................................................................................................................................................ 229

Appendix A: Data Sheet Revision History ......................................................................................................................................... 230

The Microchip Web Site .................................................................................................................................................................... 231

Customer Change Notification Service ............................................................................................................................................. 231

Customer Support ............................................................................................................................................................................. 231

Product Identification System ............................................................................................................................................................ 232

2009 - 2015 Microchip Technology Inc.

DS00001996A-page 5

SCH5627P

1.0

INTRODUCTION

The SCH5627P is a 3.3V PC 2001 compliant Super I/O controller with an LPC interface. All legacy drivers used for

Super I/O components are supported making this interface transparent to the supporting software. The LPC bus also

supports power management, such as wake-up and sleep modes.

The SCH5627P provides temperature monitoring with auto fan control. The temperature monitor is capable of monitor-

ing up to three external diodes, one internal ambient temperature sensor or retrieving temperatures from external pro-

cessors that implement the PECI Interface. This device offers programmable automatic fan control support based on

one or more of these measured temperatures. There are four pulse width modulation (PWM) outputs with

high fre-

quency support as well as four fan tachometer inputs. In addition, there is support for a bi-directional PROCHOT# pin

that may be used to generate an interrupt, adjust the programmed temperature limits in the auto fan control logic, or

force the PWM outputs on full. The RRCC feature provides a linear relationship of temperature to fan speed.

The Glue Logic includes various power management logic; including generation of RSMRST# and Power OK signal

generation. There are also two LEDs to indicate power status. The part also provides a low battery warning circuit.

The SCH5627P provides 60 General Purpose I/O control pins, which offer flexibility to the system designer.

The SCH5627P incorporates the following Super I/O components: a parallel port that is compatible with IBM PC/AT

architecture, as well as the IEEE 1284 EPP and ECP; two serial ports that are 16C550A UART compatible; a key-

board/mouse controller that uses an 8042 micro controller; and a floppy disk controller.

The SCH5627P is ACPI 1.0b/2.0 compatible and supports multiple low power-down modes. It incorporates sophisti-

cated power control circuitry (PCC), which includes keyboard and mouse wake-up events.

The SCH5627P incorporates a high-performance embedded microcontroller. The SCH5627P communicates with the

system host using the Intel® Low Pin Count bus.

The SCH5627P is directly powered by two separate suspend supply planes (VBAT and VTR) and senses a third runtime

power plane (VCC) to provide “instant on” and system power management functions. The SCH5627P also contains an

integrated VTR Reset Generator and a system power management interface that supports low-power states and can

drive state changes as a result of hardware wake events as defined by the SCH5627P wake interface.

SCH5627P

DS00001996A-page 6

2009 - 2015 Microchip Technology Inc.

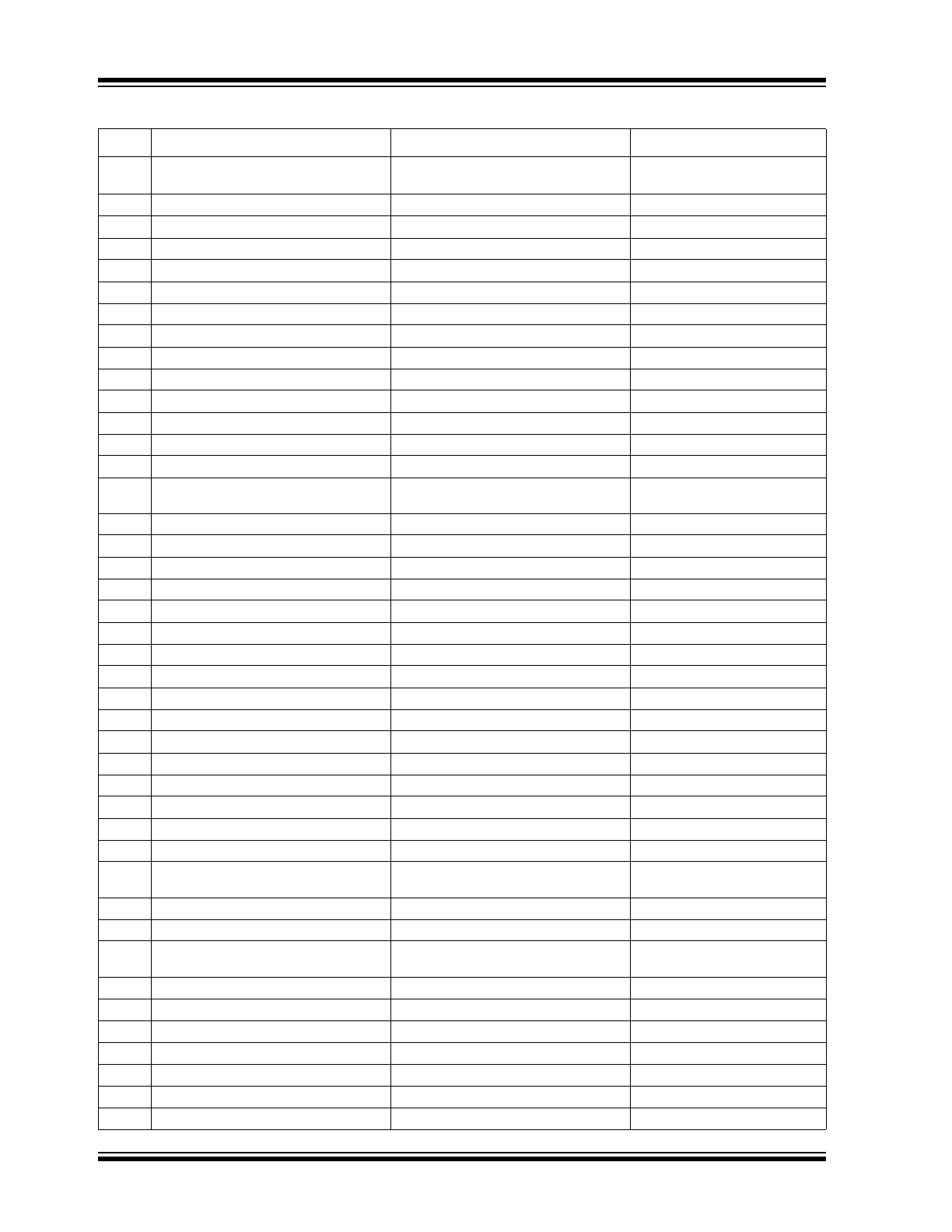

2.0

PIN LAYOUT

FIGURE 2-1:

SCH5627P PIN DIAGRAM

GP071 /

IO

_SM

I#

GP070 /

SP

EA

KE

R

TR

ST

#

PW

RG

D_

PS

/ G

P0

67

SLP

_S4_S

5# /

GP

066

SLP

_S3# /

GP065

VT

R

GP064 /

A20M

GP063 /

KB

D

R

ST

#

VS

S

MDA

T

MCL

K

KD

AT

KC

LK

GP062/

R

I2#

GP061 /

D

TR

2#

GP060 /

C

TS2#

GP057

/ T

XD

2

GP056 /

R

TS2#

GP055 /

R

XD

2

GP054 /

D

SR

2#

GP053 /

D

C

D

2#

VT

R

R

I1# /

GP

052

D

TR

1# [

TES

T_

EN

] /

G

P051

C

TS1# /

GP050

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SER_IRQ - 1

102 - GP047 / TXD1

CAP1 - 2

101 - RTS1# / GP046

VSS - 3

100 - RXD1 / GP045

GP000 / PWM4 - 4

99 - DSR1# / GP044 / MCCLK

GP001 / TACH4 - 5

98 - DCD1# / GP043 / MCDAT

VCC - 6

97 - STROBE#

GP002 / PCIRST_OUT3# - 7

96 - ALF#

GP003 / PCIRST_OUT4# - 8

95 - ERROR#

CLOCKI - 9

94 - INIT#

LAD0 - 10

93 - SLCTIN#

LAD1 - 11

92 - VSS

LAD2 - 12

91 - PD0 / TCK

LAD3 - 13

90 - PD1 / TDI

LFRAME# - 14

89 - PD2 / TDO

LDRQ# - 15

88 - PD3 / TMS

LRESET# / GP074 - 16

87 - PD4

GP004 - 17

86 - PD5

PCICLK - 18

85 - PD6

VSS - 19

84 - PD7

AVSS - 20

83 - ACK#

CLK32 - 21

82 - BUSY

GP005 / PECI_REQUEST# - 22

81 - PE

VBAT - 23

80 - SLCT

VTR - 24

79 - VTR

LED1# / GP006 - 25

78 - GP042 / DRVDEN0

LED2# / GP007 - 26

77 - GP041 / IO_PME#

SMBDAT2 / GP010 - 27

76 - INDEX#

SMBCLK2 / GP011 - 28

75 - MTR0#

GP012 / LAN_WAKE# - 29

74 - GP040 / SMBDAT1

GP013 / VSB_CTRL - 30

73 - DS0#

PECI VREF - 31

72 - GP036 / SMBCLK1

PECI / LVSMBCLK1 / GP072 - 32

71 - DIR#

PECI_READY / LVSMBDAT1 / GP073 - 33

70 - STEP#

VTR - 34

69 - LATCHED_BF_CUT / GP035

GP014 / INTRUSION# - 35

68 - WDATA#

PWRBTN# / GP015 - 36

67 - WGATE#

VSS - 37

66 - TRK0#

PROCHOT_IN# / PROCHOT_OUT# / GP016 - 38

65 -

WRTPRT#

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TA

C

H

1 /

G

P017

TA

C

H

2 /

G

P020

TA

C

H

3 /

G

P021

H

VSS

R

em

ot

e1+

R

em

ot

e1-

R

em

ot

e2A

+/

R

em

ot

e2B-

R

em

ot

e2A

-/R

em

ot

e2B+

HV

TR

V_

IN

GP

022 /

PW

M

1

GP

023 /

PW

M

2

GP

024 /

PW

M

3

GP025 /

PW

R

BT

N

_OU

T#

PC

IR

ST

_OU

T1# /

G

P026

PC

IR

ST

_OU

T2# /

G

P027

PS

_ON

# /

GP03

0

GP

031 /

B

AC

KF

EE

D

_C

U

T#

VT

R

GPO

32

PW

R

_GOOD

_3V

/

GP

033

R

SM

R

ST

# /

GP034

VS

S

DS

KC

H

G

#

HD

SE

L#

RDA

TA

#

12

8

12

7

12

6

12

5

12

0

11

9

11

8

11

7

12

4

12

3

12

2

12

1

11

2

11

1

11

0

10

9

11

6

11

5

11

4

11

3

39

40

41

42

10

4

10

3

10

8

10

7

10

6

10

5

49

50

43

44

45

46

47

48

63

64

57

58

61

62

59

60

55

56

128 Pin QFP

SCH5627P

51

52

53

54

2009 - 2015 Microchip Technology Inc.

DS00001996A-page 7

SCH5627P

2.1

Pin Table

Pin #

Name

Pin #

Name

1

SER_IRQ

33

PECI_READY / LVSMBDAT1 / GP073

2

CAP1

34

VTR

3

VSS

35

GP014 / INTRUSION#

4

GP000 / PWM4

36

PWRBTN# / GP015

5

GP001 / TACH4

37

VSS

6

VCC

38

PROCHOT_IN# / PROCHOT_OUT# /

GP016

7

GP002 / PCIRST_OUT3#

39

TACH1 / GP017

8

GP003 / PCIRST_OUT4#

40

TACH2 / GP020

9

CLOCKI

41

TACH3 / GP021

10

LAD0

42

HVSS

11

LAD1

43

Remote1+

12

LAD2

44

Remote1-

13

LAD3

45

Remote2A+/Remote2B-

14

LFRAME#

46

Remote2A-/Remote2B+

15

LDRQ#

47

HVTR

16

LRESET# / GP074

48

V_IN

17

GP004

49

GP022 / PWM1

18

PCICLK

50

GP023 / PWM2

19

VSS

51

GP024 / PWM3

20

AVSS

52

GP025 / PWRBTN_OUT#

21

CLK32

53

PCIRST_OUT1# / GP026

22

GP005 / PECI_REQUEST#

54

PCIRST_OUT2# / GP027

23

VBAT

55

PS_ON# / GP030

24

VTR

56

GP031 / BACKFEED_CUT#

25

LED1# / GP006

57

VTR

26

LED2# / GP007

58

GPO32

27

SMBDAT2 / GP010

59

PWR_GOOD_3V / GP033

28

SMBCLK2 / GP011

60

RSMRST# / GP034

29

GP012 / LAN_WAKE#

61

VSS

30

GP013 / VSB_CTRL

62

DSKCHG#

31

PECI VREF

63

HDSEL#

32

PECI / LVSMBCLK1 / GP072

64

RDATA#

SCH5627P

DS00001996A-page 8

2009 - 2015 Microchip Technology Inc.

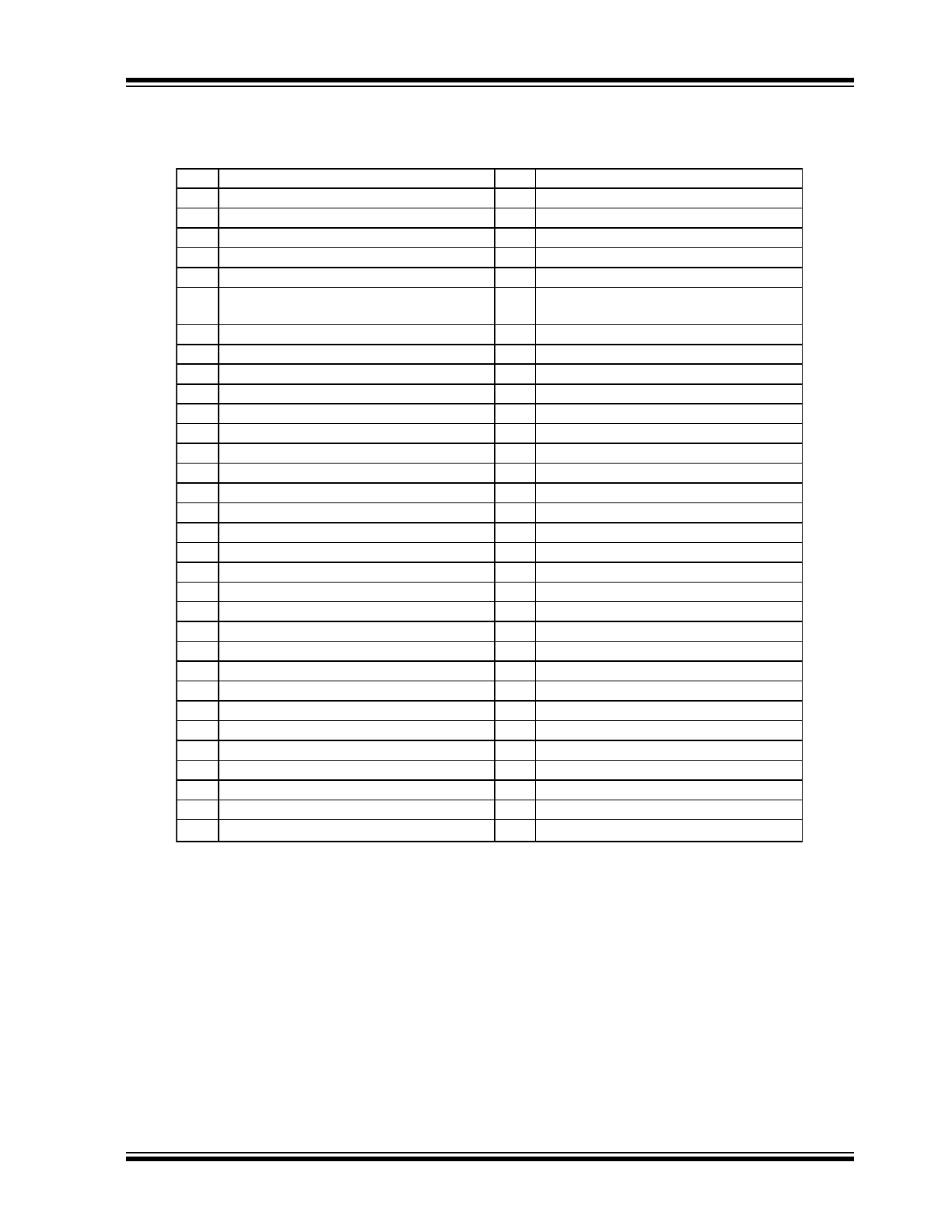

2.2

Changes from SCH5617

The following table lists pinout changes from the SCH5617. Because GPIO names have changed for all GPIOs, GPIO

name changes have not been listed in the DIFFERENCE column. In addition, there is no distinction between Host and

8051 GPIOs; all GPIO pins can be accessed by either the EC directly or by the Host indirectly through the EMI.

TABLE 2-1:

PIN CHANGES FROM THE SCH5617

Pin #

SCH5627P Pin Name

SCH5617 Pin Name

Difference

1

SER_IRQ

SER_IRQ

2

CAP1

CAP1

3

VSS

VSS

4

GP000 / PWM4

GP8051_1 / SMB_DATA_5V

SMB_DATA_5V eliminated

5

GP001) / TACH4

GP8051_3 / SMB_DATA_2P5V

SMB_DATA_2P5V eliminated

6

VCC

VCC

Pin #

Name

Pin #

Name

65

WRTPRT#

97

STROBE#

66

TRK0#

98

DCD1# / GP043 / MCDAT

67

WGATE#

99

DSR1# / GP044 / MCCLK

68

WDATA#

100

RXD1 / GP045

69

LATCHED_BF_CUT / GP035

101

RTS1# / GP046

70

STEP#

102

GP047 / TXD1

71

DIR#

103

CTS1# / GP050

72

GP036 / SMBCLK1

104

DTR1# [TEST_EN] /GP051

73

DS0#

105

RI1# / GP052

74

GP040 / SMBDAT1

106

VTR

75

MTR0#

107

GP053 / DCD2#

76

INDEX#

108

GP054 / DSR2#

77

GP041 / IO_PME#

109

GP055 / RXD2

78

GP042 / DRVDEN0

110

GP056 / RTS2#

79

VTR

111

GP057 / TXD2

80

SLCT

112

GP060 / CTS2#

81

PE

113

GP061 / DTR2#

82

BUSY

114

GP062/ RI2#

83

ACK#

115

KCLK

84

PD7

116

KDAT

85

PD6

117

MCLK

86

PD5

118

MDAT

87

PD4

119

VSS

88

PD3 / TMS

120

GP063 / KBDRST#

89

PD2 / TDO

121

GP064 / A20M

90

PD1 / TDI

122

VTR

91

PD0 / TCK

123

SLP_S3# / GP065

92

VSS

124

SLP_S4_S5# / GP066

93

SLCTIN#

125

PWRGD_PS / GP067

94

INIT#

126

TRST#

95

ERROR#

127

GP070 / SPEAKER

96

ALF#

128

GP071 / IO_SMI#

2009 - 2015 Microchip Technology Inc.

DS00001996A-page 9

SCH5627P

7

GP002 /

PCIRST_OUT3#

GP8051_2 / SMB_CLK_5V

SMB_CLK_5V eliminated

8

GP003 /

PCIRST_OUT4#

GP8051_4 / SMB_CLK_5V

SMB_CLK_2P5V eliminated

9

CLOCKI

CLOCKI

10

LAD0

LAD0

11

LAD1

LAD1

12

LAD2

LAD2

13

LAD3

LAD3

14

LFRAME#

LFRAME#

15

LDRQ#

LDRQ#

16

LRESET# / GP074

LRESET#

17

GP004

LPCPD#

LPCPD# eliminated

18

PCICLK

PCICLK

19

VSS

VSS

20

AVSS

AVSS

21

CLK32

LATCHED_BF_CUT/GP23/

GP8051_18

LATCHED_BF_CUT and

GPIO eliminated

(LATCHED_BF_CUT moved

to pin 69)

32K clock added

22

GP005 /

PECI_REQUEST#

TEST

.TEST eliminated,

PECI_REQUEST and GPIO

added

23

VBAT

VBAT

24

VTR

VTR

25

LED1 / GP006

LED3 / GP60

26

LED2 / GP007

LED2 / GP60

27

SMBDAT2 / GP010

SDAT_1 / GP42/ IO_SMI#

SMB Isolation eliminated,

IO_SMI# eliminated (moved

to pin 128);

SMB Dat added

28

SMBCLK2 / GP011

SDAT/ GP35 / LED1

SMB Isolation eliminated;

SMB Clock added

LED1 eliminated

29

GP012 / LAN_WAKE#

SCLK_1 / GP26

SMB Isolation eliminated,

LAN_WAKE# added

30

GP013 / VSB_CTRL

SCLK / GP25

SMB Isolation eliminated

VSB_CTRL added

31

PECI VREF

PECI VREF

32

PECI / LVSMBCLK1 / GP072

PECI

LVSMBCLK1 added

33

PECI_READY / LVSMBDAT1 /

GP073

PECI READY

LVSMBCLK1 added

34

VTR

VTR

35

GP014 /

INTRUSION

PROCHOT_OUT

PROCHOT_OUT eliminated

(PROCHOT_IN#, pin 38, now

bidirectional);

GPIO added, INTRUSION

added;

36

PWRBTN# / GP015

GP8051_47 / GP33

PWRBTN# added

37

VSS

VSS

TABLE 2-1:

PIN CHANGES FROM THE SCH5617 (CONTINUED)

Pin #

SCH5627P Pin Name

SCH5617 Pin Name

Difference

SCH5627P

DS00001996A-page 10

2009 - 2015 Microchip Technology Inc.

38

PROCHOT_IN# / PROCHOT_OUT#

/ GP016

PROCHOT_I#

PROCHOT function now

bidirectional

39

TACH1 / GP017

TACH1

GPIO added

40

TACH2 / GP020

TACH2

GPIO added

41

TACH3 / GP021

TACH3

GPIO added

42

HVSS

HVSS

43

Remote1+

Remote1+

44

Remote1-

Remote1-

45

Remote2+

Remote2+

46

Remote2-

Remote2-

47

HVTR

HVTR

48

V_IN

VIN1

49

GP022 / PWM1

PWM1

GPIO added

50

GP023 / PWM2

PWM2

GPIO added

51

GP024 / PWM3

PWM3

GPIO added

52

GP025 / PWRBTN_OUT#

IDE_RSTDRV# / GP75

PWRBTN_OUT# added,

IDE_RSTDRV# deleted

53

PCIRST_OUT1# / GP026

PCI_RST_SYS# / GP76

54

PCIRST_OUT2# / GP027

PCI_RST_SLOTS# / GP77

55

PS_ON#/ / GP030

PS_ON# / GP80

56

GP031 / BACKFEED_CUT#

BACKFEED_CUT# / GP81

57

VTR

VTR

58

GPO32

GP82

59

PWR_GOOD_3V / GP033

PWR_GOOD_3V / GP83

60

RSMRST# / GP034

RSMRST# / GP84

61

VSS

VSS

62

DSKCHG#

DSKCHG#

63

HDSEL#

HDSEL#

64

RDATA#

RDATA#

65

WRTPRT#

WRTPRT#

66

TRK0#

TRK0#

67

WGATE#

WGATE#

68

WDATA#

WDATA#

69

LATCHED_BF_CUT / GP035

CAP2

CAP2 eliminated

70

STEP#

STEP#

71

DIR#

DIR#

72

GP036 / SMBCLK1

GP22 / P12 / MRT1# / SCSI#

P12 / MTR1# / SCSI#

eliminated

73

DS0#

DS0#

74

GP040 / SMBDAT1

GP21/ P16 / DS1#

P16 / DS1# eliminated

75

MTR0#

MTR0#

76

INDEX#

INDEX#

77

GP041 / IO_PME#

GP41 / IO_PME#

78

GP042 / DRVDEN0

GP40 / DRVDEN0

79

VTR

VTR

TABLE 2-1:

PIN CHANGES FROM THE SCH5617 (CONTINUED)

Pin #

SCH5627P Pin Name

SCH5617 Pin Name

Difference