2015 Microchip Technology Inc.

DS00002028B-page 1

Product Features

• General Features

- 3.3 Volt Operation

(SIO Block is 5 Volt Tolerant)

- Programmable Wake-up Event (PME) Inter-

face

- PC99, PC2001 Compliant

- ACPI 2.0 Compliant

- Serial IRQ Interface Compatible with Serial-

ized IRQ Support for PCI Systems

- ISA Plug-and-Play Compatible Register Set

- Four Address Options for Power On Configu-

ration Port

- System Management Interrupt (SMI)

- 19 General Purpose I/O pins, 2 with VID

compatible inputs

- Security Key Register (32 byte) for Device

Authentication

• Low Pin Count Bus (LPC) Interface

- Supports LPC Bus frequencies of 19MHz to

33MHz

• Watchdog Timer

• Resume and Main Power Good Generator

• Programmable Clock Output to 16Hz

• 2 Full Function Serial Ports

- High Speed NS16C550A Compatible UARTs

with

- Send/Receive 16-Byte FIFOs

- Supports 230k, 460k, 921k and 1.5M Baud

- Programmable Baud Rate Generator

- Modem Control Circuitry

- 480 Address and 15 IRQ Options

- Support IRQ Sharing among serial ports

- RS485 Auto Direction Control Mode

• Hardware Monitor

- Monitor Power supplies (+2.5V, +5V, +12V,

Vccp (processor voltage), VCC, Vbat and Vtr.

- Remote Thermal Diode Sensing for One

External Temperature Measurement accurate

to 1.5

o

C

- Internal Ambient Temperature Measurement

- Limit Comparison of all Monitored Values

- One Programmable Automatic FAN control

based on temperature

• IDE Reset Output and 3 PCI Reset Buffers with

Software Control Capability

• Power Button Control and AC Power Failure

Recovery

• Temperature Range Available

- Industrial (+85

C to -40C)

- Commercial (+70

C to 0C)

• 64-Ball WFBGA RoHS Compliant Package

SCH3223

LPC IO with Reset Generation, HWM and

Multiple Serial Ports

SCH3223

DS00002028B-page 2

2015 Microchip Technology Inc.

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at

docerrors@microchip.com

. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for cur-

rent devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the

revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site;

http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are

using.

Customer Notification System

Register on our web site at

www.microchip.com

to receive the most current information on all of our products.

2015 Microchip Technology Inc.

DS00002028B-page 3

SCH3223

Table of Contents

1.0 General Description ........................................................................................................................................................................ 4

2.0 Pin Layout ....................................................................................................................................................................................... 5

3.0 Block Diagram ............................................................................................................................................................................... 13

4.0 Power Functionality ....................................................................................................................................................................... 14

5.0 SIO Overview ................................................................................................................................................................................ 17

6.0 LPC Interface ................................................................................................................................................................................ 18

7.0 Serial Port (UART) ........................................................................................................................................................................ 20

8.0 Power Management ...................................................................................................................................................................... 36

9.0 Serial IRQ ..................................................................................................................................................................................... 37

10.0 General Purpose I/O (GPIO) ....................................................................................................................................................... 40

11.0 System Management Interrupt (SMI) .......................................................................................................................................... 45

12.0 PME Support ............................................................................................................................................................................... 46

13.0 Watchdog Timer .......................................................................................................................................................................... 48

14.0 Programmable Clock Output ....................................................................................................................................................... 49

15.0 Reset Generation ........................................................................................................................................................................ 50

16.0 Buffered PCI Outputs .................................................................................................................................................................. 53

17.0 Power Control Features .............................................................................................................................................................. 55

18.0 Low Battery Detection Logic ....................................................................................................................................................... 62

19.0 Battery Backed Security Key Register ........................................................................................................................................ 64

20.0 Temperature Monitoring and Fan Control ................................................................................................................................... 66

21.0 Hardware Monitoring Register Set ............................................................................................................................................ 100

22.0 Config Registers ....................................................................................................................................................................... 137

23.0 Runtime Registers .................................................................................................................................................................... 150

24.0 Valid Power Modes ................................................................................................................................................................... 169

25.0 Operational Description ............................................................................................................................................................ 170

26.0 Timing Diagrams ....................................................................................................................................................................... 178

27.0 Package Outline ........................................................................................................................................................................ 188

Appendix A: ADC Voltage Conversion .............................................................................................................................................. 189

Appendix B: Example Fan Circuits ................................................................................................................................................... 190

Appendix C: Revision History ........................................................................................................................................................... 193

Product Identification System ........................................................................................................................................................... 194

The Microchip Web Site .................................................................................................................................................................... 195

Customer Change Notification Service ............................................................................................................................................. 195

Customer Support ............................................................................................................................................................................. 195

SCH3223

DS00002028B-page 4

2015 Microchip Technology Inc.

1.0

GENERAL DESCRIPTION

The SCH3223 is a 3.3V (Super I/O Block is 5V tolerant) PC99/PC2001 compliant Super I/O controller with an LPC inter-

face. The SCH3223 also includes Hardware Monitoring capabilities, enhanced Security features, Power Control logic

and Motherboard Glue logic.

SCH3223 The SCH3223 incorporates Super I/O functionality including LPC bus interface, a Serialized IRQ interface

and the ISA Plug-and-Play standard register set (Version 1.0a). The I/O Address and hardware IRQ of each logical

device in the SCH3223 may be reprogrammed through the internal configuration registers. Related functionality offers

flexibility to the system designer, with General Purpose I/O control functions, and control of two LED's.

The SCH3223's Hardware Monitoring capability includes temperature, voltage and fan speed monitoring. It has the abil-

ity to alert the system of out-of-limit conditions and automatically control the speed of a fan via PWM and Tach pins.

There are four analog inputs for monitoring external voltages of +5V, +2.5V, +12V and Vccp (core processor voltage),

as well as internal monitoring of its VCC, VTR, and Vbat power supplies. The SCH3223 includes support for monitoring

one external temperature via thermal diode inputs and an internal sensor for measuring ambient temperature. The hard-

ware monitoring block of the SCH3223 is accessible via the LPC bus. Interrupt events can create PME wakeup events.

The Motherboard Glue logic includes various power management and system logic including generation of nRSMRST

and reset generation. The reset generation includes a watchdog timer which can be used to generate a reset pulse. The

width of this pulse is selectable via an external strapping option.

The two serial ports are fully functional NS16550 compatible UARTs that support data rates up to 1.5 Mbps. The Serial

Ports contain programmable direction control, which can automatically drive nRTS based on the status of the Output

Buffer.

The SCH3223 is ACPI 1.0/2.0 compatible and therefore supports multiple low power-down modes.

CAUTION: This device contains circuits which must not be used because their pins are not brought out of the package,

and are pulled to known states internally. Any features, and especially Logical Devices, that are not listed in this docu-

ment must not be activated or accessed. Doing so may cause unpredictable behavior and/or excessive currents, and

therefore may damage the device and/or the system.

1.1

Reference Documents

1.

Intel Low Pin Count Specification, Revision 1.0, September 29, 1997

2.

PCI Local Bus Specification, Revision 2.2, December 18, 1998

3.

Advanced Configuration and Power Interface Specification, Revision 1.0b, February 2, 1999

2015 Microchip Technology Inc.

DS00002028B-page 5

SCH3223

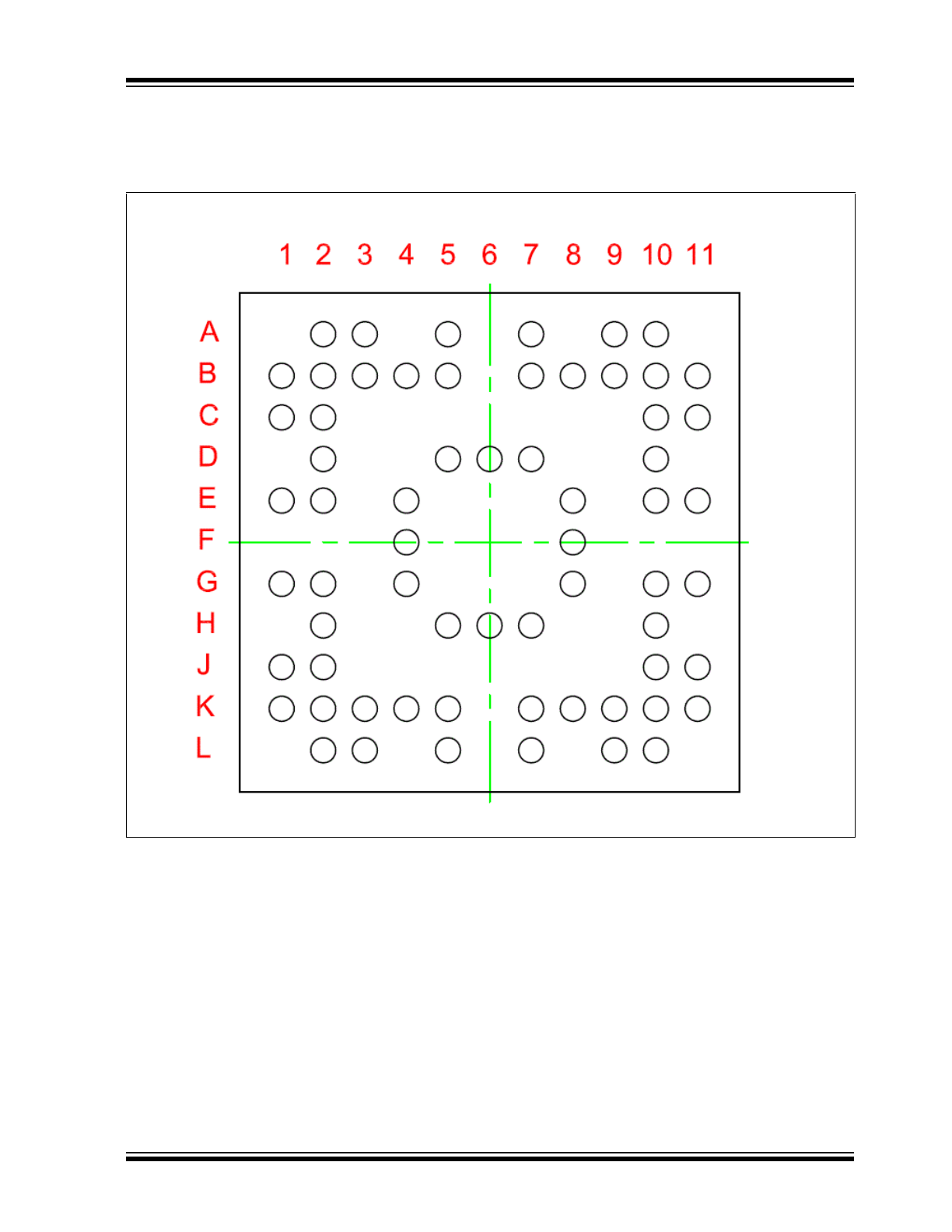

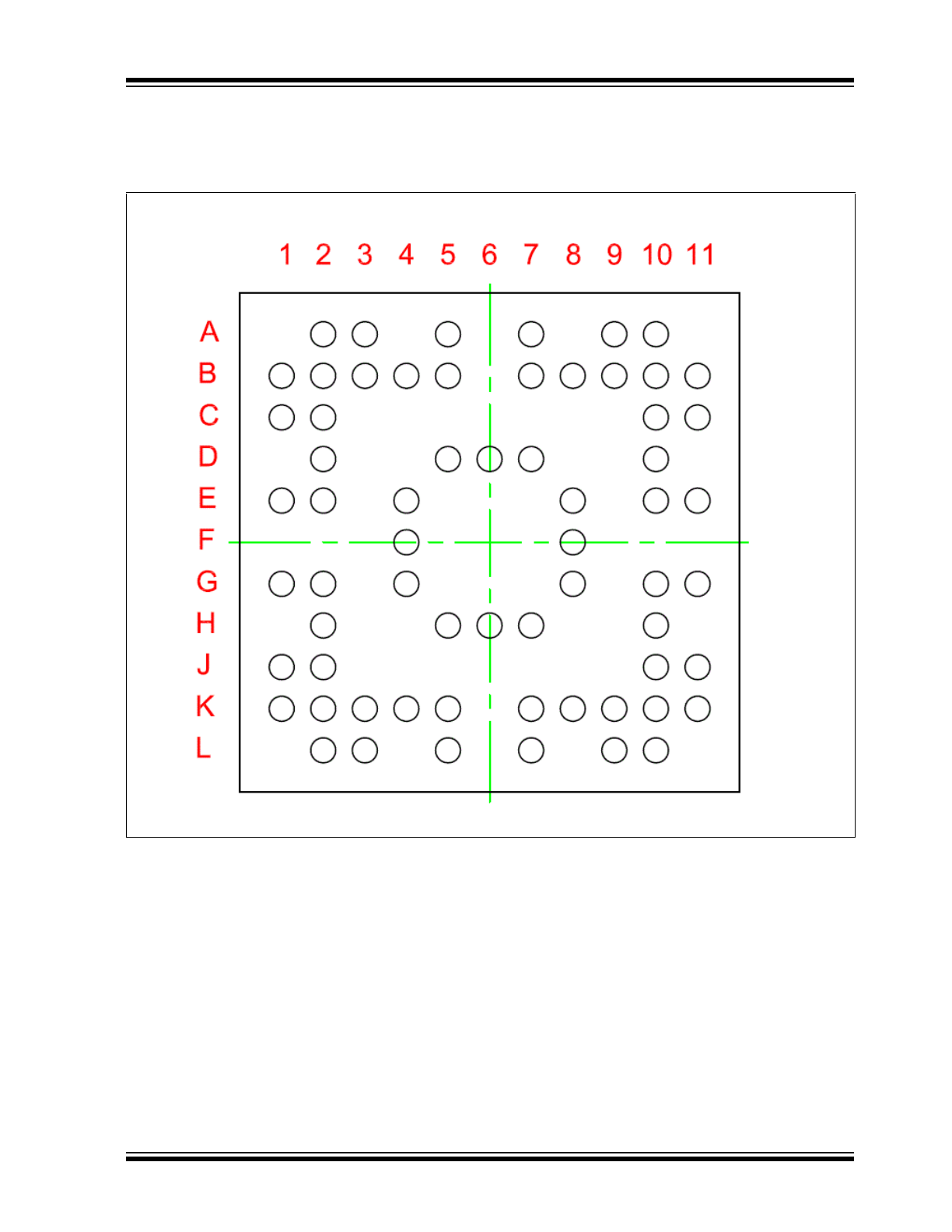

2.0

PIN LAYOUT

This is a 64-ball 6mm x 6mm package, with ball pitch of 0.5mm. However, the sparse 0.5mm pitch ball array allows

0.65mm trace routing rules. For a specific recommendation, see the drawing in

Section 27.0, "Package Outline," on

page 188

.

FIGURE 2-1:

SCH3223 64-BALL WFBGA FOOTPRINT DIAGRAM, TOP VIEW

SCH3223

DS00002028B-page 6

2015 Microchip Technology Inc.

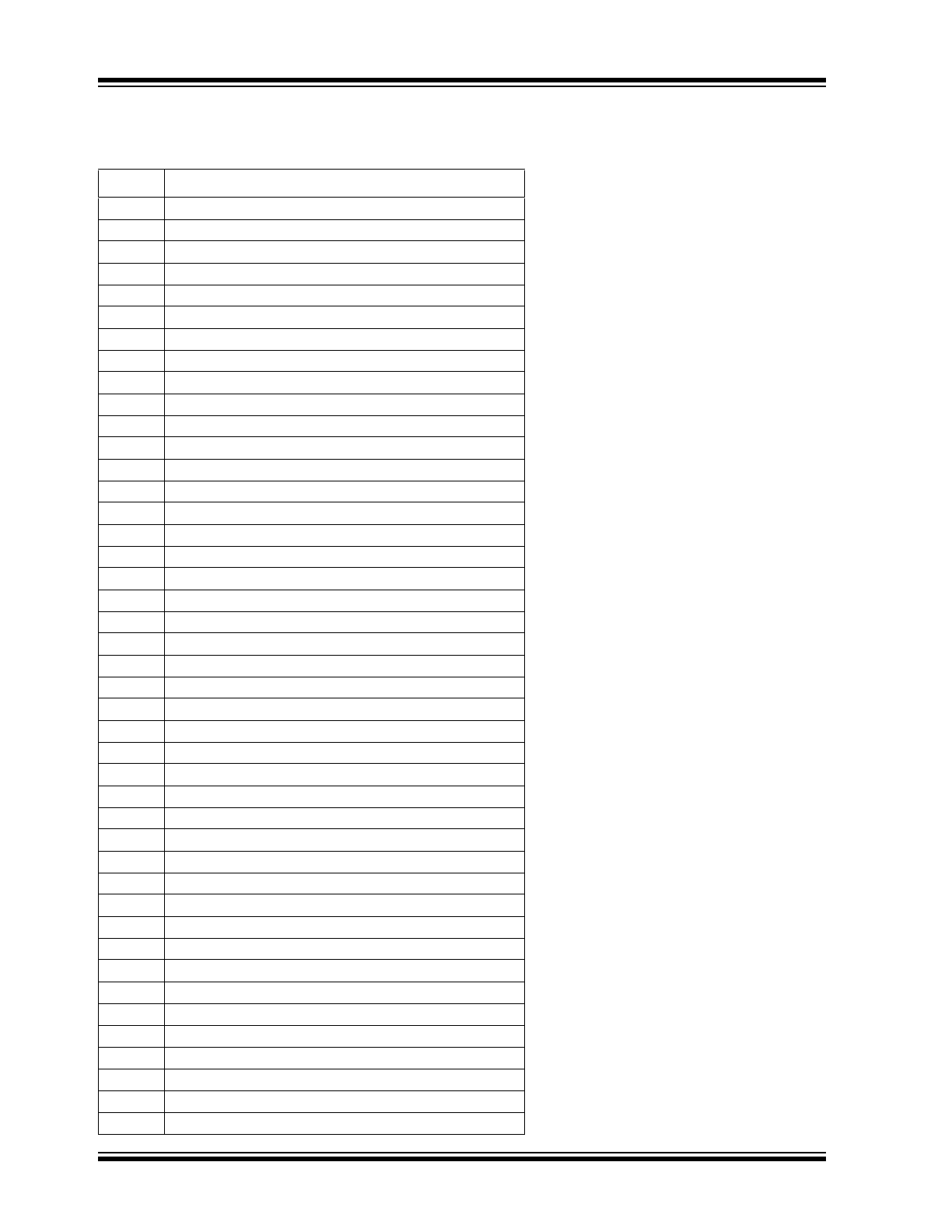

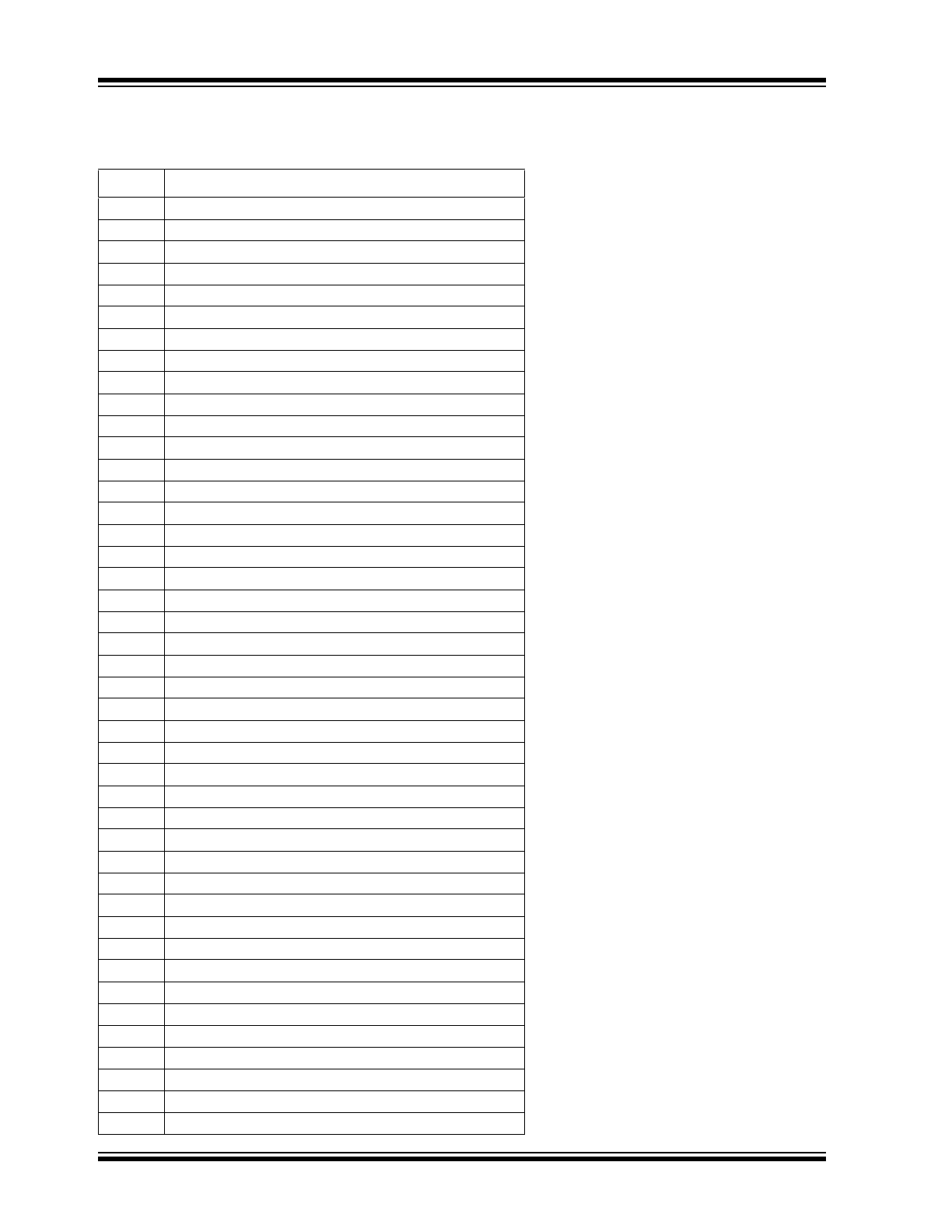

2.1

SCH3223 Pin Layout Summary

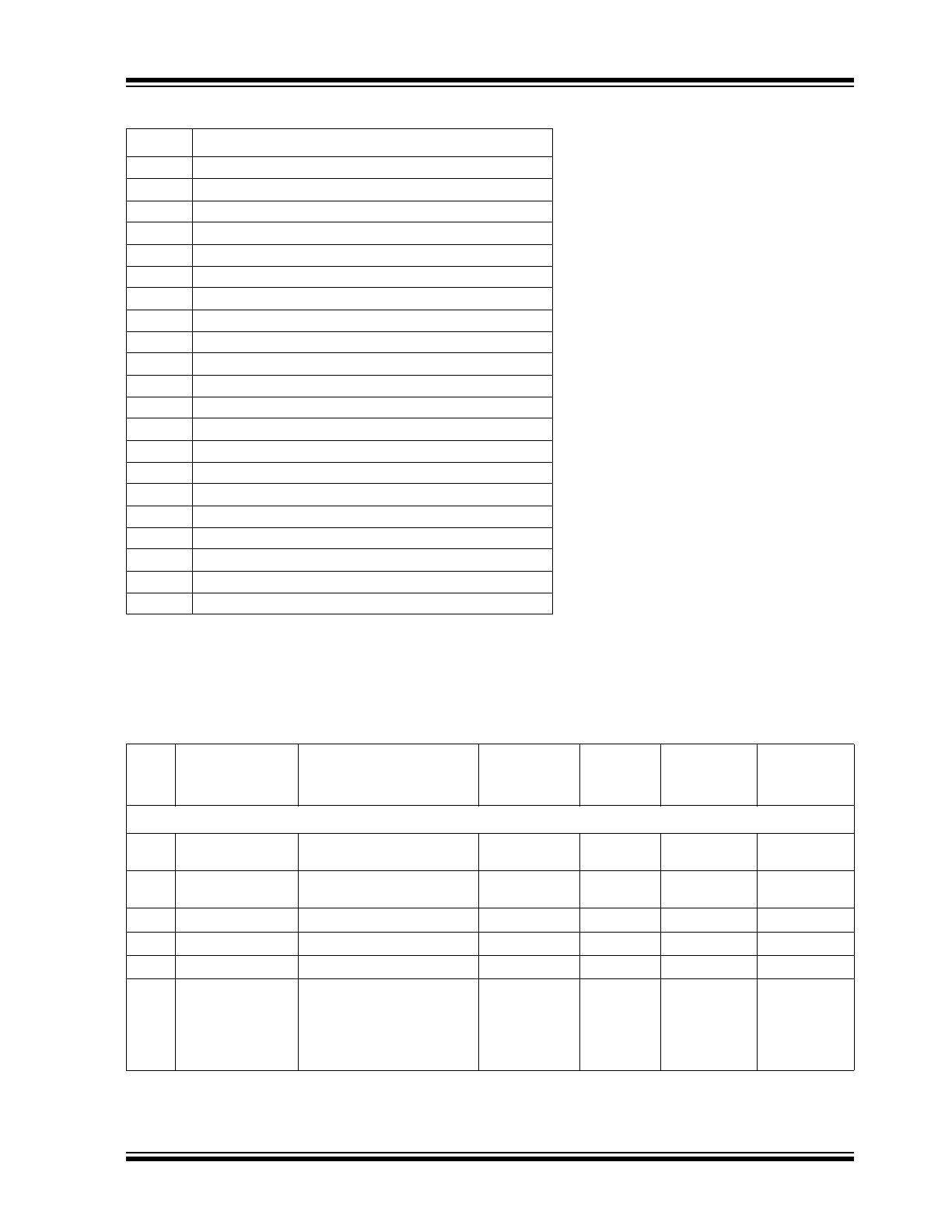

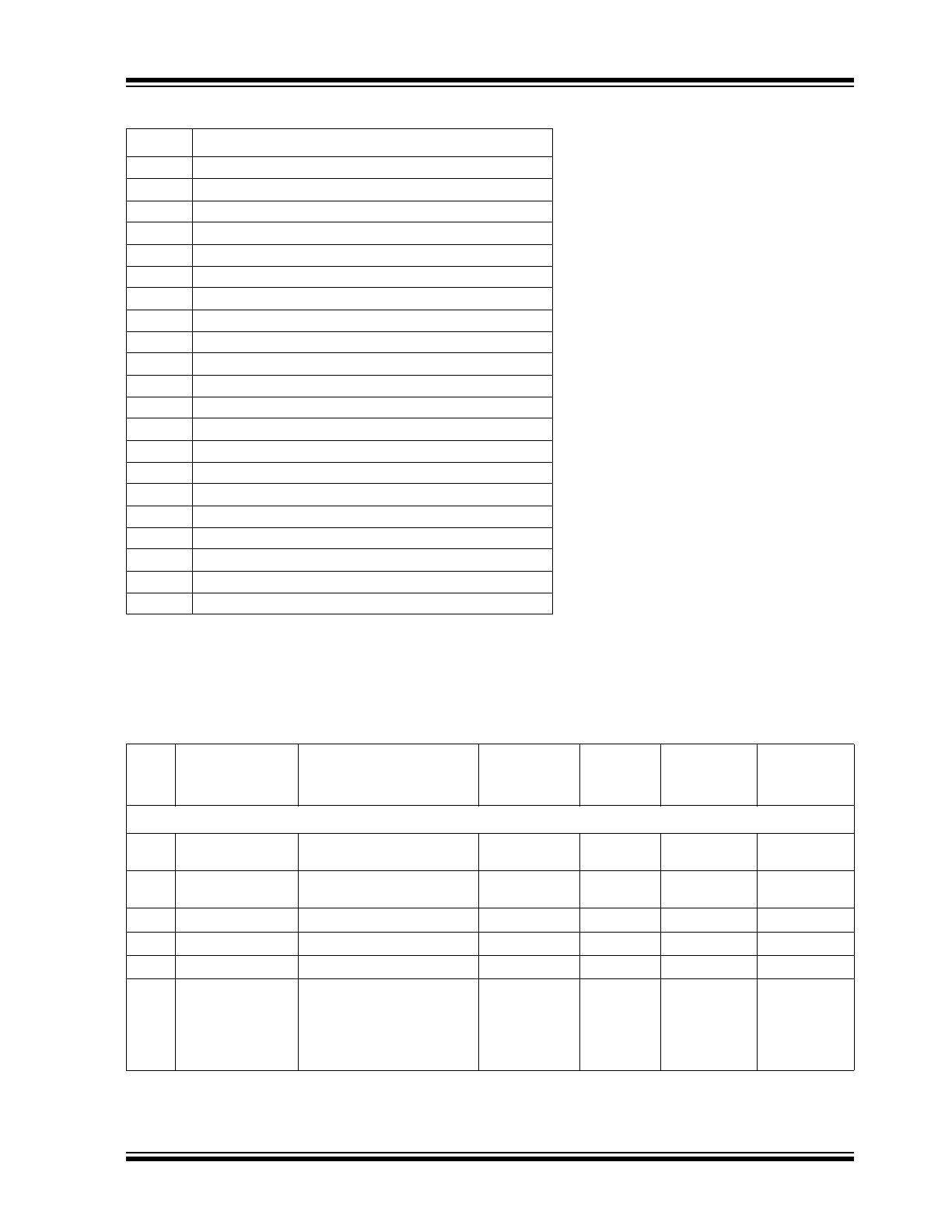

TABLE 2-1:

SCH3223 SUMMARY

Ball#

Function (

Note 1

)

B1

+12V_IN

C1

+5V_IN

C2

VTR

D2

TEST=VSS

E2

VSS

E1

CLOCKI

E4

LAD0

F4

LAD1

G4

LAD2

G2

LAD3

G1

LFRAME#

H6

PCI_RESET#

H5

PCI_CLK

H2

SER_IRQ

J2

VSS

K3

VCC

J1

nIDE_RSTDRV / GP44

K2

nPCIRST1 / GP45

K1

nPCIRST2 / GP46

L2

nPCIRST3 / GP47

L3

AVSS

K4

VBAT

K5

GP27 / nIO_SMI

L5

VTR

L9

nRI1

L10

nDCD1

K11

RXD1

K7

TXD1

K8

nDSR1

K9

nRTS1 / SYSOPT0

K10

nCTS1

J10

nDTR1 / SYSOPT1

J11

GP50 / nRI2

H10

VTR

L7

VSS

H7

GP51 / nDCD2

G11

GP52 / RXD2

G10

GP53 / TXD2

G8

GP54 / nDSR2

F8

GP55 / nRTS2 / RESGEN

E8

GP56 / nCTS2

D6

GP57 / nDTR2

D7

PB_OUT#

2015 Microchip Technology Inc.

DS00002028B-page 7

SCH3223

Note 1:

Device ID register at Plug&Play Index 0x20 holds 0x7D.

2.2

Pin Functions

E10

PS_ON#

E11

PB_IN#

D10

SLP_SX#

C11

GP42 / nIO_PME

C10

GP61 / nLED2 / CLKO

B11

GP60 / nLED1 / WDT

A10

GP63

B10

CLKI32

A9

nRSMRST

B9

GP62

B8

PWRGD_OUT

B7

PWRGD_PS

A7

nFPRST / GP30

A5

PWM1

B5

FANTACH1

D5

HVSS

B4

HVTR

B3

REMOTE1-

A3

REMOTE1+

B2

VCCP_IN

A2

+2.5V_IN

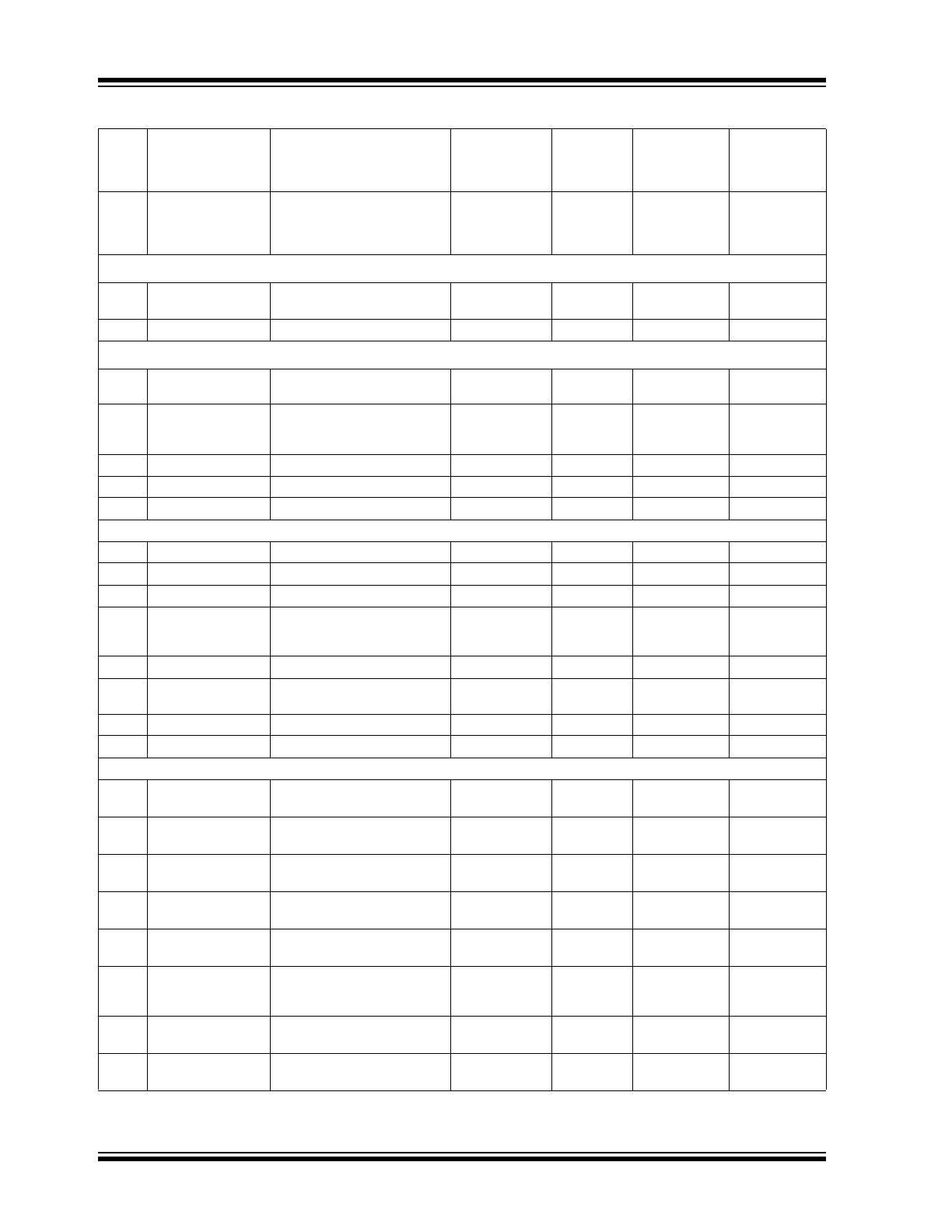

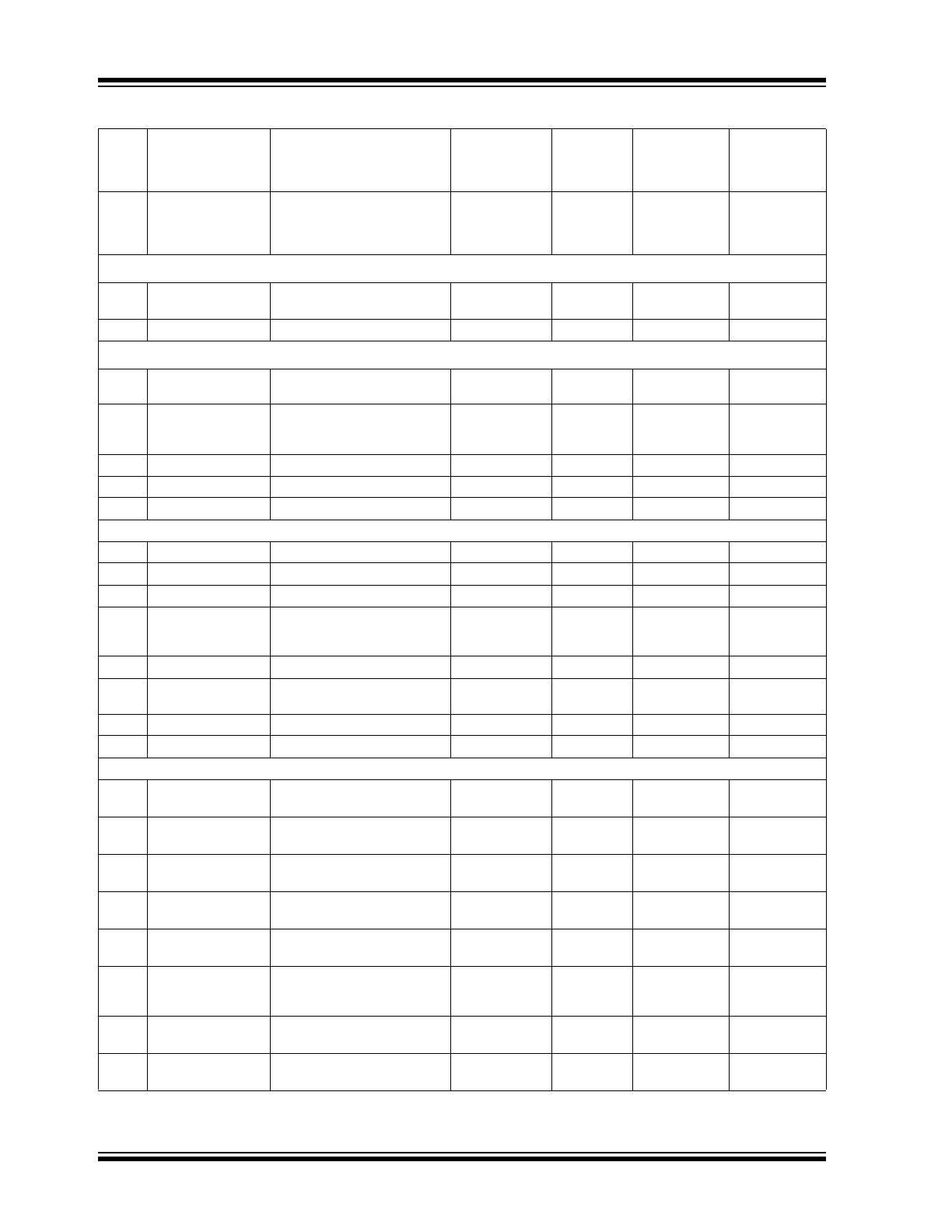

TABLE 2-2:

SCH3223 PIN FUNCTIONS DESCRIPTION

Note

Name

Description

VCC

Power

Plane

VTR

Power

Plane

VCC=0

Operation

(

Note 2-10

)

Buffer

Modes

(

Note 2-1

)

POWER PINS

2-3

,

2-4

VCC

+3.3 Volt Supply Voltage

2-3

,

2-4

VTR

+3.3 Volt Standby Supply

Voltage

2-6

VBAT

+3.0 Volt Battery Supply

)

VSS

Ground

AVSS

Analog Ground

2-3

HVTR

Analog Power. +3.3V VTR

pin dedicated to the

Hardware Monitoring

block.

HVTR is powered

by +3.3V Standby power

VTR.

TABLE 2-1:

SCH3223 SUMMARY (CONTINUED)

Ball#

Function (

Note 1

)

SCH3223

DS00002028B-page 8

2015 Microchip Technology Inc.

2-3

HVSS

Analog Ground. Internally

connected to all of the

Hardware Monitoring Block

circuitry.

CLOCK PINS

CLKI32

32.768kHz Trickle Clock

Input

CLKI32

No Gate

IS

CLOCKI

14.318MHz Clock Input

CLOCKI

IS

LPC INTERFACE

LAD[3:0]

Multiplexed Command

Address and Data

LAD[3:0]

GATE/ Hi-Z

PCI_IO

LFRAME#

Frame signal. Indicates

start of new cycle and

termination of broken cycle

LFRAME#

GATE

PCI_I

PCI_RESET#

PCI Reset

PCI_RESET#

NO GATE

PCI_I

PCI_CLK

PCI Clock

PCI_CLK

GATE

PCI_ICLK

SER_IRQ

Serial IRQ

SER_IRQ

GATE / Hi-Z

PCI_IO

SERIAL PORT 1 INTERFACE

RXD1

Receive Data 1

RXD1

GATE

IS

TXD1

Transmit Data 1

TXD1

HI-Z

O12/O12

nDSR1

Data Set Ready 1

nDSR1

GATE

I

2-5

nRTS1 /

SYSOPT0

Request to Send 1/

SYSOPT (Configuration

Port Base Address Control)

nRTS1/

SYSOPT0

GATE/ Hi-Z

OP14 / I

nCTS1

Clear to Send 1

nCTS1

GATE

I

nDTR1 /

SYSOPT1

Data Terminal Ready 1

nDTR1 /

SYSOPT1

GATE/ Hi-Z

O6 / I

2-7

nRI1

Ring Indicator 1

nRI1

GATE

IS

nDCD1

Data Carrier Detect 1

nDCD1

GATE

I

SERIAL PORT 2 INTERFACE

2-7

GP50 / nRI2

Ring Indicator 2

GP50

nRI2

NO GATE/

HI-Z

(I/OD8/OD8) /

IS

2-7

GP51 / nDCD2

Data Carrier Detect 2

GP51 /

nDCD2

NO GATE/

HI-Z

(I/OD8/OD8) /

I

2-7

GP52 / RXD2

Receive Data 2

GP52 / RXD2

NO GATE/

HI-Z

(I/OD8OD8) /

IS

2-9

,

2-7

GP53 / TXD2

Transmit Data 2

GP53 / TXD2

NO GATE/

HI-Z

(I/O12/OD12)

/ (O12/OD12)

2-7

GP54 / nDSR2

Data Set Ready 2

GP54 /

nDSR2

NO GATE/

HI-Z

(I/OD8/OD8) /

I

2-7

2-11

GP55 / nRTS2 /

RESGEN

Request to Send 2 /

Reset Generator Pulse

Width Strap Option

GP55 / nRTS2

/

RESGEN

NO GATE/

HI-Z

(I/O8/OD8) / I

/ IOP8

2-7

GP56 / nCTS2

Clear to Send 2

GP56 / nCTS2

NO GATE/

HI-Z

(I/OD8OD8) /

I

2-7

GP57 / nDTR2

Data Terminal Ready 2

GP57 / nDTR2

NO GATE/

HI-Z

(I/OD8OD8) /

O6

TABLE 2-2:

SCH3223 PIN FUNCTIONS DESCRIPTION (CONTINUED)

Note

Name

Description

VCC

Power

Plane

VTR

Power

Plane

VCC=0

Operation

(

Note 2-10

)

Buffer

Modes

(

Note 2-1

)

2015 Microchip Technology Inc.

DS00002028B-page 9

SCH3223

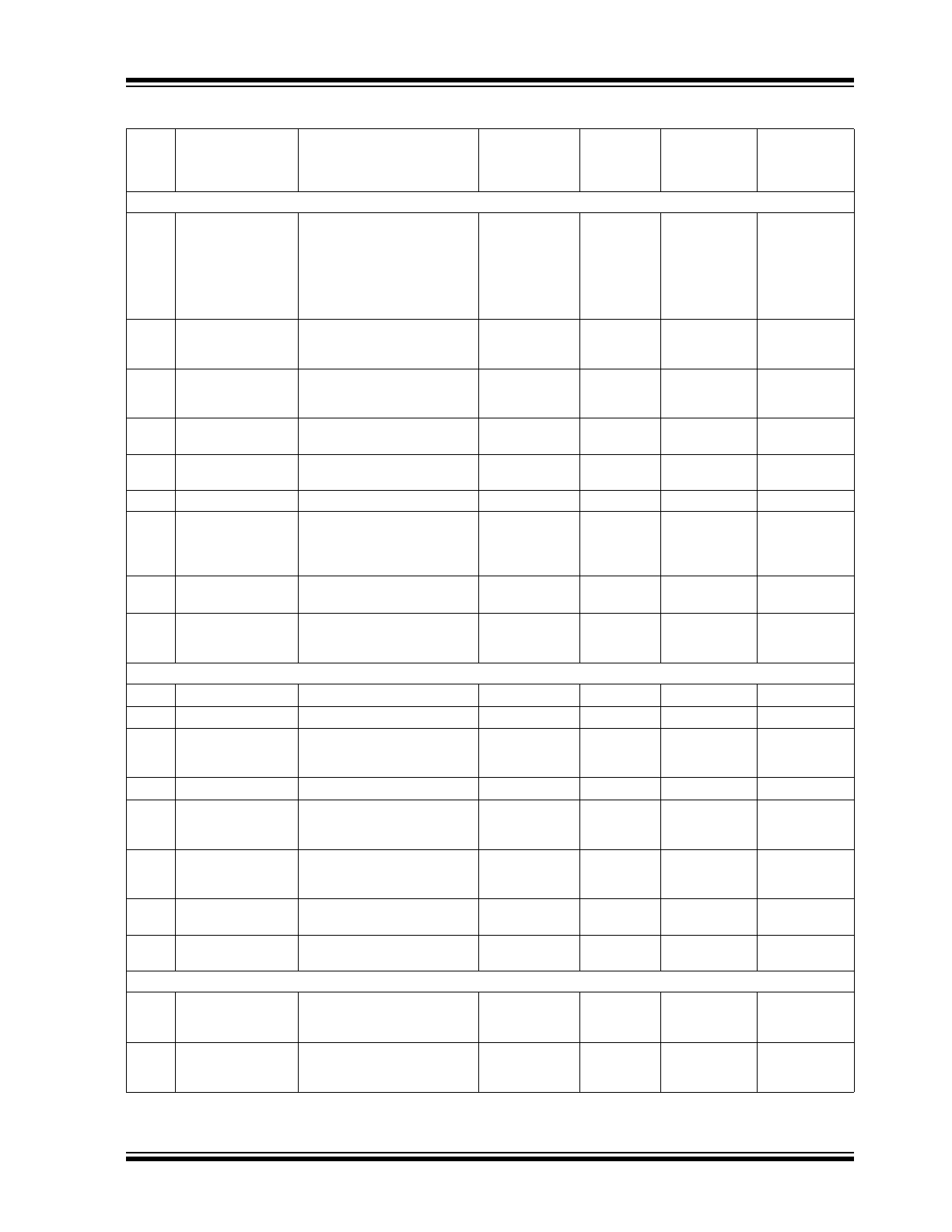

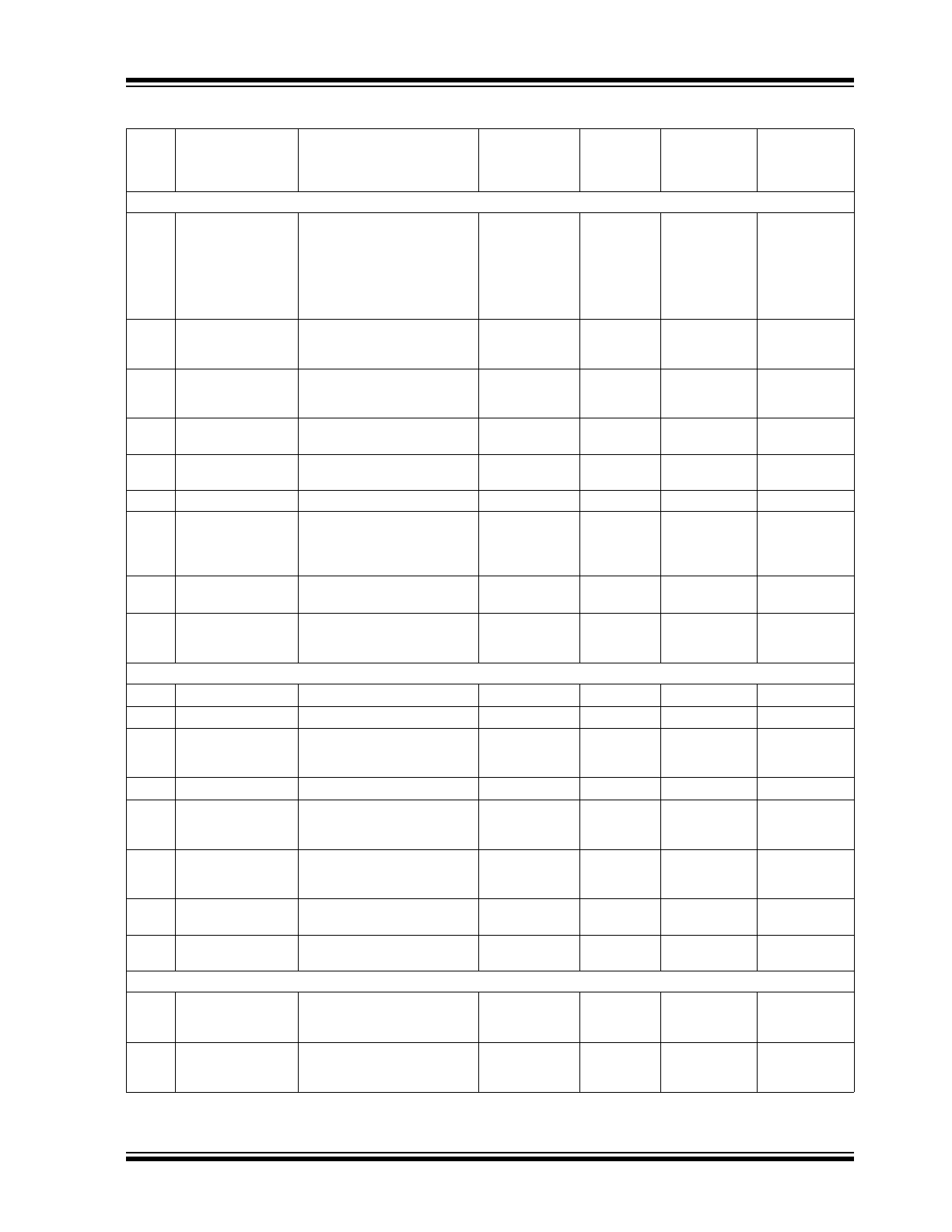

MISCELLANEOUS PINS

GP42/

nIO_PME

General Purpose I/O.

Power Management Event

Output. This active low

Power Management Event

signal allows this device to

request wake-up in either

S3 or S5 and below.

GP42/

nIO_PME

NO GATE

(I/O12/OD12)

/(O12/OD12)

2-6

,

2-7

GP60

/nLED1

/WDT

General Purpose I/O

/nLED1

Watchdog Timer Output

GP60

/nLED1

/WDT

NO GATE

(I/O12/OD12)

/(O12/OD12)

/(O12/OD12)

nFPRST /

GP30

Front Panel Reset /

General Purpose IO

nFPRST /

GP30

NO GATE

ISPU_400 /

(I/O4/OD4)

PWRGD_PS

Power Good Input from

Power Supply

PWRGD_P

S

NO GATE

ISPU_400

PWRGD_OUT

Power Good Output –

Open Drain

PWRGD_

OUT

NO GATE

OD8

nRSMRST

Resume Reset Output

nRSMRST

NO GATE

OD24

2-6

,

2-7

GP61

/nLED2 /

CLKO

General Purpose I/O

/nLED2

/ Programmable Clock

Output

GP61

/nLED2 /

CLKO

NO GATE

(I/O12/OD12)

/ (O12/OD12)

/ (O12/OD12)

2-7

GP27 /nIO_SMI

General Purpose I/O

/System Mgt. Interrupt

GP27

/nIO_SMI

GP27

/

HI-Z

(I/O12/OD12)

/(O12/OD12)

TEST

Test purposes. Customer

should tie this pin to VSS at

all times.

TEST

TEST

HARDWARE MONITORING BLOCK

2-8

+5V_IN

Analog input for +5V

HVTR

I

AN

2-8

+2.5_IN

Analog input for +2.5V

HVTR

I

AN

2-8

VCCP_IN

Analog input for +Vccp

(processor voltage: 1.5 V

nominal).

HVTR

I

AN

2-8

+12V_IN

Analog input for +12V

HVTR

I

AN

REMOTE1-

This is the negative input

(current sink) from the

remote thermal diode 1.

HVTR

I

AND-

REMOTE1+

This is the positive input

(current source) from the

remote thermal diode 1.

HVTR

I

AND+

PWM1

Fan Speed Control 1

Output.

PWM1 OD8

FANTACH1

Tachometer Input 1 for

monitoring a fan.

FANTACH

1

I

M

RESET OUTPUTS

nPCIRST3 /

GP47

PCI Reset output 3

GPIO with Schmitt trigger

input

nPCIRST3

GP47

NO GATE

(O4/OD4) /

(IS/O4/OD4)

nPCIRST2 /

GP46

PCI Reset output 2

GPIO with Schmitt trigger

input

nPCIRST2

GP46

NO GATE

(O8/OD8) /

(IS/O8/OD8)

TABLE 2-2:

SCH3223 PIN FUNCTIONS DESCRIPTION (CONTINUED)

Note

Name

Description

VCC

Power

Plane

VTR

Power

Plane

VCC=0

Operation

(

Note 2-10

)

Buffer

Modes

(

Note 2-1

)

SCH3223

DS00002028B-page 10

2015 Microchip Technology Inc.

Note 2-1

Buffer types per function on multiplexed pins are separated by a slash “/”. Buffer types in parenthesis

represent multiple buffer types for a single pin function.

Note 2-2

Pins that have input buffers must always be held to either a logical low or a logical high state when

powered. Bi-directional buses that may be trisected should have either weak external pull-ups or pull-

downs to hold the pins in a logic state (i.e., logic states are VCC or ground).

Note 2-3

VCC and VSS pins are for Super I/O Blocks. HVTR and HVSS are dedicated for the Hardware

Monitoring Block.

Note 2-4

VTR can be connected to VCC if no wake-up functionality is required.

Note 2-5

The nRTS1/SYSOPT0 pin requires an external pull-down resistor to put the base I/O address for

configuration at 0x02E. An external pull-up resistor is required to move the base I/O address for

configuration to 0x04E.

Note 2-6

The LED pins are powered by VTR so that the LEDs can be controlled when the part is under VTR

power.

Note 2-7

This pin is an input into the wake-up logic that is powered by VTR. In the case of a ring indicator for

a serial port, or a GPIO it will also go to VCC powered logic. This logic must be disabled when

VCC=0.

Note 2-8

This analog input is backdrive protected.

Although HVTR is powered by VTR, it is possible that

monitored power supplies may be powered when HVTR is off.

Note 2-9

The GP53/TXD2 pin defaults to the GPIO input function on a VTR POR and presents a tristate

impedance. When VCC=0 the pin is tristate. If GP53 function is selected and VCC is power is applied,

the pin reflects the current state of GP53. The GP53/TXD2 pin is tristate when it is configured for the

TXD2 function.

Note 2-10

All logic is powered by VTR. Vcc on pin 29 is used as an indication of the presence of the VCC rail

being active. All logic that requires VCC power, is only enabled when the VCC rail is active.

Note 2-11

The GP55/nRTS2/RESGEN pin requires an external pull-down resistor to enable 500ms delay circuit.

An external pull-up resistor is required to enable 200ms delay circuit.

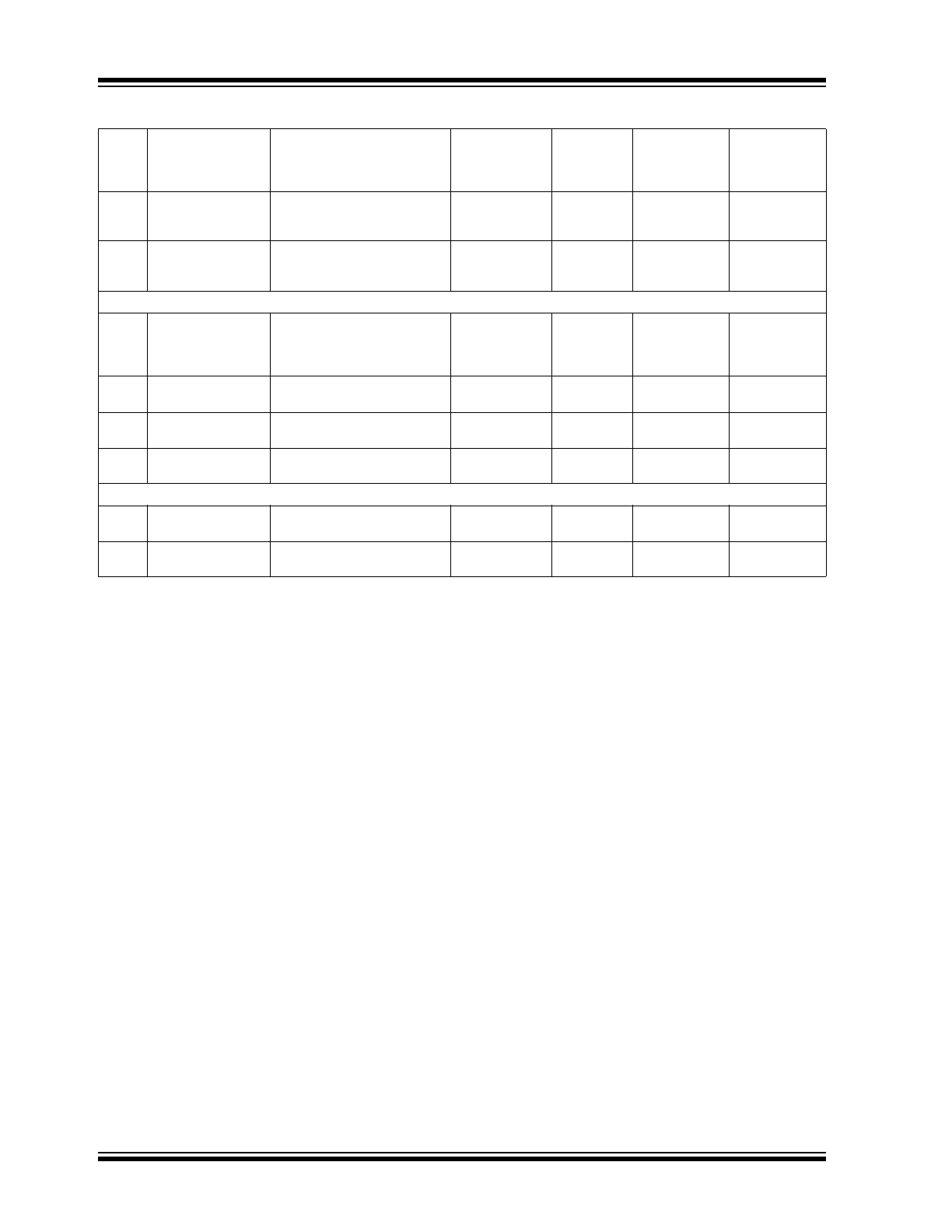

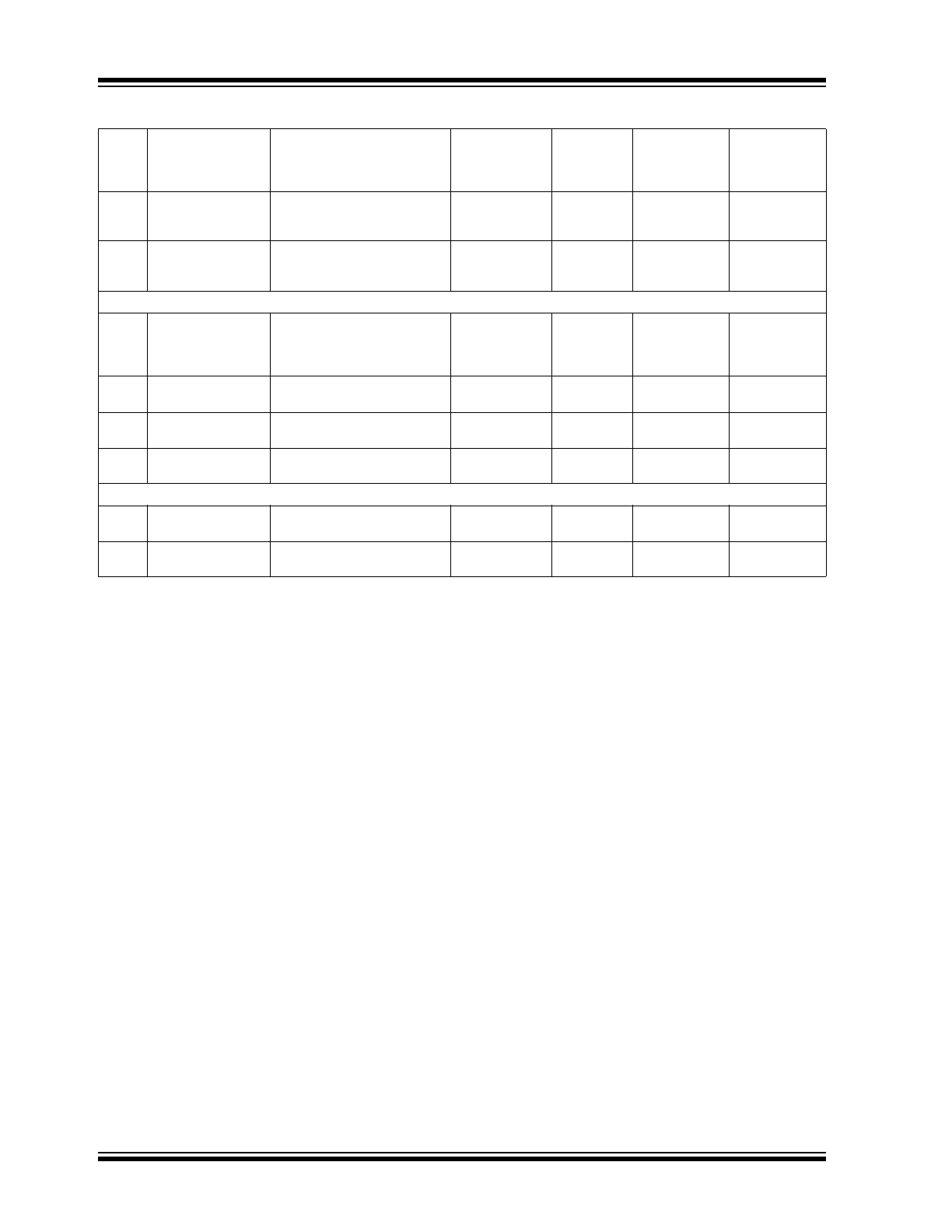

nPCIRST1 /

GP45

PCI Reset output 1

GPIO with Schmitt trigger

input

nPCIRST1

GP45

NO GATE

(O8/OD8) /

(IS/O8/OD8)

nIDE_RSTDRV /

GP44

IDE Reset output

GPIO with Schmitt trigger

input

nIDE_RSTDR

V

GP44

NO GATE

(O4/OD4) /

(IS/O4/OD4)

GLUE LOGIC

PB_IN#

Power Button In is used to

detect a power button

event

PB_IN# NO

GATE

I

2-7

SLP_SX#

Sx Sleep State Input Pin.

SLP_SX#

NO GATE

I

PB_OUT# Power

Button

Out

PB_OUT# NO

GATE

O8

PS_ON#

Power supply On

PS_ON#

NO GATE

O12

DEDICATED GPIO

2-7

GP62*

GPIO with I_VID buffer

Input

GP62* NO

GATE

(I/O8/OD8)

2-7

GP63*

GPIO with I_VID buffer

Input

GP63* NO

GATE

(I/O8/OD8)

TABLE 2-2:

SCH3223 PIN FUNCTIONS DESCRIPTION (CONTINUED)

Note

Name

Description

VCC

Power

Plane

VTR

Power

Plane

VCC=0

Operation

(

Note 2-10

)

Buffer

Modes

(

Note 2-1

)

2015 Microchip Technology Inc.

DS00002028B-page 1

Product Features

• General Features

- 3.3 Volt Operation

(SIO Block is 5 Volt Tolerant)

- Programmable Wake-up Event (PME) Inter-

face

- PC99, PC2001 Compliant

- ACPI 2.0 Compliant

- Serial IRQ Interface Compatible with Serial-

ized IRQ Support for PCI Systems

- ISA Plug-and-Play Compatible Register Set

- Four Address Options for Power On Configu-

ration Port

- System Management Interrupt (SMI)

- 19 General Purpose I/O pins, 2 with VID

compatible inputs

- Security Key Register (32 byte) for Device

Authentication

• Low Pin Count Bus (LPC) Interface

- Supports LPC Bus frequencies of 19MHz to

33MHz

• Watchdog Timer

• Resume and Main Power Good Generator

• Programmable Clock Output to 16Hz

• 2 Full Function Serial Ports

- High Speed NS16C550A Compatible UARTs

with

- Send/Receive 16-Byte FIFOs

- Supports 230k, 460k, 921k and 1.5M Baud

- Programmable Baud Rate Generator

- Modem Control Circuitry

- 480 Address and 15 IRQ Options

- Support IRQ Sharing among serial ports

- RS485 Auto Direction Control Mode

• Hardware Monitor

- Monitor Power supplies (+2.5V, +5V, +12V,

Vccp (processor voltage), VCC, Vbat and Vtr.

- Remote Thermal Diode Sensing for One

External Temperature Measurement accurate

to 1.5

o

C

- Internal Ambient Temperature Measurement

- Limit Comparison of all Monitored Values

- One Programmable Automatic FAN control

based on temperature

• IDE Reset Output and 3 PCI Reset Buffers with

Software Control Capability

• Power Button Control and AC Power Failure

Recovery

• Temperature Range Available

- Industrial (+85

C to -40C)

- Commercial (+70

C to 0C)

• 64-Ball WFBGA RoHS Compliant Package

SCH3223

LPC IO with Reset Generation, HWM and

Multiple Serial Ports

SCH3223

DS00002028B-page 2

2015 Microchip Technology Inc.

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at

docerrors@microchip.com

. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for cur-

rent devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the

revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site;

http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are

using.

Customer Notification System

Register on our web site at

www.microchip.com

to receive the most current information on all of our products.

2015 Microchip Technology Inc.

DS00002028B-page 3

SCH3223

Table of Contents

1.0 General Description ........................................................................................................................................................................ 4

2.0 Pin Layout ....................................................................................................................................................................................... 5

3.0 Block Diagram ............................................................................................................................................................................... 13

4.0 Power Functionality ....................................................................................................................................................................... 14

5.0 SIO Overview ................................................................................................................................................................................ 17

6.0 LPC Interface ................................................................................................................................................................................ 18

7.0 Serial Port (UART) ........................................................................................................................................................................ 20

8.0 Power Management ...................................................................................................................................................................... 36

9.0 Serial IRQ ..................................................................................................................................................................................... 37

10.0 General Purpose I/O (GPIO) ....................................................................................................................................................... 40

11.0 System Management Interrupt (SMI) .......................................................................................................................................... 45

12.0 PME Support ............................................................................................................................................................................... 46

13.0 Watchdog Timer .......................................................................................................................................................................... 48

14.0 Programmable Clock Output ....................................................................................................................................................... 49

15.0 Reset Generation ........................................................................................................................................................................ 50

16.0 Buffered PCI Outputs .................................................................................................................................................................. 53

17.0 Power Control Features .............................................................................................................................................................. 55

18.0 Low Battery Detection Logic ....................................................................................................................................................... 62

19.0 Battery Backed Security Key Register ........................................................................................................................................ 64

20.0 Temperature Monitoring and Fan Control ................................................................................................................................... 66

21.0 Hardware Monitoring Register Set ............................................................................................................................................ 100

22.0 Config Registers ....................................................................................................................................................................... 137

23.0 Runtime Registers .................................................................................................................................................................... 150

24.0 Valid Power Modes ................................................................................................................................................................... 169

25.0 Operational Description ............................................................................................................................................................ 170

26.0 Timing Diagrams ....................................................................................................................................................................... 178

27.0 Package Outline ........................................................................................................................................................................ 188

Appendix A: ADC Voltage Conversion .............................................................................................................................................. 189

Appendix B: Example Fan Circuits ................................................................................................................................................... 190

Appendix C: Revision History ........................................................................................................................................................... 193

Product Identification System ........................................................................................................................................................... 194

The Microchip Web Site .................................................................................................................................................................... 195

Customer Change Notification Service ............................................................................................................................................. 195

Customer Support ............................................................................................................................................................................. 195

SCH3223

DS00002028B-page 4

2015 Microchip Technology Inc.

1.0

GENERAL DESCRIPTION

The SCH3223 is a 3.3V (Super I/O Block is 5V tolerant) PC99/PC2001 compliant Super I/O controller with an LPC inter-

face. The SCH3223 also includes Hardware Monitoring capabilities, enhanced Security features, Power Control logic

and Motherboard Glue logic.

SCH3223 The SCH3223 incorporates Super I/O functionality including LPC bus interface, a Serialized IRQ interface

and the ISA Plug-and-Play standard register set (Version 1.0a). The I/O Address and hardware IRQ of each logical

device in the SCH3223 may be reprogrammed through the internal configuration registers. Related functionality offers

flexibility to the system designer, with General Purpose I/O control functions, and control of two LED's.

The SCH3223's Hardware Monitoring capability includes temperature, voltage and fan speed monitoring. It has the abil-

ity to alert the system of out-of-limit conditions and automatically control the speed of a fan via PWM and Tach pins.

There are four analog inputs for monitoring external voltages of +5V, +2.5V, +12V and Vccp (core processor voltage),

as well as internal monitoring of its VCC, VTR, and Vbat power supplies. The SCH3223 includes support for monitoring

one external temperature via thermal diode inputs and an internal sensor for measuring ambient temperature. The hard-

ware monitoring block of the SCH3223 is accessible via the LPC bus. Interrupt events can create PME wakeup events.

The Motherboard Glue logic includes various power management and system logic including generation of nRSMRST

and reset generation. The reset generation includes a watchdog timer which can be used to generate a reset pulse. The

width of this pulse is selectable via an external strapping option.

The two serial ports are fully functional NS16550 compatible UARTs that support data rates up to 1.5 Mbps. The Serial

Ports contain programmable direction control, which can automatically drive nRTS based on the status of the Output

Buffer.

The SCH3223 is ACPI 1.0/2.0 compatible and therefore supports multiple low power-down modes.

CAUTION: This device contains circuits which must not be used because their pins are not brought out of the package,

and are pulled to known states internally. Any features, and especially Logical Devices, that are not listed in this docu-

ment must not be activated or accessed. Doing so may cause unpredictable behavior and/or excessive currents, and

therefore may damage the device and/or the system.

1.1

Reference Documents

1.

Intel Low Pin Count Specification, Revision 1.0, September 29, 1997

2.

PCI Local Bus Specification, Revision 2.2, December 18, 1998

3.

Advanced Configuration and Power Interface Specification, Revision 1.0b, February 2, 1999

2015 Microchip Technology Inc.

DS00002028B-page 5

SCH3223

2.0

PIN LAYOUT

This is a 64-ball 6mm x 6mm package, with ball pitch of 0.5mm. However, the sparse 0.5mm pitch ball array allows

0.65mm trace routing rules. For a specific recommendation, see the drawing in

Section 27.0, "Package Outline," on

page 188

.

FIGURE 2-1:

SCH3223 64-BALL WFBGA FOOTPRINT DIAGRAM, TOP VIEW

SCH3223

DS00002028B-page 6

2015 Microchip Technology Inc.

2.1

SCH3223 Pin Layout Summary

TABLE 2-1:

SCH3223 SUMMARY

Ball#

Function (

Note 1

)

B1

+12V_IN

C1

+5V_IN

C2

VTR

D2

TEST=VSS

E2

VSS

E1

CLOCKI

E4

LAD0

F4

LAD1

G4

LAD2

G2

LAD3

G1

LFRAME#

H6

PCI_RESET#

H5

PCI_CLK

H2

SER_IRQ

J2

VSS

K3

VCC

J1

nIDE_RSTDRV / GP44

K2

nPCIRST1 / GP45

K1

nPCIRST2 / GP46

L2

nPCIRST3 / GP47

L3

AVSS

K4

VBAT

K5

GP27 / nIO_SMI

L5

VTR

L9

nRI1

L10

nDCD1

K11

RXD1

K7

TXD1

K8

nDSR1

K9

nRTS1 / SYSOPT0

K10

nCTS1

J10

nDTR1 / SYSOPT1

J11

GP50 / nRI2

H10

VTR

L7

VSS

H7

GP51 / nDCD2

G11

GP52 / RXD2

G10

GP53 / TXD2

G8

GP54 / nDSR2

F8

GP55 / nRTS2 / RESGEN

E8

GP56 / nCTS2

D6

GP57 / nDTR2

D7

PB_OUT#

2015 Microchip Technology Inc.

DS00002028B-page 7

SCH3223

Note 1:

Device ID register at Plug&Play Index 0x20 holds 0x7D.

2.2

Pin Functions

E10

PS_ON#

E11

PB_IN#

D10

SLP_SX#

C11

GP42 / nIO_PME

C10

GP61 / nLED2 / CLKO

B11

GP60 / nLED1 / WDT

A10

GP63

B10

CLKI32

A9

nRSMRST

B9

GP62

B8

PWRGD_OUT

B7

PWRGD_PS

A7

nFPRST / GP30

A5

PWM1

B5

FANTACH1

D5

HVSS

B4

HVTR

B3

REMOTE1-

A3

REMOTE1+

B2

VCCP_IN

A2

+2.5V_IN

TABLE 2-2:

SCH3223 PIN FUNCTIONS DESCRIPTION

Note

Name

Description

VCC

Power

Plane

VTR

Power

Plane

VCC=0

Operation

(

Note 2-10

)

Buffer

Modes

(

Note 2-1

)

POWER PINS

2-3

,

2-4

VCC

+3.3 Volt Supply Voltage

2-3

,

2-4

VTR

+3.3 Volt Standby Supply

Voltage

2-6

VBAT

+3.0 Volt Battery Supply

)

VSS

Ground

AVSS

Analog Ground

2-3

HVTR

Analog Power. +3.3V VTR

pin dedicated to the

Hardware Monitoring

block.

HVTR is powered

by +3.3V Standby power

VTR.

TABLE 2-1:

SCH3223 SUMMARY (CONTINUED)

Ball#

Function (

Note 1

)

SCH3223

DS00002028B-page 8

2015 Microchip Technology Inc.

2-3

HVSS

Analog Ground. Internally

connected to all of the

Hardware Monitoring Block

circuitry.

CLOCK PINS

CLKI32

32.768kHz Trickle Clock

Input

CLKI32

No Gate

IS

CLOCKI

14.318MHz Clock Input

CLOCKI

IS

LPC INTERFACE

LAD[3:0]

Multiplexed Command

Address and Data

LAD[3:0]

GATE/ Hi-Z

PCI_IO

LFRAME#

Frame signal. Indicates

start of new cycle and

termination of broken cycle

LFRAME#

GATE

PCI_I

PCI_RESET#

PCI Reset

PCI_RESET#

NO GATE

PCI_I

PCI_CLK

PCI Clock

PCI_CLK

GATE

PCI_ICLK

SER_IRQ

Serial IRQ

SER_IRQ

GATE / Hi-Z

PCI_IO

SERIAL PORT 1 INTERFACE

RXD1

Receive Data 1

RXD1

GATE

IS

TXD1

Transmit Data 1

TXD1

HI-Z

O12/O12

nDSR1

Data Set Ready 1

nDSR1

GATE

I

2-5

nRTS1 /

SYSOPT0

Request to Send 1/

SYSOPT (Configuration

Port Base Address Control)

nRTS1/

SYSOPT0

GATE/ Hi-Z

OP14 / I

nCTS1

Clear to Send 1

nCTS1

GATE

I

nDTR1 /

SYSOPT1

Data Terminal Ready 1

nDTR1 /

SYSOPT1

GATE/ Hi-Z

O6 / I

2-7

nRI1

Ring Indicator 1

nRI1

GATE

IS

nDCD1

Data Carrier Detect 1

nDCD1

GATE

I

SERIAL PORT 2 INTERFACE

2-7

GP50 / nRI2

Ring Indicator 2

GP50

nRI2

NO GATE/

HI-Z

(I/OD8/OD8) /

IS

2-7

GP51 / nDCD2

Data Carrier Detect 2

GP51 /

nDCD2

NO GATE/

HI-Z

(I/OD8/OD8) /

I

2-7

GP52 / RXD2

Receive Data 2

GP52 / RXD2

NO GATE/

HI-Z

(I/OD8OD8) /

IS

2-9

,

2-7

GP53 / TXD2

Transmit Data 2

GP53 / TXD2

NO GATE/

HI-Z

(I/O12/OD12)

/ (O12/OD12)

2-7

GP54 / nDSR2

Data Set Ready 2

GP54 /

nDSR2

NO GATE/

HI-Z

(I/OD8/OD8) /

I

2-7

2-11

GP55 / nRTS2 /

RESGEN

Request to Send 2 /

Reset Generator Pulse

Width Strap Option

GP55 / nRTS2

/

RESGEN

NO GATE/

HI-Z

(I/O8/OD8) / I

/ IOP8

2-7

GP56 / nCTS2

Clear to Send 2

GP56 / nCTS2

NO GATE/

HI-Z

(I/OD8OD8) /

I

2-7

GP57 / nDTR2

Data Terminal Ready 2

GP57 / nDTR2

NO GATE/

HI-Z

(I/OD8OD8) /

O6

TABLE 2-2:

SCH3223 PIN FUNCTIONS DESCRIPTION (CONTINUED)

Note

Name

Description

VCC

Power

Plane

VTR

Power

Plane

VCC=0

Operation

(

Note 2-10

)

Buffer

Modes

(

Note 2-1

)

2015 Microchip Technology Inc.

DS00002028B-page 9

SCH3223

MISCELLANEOUS PINS

GP42/

nIO_PME

General Purpose I/O.

Power Management Event

Output. This active low

Power Management Event

signal allows this device to

request wake-up in either

S3 or S5 and below.

GP42/

nIO_PME

NO GATE

(I/O12/OD12)

/(O12/OD12)

2-6

,

2-7

GP60

/nLED1

/WDT

General Purpose I/O

/nLED1

Watchdog Timer Output

GP60

/nLED1

/WDT

NO GATE

(I/O12/OD12)

/(O12/OD12)

/(O12/OD12)

nFPRST /

GP30

Front Panel Reset /

General Purpose IO

nFPRST /

GP30

NO GATE

ISPU_400 /

(I/O4/OD4)

PWRGD_PS

Power Good Input from

Power Supply

PWRGD_P

S

NO GATE

ISPU_400

PWRGD_OUT

Power Good Output –

Open Drain

PWRGD_

OUT

NO GATE

OD8

nRSMRST

Resume Reset Output

nRSMRST

NO GATE

OD24

2-6

,

2-7

GP61

/nLED2 /

CLKO

General Purpose I/O

/nLED2

/ Programmable Clock

Output

GP61

/nLED2 /

CLKO

NO GATE

(I/O12/OD12)

/ (O12/OD12)

/ (O12/OD12)

2-7

GP27 /nIO_SMI

General Purpose I/O

/System Mgt. Interrupt

GP27

/nIO_SMI

GP27

/

HI-Z

(I/O12/OD12)

/(O12/OD12)

TEST

Test purposes. Customer

should tie this pin to VSS at

all times.

TEST

TEST

HARDWARE MONITORING BLOCK

2-8

+5V_IN

Analog input for +5V

HVTR

I

AN

2-8

+2.5_IN

Analog input for +2.5V

HVTR

I

AN

2-8

VCCP_IN

Analog input for +Vccp

(processor voltage: 1.5 V

nominal).

HVTR

I

AN

2-8

+12V_IN

Analog input for +12V

HVTR

I

AN

REMOTE1-

This is the negative input

(current sink) from the

remote thermal diode 1.

HVTR

I

AND-

REMOTE1+

This is the positive input

(current source) from the

remote thermal diode 1.

HVTR

I

AND+

PWM1

Fan Speed Control 1

Output.

PWM1 OD8

FANTACH1

Tachometer Input 1 for

monitoring a fan.

FANTACH

1

I

M

RESET OUTPUTS

nPCIRST3 /

GP47

PCI Reset output 3

GPIO with Schmitt trigger

input

nPCIRST3

GP47

NO GATE

(O4/OD4) /

(IS/O4/OD4)

nPCIRST2 /

GP46

PCI Reset output 2

GPIO with Schmitt trigger

input

nPCIRST2

GP46

NO GATE

(O8/OD8) /

(IS/O8/OD8)

TABLE 2-2:

SCH3223 PIN FUNCTIONS DESCRIPTION (CONTINUED)

Note

Name

Description

VCC

Power

Plane

VTR

Power

Plane

VCC=0

Operation

(

Note 2-10

)

Buffer

Modes

(

Note 2-1

)

SCH3223

DS00002028B-page 10

2015 Microchip Technology Inc.

Note 2-1

Buffer types per function on multiplexed pins are separated by a slash “/”. Buffer types in parenthesis

represent multiple buffer types for a single pin function.

Note 2-2

Pins that have input buffers must always be held to either a logical low or a logical high state when

powered. Bi-directional buses that may be trisected should have either weak external pull-ups or pull-

downs to hold the pins in a logic state (i.e., logic states are VCC or ground).

Note 2-3

VCC and VSS pins are for Super I/O Blocks. HVTR and HVSS are dedicated for the Hardware

Monitoring Block.

Note 2-4

VTR can be connected to VCC if no wake-up functionality is required.

Note 2-5

The nRTS1/SYSOPT0 pin requires an external pull-down resistor to put the base I/O address for

configuration at 0x02E. An external pull-up resistor is required to move the base I/O address for

configuration to 0x04E.

Note 2-6

The LED pins are powered by VTR so that the LEDs can be controlled when the part is under VTR

power.

Note 2-7

This pin is an input into the wake-up logic that is powered by VTR. In the case of a ring indicator for

a serial port, or a GPIO it will also go to VCC powered logic. This logic must be disabled when

VCC=0.

Note 2-8

This analog input is backdrive protected.

Although HVTR is powered by VTR, it is possible that

monitored power supplies may be powered when HVTR is off.

Note 2-9

The GP53/TXD2 pin defaults to the GPIO input function on a VTR POR and presents a tristate

impedance. When VCC=0 the pin is tristate. If GP53 function is selected and VCC is power is applied,

the pin reflects the current state of GP53. The GP53/TXD2 pin is tristate when it is configured for the

TXD2 function.

Note 2-10

All logic is powered by VTR. Vcc on pin 29 is used as an indication of the presence of the VCC rail

being active. All logic that requires VCC power, is only enabled when the VCC rail is active.

Note 2-11

The GP55/nRTS2/RESGEN pin requires an external pull-down resistor to enable 500ms delay circuit.

An external pull-up resistor is required to enable 200ms delay circuit.

nPCIRST1 /

GP45

PCI Reset output 1

GPIO with Schmitt trigger

input

nPCIRST1

GP45

NO GATE

(O8/OD8) /

(IS/O8/OD8)

nIDE_RSTDRV /

GP44

IDE Reset output

GPIO with Schmitt trigger

input

nIDE_RSTDR

V

GP44

NO GATE

(O4/OD4) /

(IS/O4/OD4)

GLUE LOGIC

PB_IN#

Power Button In is used to

detect a power button

event

PB_IN# NO

GATE

I

2-7

SLP_SX#

Sx Sleep State Input Pin.

SLP_SX#

NO GATE

I

PB_OUT# Power

Button

Out

PB_OUT# NO

GATE

O8

PS_ON#

Power supply On

PS_ON#

NO GATE

O12

DEDICATED GPIO

2-7

GP62*

GPIO with I_VID buffer

Input

GP62* NO

GATE

(I/O8/OD8)

2-7

GP63*

GPIO with I_VID buffer

Input

GP63* NO

GATE

(I/O8/OD8)

TABLE 2-2:

SCH3223 PIN FUNCTIONS DESCRIPTION (CONTINUED)

Note

Name

Description

VCC

Power

Plane

VTR

Power

Plane

VCC=0

Operation

(

Note 2-10

)

Buffer

Modes

(

Note 2-1

)