1998-2011 Microchip Technology Inc.

DS21290F-page 1

MCP3201

Features

• 12-Bit Resolution

• ±1 LSB max DNL

• ±1 LSB max INL (MCP3201-B)

• ±2 LSB max INL (MCP3201-C)

• On-chip Sample and Hold

• SPI Serial Interface (modes 0,0 and 1,1)

• Single Supply Operation: 2.7V - 5.5V

• 100 ksps Maximum Sampling Rate at V

DD

= 5V

• 50 ksps Maximum Sampling Rate at V

DD

= 2.7V

• Low-Power CMOS Technology

• 500 nA Typical Standby Current, 2 µA Maximum

• 400 µA Maximum Active Current at 5V

• Industrial Temp Range: -40°C to +85°C

• 8-pin MSOP, PDIP, SOIC and TSSOP Packages

Applications

• Sensor Interface

• Process Control

• Data Acquisition

• Battery Operated Systems

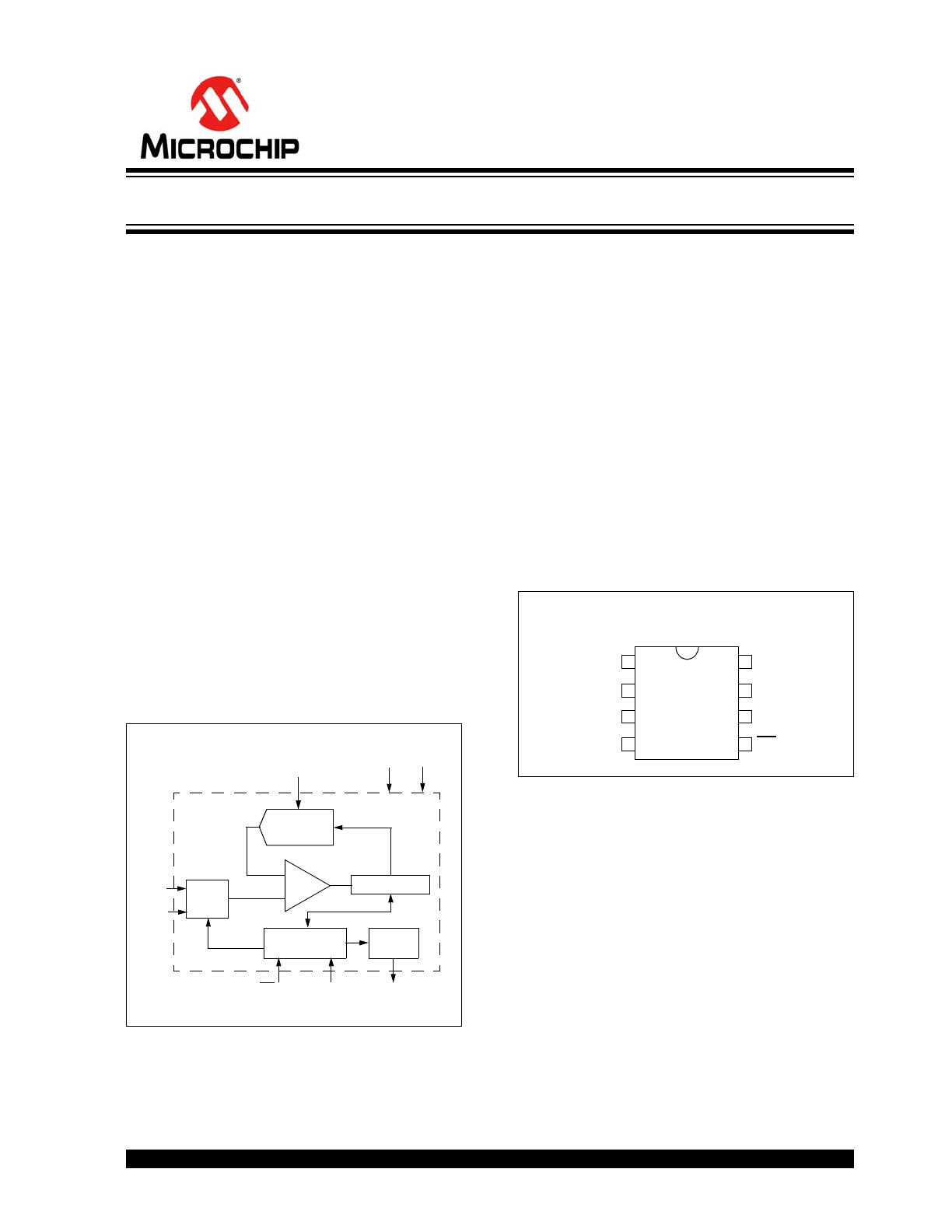

Functional Block Diagram

Description

The Microchip Technology Inc. MCP3201 device is a

successive approximation 12-bit Analog-to-Digital

(A/D) Converter with on-board sample and hold

circuitry. The device provides a single pseudo-differen-

tial input. Differential Nonlinearity (DNL) is specified at

±1 LSB, and Integral Nonlinearity (INL) is offered in

±1 LSB (MCP3201-B) and ±2 LSB (MCP3201-C)

versions. Communication with the device is done using

a simple serial interface compatible with the SPI

protocol. The device is capable of sample rates of up to

100 ksps at a clock rate of 1.6 MHz. The MCP3201

device operates over a broad voltage range (2.7V-

5.5V). Low-current design permits operation with

typical standby and active currents of only 500 nA and

300 µA, respectively. The device is offered in 8-pin

MSOP, PDIP, TSSOP and 150 mil SOIC packages.

Package Types

Comparator

Sample

and

Hold

12-Bit SAR

DAC

Control Logic

CS/SHDN

V

REF

IN+

IN-

V

SS

V

DD

CLK

D

OUT

Shift

Register

V

REF

IN+

IN–

V

SS

V

DD

CLK

D

OUT

CS/SHDN

1

2

3

4

8

7

6

5

MSOP, PDIP, SOIC, TSSOP

MCP

3

20

1

2.7V 12-Bit A/D Converter with SPI Serial Interface

MCP3201

DS21290F-page 2

1998-2011 Microchip Technology Inc.

NOTES:

1998-2011 Microchip Technology Inc.

DS21290F-page 3

MCP3201

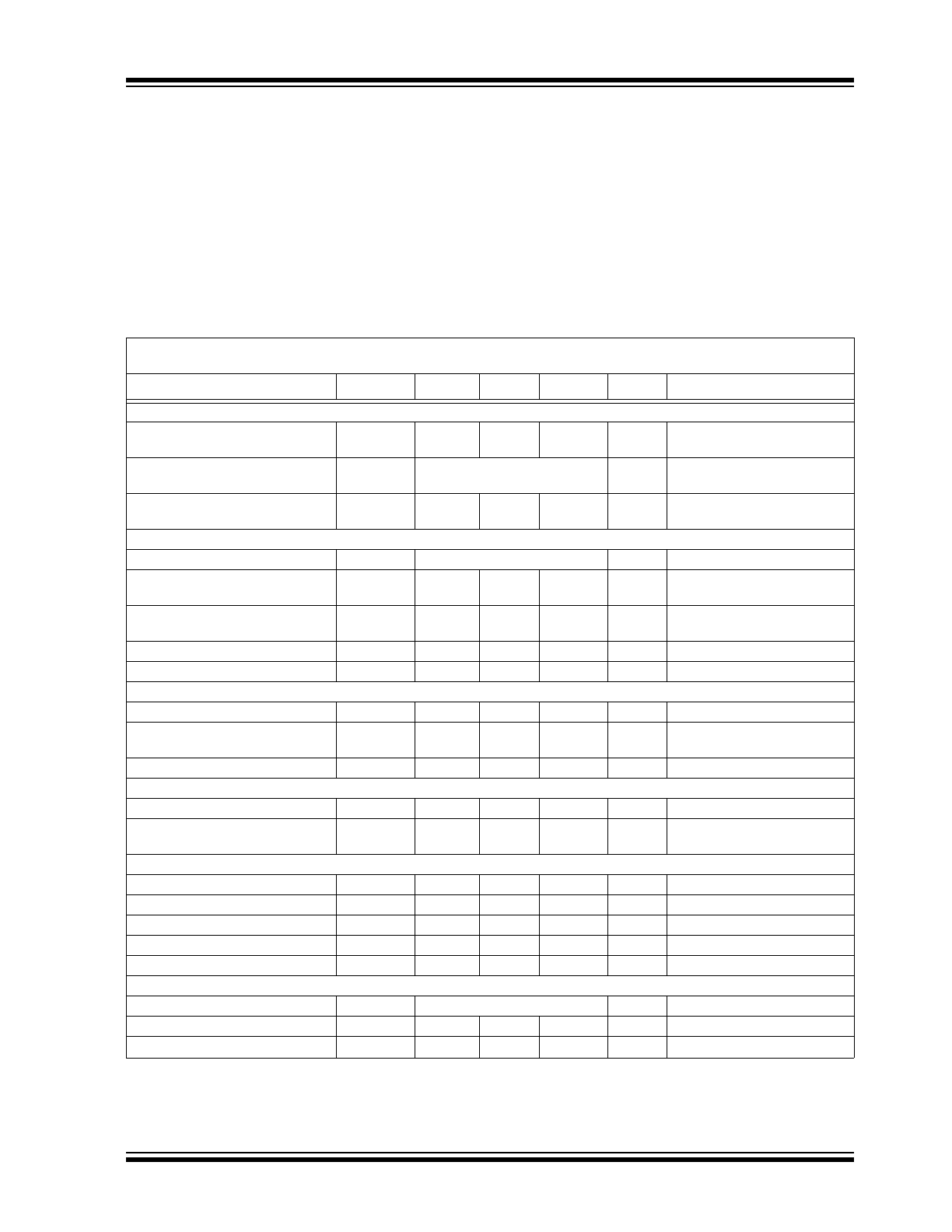

1.0

ELECTRICAL

CHARACTERISTICS

1.1

Maximum Ratings†

V

DD

...................................................................................7.0V

All inputs and outputs w.r.t. V

SS

................ -0.6V to V

DD

+0.6V

Storage temperature .....................................-65°C to +150°C

Ambient temp. with power applied ................-65°C to +125°C

ESD protection on all pins (HBM) .................................> 4 kV

†Notice:

Stresses above those listed under “Maximum

ratings” may cause permanent damage to the device. This is

a stress rating only and functional operation of the device at

those or any other conditions above those indicated in the

operational listings of this specification is not implied.

Exposure to maximum rating conditions for extended periods

may affect device reliability.

ELECTRICAL CHARACTERISTICS

Electrical Specifications:

All parameters apply at V

DD

= 5V, V

SS

= 0V, V

REF

= 5V, T

A

= -40°C to +85°C, f

SAMPLE

= 100 ksps, and

fCLK = 16*f

SAMPLE

, unless otherwise noted.

Parameter

Sym

Min

Typ

Max

Units

Conditions

Conversion Rate:

Conversion Time

t

CONV

—

—

12

clock

cycles

Analog Input Sample Time

t

SAMPLE

1.5

clock

cycles

Throughput Rate

f

SAMPLE

—

—

100

50

ksps

ksps

V

DD

= V

REF

= 5V

V

DD

= V

REF

= 2.7V

DC Accuracy:

Resolution

12

bits

Integral Nonlinearity

INL

—

—

±0.75

±1

±1

±2

LSB

LSB

MCP3201-B

MCP3201-C

Differential Nonlinearity

DNL

—

±0.5

±1

LSB

No missing codes over

temperature

Offset Error

—

±1.25

±3

LSB

Gain Error

—

±1.25

±5

LSB

Dynamic Performance:

Total Harmonic Distortion

THD

—

-82

—

dB

V

IN

= 0.1V to 4.9V@1 kHz

Signal to Noise and Distortion

(SINAD)

SINAD

—

72

—

dB

V

IN

= 0.1V to 4.9V@1 kHz

Spurious Free Dynamic Range

SFDR

—

86

—

dB

V

IN

= 0.1V to 4.9V@1 kHz

Reference Input:

Voltage Range

0.25

—

V

DD

V

Note 2

Current Drain

—

—

100

.001

150

3

µA

µA

CS = V

DD

= 5V

Analog Inputs:

Input Voltage Range (IN+)

IN+

IN-

—

V

REF

+IN-

V

Input Voltage Range (IN-)

IN-

V

SS

-100

V

SS

+100

mV

Leakage Current

—

0.001

±1

µA

Switch Resistance

R

SS

—

1K

—

W

See

Figure 4-1

Sample Capacitor

C

SAMPLE

—

20

—

pF

See

Figure 4-1

Digital Input/Output:

Data Coding Format

Straight Binary

High Level Input Voltage

V

IH

0.7 V

DD

—

—

V

Low Level Input Voltage

V

IL

—

—

0.3 V

DD

V

Note 1:

This parameter is established by characterization and not 100% tested.

2:

See graph that relates linearity performance to V

REF

level.

3:

Because the sample cap will eventually lose charge, effective clock rates below 10 kHz can affect linearity performance,

especially at elevated temperatures. See

Section 6.2 “Maintaining Minimum Clock Speed”

for more information.

MCP3201

DS21290F-page 4

1998-2011 Microchip Technology Inc.

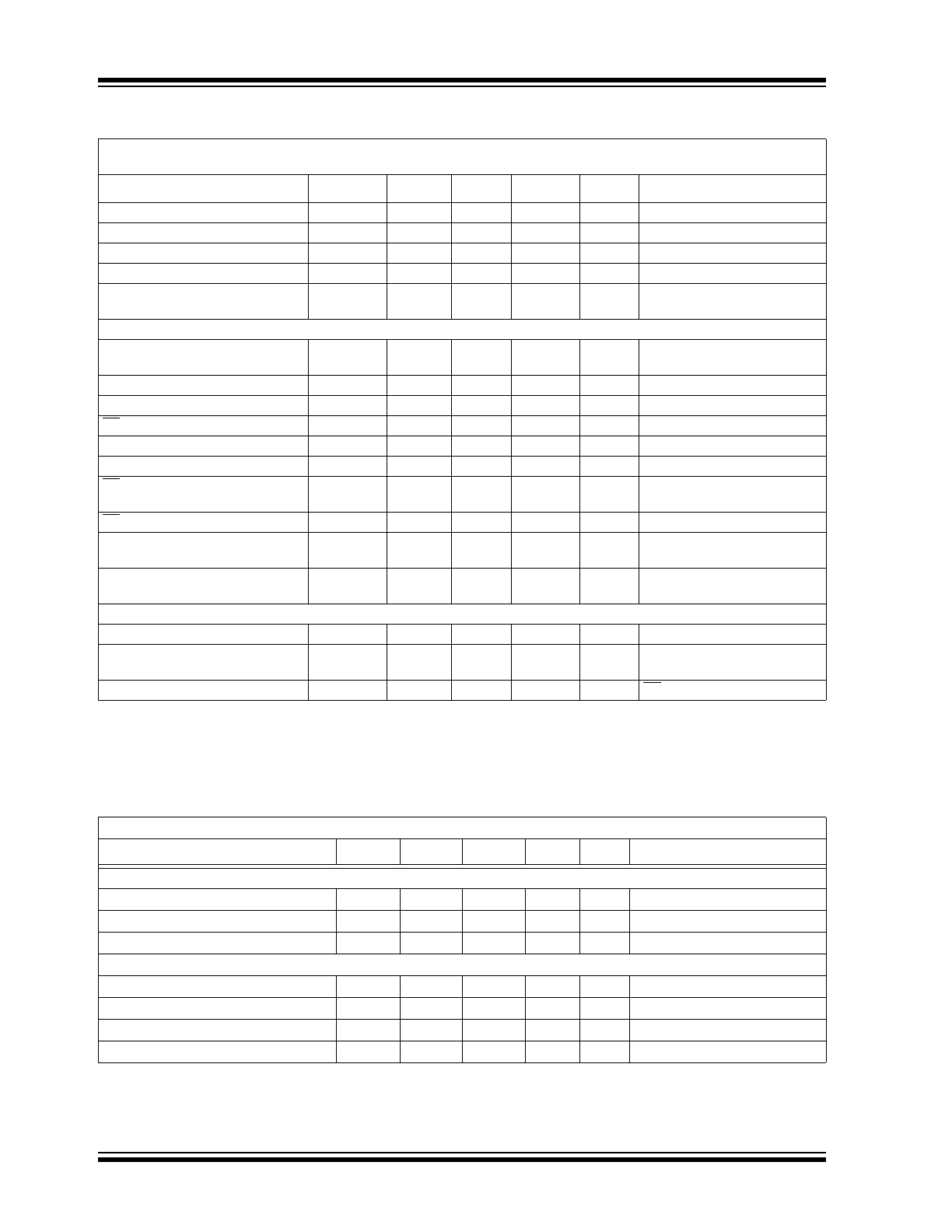

TEMPERATURE CHARACTERISTICS

High Level Output Voltage

V

OH

4.1

—

—

V

I

OH

= -1 mA, V

DD

= 4.5V

Low Level Output Voltage

V

OL

—

—

0.4

V

I

OL

= 1 mA, V

DD

= 4.5V

Input Leakage Current

I

LI

-10

—

10

µA

V

IN

= V

SS

or V

DD

Output Leakage Current

I

LO

-10

—

10

µA

V

OUT

= V

SS

or V

DD

Pin Capacitance

(all inputs/outputs)

C

IN

, C

OUT

—

—

10

pF

V

DD

= 5.0V (

Note 1

)

T

A

= +25°C, f = 1 MHz

Timing Parameters:

Clock Frequency

f

CLK

—

—

—

—

1.6

0.8

MHz

MHz

V

DD

= 5V (

Note 3

)

V

DD

= 2.7V (

Note 3

)

Clock High Time

t

HI

312

—

—

ns

Clock Low Time

t

LO

312

—

—

ns

CS Fall To First Rising CLK Edge

t

SUCS

100

—

—

ns

CLK Fall To Output Data Valid

t

DO

—

—

200

ns

See Test Circuits,

Figure 1-2

CLK Fall To Output Enable

t

EN

—

—

200

ns

See Test Circuits,

Figure 1-2

CS Rise To Output Disable

t

DIS

—

—

100

ns

See Test Circuits,

Figure 1-2

(

Note 1

)

CS Disable Time

t

CSH

625

—

—

ns

D

OUT

Rise Time

t

R

—

—

100

ns

See Test Circuits,

Figure 1-2

(

Note 1

)

D

OUT

Fall Time

t

F

—

—

100

ns

See Test Circuits,

Figure 1-2

(

Note 1

)

Power Requirements:

Operating Voltage

V

DD

2.7

—

5.5

V

Operating Current

I

DD

—

—

300

210

400

—

µA

µA

V

DD

= 5.0V, D

OUT

unloaded

V

DD

= 2.7V, D

OUT

unloaded

Standby Current

I

DDS

—

0.5

2

µA

CS = V

DD

= 5.0V

Electrical Specifications:

Unless otherwise indicated, V

DD

= +2.7V to +5.5V, V

SS

= GND.

Parameters

Sym

Min

Typ

Max

Units

Conditions

Temperature Ranges

Specified Temperature Range

T

A

-40

—

+85

°C

Operating Temperature Range

T

A

-40

—

+85

°C

Storage Temperature Range

T

A

-65

—

+150

°C

Thermal Package Resistances

Thermal Resistance, 8L-MSOP

JA

—

211

—

°C/W

Thermal Resistance, 8L-PDIP

JA

—

89.5

—

°C/W

Thermal Resistance, 8L-SOIC

JA

—

149.5

—

°C/W

Thermal Resistance, 8L-TSSOP

JA

—

139

—

°C/W

ELECTRICAL CHARACTERISTICS (CONTINUED)

Electrical Specifications:

All parameters apply at V

DD

= 5V, V

SS

= 0V, V

REF

= 5V, T

A

= -40°C to +85°C, f

SAMPLE

= 100 ksps, and

fCLK = 16*f

SAMPLE

, unless otherwise noted.

Parameter

Sym

Min

Typ

Max

Units

Conditions

Note 1:

This parameter is established by characterization and not 100% tested.

2:

See graph that relates linearity performance to V

REF

level.

3:

Because the sample cap will eventually lose charge, effective clock rates below 10 kHz can affect linearity performance,

especially at elevated temperatures. See

Section 6.2 “Maintaining Minimum Clock Speed”

for more information.

1998-2011 Microchip Technology Inc.

DS21290F-page 5

MCP3201

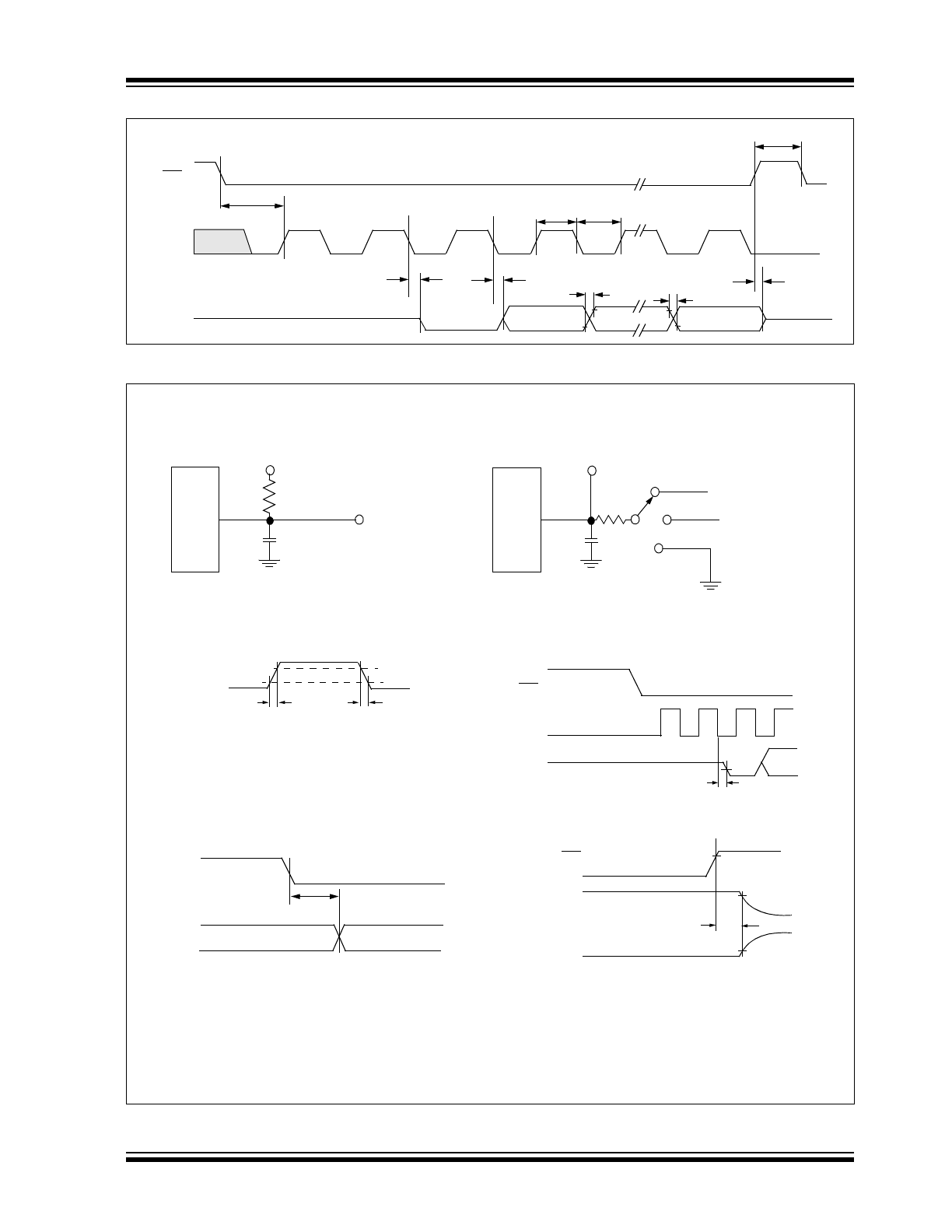

FIGURE 1-1:

Serial Timing.

FIGURE 1-2:

Test Circuits.

CS

CLK

t

SUCS

t

CSH

t

HI

t

LO

D

OUT

t

EN

t

DO

t

R

t

F

LSB

MSB OUT

t

DIS

NULL BIT

HI-Z

HI-Z

V

IH

t

DIS

CS

D

OUT

Waveform 1*

D

OUT

Waveform 2†

90%

10%

* Waveform 1 is for an output with internal condi-

tions such that the output is high, unless disabled

by the output control.

† Waveform 2 is for an output with internal condi-

tions such that the output is low, unless disabled

by the output control.

Voltage Waveforms for t

DIS

Test Point

1.4V

D

OUT

Load circuit for t

R

, t

F

, t

DO

3 kΩ

C

L

= 30 pF

Test Point

D

OUT

Load circuit for t

DIS

and t

EN

3 kΩ

30 pF

t

DIS

Waveform 2

t

DIS

Waveform 1

CS

CLK

D

OUT

t

EN

1

2

B9

Voltage Waveforms for t

EN

t

EN

Waveform

V

DD

V

DD

/2

V

SS

3

4

D

OUT

t

R

Voltage Waveforms for t

R

, t

F

CLK

D

OUT

t

DO

Voltage Waveforms for t

DO

t

F

V

OH

V

OL

MCP3201

DS21290F-page 6

1998-2011 Microchip Technology Inc.

NOTES:

1998-2011 Microchip Technology Inc.

DS21290F-page 7

MCP3201

2.0

TYPICAL PERFORMANCE CHARACTERISTICS

Note:

Unless otherwise indicated, V

DD

= V

REF

= 5V, V

SS

= 0V, f

SAMPLE

= 100 ksps, f

CLK

= 16*f

SAMPLE

, T

A

= +25°C.

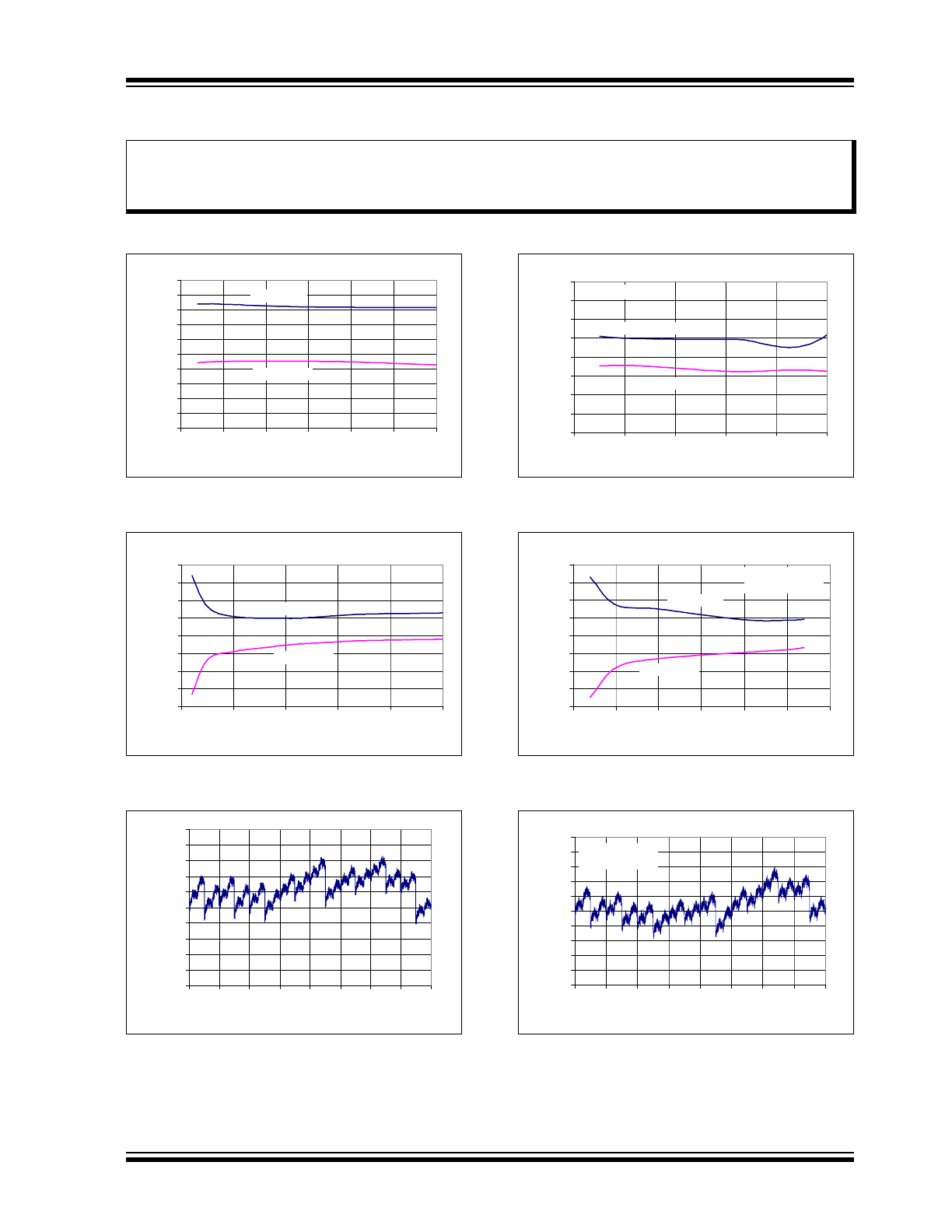

FIGURE 2-1:

Integral Nonlinearity (INL)

vs. Sample Rate.

FIGURE 2-2:

Integral Nonlinearity (INL)

vs. V

REF

.

FIGURE 2-3:

Integral Nonlinearity (INL)

vs. Code (Representative Part).

FIGURE 2-4:

Integral Nonlinearity (INL)

vs. Sample Rate (V

DD

= 2.7V).

FIGURE 2-5:

Integral Nonlinearity (INL)

vs. V

REF

(V

DD

= 2.7V).

FIGURE 2-6:

Integral Nonlinearity (INL)

vs. Code (Representative Part, V

DD

= 2.7V).

Note:

The graphs provided following this note are a statistical summary based on a limited number of samples

and are provided for informational purposes only. The performance characteristics listed herein are not

tested or guaranteed. In some graphs, the data presented may be outside the specified operating range

(e.g., outside specified power supply range) and therefore outside the warranted range.

-1.0

-0.8

-0.6

-0.4

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

0

25

50

75

100

125

150

Sample Rate (ksps)

IN

L

(

L

S

B

)

Positive INL

Negative INL

-2.0

-1.5

-1.0

-0.5

0.0

0.5

1.0

1.5

2.0

0

1

2

3

4

5

V

REF

(V)

IN

L

(L

S

B

)

Positive INL

Negative INL

-1.0

-0.8

-0.6

-0.4

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

0

512

1024 1536 2048 2560 3072 3584 4096

Digital Code

INL (

L

S

B

)

-2.0

-1.5

-1.0

-0.5

0.0

0.5

1.0

1.5

2.0

0

20

40

60

80

100

Sample Rate (ksps)

INL

(

L

S

B

)

V

DD

= V

REF

= 2.7V

Positive INL

Negative INL

-2.0

-1.5

-1.0

-0.5

0.0

0.5

1.0

1.5

2.0

0.0

0.5

1.0

1.5

2.0

2.5

3.0

V

REF

(V)

IN

L

(

L

S

B

)

Positive INL

Negative INL

V

DD

= 2.7V

F

SAMPLE

= 50 ksps

-1.0

-0.8

-0.6

-0.4

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

0

512 1024 1536 2048 2560 3072 3584 4096

Digital Code

IN

L

(

L

S

B

)

V

DD

= V

REF

= 2.7V

F

SAMPLE

= 50 ksps

MCP3201

DS21290F-page 8

1998-2011 Microchip Technology Inc.

Note:

Unless otherwise indicated, V

DD

= V

REF

= 5V, V

SS

= 0V, f

SAMPLE

= 100 ksps, f

CLK

= 16*f

SAMPLE

, T

A

= +25°C.

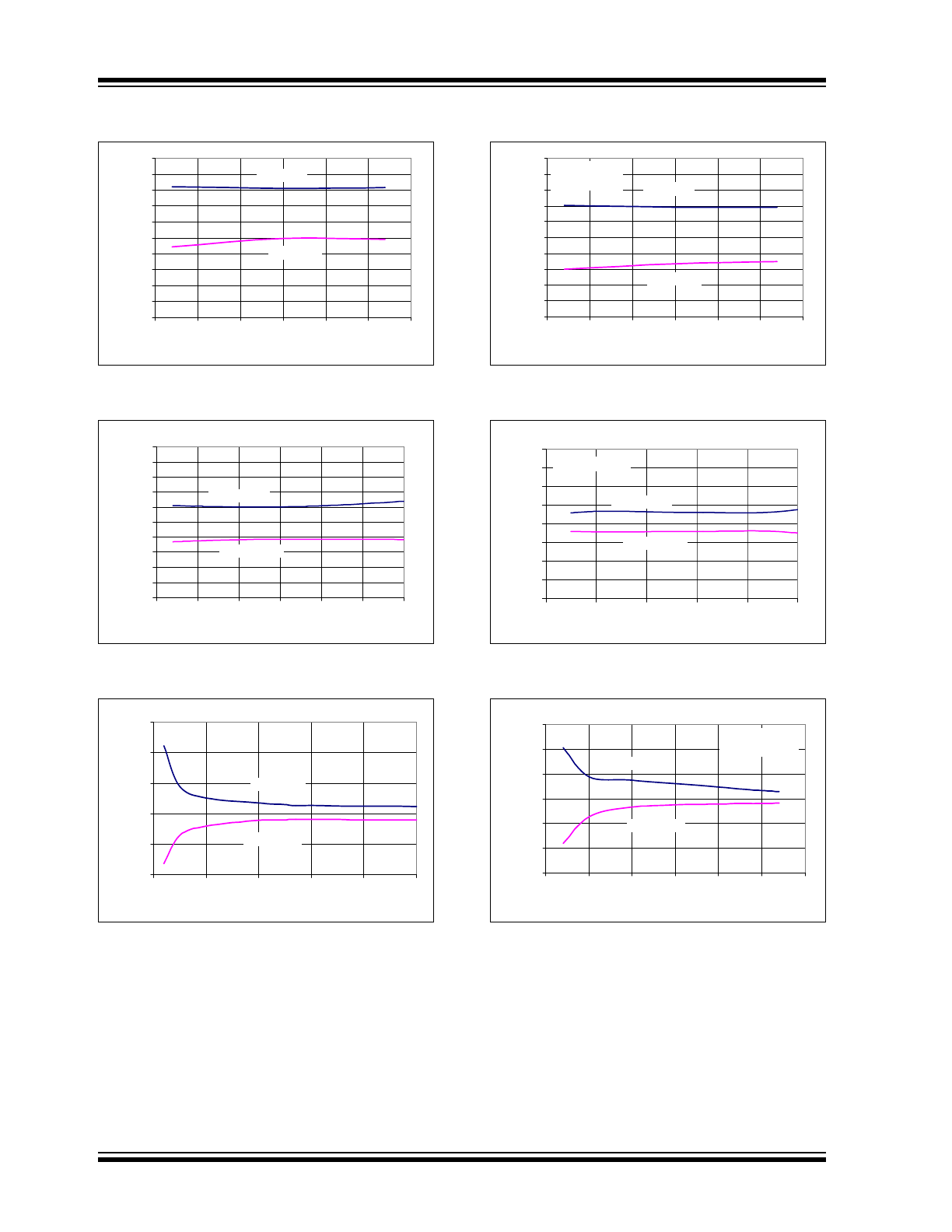

FIGURE 2-7:

Integral Nonlinearity (INL)

vs. Temperature.

FIGURE 2-8:

Differential Nonlinearity

(DNL) vs. Sample Rate.

FIGURE 2-9:

Differential Nonlinearity

(DNL) vs. V

REF

.

FIGURE 2-10:

Integral Nonlinearity (INL)

vs. Temperature (V

DD

= 2.7V).

FIGURE 2-11:

Differential Nonlinearity

(DNL) vs. Sample Rate (V

DD

= 2.7V).

FIGURE 2-12:

Differential Nonlinearity

(DNL) vs. V

REF

(V

DD

= 2.7V).

-1.0

-0.8

-0.6

-0.4

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

-50

-25

0

25

50

75

100

Temperature (°C)

IN

L

(

L

S

B

)

Positive INL

Negative INL

-1.0

-0.8

-0.6

-0.4

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

0

25

50

75

100

125

150

Sample Rate (ksps)

DNL

(

L

S

B

)

Positive DNL

Negative DNL

-2.0

-1.0

0.0

1.0

2.0

3.0

0

1

2

3

4

5

V

REF

(V)

DN

L (LS

B

)

Negative DNL

Positive DNL

-1.0

-0.8

-0.6

-0.4

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

-50

-25

0

25

50

75

100

Temperature (°C)

IN

L

(

L

S

B

)

Positive INL

V

DD

= V

REF

= 2.7V

F

SAMPLE

= 50 ksps

Negative INL

-2.0

-1.5

-1.0

-0.5

0.0

0.5

1.0

1.5

2.0

0

20

40

60

80

100

Sample Rate (ksps)

DNL

(

L

S

B

)

V

DD

= V

REF

= 2.7V

Positive DNL

Negative DNL

-3.0

-2.0

-1.0

0.0

1.0

2.0

3.0

0.0

0.5

1.0

1.5

2.0

2.5

3.0

V

REF

(V)

DNL (

L

S

B

)

Positive DNL

Negative DNL

V

DD

= 2.7V

F

SAMPLE

= 50 ksps

1998-2011 Microchip Technology Inc.

DS21290F-page 9

MCP3201

Note:

Unless otherwise indicated, V

DD

= V

REF

= 5V, V

SS

= 0V, f

SAMPLE

= 100 ksps, f

CLK

= 16*f

SAMPLE

, T

A

= +25°C.

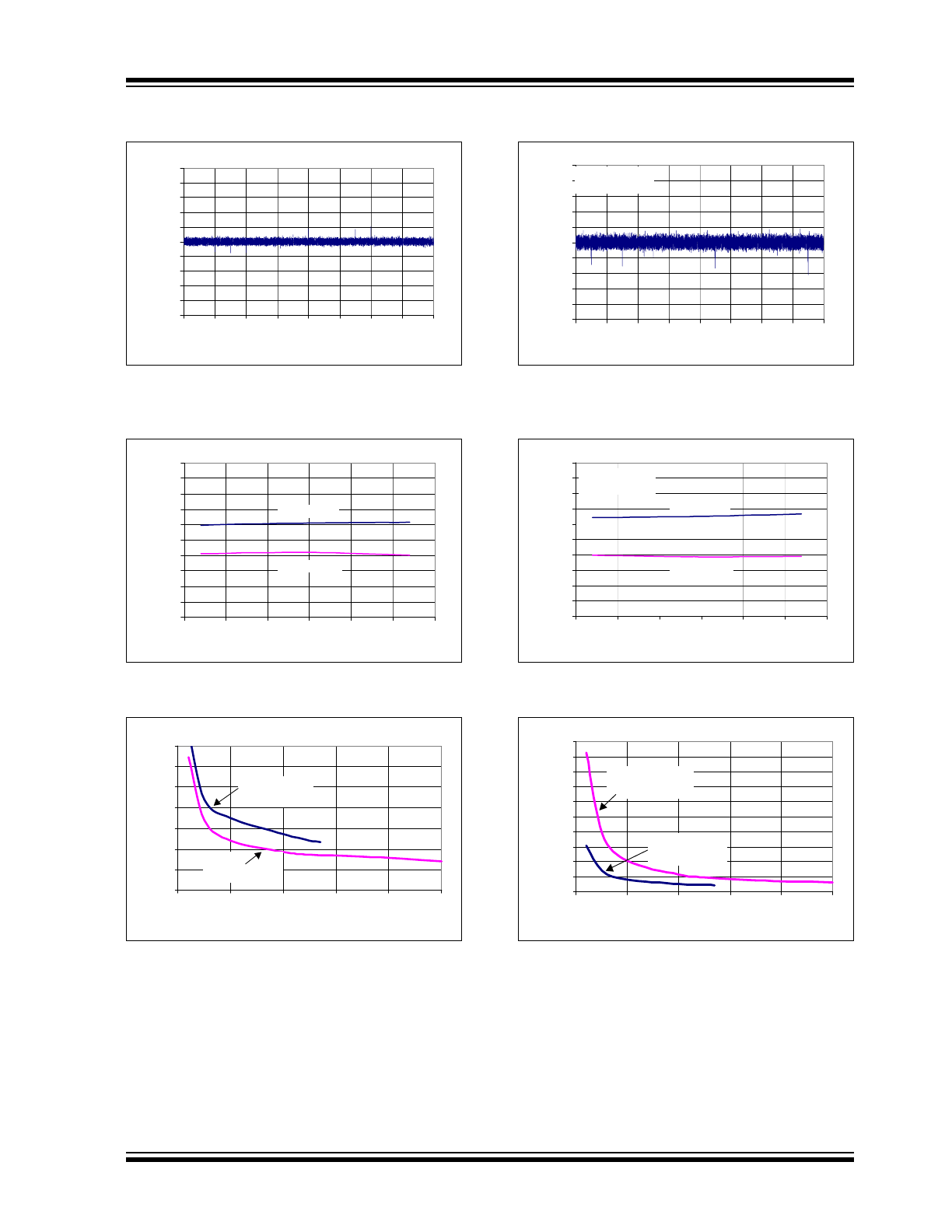

FIGURE 2-13:

Differential Nonlinearity

(DNL) vs. Code (Representative Part).

FIGURE 2-14:

Differential Nonlinearity

(DNL) vs. Temperature.

FIGURE 2-15:

Gain Error vs. V

REF

.

FIGURE 2-16:

Differential Nonlinearity

(DNL) vs. Code (Representative Part,

V

DD

= 2.7V).

FIGURE 2-17:

Differential Nonlinearity

(DNL) vs. Temperature (V

DD

= 2.7V).

FIGURE 2-18:

Offset Error vs. V

REF

.

-1.0

-0.8

-0.6

-0.4

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

0

512

1024 1536 2048 2560 3072 3584 4096

Digital Code

DN

L

(

L

S

B

)

-1.0

-0.8

-0.6

-0.4

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

-50

-25

0

25

50

75

100

Temperature (°C)

DNL

(

L

S

B

)

Positive DNL

Negative DNL

-2

-1

0

1

2

3

4

5

0

1

2

3

4

5

V

REF

(V)

Ga

in

Erro

r (L

SB)

V

DD

= 2.7V

F

SAMPLE

= 50 ksps

V

DD

= 5V

F

SAMPLE

= 100 ksps

-1.0

-0.8

-0.6

-0.4

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

0

512 1024 1536 2048 2560 3072 3584 4096

Digital Code

DN

L

(

L

S

B

)

V

DD

= V

REF

= 2.7V

F

SAMPLE

= 50 ksps

-1.0

-0.8

-0.6

-0.4

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

-50

-25

0

25

50

75

100

Temperature (°C)

DNL

(

L

S

B

)

Positive DNL

V

DD

= 2.7V

F

SAMPLE

= 50ksps

Negative DNL

0

2

4

6

8

10

12

14

16

18

20

0

1

2

3

4

5

V

REF

(V)

Of

fs

e

t Error (

L

SB

)

V

DD

= 5V

F

SAMPLE

= 100 ksps

V

DD

= 2.7V

F

SAMPLE

= 50ksps

MCP3201

DS21290F-page 10

1998-2011 Microchip Technology Inc.

Note:

Unless otherwise indicated, V

DD

= V

REF

= 5V, V

SS

= 0V, f

SAMPLE

= 100 ksps, f

CLK

= 16*f

SAMPLE

, T

A

= +25°C.

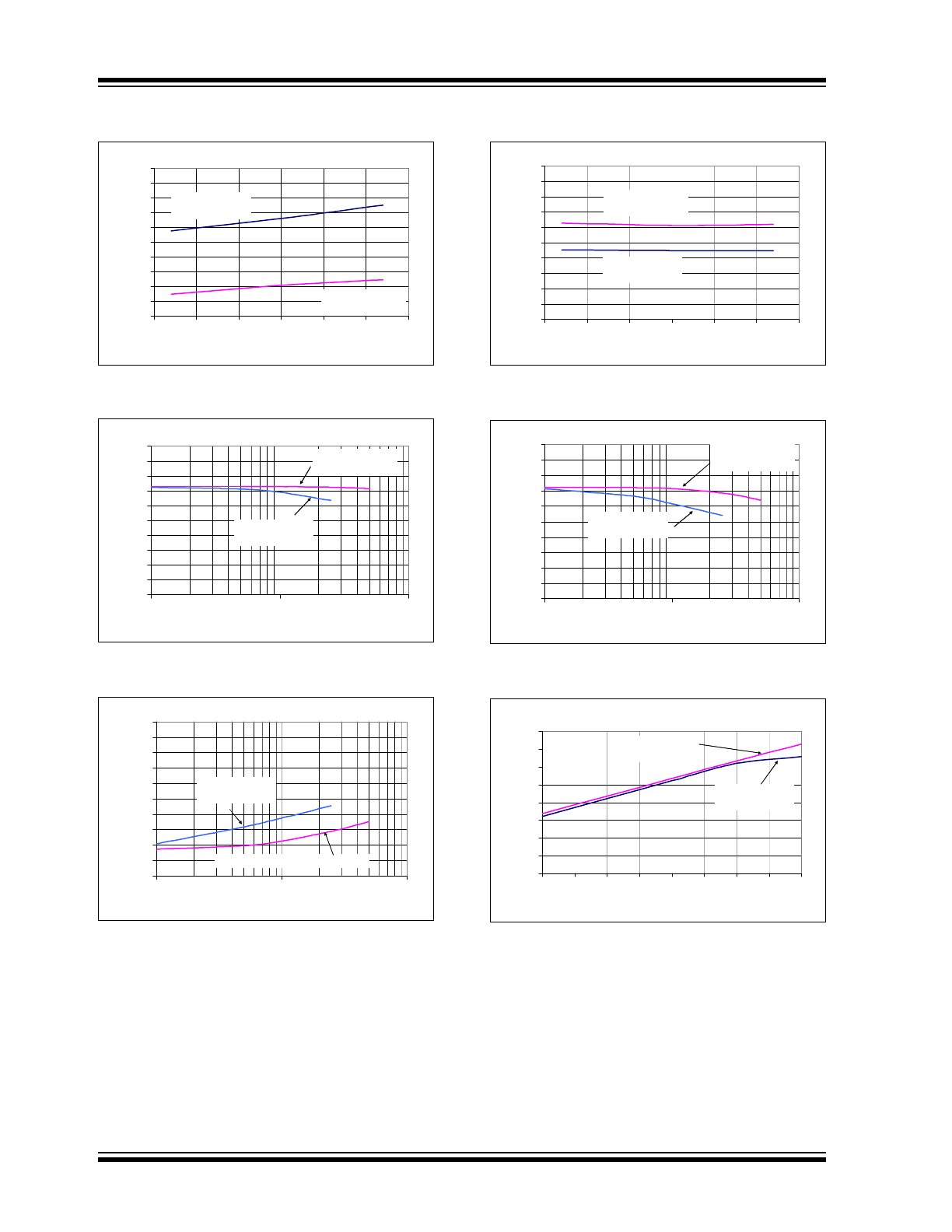

FIGURE 2-19:

Gain Error vs. Temperature.

FIGURE 2-20:

Signal-to-Noise Ratio (SNR)

vs. Input Frequency.

FIGURE 2-21:

Total Harmonic Distortion

(THD) vs. Input Frequency.

FIGURE 2-22:

Offset Error vs.

Temperature.

FIGURE 2-23:

Signal-to-Noise and

Distortion (SINAD) vs. Input Frequency.

FIGURE 2-24:

Signal-to-Noise and

Distortion (SINAD) vs. Input Signal Level.

-1.0

-0.8

-0.6

-0.4

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

-50

-25

0

25

50

75

100

Temperature (°C)

Ga

in

E

rr

o

r (

L

S

B

)

V

DD

= V

REF

= 5V

F

SAMPLE

= 100 ksps

V

DD

= V

REF

= 2.7V

F

SAMPLE

= 50 ksps

0

10

20

30

40

50

60

70

80

90

100

1

10

100

Input Frequency (kHz)

S

NR (

d

B

)

V

DD

= V

REF

= 2.7V

F

SAMPLE

= 50 ksps

V

DD

= V

REF

= 5V

F

SAMPLE

= 100 ksps

-100

-90

-80

-70

-60

-50

-40

-30

-20

-10

0

1

10

100

Input Frequency (kHz)

TH

D

(

d

B

)

V

DD

= V

REF

= 2.7V

F

SAMPLE

= 50 ksps

V

DD

= V

REF

= 5V, F

SAMPLE

= 100 ksps

0.0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

1.6

1.8

2.0

-50

-25

0

25

50

75

100

Temperature (°C)

O

ff

s

e

t Er

ro

r

(L

SB)

V

DD

= V

REF

= 5V

F

SAMPLE

= 100 ksps

V

DD

= V

REF

= 2.7V

F

SAMPLE

= 50 ksps

0

10

20

30

40

50

60

70

80

90

100

1

10

100

Input Frequency (kHz)

S

INA

D (

d

B)

V

DD

= V

REF

= 2.7V

F

SAMPLE

= 50 ksps

V

DD

= V

REF

= 5V

F

SAMPLE

= 100 ksps

0

10

20

30

40

50

60

70

80

-40

-35

-30

-25

-20

-15

-10

-5

0

Input Signal Level (dB)

S

INAD

(

d

B)

V

DD

= V

REF

= 2.7V

F

SAMPLE

= 50 ksps

V

DD

= V

REF

= 5V

F

SAMPLE

= 100 ksps