2005-2016 Microchip Technology Inc.

DS20001952C-page 1

MCP23017/MCP23S17

Features

• 16-Bit Remote Bidirectional I/O Port:

- I/O pins default to input

• High-Speed I

2

C Interface (MCP23017):

- 100 kHz

- 400 kHz

- 1.7 MHz

• High-Speed SPI Interface (MCP23S17):

- 10 MHz (maximum)

• Three Hardware Address Pins to Allow Up to

Eight Devices On the Bus

• Configurable Interrupt Output Pins:

- Configurable as active-high, active-low or

open-drain

• INTA and INTB Can Be Configured to Operate

Independently or Together

• Configurable Interrupt Source:

- Interrupt-on-change from configured register

defaults or pin changes

• Polarity Inversion Register to Configure the

Polarity of the Input Port Data

• External Reset Input

• Low Standby Current: 1 µA (max.)

• Operating Voltage:

- 1.8V to 5.5V @ -40°C to +85°C

- 2.7V to 5.5V @ -40°C to +85°C

- 4.5V to 5.5V @ -40°C to +125°C

Packages

• 28-pin QFN, 6 x 6 mm Body

• 28-pin SOIC, Wide, 7.50 mm Body

• 28-pin SPDIP, 300 mil Body

• 28-pin SSOP, 5.30 mm Body

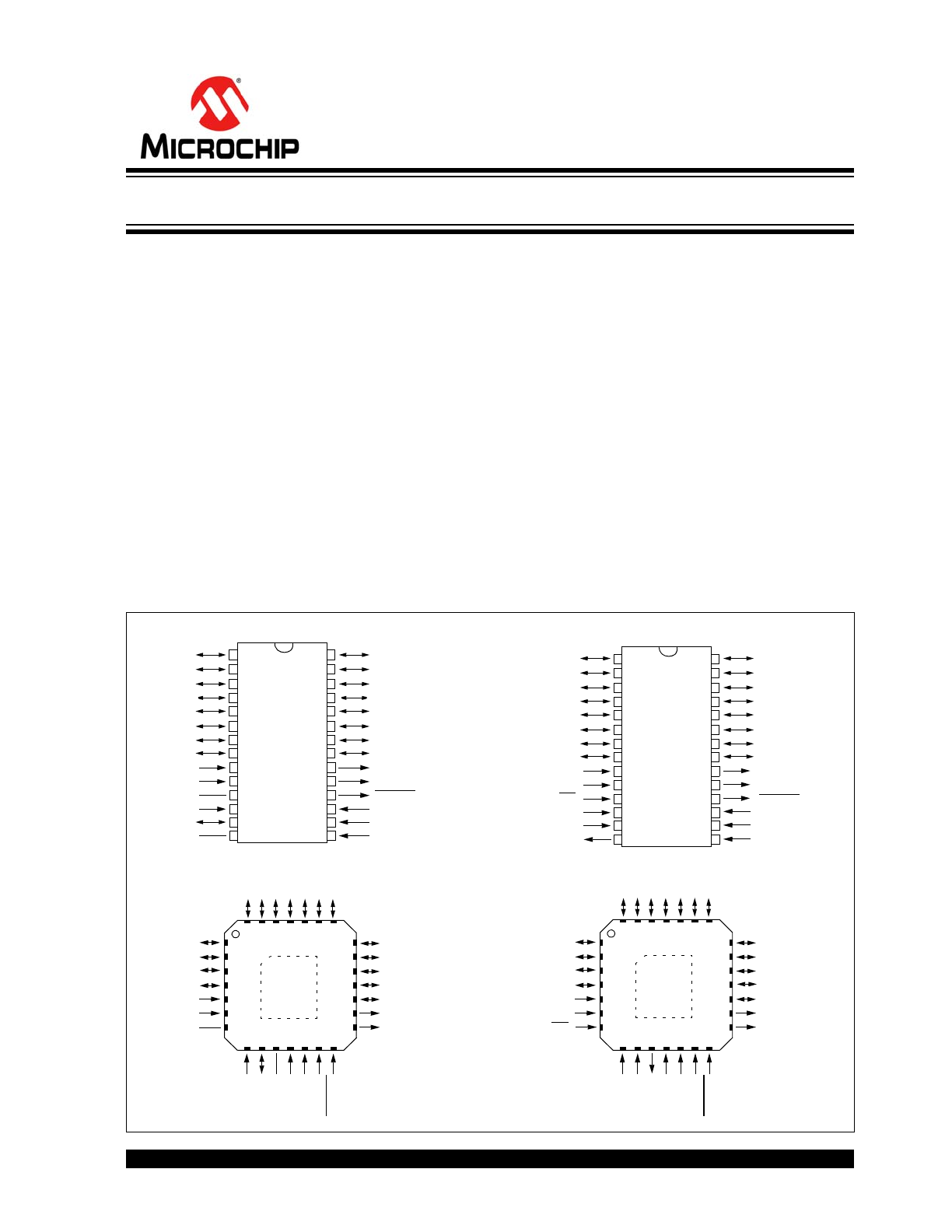

Package Types

2

3

4

5

6

1

7

V

SS

NC

15

16

17

18

19

20

21

GPA4

GPA3

GPA2

GPA1

GPA0

V

DD

INTB

SCK

SDA

NC

A0

A1

A2

RE

SET

23

24

25

26

27

28

22

G

PB3

G

PB2

G

PB1

G

PB0

GP

A

7

GP

A

6

GP

A

5

10 11

8 9

121314

GPB5

GPB6

GPB7

GPB4

INTA

GPB0

GPB1

GPB2

GPB3

INTA

GPB4

NC

NC

GPB5

GPB6

GPB7

SCK

GPA7

GPA6

GPA5

GPA4

GPA3

GPA2

GPA1

GPA0

V

DD

V

SS

A2

A1

A0

SDA

• 1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

INTB

RESET

EP

29 *

SPDIP

SSOP

SOIC

QFN

* Includes Exposed Thermal Pad; see

Table 2-1

.

2

3

4

5

6

1

7

V

SS

CS

15

16

17

18

19

20

21

GPA4

GPA3

GPA2

GPA1

GPA0

V

DD

INTB

SI

SO

A0

A1

A2

RE

S

E

T

23

24

25

26

27

28

22

GPB

3

GPB

2

GPB

1

GPB

0

GP

A

7

GP

A

6

GP

A

5

10 11

8 9

121314

GPB5

GPB6

GPB7

GPB4

INTA

SC

K

EP

29 *

GPB0

GPB1

GPB2

GPB3

INTA

GPB4

SO

CS

GPB5

GPB6

GPB7

SCK

GPA7

GPA6

GPA5

GPA4

GPA3

GPA2

GPA1

GPA0

V

DD

V

SS

A2

A1

A0

SI

• 1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

INTB

RESET

MCP23S17

MCP23017

16-Bit I/O Expander with Serial Interface

MCP23017/MCP23S17

DS20001952C-page 2

2005-2016 Microchip Technology Inc.

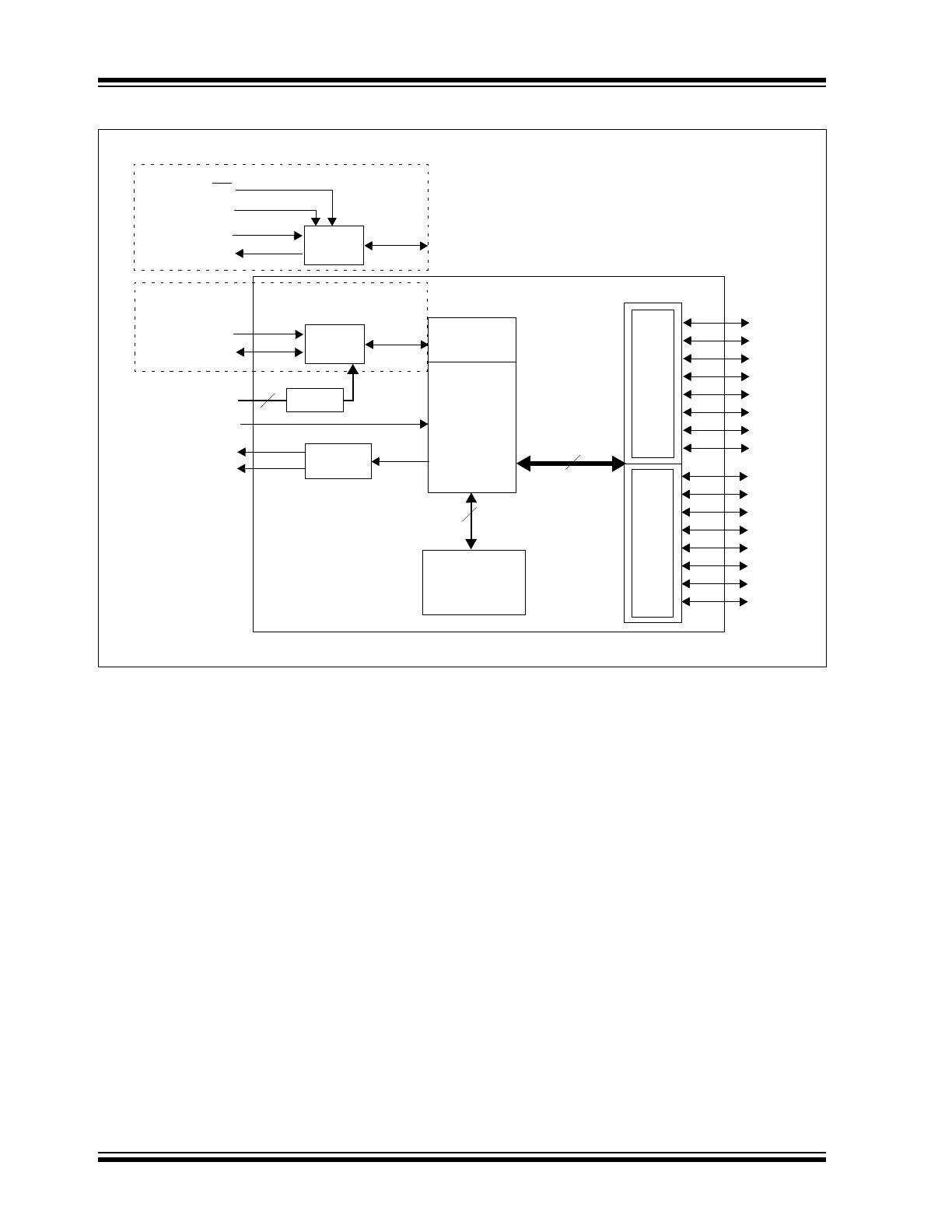

Functional Block Diagram

GPB7

GPB6

GPB5

GPB4

GPB3

GPB2

GPB1

GPB0

I

2

C

Control

GPIO

SCL

SDA

RESET

INTA

16

Configuration/

8

A2:A0

3

Control

Registers

SPI

SI

SO

SCK

CS

MCP23S17

MCP23017

GPA7

GPA6

GPA5

GPA4

GPA3

GPA2

GPA1

GPA0

INTB

Interrupt

GPIO

Serializer/

Deserializer

Logic

Decode

2005-2016 Microchip Technology Inc.

DS20001952C-page 3

MCP23017/MCP23S17

1.0

ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings †

Ambient temperature under bias............................................................................................................. -40°C to +125°C

Storage temperature ............................................................................................................................... -65°C to +150°C

Voltage on V

DD

with respect to V

SS

.......................................................................................................... -0.3V to +5.5V

Voltage on all other pins with respect to V

SS

(except V

DD

)............................................................. -0.6V to (V

DD

+ 0.6V)

Total power dissipation......................................................................................................................................... 700 mW

Maximum current out of V

SS

pin ...........................................................................................................................150 mA

Maximum current into V

DD

pin .............................................................................................................................. 125 mA

Input clamp current, I

IK

(V

I

< 0 or V

I

> V

DD

) .......................................................................................................... ±20 mA

Output clamp current, I

OK

(V

O

< 0 or V

O

> V

DD

) ................................................................................................... ±20 mA

Maximum output current sunk by any output pin .................................................................................................... 25 mA

Maximum output current sourced by any output pin ...............................................................................................25 mA

ESD protection on all pins (HBM:MM) ..............................................................................................................4 kV:400V

† Notice: Stresses above those listed under “Maximum Ratings” may cause permanent damage to the device. This is

a stress rating only and functional operation of the device at those or any other conditions above those indicated in the

operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may

affect device reliability.

MCP23017/MCP23S17

DS20001952C-page 4

2005-2016 Microchip Technology Inc.

1.1

DC Characteristics

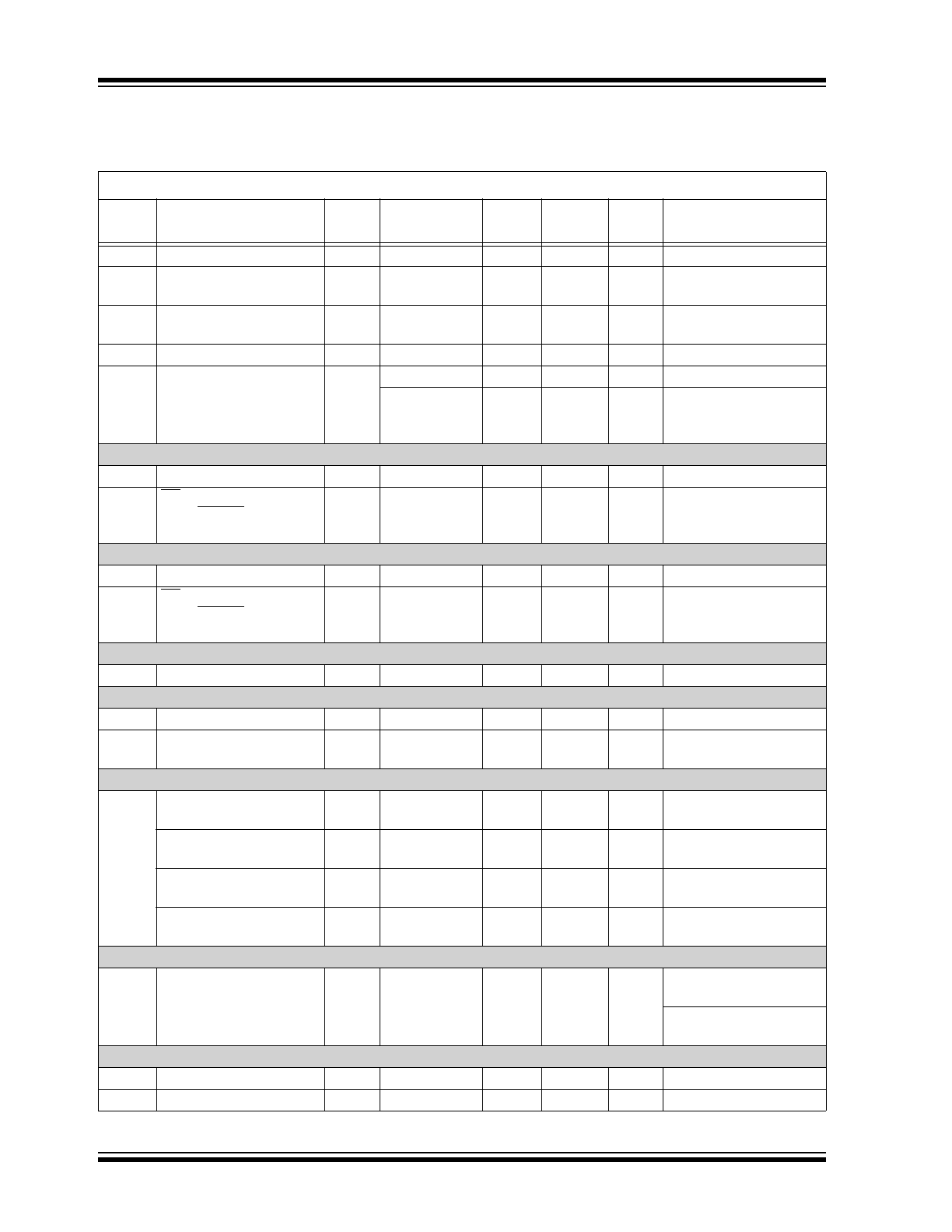

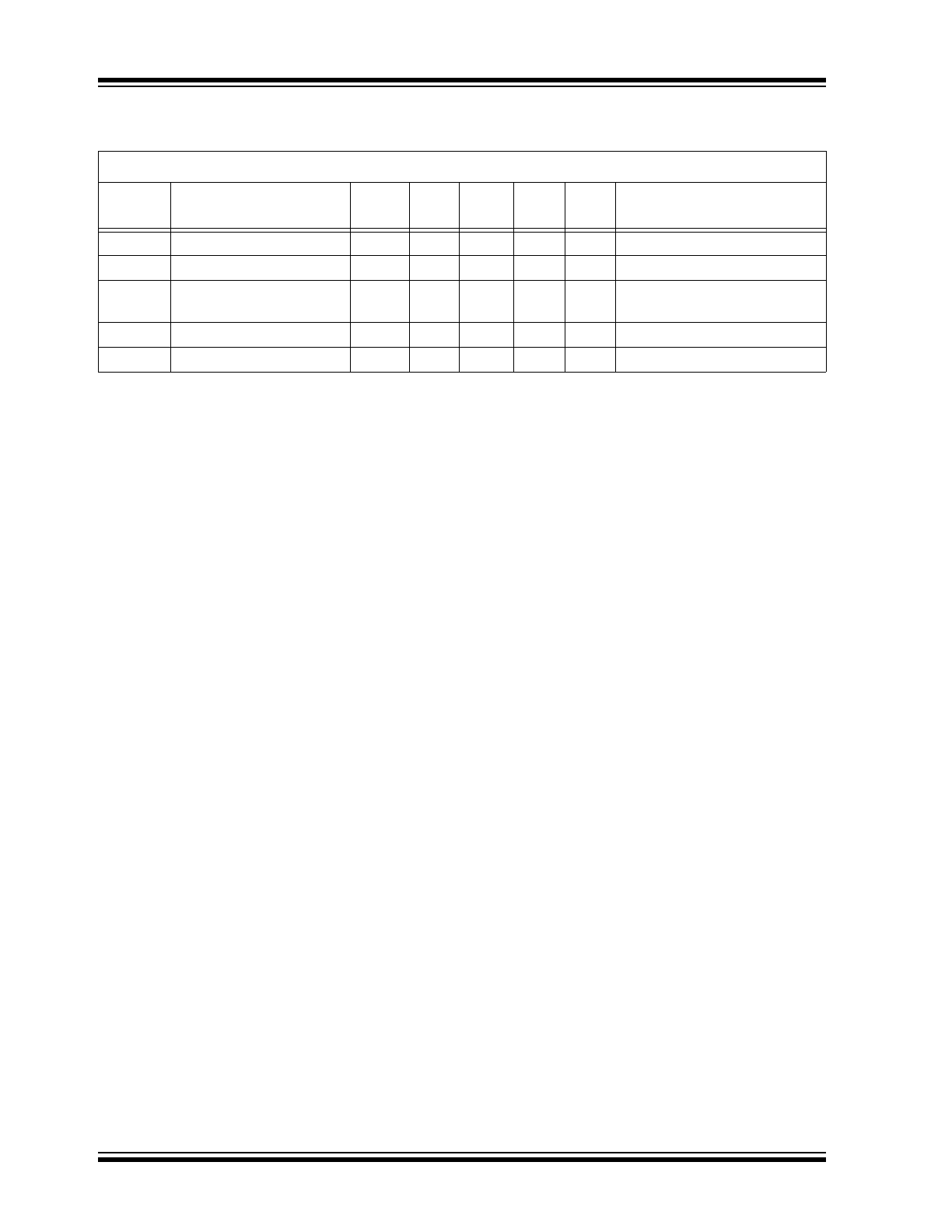

TABLE 1-1:

DC CHARACTERISTICS

Electrical Specifications: Unless otherwise noted, 1.8V

V

DD

5.5V at -40C T

A

+125C

Param.

No.

Characteristic

Sym.

Min.

Typ.

(

1

)

Max.

Units

Conditions

D001

Supply Voltage

V

DD

1.8

—

5.5

V

D002

V

DD

Start Voltage to

ensure Power-on Reset

V

POR

—

V

SS

—

V

D003

V

DD

Rise Rate to ensure

Power-on Reset

SV

DD

0.05

—

—

V/ms

Design guidance only.

Not tested.

D004

Supply Current

I

DD

—

—

1

mA

SCL/SCK = 1 MHz

D005

Standby current

I

DDS8

—

—

1

µA

-40°C

T

A

+85°C

—

—

3

µA

4.5V

V

DD

5.5V

+85°C

T

A

+125C

(

Note 1

)

Input Low Voltage

D030

A0, A1, A2 (TTL buffer)

V

IL

V

SS

—

0.15 V

DD

V

D031

CS, GPIO, SCL/SCK,

SDA, RESET

(Schmitt Trigger)

V

IL

V

SS

—

0.2 V

DD

V

Input High Voltage

D040

A0, A1, A2 (TTL buffer)

V

IH

0.25 V

DD

+ 0.8

—

V

DD

V

D041

CS, GPIO, SCL/SCK,

SDA, RESET

(Schmitt Trigger)

V

IH

0.8 V

DD

—

V

DD

V

For entire V

DD

range

Input Leakage Current

D060

I/O port pins

I

IL

—

—

±1

µA

V

SS

V

PIN

V

DD

Output Leakage Current

D065

I/O port pins

I

LO

—

—

±1

µA

V

SS

V

PIN

V

DD

D070

GPIO weak pull-up

current

I

PU

40

75

115

µA

V

DD

= 5V

GP pins = V

SS

Output Low-Voltage

D080

GPIO

V

OL

—

—

0.6

V

I

OL

= 8.0 mA

V

DD

= 4.5V

INT

V

OL

—

—

0.6

V

I

OL

= 1.6 mA

V

DD

= 4.5V

SO, SDA

V

OL

—

—

0.6

V

I

OL

= 3.0 mA

V

DD

= 1.8V

SDA

V

OL

—

—

0.8

V

I

OL

= 3.0 mA

V

DD

= 4.5V

Output High-Voltage

D090

GPIO, INT, SO

V

OH

V

DD

– 0.7

—

—

V

I

OH

= -3.0 mA

V

DD

= 4.5V

V

DD

– 0.7

—

—

I

OH

= -400 µA

V

DD

= 1.8V

Capacitive Loading Specs on Output Pins

D101

GPIO, SO, INT

C

IO

—

—

50

pF

D102

SDA

C

B

—

—

400

pF

Note 1:

This parameter is characterized, not 100% tested.

2005-2016 Microchip Technology Inc.

DS20001952C-page 5

MCP23017/MCP23S17

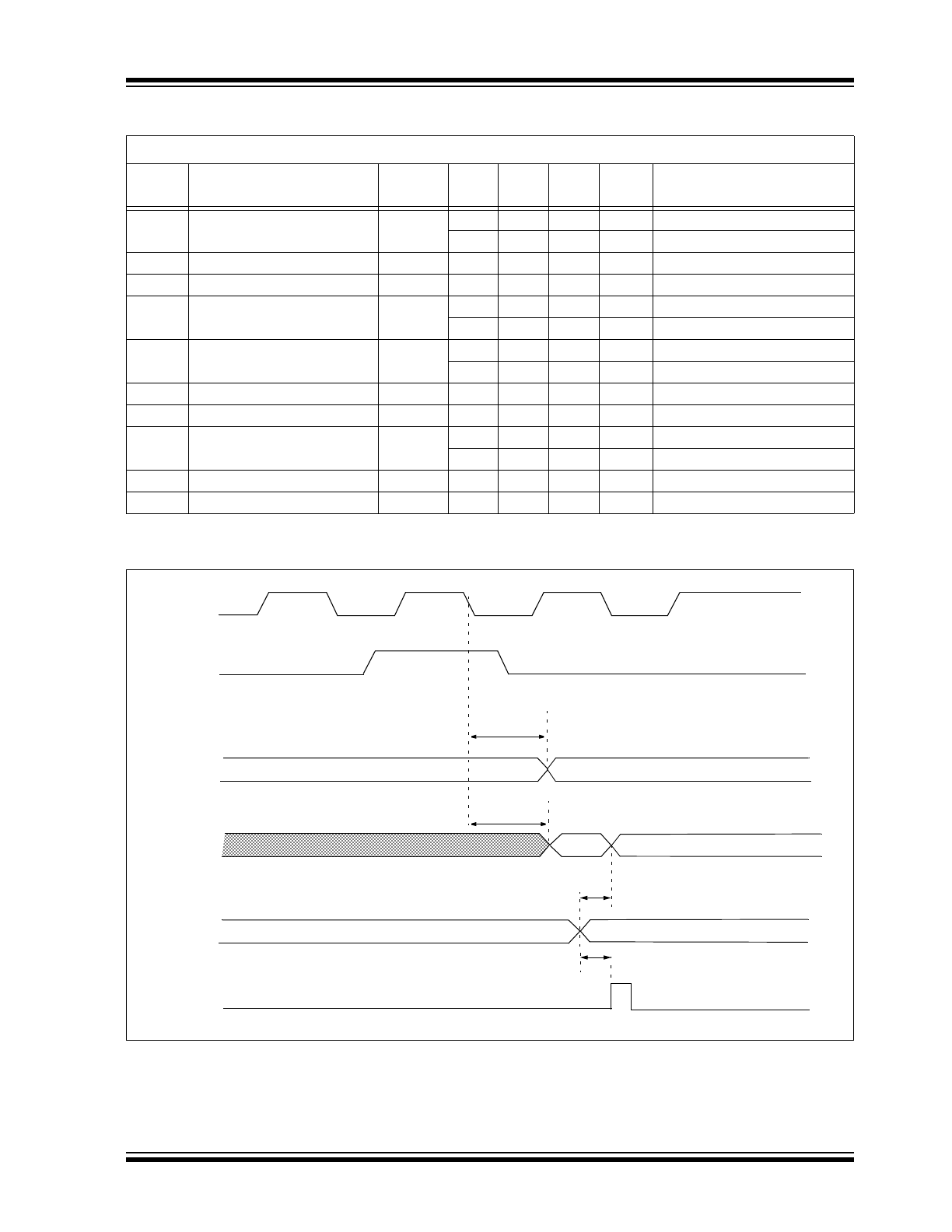

1.2

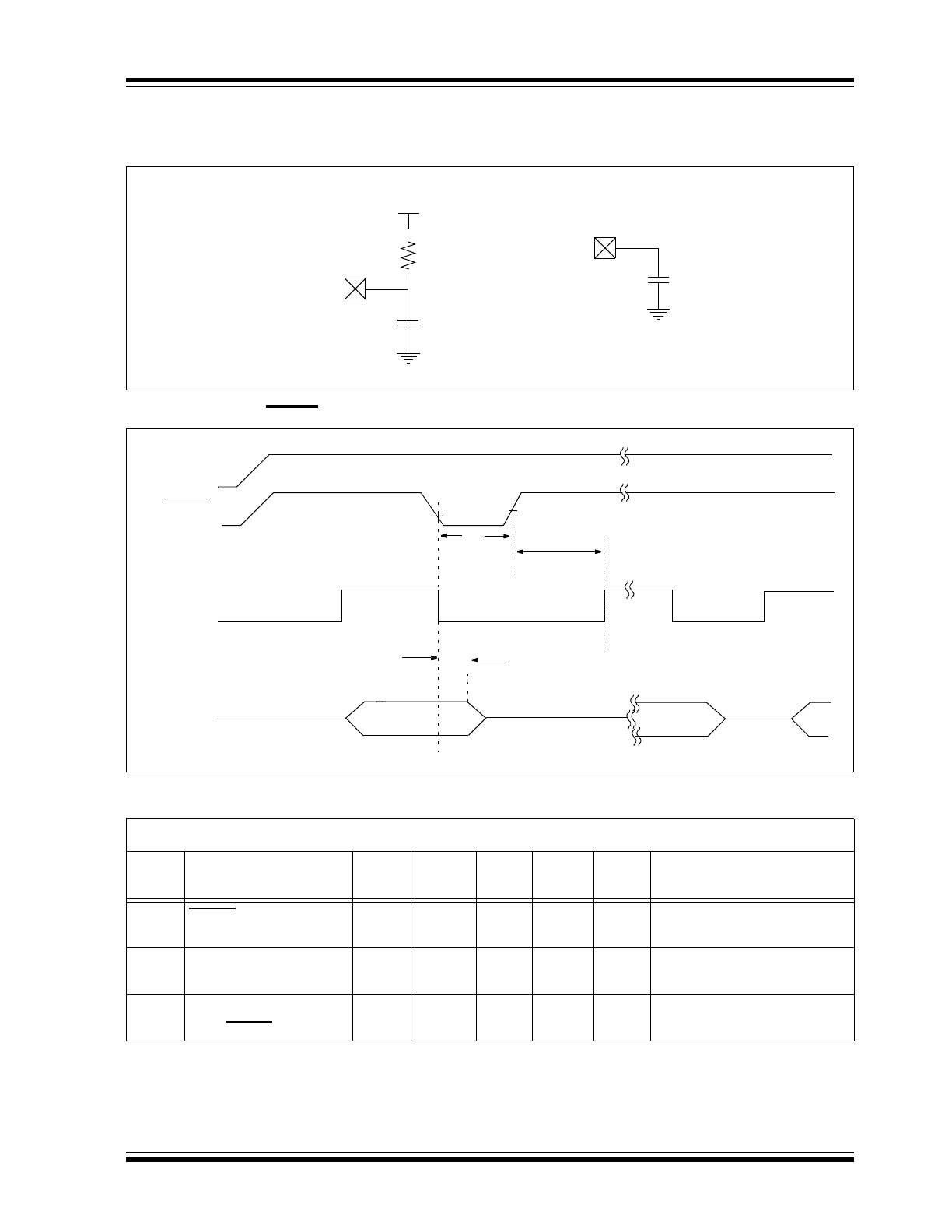

AC Characteristics

FIGURE 1-1:

LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

FIGURE 1-2:

RESET AND DEVICE RESET TIMER TIMING

TABLE 1-2:

DEVICE RESET SPECIFICATIONS

AC Characteristics: Unless otherwise noted, 1.8V

V

DD

5.5V at -40C T

A

+125C

Param.

No.

Characteristic

Sym.

Min.

Typ.

(

1

)

Max.

Units

Conditions

30

RESET Pulse Width

(Low)

T

RSTL

1

—

—

µs

32

Device Active After Reset

high

T

HLD

—

0

—

ns

V

DD

= 5.0V

34

Output High-Impedance

From RESET Low

T

IOZ

—

—

1

µs

Note 1:

This parameter is characterized, not 100% tested.

135 pF

1 k

V

DD

SCL and

SDA pin

MCP23017

50 pF

Pin

V

DD

RESET

Internal

RESET

34

Output pin

32

30

MCP23017/MCP23S17

DS20001952C-page 6

2005-2016 Microchip Technology Inc.

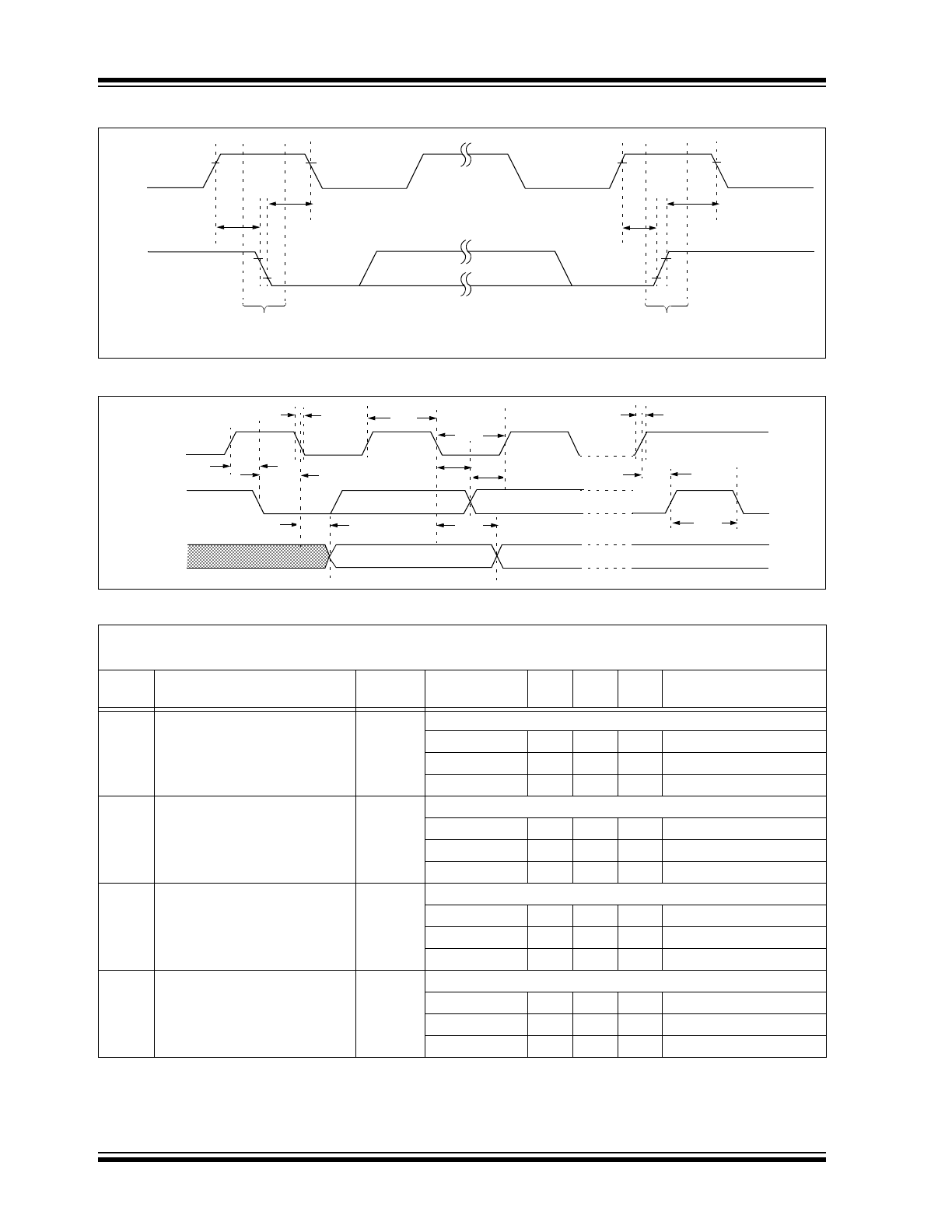

FIGURE 1-3:

I

2

C BUS START/STOP BITS TIMING

FIGURE 1-4:

I

2

C BUS DATA TIMING

TABLE 1-3:

I

2

C BUS DATA REQUIREMENTS

I

2

C Interface AC Characteristics: Unless otherwise noted, 1.8V

V

DD

5.5V at -40C T

A

+125C, R

PU

(SCL,

SDA) = 1 k

, C

L

(SCL, SDA) = 135 pF

Param.

No.

Characteristic

Sym.

Min.

Typ.

Max. Units

Conditions

100

Clock High Time:

T

HIGH

100 kHz mode

4.0

—

—

µs

1.8V – 5.5V

400 kHz mode

0.6

—

—

µs

2.7V – 5.5V

1.7 MHz mode

0.12

—

—

µs

4.5V – 5.5V

101

Clock Low Time:

T

LOW

100 kHz mode

4.7

—

—

µs

1.8V – 5.5V

400 kHz mode

1.3

—

—

µs

2.7V – 5.5V

1.7 MHz mode

0.32

—

—

µs

4.5V – 5.5V

102

SDA and SCL Rise Time:

T

R

(

1

)

100 kHz mode

—

—

1000

ns

1.8V – 5.5V

400 kHz mode

20 + 0.1 C

B

(

2

)

—

300

ns

2.7V – 5.5V

1.7 MHz mode

20

—

160

ns

4.5V – 5.5V

103

SDA and SCL Fall Time:

T

F

(

1

)

100 kHz mode

—

—

300

ns

1.8V – 5.5V

400 kHz mode

20 + 0.1 C

B

(

2

)

—

300

ns

2.7V – 5.5V

1.7 MHz mode

20

—

80

ns

4.5V – 5.5V

Note 1:

This parameter is characterized, not 100% tested.

2:

C

B

is specified to be from 10 to 400 pF.

91

93

SCL

SDA

Start

Condition

Stop

Condition

90

92

90

91

92

100

101

103

106

107

109

109

110

102

SCL

SDA

In

SDA

Out

2005-2016 Microchip Technology Inc.

DS20001952C-page 7

MCP23017/MCP23S17

90

START Condition Setup Time:

T

SU:STA

100 kHz mode

4.7

—

—

µs

1.8V – 5.5V

400 kHz mode

0.6

—

—

µs

2.7V – 5.5V

1.7 MHz mode

0.16

—

—

µs

4.5V – 5.5V

91

START Condition Hold Time:

T

HD:STA

100 kHz mode

4.0

—

—

µs

1.8V – 5.5V

400 kHz mode

0.6

—

—

µs

2.7V – 5.5V

1.7 MHz mode

0.16

—

—

µs

4.5V – 5.5V

106

Data Input Hold Time:

T

HD:DAT

100 kHz mode

0

—

3.45

µs

1.8V – 5.5V

400 kHz mode

0

—

0.9

µs

2.7V – 5.5V

1.7 MHz mode

0

—

0.15

µs

4.5V – 5.5V

107

Data Input Setup Time:

T

SU:DAT

100 kHz mode

250

—

—

ns

1.8V – 5.5V

400 kHz mode

100

—

—

ns

2.7V – 5.5V

1.7 MHz mode

0.01

—

—

µs

4.5V – 5.5V

92

Stop Condition Setup Time:

T

SU:STO

100 kHz mode

4.0

—

—

µs

1.8V – 5.5V

400 kHz mode

0.6

—

—

µs

2.7V – 5.5V

1.7 MHz mode

0.16

—

—

µs

4.5V–5.5V

109

Output Valid From Clock:

T

AA

100 kHz mode

—

—

3.45

µs

1.8V – 5.5V

400 kHz mode

—

—

0.9

µs

2.7V – 5.5V

1.7 MHz mode

—

—

0.18

µs

4.5V – 5.5V

110

Bus Free Time:

T

BUF

100 kHz mode

4.7

—

—

µs

1.8V – 5.5V

400 kHz mode

1.3

—

—

µs

2.7V – 5.5V

1.7 MHz mode

N/A

—

N/A

µs

4.5V – 5.5V

111

Bus Capacitive Loading:

C

B

100 kHz and 400 kHz

—

—

400

pF

Note 1

1.7 MHz

—

—

100

pF

Note 1

112

Input Filter Spike Suppression

(SDA and SCL):

T

SP

100 kHz and 400 kHz

—

—

50

ns

1.7 MHz

—

—

10

ns

Spike suppression off

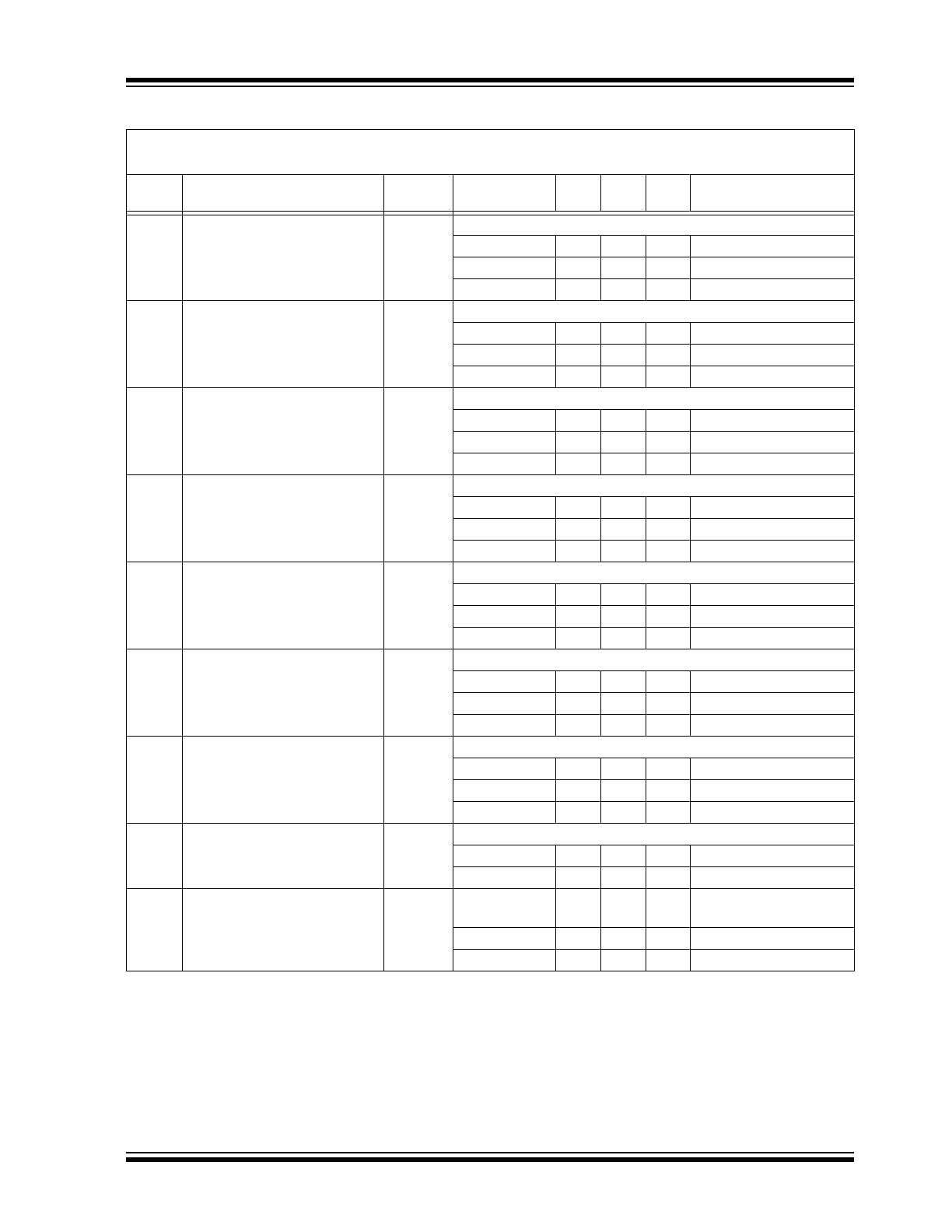

TABLE 1-3:

I

2

C BUS DATA REQUIREMENTS (CONTINUED)

I

2

C Interface AC Characteristics: Unless otherwise noted, 1.8V

V

DD

5.5V at -40C T

A

+125C, R

PU

(SCL,

SDA) = 1 k

, C

L

(SCL, SDA) = 135 pF

Param.

No.

Characteristic

Sym.

Min.

Typ.

Max. Units

Conditions

Note 1:

This parameter is characterized, not 100% tested.

2:

C

B

is specified to be from 10 to 400 pF.

MCP23017/MCP23S17

DS20001952C-page 8

2005-2016 Microchip Technology Inc.

FIGURE 1-5:

SPI INPUT TIMING

FIGURE 1-6:

SPI OUTPUT TIMING

TABLE 1-4:

SPI INTERFACE REQUIREMENTS

SPI Interface AC Characteristics: Unless otherwise noted, 1.8V

V

DD

5.5V at -40C T

A

+125C

Param.

No.

Characteristic

Sym.

Min.

Typ.

Max.

Units

Conditions

—

Clock Frequency

F

CLK

—

—

5

MHz

1.8V – 5.5V

—

—

10

MHz

2.7V – 5.5V

—

—

10

MHz

4.5V – 5.5V

1

CS Setup Time

T

CSS

50

—

—

ns

2

CS Hold Time

T

CSH

100

—

—

ns

1.8V – 5.5V

50

—

—

ns

2.7V – 5.5V

3

CS Disable Time

T

CSD

100

—

—

ns

1.8V – 5.5V

50

—

—

ns

2.7V – 5.5V

4

Data Setup Time

T

SU

20

—

—

ns

1.8V – 5.5V

10

—

—

ns

2.7V – 5.5V

Note 1:

This parameter is characterized, not 100% tested.

SCK

SI

SO

1

5

4

7

6

3

10

2

LSB in

MSB in

High-Impedance

11

Mode 1,1

Mode 0,0

Note 1:

When using SPI Mode 1,1 the CS pin needs to be toggled once before the first communication after

power-up.

CS

(

1

)

CS

SCK

SO

8

13

MSB out

LSB out

2

14

Don’t Care

SI

Mode 1,1

Mode 0,0

9

12

2005-2016 Microchip Technology Inc.

DS20001952C-page 9

MCP23017/MCP23S17

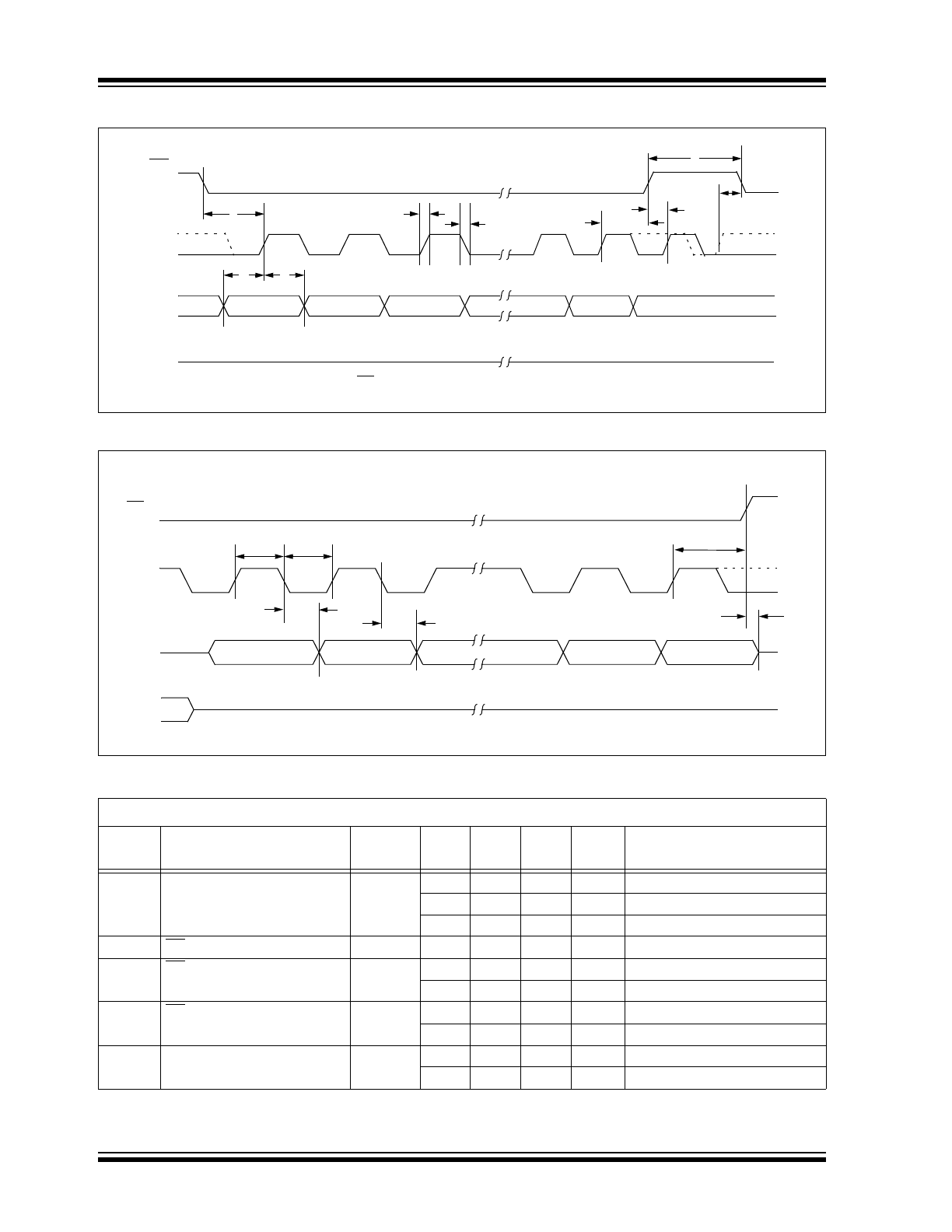

FIGURE 1-7:

GPIO AND INT TIMING

5

Data Hold Time

T

HD

20

—

—

ns

1.8V – 5.5V

10

—

—

ns

2.7V – 5.5V

6

CLK Rise Time

T

R

—

—

2

µs

Note 1

7

CLK Fall Time

T

F

—

—

2

µs

Note 1

8

Clock High Time

T

HI

90

—

—

ns

1.8V – 5.5V

45

—

—

ns

2.7V – 5.5V

9

Clock Low Time

T

LO

90

—

—

ns

1.8V – 5.5V

45

—

—

ns

2.7V – 5.5V

10

Clock Delay Time

T

CLD

50

—

—

ns

11

Clock Enable Time

T

CLE

50

—

—

ns

12

Output Valid from Clock Low

T

V

—

—

90

ns

1.8V – 5.5V

—

—

45

ns

2.7V – 5.5V

13

Output Hold Time

T

HO

0

—

—

ns

14

Output Disable Time

T

DIS

—

—

100

ns

TABLE 1-4:

SPI INTERFACE REQUIREMENTS (CONTINUED)

SPI Interface AC Characteristics: Unless otherwise noted, 1.8V

V

DD

5.5V at -40C T

A

+125C

Param.

No.

Characteristic

Sym.

Min.

Typ.

Max.

Units

Conditions

Note 1:

This parameter is characterized, not 100% tested.

50

SCL/SCK

SDA/SI

In

GPn

Pin

D0

D1

LSb of data byte zero

during a write or read

INT

Pin

INT Pin Active

51

command, depending

on parameter

Output

GPn

Pin

Input

Inactive

53

52

Register

Loaded

MCP23017/MCP23S17

DS20001952C-page 10

2005-2016 Microchip Technology Inc.

TABLE 1-5:

GP AND INT PINS REQUIREMENTS

GP and INT Pins AC Characteristics: Unless otherwise noted, 1.8V

V

DD

5.5V at -40C T

A

+125C

Param.

No.

Characteristic

Sym.

Min.

Typ.

Max.

Units

Conditions

50

Serial Data to Output Valid

T

GPOV

—

—

500

ns

51

Interrupt Pin Disable Time

T

INTD

—

—

600

ns

52

GP Input Change to

Register Valid

T

GPIV

—

—

450

ns

53

IOC Event to INT Active

T

GPINT

—

—

600

ns

Glitch Filter on GP Pins

T

GLITCH

—

—

150

ns

Note 1

Note 1:

This parameter is characterized, not 100% tested.