2010-2017 Microchip Technology Inc.

DS00001875C-page 1

Highlights

• Single Chip Hi-Speed USB 2.0 to 10/100 Ethernet

Controller

• Integrated 10/100 Ethernet MAC with Full-Duplex

Support

• Integrated 10/100 Ethernet PHY with HP Auto-

MDIX support

• Integrated USB 2.0 Hi-Speed Device Controller

• Integrated USB 2.0 Hi-Speed PHY

• Implements Reduced Power Operating Modes

Target Applications

• Embedded Systems

• Set-Top Boxes

• PVRs

• CE Devices

• Networked Printers

• USB Port Replicators

• Standalone USB to Ethernet Dongles

• Test Instrumentation

• Industrial

Key Features

• USB Device Controller

- Fully compliant with Hi-Speed Universal

Serial Bus Specification Revision 2.0

- Supports HS (480 Mbps) and FS (12 Mbps)

modes

- Four endpoints supported

- Supports vendor specific commands

- Integrated USB 2.0 PHY

- Remote wakeup supported

• High-Performance 10/100 Ethernet Controller

- Fully compliant with IEEE802.3/802.3u

- Integrated Ethernet MAC and PHY

- 10BASE-T and 100BASE-TX support

- Full- and half-duplex support

- Full- and half-duplex flow control

- Preamble generation and removal

- Automatic 32-bit CRC generation and check-

ing

- Automatic payload padding and pad removal

- Loop-back modes

- TCP/UDP/IP/ICMP checksum offload support

- Flexible address filtering modes

–One 48-bit perfect address

–64 hash-filtered multicast addresses

–Pass all multicast

–Promiscuous mode

–Inverse filtering

–Pass all incoming with status report

- Wakeup packet support

- Integrated Ethernet PHY

–Auto-negotiation

–Automatic polarity detection and correction

–HP Auto-MDIX support

–Link status change wake-up detection

- Support for 3 status LEDs

- External MII and Turbo MII support Home-

PNA™ and HomePlug® PHY

• Power and I/Os

- Various low power modes

- NetDetach feature increases battery life

1

- Supports PCI-like PME wake

1

- 11 GPIOs

- Supports bus-powered and self-powered

operation

- Integrated power-on reset circuit

- Single external 3.3v I/O supply

–Internal core regulator

• Miscellaneous Features

- EEPROM Controller

- Supports custom operation without

EEPROM

1

- IEEE 1149.1 (JTAG) Boundary Scan

- Requires single 25 MHz crystal

• Software

- Windows XP/Vista Driver

- Linux Driver

- Win CE Driver

- MAC OS Driver

- EEPROM Utility

• Packaging

- 56-pin QFN (8x8 mm) RoHS Compliant

Environmental

- Commercial Temperature Range (0°C to

+70°C)

- Industrial Temperature Range (-40°C to

+85°C)

1

= LAN9500A/LAN9500Ai ONLY

LAN9500/LAN9500i/LAN9500A/LAN9500Ai

LAN950x USB 2.0 to 10/100 Ethernet Controller

LAN950x

DS00001875C-page 2

2010-2017 Microchip Technology Inc.

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at

docerrors@microchip.com

. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for cur-

rent devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the

revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site;

http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are

using.

Customer Notification System

Register on our web site at

www.microchip.com

to receive the most current information on all of our products.

2010-2017 Microchip Technology Inc.

DS00001875C-page 3

LAN950x

Table of Contents

1.0 LAN950x Family Differences Overview .......................................................................................................................................... 4

2.0 Introduction ..................................................................................................................................................................................... 6

3.0 Pin Description and Configuration ................................................................................................................................................ 11

4.0 Power Connections ....................................................................................................................................................................... 24

5.0 Functional Description .................................................................................................................................................................. 25

6.0 PME Operation ........................................................................................................................................................................... 112

7.0 Register Descriptions .................................................................................................................................................................. 116

8.0 Operational Characteristics ......................................................................................................................................................... 189

9.0 Package Outline .......................................................................................................................................................................... 207

Appendix A: Data Sheet Revision History ......................................................................................................................................... 209

The Microchip Web Site .................................................................................................................................................................... 210

Customer Change Notification Service ............................................................................................................................................. 210

Customer Support ............................................................................................................................................................................. 210

Product Identification System ........................................................................................................................................................... 211

LAN950x

DS00001875C-page 4

2010-2017 Microchip Technology Inc.

1.0

LAN950X FAMILY DIFFERENCES OVERVIEW

The Microchip LAN950x is a family of high performance Hi-Speed USB 2.0 to 10/100 Ethernet controllers. The “x” in the

part number is a generic term referring to the entire family, which includes the following devices:

• LAN9500

• LAN9500i

• LAN9500A

• LAN9500Ai

Device specific features that do no pertain to the entire LAN950x family are called out independently throughout this

document.

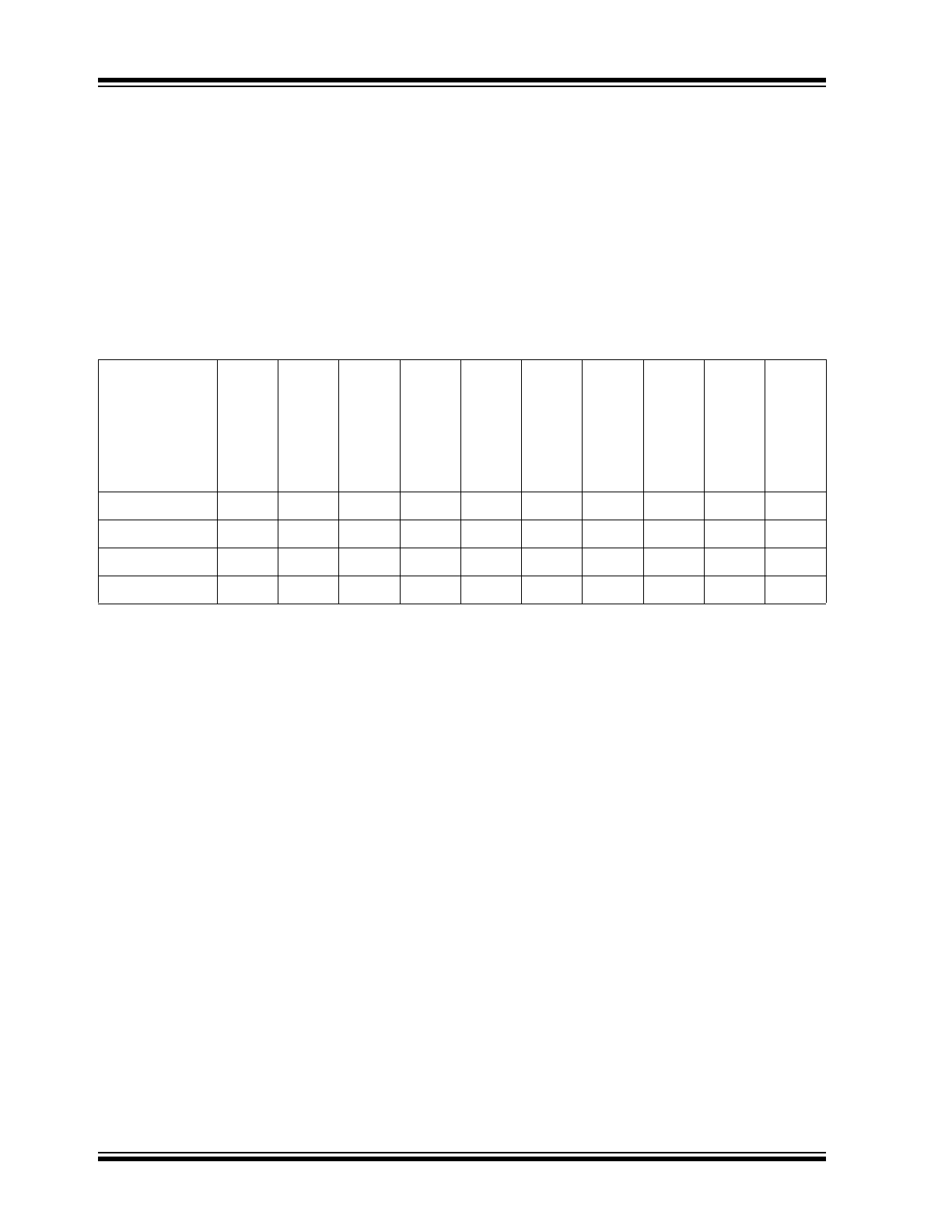

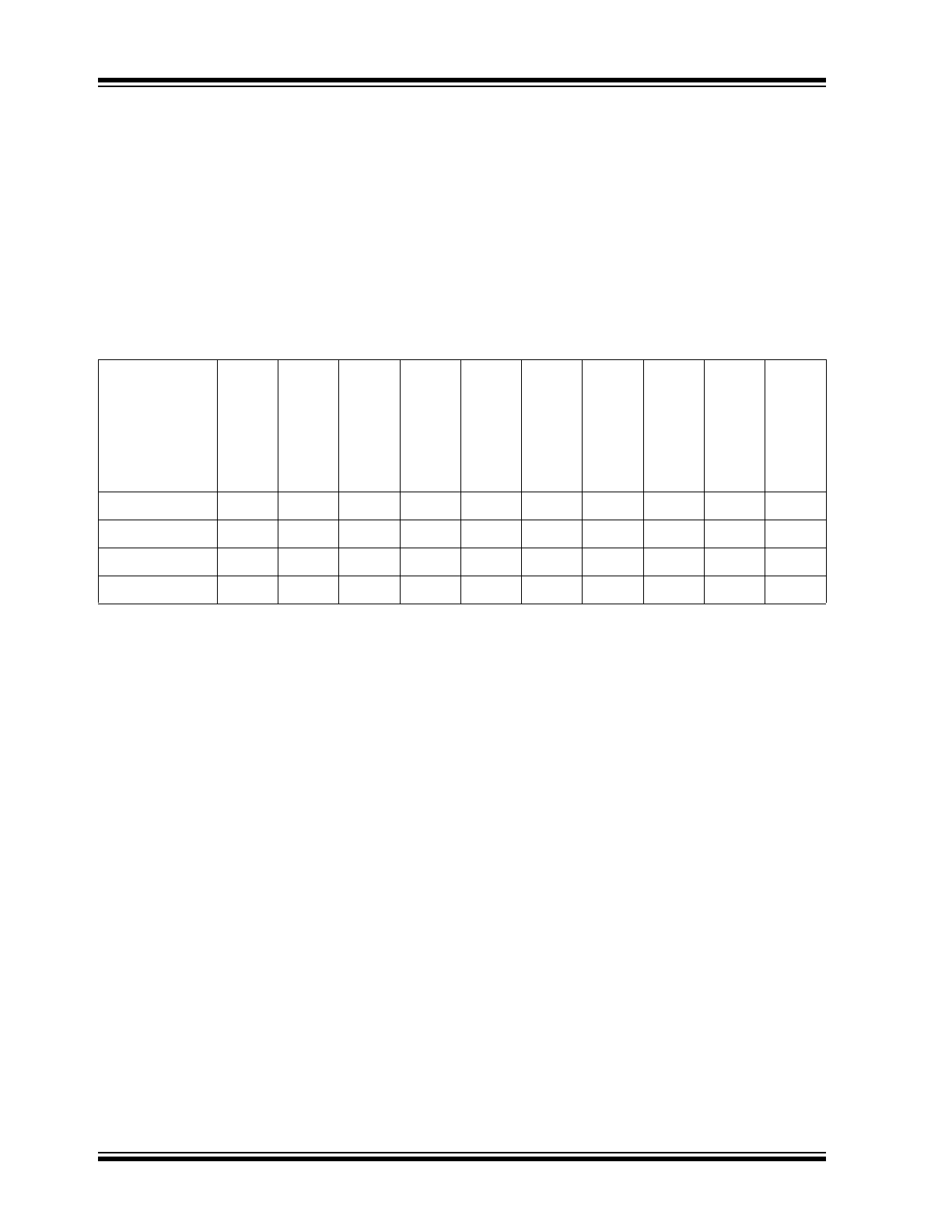

Table 1-1

provides a summary of the feature differences between family members.

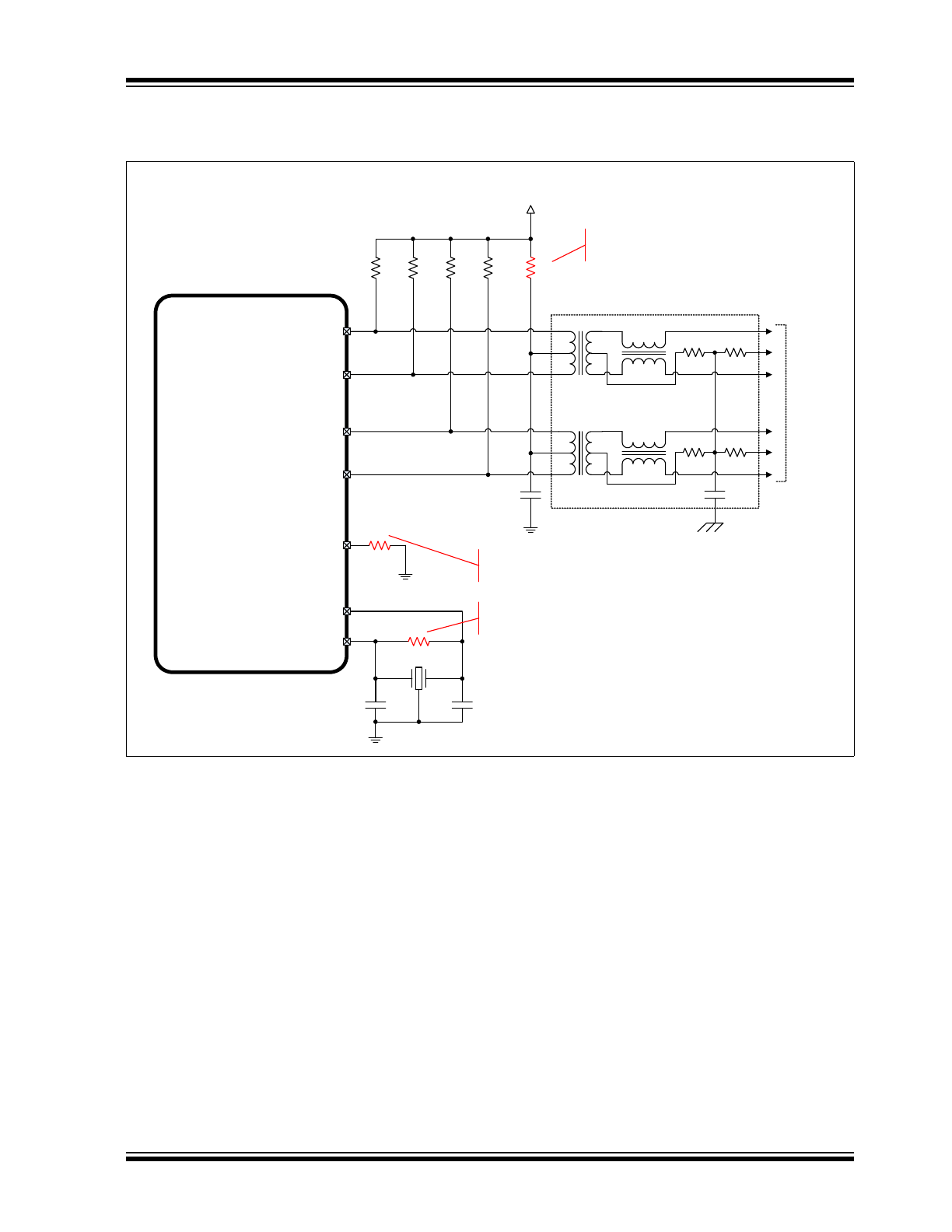

The LAN9500/LAN9500i and LAN9500A/LAN9500Ai are pin compatible. However, the value of the required EXRES

resistor and other system components differ between devices. Refer to

Figure 1-1

and the LAN950x reference sche-

matics for additional information.

TABLE 1-1:

LAN950X FAMILY DIFFERENCES

Part

Num

b

er

PME

W

ake

Ne

t

Deta

ch

Suspend3

St

ate

Go

od

Packe

t

W

a

keu

p

PHY

Boost

C

u

sto

m

Op

era

tio

n

without EEPROM

In

cr

ease

d W

ake

up

Fra

m

e Fi

lte

r

Lo

w Po

wer

100

Μ

W Cry

stal

Su

pp

ort

0

o

To

7

0

o

C

-40

o

to 85

o

c

LAN9500

X

LAN9500i

X

LAN9500A

X

X

X

X

X

X

X

X

X

LAN9500Ai

X

X

X

X

X

X

X

X

X

2010-2017 Microchip Technology Inc.

DS00001875C-page 5

LAN950x

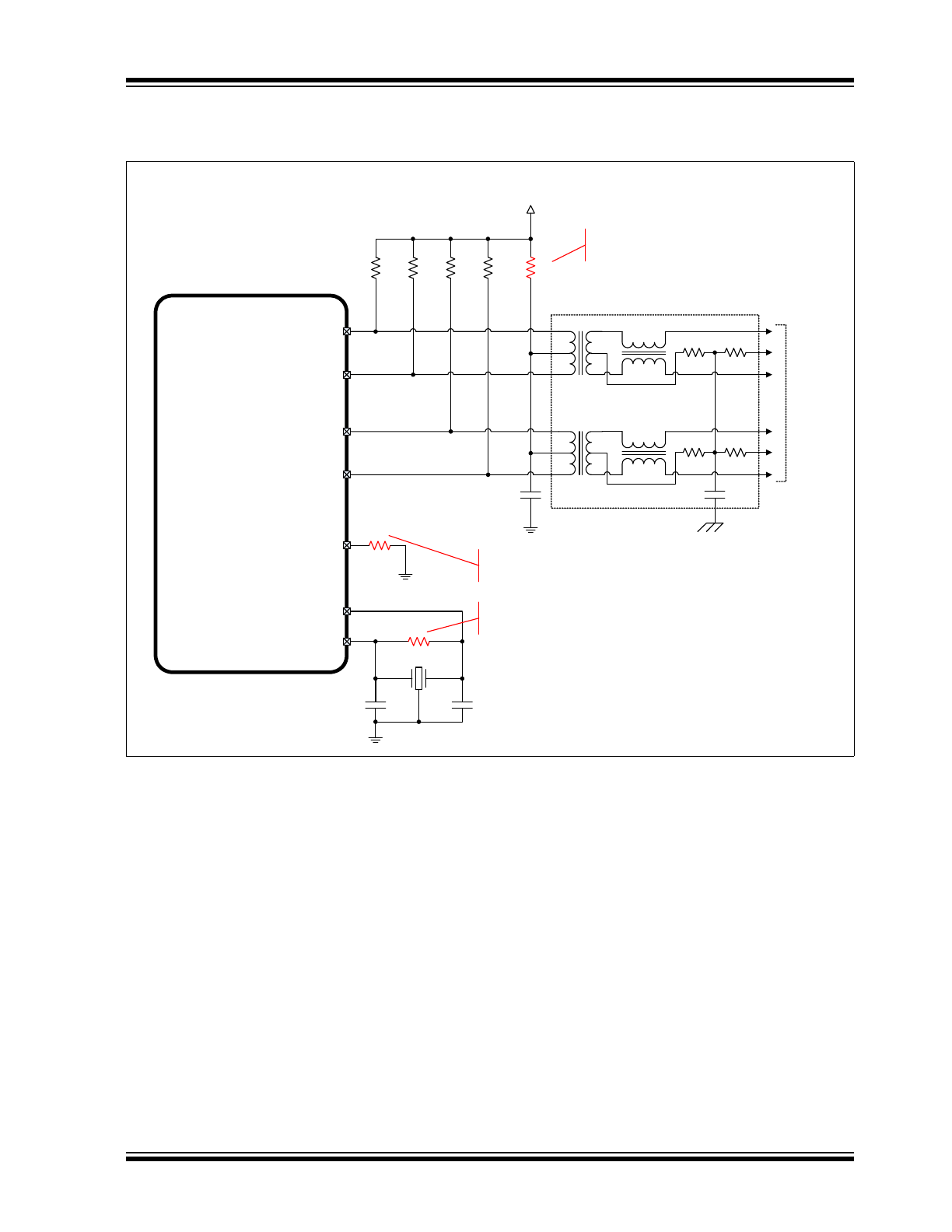

FIGURE 1-1:

SYSTEM COMPONENT DIFFERENCES

+3.3V

Analog

LAN950x

56-PIN QFN

TXP

TXN

RXP

RXN

R1

For LAN9500/LAN9500i: 10 Ohm 1%

For LAN9500A/LAN9500Ai: 0 Ohm

Ethernet Magnetics/RJ45

To

Ethernet

49.9

Ohm

1%

49.9

Ohm

1%

49.9

Ohm

1%

49.9

Ohm

1%

EXRES

R2

For LAN9500/LAN9500i: 12.4K Ohm 1%

For LAN9500A/LAN9500Ai: 12.0K Ohm 1%

XO

XI

33pF

33pF

25.000MHz

R3

For LAN9500/LAN9500i: 1M Ohm 1%

For LAN9500A/LAN9500Ai: Do Not Populate

LAN950x

DS00001875C-page 6

2010-2017 Microchip Technology Inc.

2.0

INTRODUCTION

2.1

General Terms and Conventions

The following is a list of the general terms used in this document:

BYTE

8-bits

CSR

Control and Status Registers

DWORD

32-bits

FIFO

First In First Out buffer

Frame

In the context of this document, a frame refers to transfers on the Ethernet

interface.

FSM

Finite State Machine

GPIO

General Purpose I/O

HOST

External system (Includes processor, application software, etc.)

Level-Triggered Sticky Bit

This type of status bit is set whenever the condition that it represents is

asserted. The bit remains set until the condition is no longer true, and the

status bit is cleared by writing a zero.

LFSR

Linear Feedback Shift Register

MAC

Media Access Controller

MII

Media Independent Interface

N/A

Not Applicable

Packet

In the context of this document, a packet refers to transfers on the USB

interface.

POR

Power on Reset.

RESERVED

Refers to a reserved bit field or address. Unless otherwise noted, reserved

bits must always be zero for write operations. Unless otherwise noted, values

are not guaranteed when reading reserved bits. Unless otherwise noted, do

not read or write to reserved addresses.

SCSR

System Control and Status Registers

SMI

Serial Management Interface

TLI

Transaction Layer Interface

URX

USB Bulk Out Packet Receiver

UTX

USB Bulk In Packet Transmitter

WORD

16-bits

ZLP

Zero Length USB Packet

2010-2017 Microchip Technology Inc.

DS00001875C-page 7

LAN950x

2.2

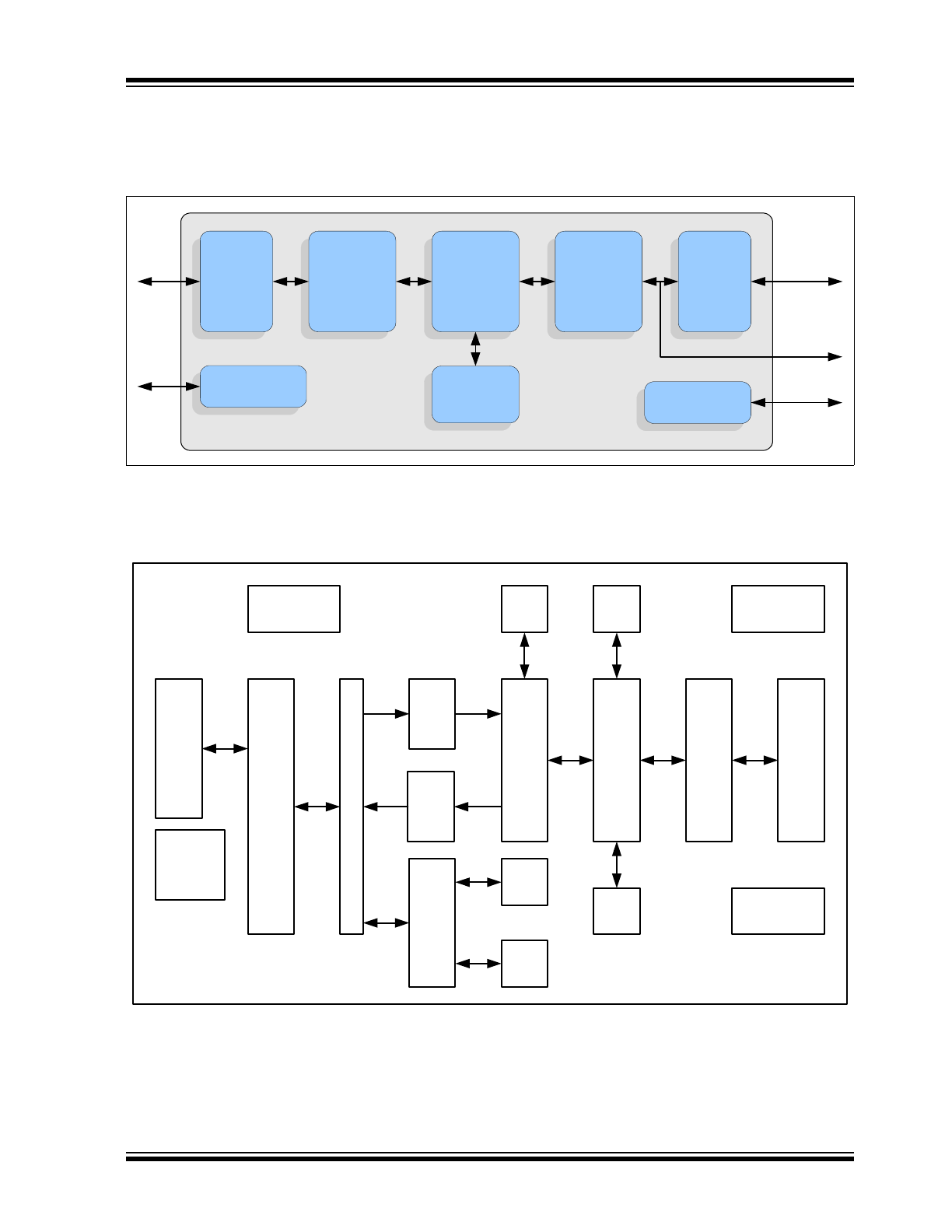

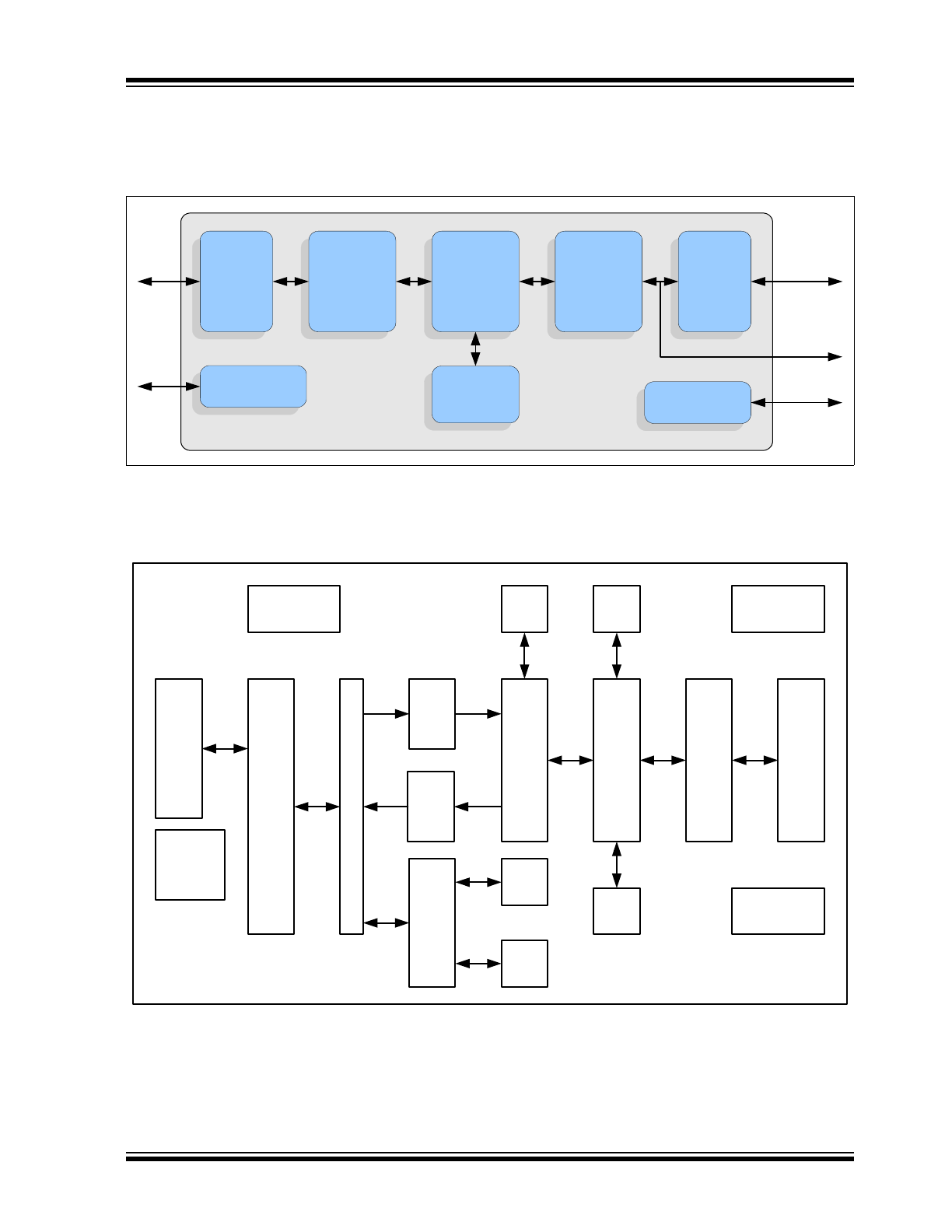

Block Diagram

FIGURE 2-1:

LAN950X BLOCK DIAGRAM

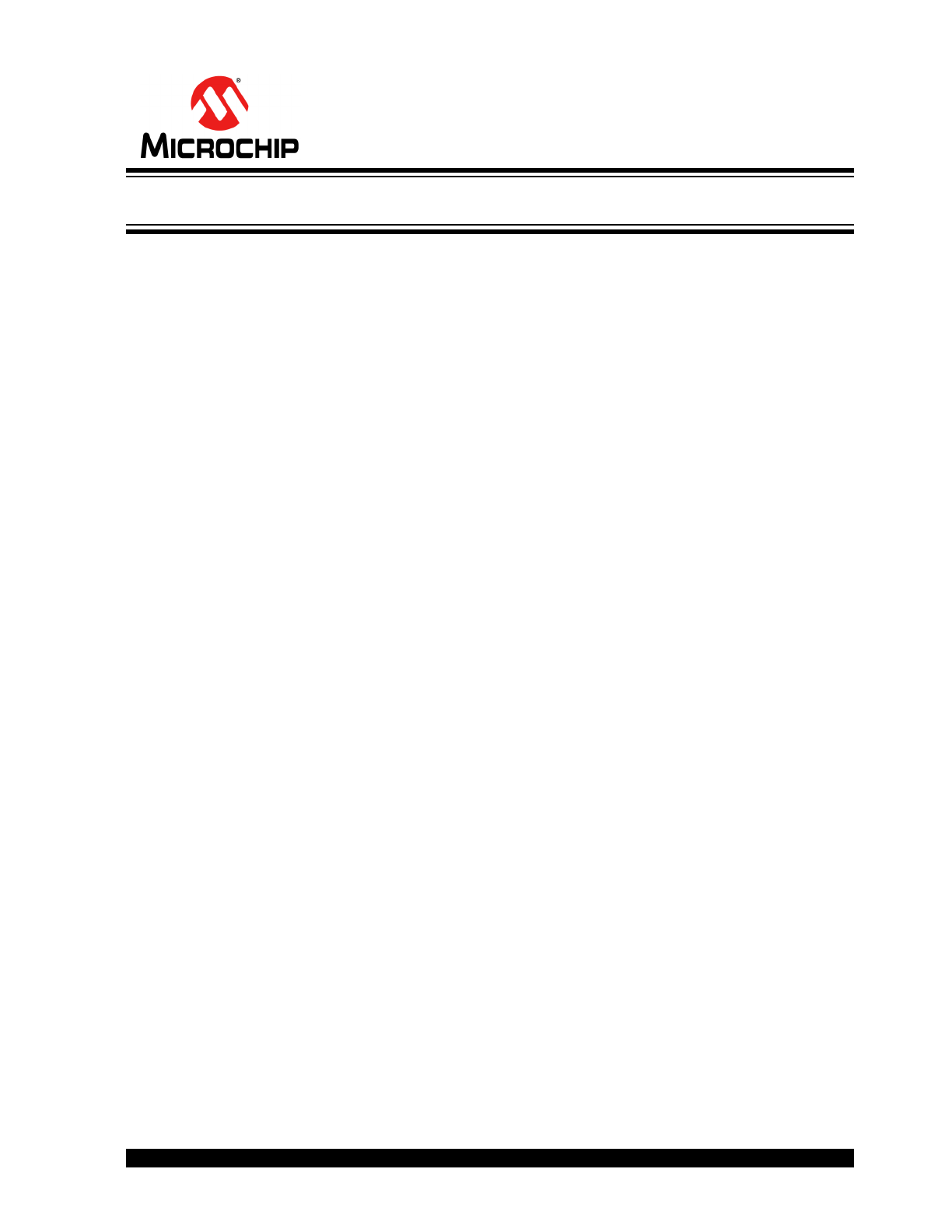

FIGURE 2-2:

LAN950X SYSTEM DIAGRAM

TAP

Controller

EEPROM

Controller

USB 2.0

Device

Controller

SRAM

Ethernet

PHY

10/100

Ethernet

MAC

FIFO

Controller

USB

PHY

LAN950x

MII: To optional

external PHY

Ethernet

EEPROM

JTAG

USB

UDC

MAC

FCT

RAM

7Kx32

TLI

Reg

File

512x37

Reg

File

32x37

EEPROM

Controller

ETH

PHY

USB

PHY

8-bit

60 MHz

UTMI+

UTX

TAP

Controller

USB

Common

Block

URX

CTL

M

U

X

Reg

File

128x32

SCSR

CPM

LAN950x

DS00001875C-page 8

2010-2017 Microchip Technology Inc.

2.2.1

OVERVIEW

The LAN950x is a high performance solution for USB to 10/100 Ethernet port bridging. With applications ranging from

embedded systems, set-top boxes, and PVRs, to USB port replicators, USB to Ethernet dongles, and test instrumenta-

tion, the device is targeted as a high performance, low cost USB/Ethernet connectivity solution.

The LAN950x contains an integrated 10/100 Ethernet PHY, USB PHY, Hi-Speed USB 2.0 device controller, 10/100

Ethernet MAC, TAP controller, EEPROM controller, and a FIFO controller with a total of 30 KB of internal packet buffer-

ing. Two KB of buffer memory are allocated to the Transaction Layer Interface (TLI), while 28 KB are allocated to the

FIFO Controller (FCT).

The internal USB 2.0 device controller and USB PHY are compliant with the USB 2.0 Hi-Speed standard. The device

implements Control, Interrupt, Bulk-in, and Bulk-out USB Endpoints.

The Ethernet controller supports auto-negotiation, auto-polarity correction, HP Auto-MDIX, and is compliant with the

IEEE 802.3 and IEEE 802.3u standards. An external MII interface provides support for an external Fast Ethernet PHY,

HomePNA, and HomePlug functionality.

Multiple power management features are provided, including various low power modes and “Magic Packet”, “Wake On

LAN”, and “Link Status Change” wake events. These wake events can be programmed to initiate a USB remote wakeup.

An internal EEPROM controller exists to load various USB configuration information and the device MAC address. The

integrated IEEE 1149.1 compliant TAP controller provides boundary scan via JTAG.

2.2.2

USB

The USB portion of LAN950x consists of the USB Device Controller (UDC), USB Bulk Out Packet Receiver (URX), USB

Bulk In Packet Transmitter (UTX), Control Block (CTL), System Control and Status Registers (SCSR), and USB PHY.

The USB device controller (UDC) contains a USB low-level protocol interpreter that controls the USB bus protocol,

packet generation/extraction, PID/Device ID parsing, and CRC coding/decoding with autonomous error handling. It is

capable of operating either in USB 1.1 or 2.0 compliant modes. It has autonomous protocol handling functions like stall

condition clearing on setup packets, suspend/resume/reset conditions, and remote wakeup. It also autonomously han-

dles contingency operations for error conditions such as retry for CRC errors, Data toggle errors, and generation of

NYET, STALL, ACK and NACK depending on the endpoint buffer status. The UDC implements four USB endpoints:

Control, Interrupt, Bulk-In, and Bulk-Out.

The Control block (CTL) manages traffic to/from the control endpoint that is not handled by the UDC and constructs the

packets used by the interrupt endpoint. The CTL is responsible for handling some USB standard commands and all ven-

dor specific commands. The vendor specific commands allow for efficient statistics collection and access to the SCSR.

The URX and UTX implement the bulk-out and bulk-in pipes, respectively, which connect the USB Host and the UDC.

They perform the following functions:

The URX passes USB Bulk-Out packets to the FIFO Controller (FCT). It tracks whether or not a USB packet is errone-

ous. It instructs the FCT to flush erroneous packets by rewinding its write pointer.

The UTX retrieves Ethernet frames from the FCT and constructs USB Bulk-In packets from them. If the handshake for

a transmitted Bulk-In packet does not complete, the UTX is capable of retransmitting the packet. The UTX will not

instruct the FCT to advance its read head pointer until the current USB packet has been successfully transmitted to the

USB Host.

Both the URX and UTX are responsible for handling Ethernet frames encapsulated over USB by one of the following

methods.

• Multiple Ethernet frames per USB Bulk packet

• Single Ethernet frame per USB Bulk packet

The UDC also implements the System Control and Status Register (SCSR) space used by the Host to obtain status and

control overall system operation.

The integrated USB 2.0 compliant device PHY supports high speed and full speed modes.

2010-2017 Microchip Technology Inc.

DS00001875C-page 9

LAN950x

2.2.3

FIFO CONTROLLER (FCT)

The FIFO controller uses a 28 KB internal SRAM to buffer RX and TX traffic. 20 KB is allocated for received Ethernet-

USB traffic (RX buffer), while 8 KB is allocated for USB-Ethernet traffic (TX buffer). Bulk-Out packets from the USB con-

troller are directly stored into the TX buffer. The FCT is responsible for extracting Ethernet frames from the USB packet

data and passing the frames to the MAC.Ethernet Frames are directly stored into the RX buffer and become the basis

for bulk-in packets. The FCT passes the stored data to the UTX in blocks typically 512 or 64 bytes in size, depending

on the current HS/FS USB operating speed.

2.2.4

ETHERNET

LAN950x integrates an IEEE 802.3 PHY for twisted pair Ethernet applications and a 10/100 Ethernet Media Access

Controller (MAC).

The PHY can be configured for either 100 Mbps (100Base-TX) or 10 Mbps (10Base-T) Ethernet operation in either Full

or Half Duplex configurations. The PHY block includes auto-negotiation, auto-polarity correction, and Auto-MDIX. Min-

imal external components are required for the utilization of the Integrated PHY.

Optionally, an external PHY may be used via the MII (Media Independent Interface) port, effectively bypassing the inter-

nal PHY. This option allows support for HomePNA and HomePlug applications.

The transmit and receive data paths within the 10/100 Ethernet MAC are independent, allowing for the highest perfor-

mance possible, particularly in full-duplex mode. The Ethernet MAC operates in store and forward mode, utilizing an

independent 2KB buffer for transmitted frames, and a smaller 128 byte buffer for received frames. The Ethernet MAC

data paths connect to the FIFO controller. The MAC also implements a Control and Status Register (CSR) space used

by the Host to obtain status and control its operation.

The Ethernet MAC/PHY supports numerous power management wakeup features, including “Magic Packet”, “Wake on

LAN” and “Link Status Change”. Eight wakeup frame filters are provided by LAN9500A/LAN9500Ai, while four are pro-

vided by LAN9500/LAN9500i.

2.2.5

TRANSACTION LAYER INTERFACE (TLI)

The TLI interfaces the MAC with the FCT. It is a conduit between these two modules through which all transmitted and

received data, along with status information, is passed. It has separate receive and transmit data paths. The TLI contains

a 2KB transmit FIFO and a 128-byte receive FIFO. The transmit FIFO operates in store and forward mode and is capa-

ble of storing up to two Ethernet frames.

2.2.6

POWER MANAGEMENT

The LAN950x features four (

Note 2-1

) variations of USB suspend: SUSPEND0, SUSPEND1, SUSPEND2, and SUS-

PEND3. These modes allow the application to select the ideal balance of remote wakeup functionality and power con-

sumption.

• SUSPEND0: Supports GPIO, “Wake On LAN”, and “Magic Packet” remote wakeup events. This suspend state

reduces power by stopping the clocks of the MAC and other internal modules.

• SUSPEND1: Supports GPIO and “Link Status Change” for remote wakeup events. This suspend state consumes

less power than SUSPEND0.

• SUSPEND2: Supports only GPIO assertion for a remote wakeup event. This is the default suspend mode for the

device.

• SUSPEND3: (

Note 2-1

) Supports GPIO and “Good Packet” remote wakeup event. A “Good Packet” is a received

frame passing certain filtering constraints independent of those imposed on “Wake On LAN” and “Magic Packet”

frames. This suspend state consumes power at a level similar to the NORMAL state, however, it allows for power

savings in the Host CPU.

Note 2-1

All four SUSPEND states are supported by LAN9500A/LAN9500Ai. SUSPEND3 is not supported by

LAN9500/LAN9500i.

Please refer to

Section 5.12, "Wake Events," on page 100

for more information on the USB suspend states and the wake

events supported in each state.

LAN950x

DS00001875C-page 10

2010-2017 Microchip Technology Inc.

2.2.7

EEPROM CONTROLLER (EPC)

LAN950x contains an EEPROM controller for connection to an external EEPROM. This allows for the automatic loading

of static configuration data upon power-on reset, pin reset, or software reset. The EEPROM can be configured to load

USB descriptors, USB device configuration, and MAC address.

(LAN9500A/LAN9500Ai ONLY)

2.2.8

GENERAL PURPOSE I/O

When configured for internal PHY mode, up to eleven GPIOs are supported. All GPIOs can serve as remote wakeup

events when the LAN950x is in a suspended state.

2.2.9

TAP CONTROLLER

IEEE 1149.1 compliant TAP Controller supports boundary scan and various test modes.

2.2.10

CONTROL AND STATUS REGISTERS (CSR)

LAN950x’s functions are controlled and monitored by the Host via the Control and Status Registers (CSR). This register

space includes registers that control and monitor the USB controller, as well as elements of overall system operation

(System Control and Status Registers - SCSR), the MAC (MAC Control and Status Registers - MCSR), and the PHY

(accessed indirectly through the MAC via the MII_ACCESS and MII_DATA registers). The CSR may be accessed via

the USB Vendor Commands (REGISTER READ/REGISTER WRITE). Please refer to

Section 5.3.3, "USB Vendor Com-

mands," on page 41

for more information.

2.2.11

RESETS

LAN950x supports the following system reset events:

• Power on Reset (POR)

• Hardware Reset Input Pin Reset (nRESET)

• Lite Reset (LRST)

• Software Reset (SRST)

• USB Reset

• VBUS Reset

The device supports the following module level reset events:

• Ethernet PHY Software Reset (PHY_RST)

• nTRST Pin Reset for Tap Controller

2.2.12

TEST FEATURES

Read/Write access to internal SRAMs is provided via the CSRs. JTAG based USB BIST is available. Full internal scan

and At Speed scan are supported.

2.2.13

SYSTEM SOFTWARE

LAN950x software drivers are available for the following operating systems:

• Windows XP

• Windows Vista

• Linux

• Win CE

• MAC OS

In addition, an EEPROM programming utility is available for configuring the external EEPROM.

2010-2017 Microchip Technology Inc.

DS00001875C-page 1

Highlights

• Single Chip Hi-Speed USB 2.0 to 10/100 Ethernet

Controller

• Integrated 10/100 Ethernet MAC with Full-Duplex

Support

• Integrated 10/100 Ethernet PHY with HP Auto-

MDIX support

• Integrated USB 2.0 Hi-Speed Device Controller

• Integrated USB 2.0 Hi-Speed PHY

• Implements Reduced Power Operating Modes

Target Applications

• Embedded Systems

• Set-Top Boxes

• PVRs

• CE Devices

• Networked Printers

• USB Port Replicators

• Standalone USB to Ethernet Dongles

• Test Instrumentation

• Industrial

Key Features

• USB Device Controller

- Fully compliant with Hi-Speed Universal

Serial Bus Specification Revision 2.0

- Supports HS (480 Mbps) and FS (12 Mbps)

modes

- Four endpoints supported

- Supports vendor specific commands

- Integrated USB 2.0 PHY

- Remote wakeup supported

• High-Performance 10/100 Ethernet Controller

- Fully compliant with IEEE802.3/802.3u

- Integrated Ethernet MAC and PHY

- 10BASE-T and 100BASE-TX support

- Full- and half-duplex support

- Full- and half-duplex flow control

- Preamble generation and removal

- Automatic 32-bit CRC generation and check-

ing

- Automatic payload padding and pad removal

- Loop-back modes

- TCP/UDP/IP/ICMP checksum offload support

- Flexible address filtering modes

–One 48-bit perfect address

–64 hash-filtered multicast addresses

–Pass all multicast

–Promiscuous mode

–Inverse filtering

–Pass all incoming with status report

- Wakeup packet support

- Integrated Ethernet PHY

–Auto-negotiation

–Automatic polarity detection and correction

–HP Auto-MDIX support

–Link status change wake-up detection

- Support for 3 status LEDs

- External MII and Turbo MII support Home-

PNA™ and HomePlug® PHY

• Power and I/Os

- Various low power modes

- NetDetach feature increases battery life

1

- Supports PCI-like PME wake

1

- 11 GPIOs

- Supports bus-powered and self-powered

operation

- Integrated power-on reset circuit

- Single external 3.3v I/O supply

–Internal core regulator

• Miscellaneous Features

- EEPROM Controller

- Supports custom operation without

EEPROM

1

- IEEE 1149.1 (JTAG) Boundary Scan

- Requires single 25 MHz crystal

• Software

- Windows XP/Vista Driver

- Linux Driver

- Win CE Driver

- MAC OS Driver

- EEPROM Utility

• Packaging

- 56-pin QFN (8x8 mm) RoHS Compliant

Environmental

- Commercial Temperature Range (0°C to

+70°C)

- Industrial Temperature Range (-40°C to

+85°C)

1

= LAN9500A/LAN9500Ai ONLY

LAN9500/LAN9500i/LAN9500A/LAN9500Ai

LAN950x USB 2.0 to 10/100 Ethernet Controller

LAN950x

DS00001875C-page 2

2010-2017 Microchip Technology Inc.

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at

docerrors@microchip.com

. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for cur-

rent devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the

revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site;

http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are

using.

Customer Notification System

Register on our web site at

www.microchip.com

to receive the most current information on all of our products.

2010-2017 Microchip Technology Inc.

DS00001875C-page 3

LAN950x

Table of Contents

1.0 LAN950x Family Differences Overview .......................................................................................................................................... 4

2.0 Introduction ..................................................................................................................................................................................... 6

3.0 Pin Description and Configuration ................................................................................................................................................ 11

4.0 Power Connections ....................................................................................................................................................................... 24

5.0 Functional Description .................................................................................................................................................................. 25

6.0 PME Operation ........................................................................................................................................................................... 112

7.0 Register Descriptions .................................................................................................................................................................. 116

8.0 Operational Characteristics ......................................................................................................................................................... 189

9.0 Package Outline .......................................................................................................................................................................... 207

Appendix A: Data Sheet Revision History ......................................................................................................................................... 209

The Microchip Web Site .................................................................................................................................................................... 210

Customer Change Notification Service ............................................................................................................................................. 210

Customer Support ............................................................................................................................................................................. 210

Product Identification System ........................................................................................................................................................... 211

LAN950x

DS00001875C-page 4

2010-2017 Microchip Technology Inc.

1.0

LAN950X FAMILY DIFFERENCES OVERVIEW

The Microchip LAN950x is a family of high performance Hi-Speed USB 2.0 to 10/100 Ethernet controllers. The “x” in the

part number is a generic term referring to the entire family, which includes the following devices:

• LAN9500

• LAN9500i

• LAN9500A

• LAN9500Ai

Device specific features that do no pertain to the entire LAN950x family are called out independently throughout this

document.

Table 1-1

provides a summary of the feature differences between family members.

The LAN9500/LAN9500i and LAN9500A/LAN9500Ai are pin compatible. However, the value of the required EXRES

resistor and other system components differ between devices. Refer to

Figure 1-1

and the LAN950x reference sche-

matics for additional information.

TABLE 1-1:

LAN950X FAMILY DIFFERENCES

Part

Num

b

er

PME

W

ake

Ne

t

Deta

ch

Suspend3

St

ate

Go

od

Packe

t

W

a

keu

p

PHY

Boost

C

u

sto

m

Op

era

tio

n

without EEPROM

In

cr

ease

d W

ake

up

Fra

m

e Fi

lte

r

Lo

w Po

wer

100

Μ

W Cry

stal

Su

pp

ort

0

o

To

7

0

o

C

-40

o

to 85

o

c

LAN9500

X

LAN9500i

X

LAN9500A

X

X

X

X

X

X

X

X

X

LAN9500Ai

X

X

X

X

X

X

X

X

X

2010-2017 Microchip Technology Inc.

DS00001875C-page 5

LAN950x

FIGURE 1-1:

SYSTEM COMPONENT DIFFERENCES

+3.3V

Analog

LAN950x

56-PIN QFN

TXP

TXN

RXP

RXN

R1

For LAN9500/LAN9500i: 10 Ohm 1%

For LAN9500A/LAN9500Ai: 0 Ohm

Ethernet Magnetics/RJ45

To

Ethernet

49.9

Ohm

1%

49.9

Ohm

1%

49.9

Ohm

1%

49.9

Ohm

1%

EXRES

R2

For LAN9500/LAN9500i: 12.4K Ohm 1%

For LAN9500A/LAN9500Ai: 12.0K Ohm 1%

XO

XI

33pF

33pF

25.000MHz

R3

For LAN9500/LAN9500i: 1M Ohm 1%

For LAN9500A/LAN9500Ai: Do Not Populate

LAN950x

DS00001875C-page 6

2010-2017 Microchip Technology Inc.

2.0

INTRODUCTION

2.1

General Terms and Conventions

The following is a list of the general terms used in this document:

BYTE

8-bits

CSR

Control and Status Registers

DWORD

32-bits

FIFO

First In First Out buffer

Frame

In the context of this document, a frame refers to transfers on the Ethernet

interface.

FSM

Finite State Machine

GPIO

General Purpose I/O

HOST

External system (Includes processor, application software, etc.)

Level-Triggered Sticky Bit

This type of status bit is set whenever the condition that it represents is

asserted. The bit remains set until the condition is no longer true, and the

status bit is cleared by writing a zero.

LFSR

Linear Feedback Shift Register

MAC

Media Access Controller

MII

Media Independent Interface

N/A

Not Applicable

Packet

In the context of this document, a packet refers to transfers on the USB

interface.

POR

Power on Reset.

RESERVED

Refers to a reserved bit field or address. Unless otherwise noted, reserved

bits must always be zero for write operations. Unless otherwise noted, values

are not guaranteed when reading reserved bits. Unless otherwise noted, do

not read or write to reserved addresses.

SCSR

System Control and Status Registers

SMI

Serial Management Interface

TLI

Transaction Layer Interface

URX

USB Bulk Out Packet Receiver

UTX

USB Bulk In Packet Transmitter

WORD

16-bits

ZLP

Zero Length USB Packet

2010-2017 Microchip Technology Inc.

DS00001875C-page 7

LAN950x

2.2

Block Diagram

FIGURE 2-1:

LAN950X BLOCK DIAGRAM

FIGURE 2-2:

LAN950X SYSTEM DIAGRAM

TAP

Controller

EEPROM

Controller

USB 2.0

Device

Controller

SRAM

Ethernet

PHY

10/100

Ethernet

MAC

FIFO

Controller

USB

PHY

LAN950x

MII: To optional

external PHY

Ethernet

EEPROM

JTAG

USB

UDC

MAC

FCT

RAM

7Kx32

TLI

Reg

File

512x37

Reg

File

32x37

EEPROM

Controller

ETH

PHY

USB

PHY

8-bit

60 MHz

UTMI+

UTX

TAP

Controller

USB

Common

Block

URX

CTL

M

U

X

Reg

File

128x32

SCSR

CPM

LAN950x

DS00001875C-page 8

2010-2017 Microchip Technology Inc.

2.2.1

OVERVIEW

The LAN950x is a high performance solution for USB to 10/100 Ethernet port bridging. With applications ranging from

embedded systems, set-top boxes, and PVRs, to USB port replicators, USB to Ethernet dongles, and test instrumenta-

tion, the device is targeted as a high performance, low cost USB/Ethernet connectivity solution.

The LAN950x contains an integrated 10/100 Ethernet PHY, USB PHY, Hi-Speed USB 2.0 device controller, 10/100

Ethernet MAC, TAP controller, EEPROM controller, and a FIFO controller with a total of 30 KB of internal packet buffer-

ing. Two KB of buffer memory are allocated to the Transaction Layer Interface (TLI), while 28 KB are allocated to the

FIFO Controller (FCT).

The internal USB 2.0 device controller and USB PHY are compliant with the USB 2.0 Hi-Speed standard. The device

implements Control, Interrupt, Bulk-in, and Bulk-out USB Endpoints.

The Ethernet controller supports auto-negotiation, auto-polarity correction, HP Auto-MDIX, and is compliant with the

IEEE 802.3 and IEEE 802.3u standards. An external MII interface provides support for an external Fast Ethernet PHY,

HomePNA, and HomePlug functionality.

Multiple power management features are provided, including various low power modes and “Magic Packet”, “Wake On

LAN”, and “Link Status Change” wake events. These wake events can be programmed to initiate a USB remote wakeup.

An internal EEPROM controller exists to load various USB configuration information and the device MAC address. The

integrated IEEE 1149.1 compliant TAP controller provides boundary scan via JTAG.

2.2.2

USB

The USB portion of LAN950x consists of the USB Device Controller (UDC), USB Bulk Out Packet Receiver (URX), USB

Bulk In Packet Transmitter (UTX), Control Block (CTL), System Control and Status Registers (SCSR), and USB PHY.

The USB device controller (UDC) contains a USB low-level protocol interpreter that controls the USB bus protocol,

packet generation/extraction, PID/Device ID parsing, and CRC coding/decoding with autonomous error handling. It is

capable of operating either in USB 1.1 or 2.0 compliant modes. It has autonomous protocol handling functions like stall

condition clearing on setup packets, suspend/resume/reset conditions, and remote wakeup. It also autonomously han-

dles contingency operations for error conditions such as retry for CRC errors, Data toggle errors, and generation of

NYET, STALL, ACK and NACK depending on the endpoint buffer status. The UDC implements four USB endpoints:

Control, Interrupt, Bulk-In, and Bulk-Out.

The Control block (CTL) manages traffic to/from the control endpoint that is not handled by the UDC and constructs the

packets used by the interrupt endpoint. The CTL is responsible for handling some USB standard commands and all ven-

dor specific commands. The vendor specific commands allow for efficient statistics collection and access to the SCSR.

The URX and UTX implement the bulk-out and bulk-in pipes, respectively, which connect the USB Host and the UDC.

They perform the following functions:

The URX passes USB Bulk-Out packets to the FIFO Controller (FCT). It tracks whether or not a USB packet is errone-

ous. It instructs the FCT to flush erroneous packets by rewinding its write pointer.

The UTX retrieves Ethernet frames from the FCT and constructs USB Bulk-In packets from them. If the handshake for

a transmitted Bulk-In packet does not complete, the UTX is capable of retransmitting the packet. The UTX will not

instruct the FCT to advance its read head pointer until the current USB packet has been successfully transmitted to the

USB Host.

Both the URX and UTX are responsible for handling Ethernet frames encapsulated over USB by one of the following

methods.

• Multiple Ethernet frames per USB Bulk packet

• Single Ethernet frame per USB Bulk packet

The UDC also implements the System Control and Status Register (SCSR) space used by the Host to obtain status and

control overall system operation.

The integrated USB 2.0 compliant device PHY supports high speed and full speed modes.

2010-2017 Microchip Technology Inc.

DS00001875C-page 9

LAN950x

2.2.3

FIFO CONTROLLER (FCT)

The FIFO controller uses a 28 KB internal SRAM to buffer RX and TX traffic. 20 KB is allocated for received Ethernet-

USB traffic (RX buffer), while 8 KB is allocated for USB-Ethernet traffic (TX buffer). Bulk-Out packets from the USB con-

troller are directly stored into the TX buffer. The FCT is responsible for extracting Ethernet frames from the USB packet

data and passing the frames to the MAC.Ethernet Frames are directly stored into the RX buffer and become the basis

for bulk-in packets. The FCT passes the stored data to the UTX in blocks typically 512 or 64 bytes in size, depending

on the current HS/FS USB operating speed.

2.2.4

ETHERNET

LAN950x integrates an IEEE 802.3 PHY for twisted pair Ethernet applications and a 10/100 Ethernet Media Access

Controller (MAC).

The PHY can be configured for either 100 Mbps (100Base-TX) or 10 Mbps (10Base-T) Ethernet operation in either Full

or Half Duplex configurations. The PHY block includes auto-negotiation, auto-polarity correction, and Auto-MDIX. Min-

imal external components are required for the utilization of the Integrated PHY.

Optionally, an external PHY may be used via the MII (Media Independent Interface) port, effectively bypassing the inter-

nal PHY. This option allows support for HomePNA and HomePlug applications.

The transmit and receive data paths within the 10/100 Ethernet MAC are independent, allowing for the highest perfor-

mance possible, particularly in full-duplex mode. The Ethernet MAC operates in store and forward mode, utilizing an

independent 2KB buffer for transmitted frames, and a smaller 128 byte buffer for received frames. The Ethernet MAC

data paths connect to the FIFO controller. The MAC also implements a Control and Status Register (CSR) space used

by the Host to obtain status and control its operation.

The Ethernet MAC/PHY supports numerous power management wakeup features, including “Magic Packet”, “Wake on

LAN” and “Link Status Change”. Eight wakeup frame filters are provided by LAN9500A/LAN9500Ai, while four are pro-

vided by LAN9500/LAN9500i.

2.2.5

TRANSACTION LAYER INTERFACE (TLI)

The TLI interfaces the MAC with the FCT. It is a conduit between these two modules through which all transmitted and

received data, along with status information, is passed. It has separate receive and transmit data paths. The TLI contains

a 2KB transmit FIFO and a 128-byte receive FIFO. The transmit FIFO operates in store and forward mode and is capa-

ble of storing up to two Ethernet frames.

2.2.6

POWER MANAGEMENT

The LAN950x features four (

Note 2-1

) variations of USB suspend: SUSPEND0, SUSPEND1, SUSPEND2, and SUS-

PEND3. These modes allow the application to select the ideal balance of remote wakeup functionality and power con-

sumption.

• SUSPEND0: Supports GPIO, “Wake On LAN”, and “Magic Packet” remote wakeup events. This suspend state

reduces power by stopping the clocks of the MAC and other internal modules.

• SUSPEND1: Supports GPIO and “Link Status Change” for remote wakeup events. This suspend state consumes

less power than SUSPEND0.

• SUSPEND2: Supports only GPIO assertion for a remote wakeup event. This is the default suspend mode for the

device.

• SUSPEND3: (

Note 2-1

) Supports GPIO and “Good Packet” remote wakeup event. A “Good Packet” is a received

frame passing certain filtering constraints independent of those imposed on “Wake On LAN” and “Magic Packet”

frames. This suspend state consumes power at a level similar to the NORMAL state, however, it allows for power

savings in the Host CPU.

Note 2-1

All four SUSPEND states are supported by LAN9500A/LAN9500Ai. SUSPEND3 is not supported by

LAN9500/LAN9500i.

Please refer to

Section 5.12, "Wake Events," on page 100

for more information on the USB suspend states and the wake

events supported in each state.

LAN950x

DS00001875C-page 10

2010-2017 Microchip Technology Inc.

2.2.7

EEPROM CONTROLLER (EPC)

LAN950x contains an EEPROM controller for connection to an external EEPROM. This allows for the automatic loading

of static configuration data upon power-on reset, pin reset, or software reset. The EEPROM can be configured to load

USB descriptors, USB device configuration, and MAC address.

(LAN9500A/LAN9500Ai ONLY)

2.2.8

GENERAL PURPOSE I/O

When configured for internal PHY mode, up to eleven GPIOs are supported. All GPIOs can serve as remote wakeup

events when the LAN950x is in a suspended state.

2.2.9

TAP CONTROLLER

IEEE 1149.1 compliant TAP Controller supports boundary scan and various test modes.

2.2.10

CONTROL AND STATUS REGISTERS (CSR)

LAN950x’s functions are controlled and monitored by the Host via the Control and Status Registers (CSR). This register

space includes registers that control and monitor the USB controller, as well as elements of overall system operation

(System Control and Status Registers - SCSR), the MAC (MAC Control and Status Registers - MCSR), and the PHY

(accessed indirectly through the MAC via the MII_ACCESS and MII_DATA registers). The CSR may be accessed via

the USB Vendor Commands (REGISTER READ/REGISTER WRITE). Please refer to

Section 5.3.3, "USB Vendor Com-

mands," on page 41

for more information.

2.2.11

RESETS

LAN950x supports the following system reset events:

• Power on Reset (POR)

• Hardware Reset Input Pin Reset (nRESET)

• Lite Reset (LRST)

• Software Reset (SRST)

• USB Reset

• VBUS Reset

The device supports the following module level reset events:

• Ethernet PHY Software Reset (PHY_RST)

• nTRST Pin Reset for Tap Controller

2.2.12

TEST FEATURES

Read/Write access to internal SRAMs is provided via the CSRs. JTAG based USB BIST is available. Full internal scan

and At Speed scan are supported.

2.2.13

SYSTEM SOFTWARE

LAN950x software drivers are available for the following operating systems:

• Windows XP

• Windows Vista

• Linux

• Win CE

• MAC OS

In addition, an EEPROM programming utility is available for configuring the external EEPROM.