2018 Microchip Technology Inc.

DS20005667A-page 1

SM803XXX

Features

• Generates up to 12 Differential or Single-Ended

Outputs: Frequencies up to 850 MHz

• 75 fs Phase Jitter @ 156.25 MHz (1.875 MHz to

20 MHz)

• 180 fs Phase Jitter @ 156.25 MHz (12 kHz to

20 MHz)

• On-Chip Power Supply Regulation for Excellent

Power Supply Noise Immunity

• Two High-performance PLL Synthesizers to

Generate Multiple Frequencies

• Independently Programmable Output Logic and

Frequency:

- Output Logic: LVPECL, LVDS, HCSL,

LVCMOS

• Selectable Input:

- Crystal: 12 MHz to 62.5 MHz

- Reference Input: 12 MHz to 850 MHz

• SPI Programmable (See Flex SPI

Documentation)

• No External Crystal Oscillator Capacitors

Required

• 2.5V to 3.3V Operating Power Supply

• Separate Output Power Supplies:

- Each Bank can be at Different Power Supply

Voltage Levels (4 Banks of 3 Outputs Each)

• Feedback Input Pins for use as Zero Delay Buffer

• Industrial Temperature Range, –40°C to +85°C

• Green, RoHS, and PFOS Compliant QFN

Packages:

- 48-pin 7 mm × 7 mm (10 Differential or Single

Ended Outputs)

- 76-pin, 9 mm × 9 mm (12 Differential or

Single-Ended Outputs)

- 84-pin, 7 mm × 7 mm (12 Differential or

Single-Ended Outputs)

Applications

• 1/10/40/100 Gigabit Ethernet – (GbE)

• SONET/SDH

• PCI-Express Gen 1/2/3/4

• CPRI/OBSAI – Wireless Base Station

• Fibre Channel

• SAS/SATA

• DIMM (DDR2/DDR3/AMB)

General Description

The SM803xxx is a dual-PLL clock generator that

achieves ultra-low phase jitter (75 fs

RMS

). With 12 total

outputs and dividers on each output, this device can

generate 12 different frequencies up to 850 MHz, from

a low-cost quartz crystal or a reference clock input.

Each of 12 outputs can be independently programmed

to LVPECL, LVDS, HCSL, or LVCMOS logic. For

LVCMOS, only the true side of the channel is used.

The SM803xxx is packaged in a 48-pin QFN with up to

10 outputs, a 76-pin QFN, or 84-pin QFN with 12

outputs.

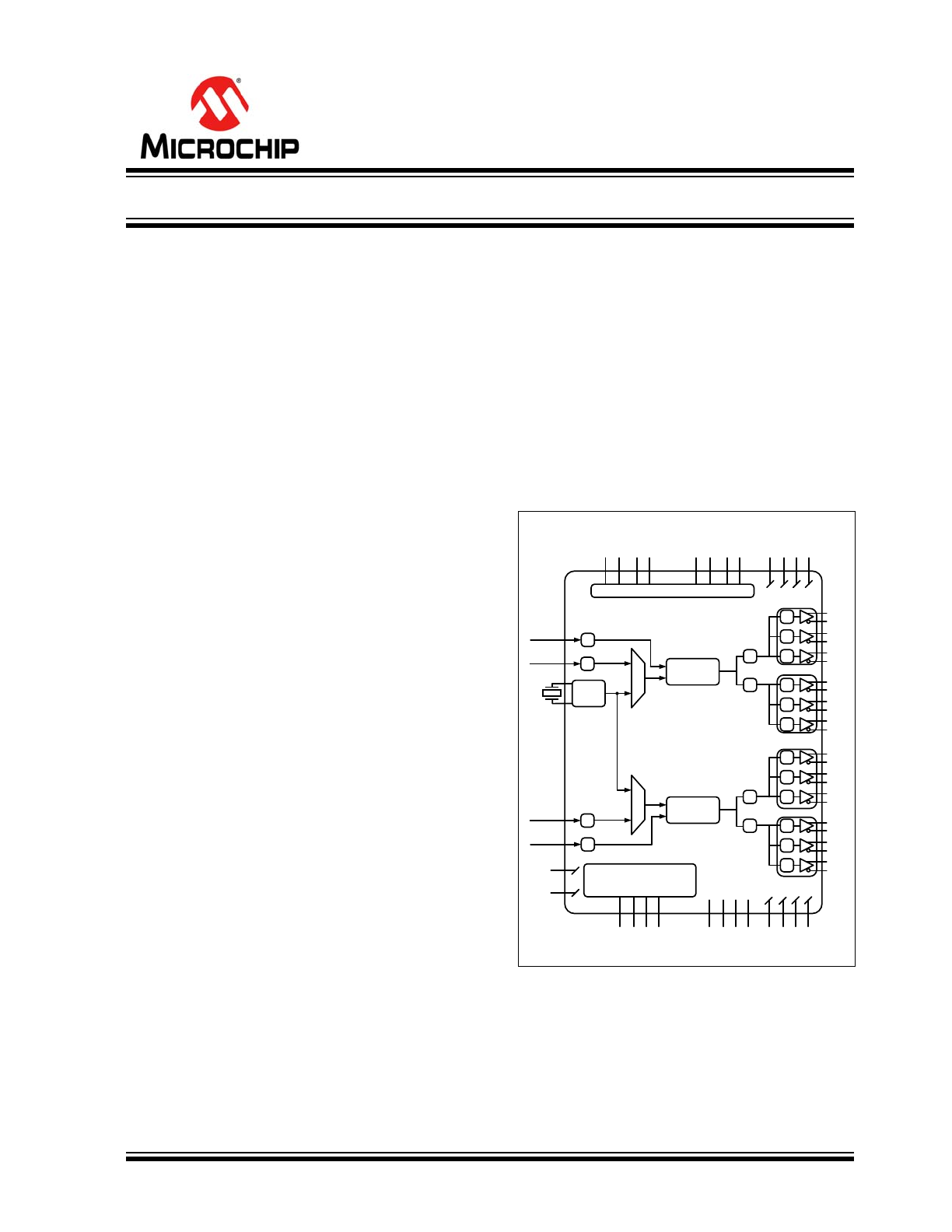

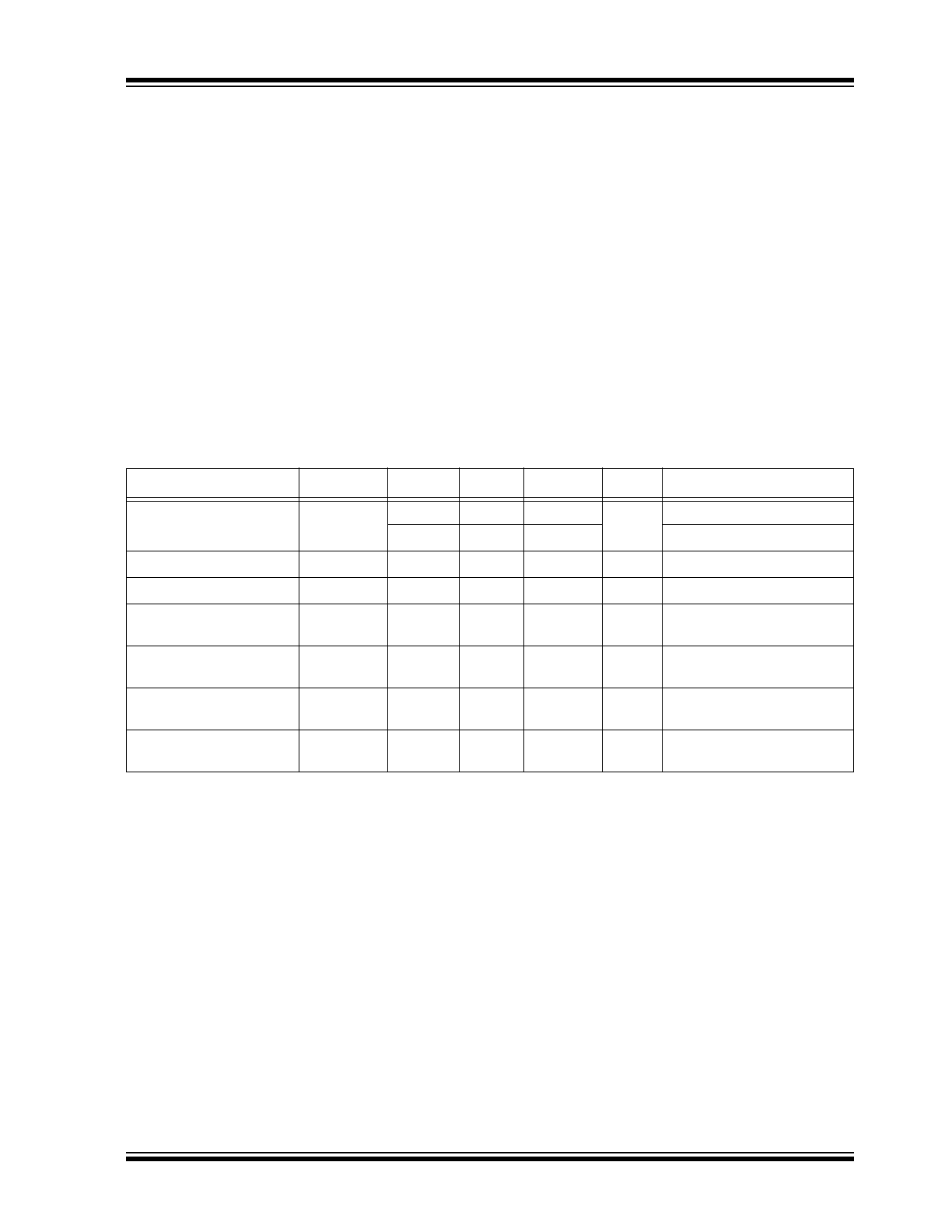

Block Diagram

PLL1

XO

REFIN1

QA1

QA2

QA3

QB1

QB2

QB3

PLL2

QC1

QC2

QC3

QD1

QD2

QD3

VDD POWER RAIL REGULATION

REFIN2

OTP MEMORY

2

VDD

1

VSS

FSD

FSC

FSB

FSA

OED

OEC

OEB

OEA

VSSOD

VSSOC

VSSOB

VSSOA

2

2

2

2

VDDOD

VDDOC

VDDOB

VDDOA

2

2

2

2

VSSAP2

VDDAP2

VSSAP1

VDDAP1

VSSI2

VDDI2

VSSI1

VDDI1

FBIN1

FBIN2

÷

÷

÷

÷

÷

÷

÷

÷

÷

÷

÷

÷

÷

÷

÷

÷

÷

÷

÷

÷

Flexible Ultra-Low Jitter Clock Synthesizer

SM803XXX

DS20005667A-page 2

2018 Microchip Technology Inc.

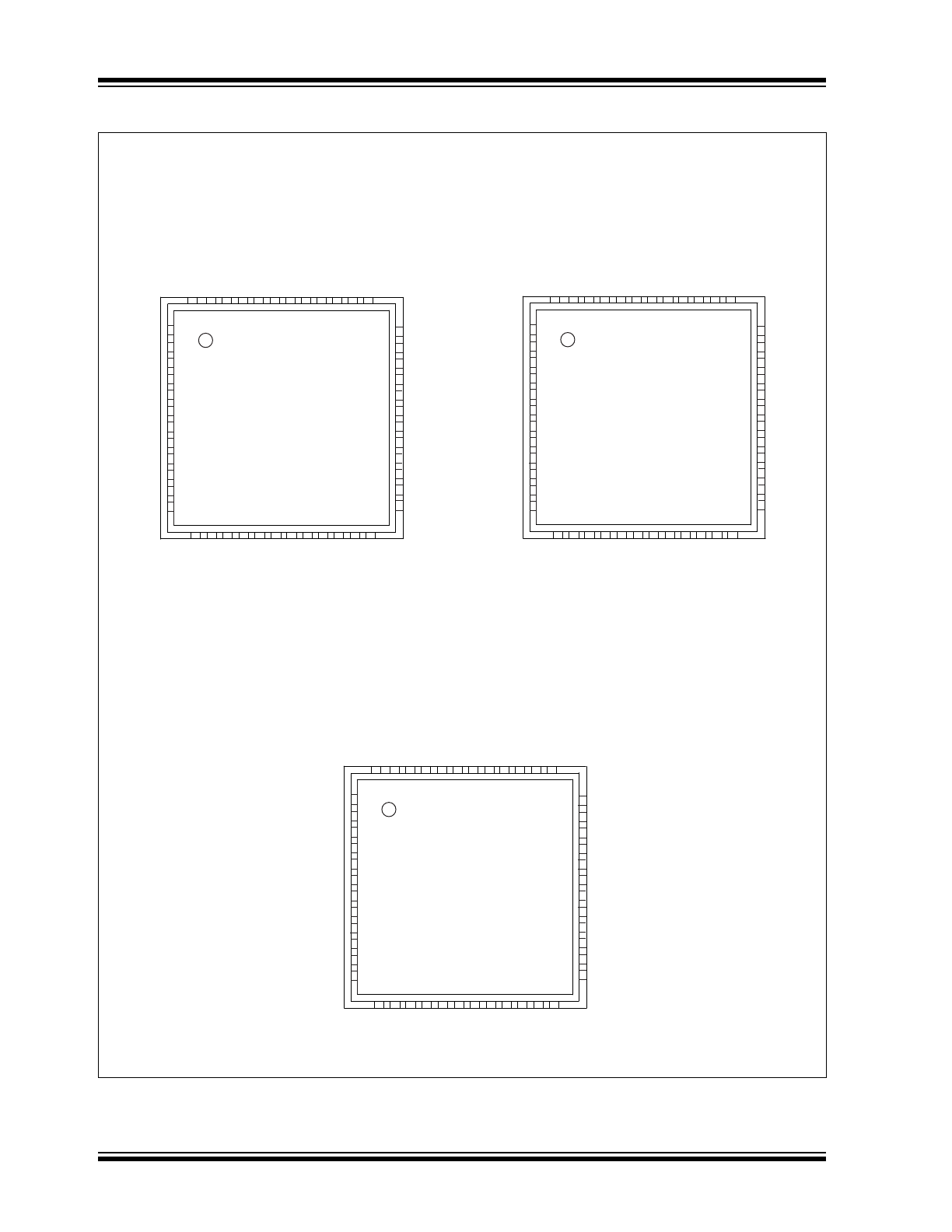

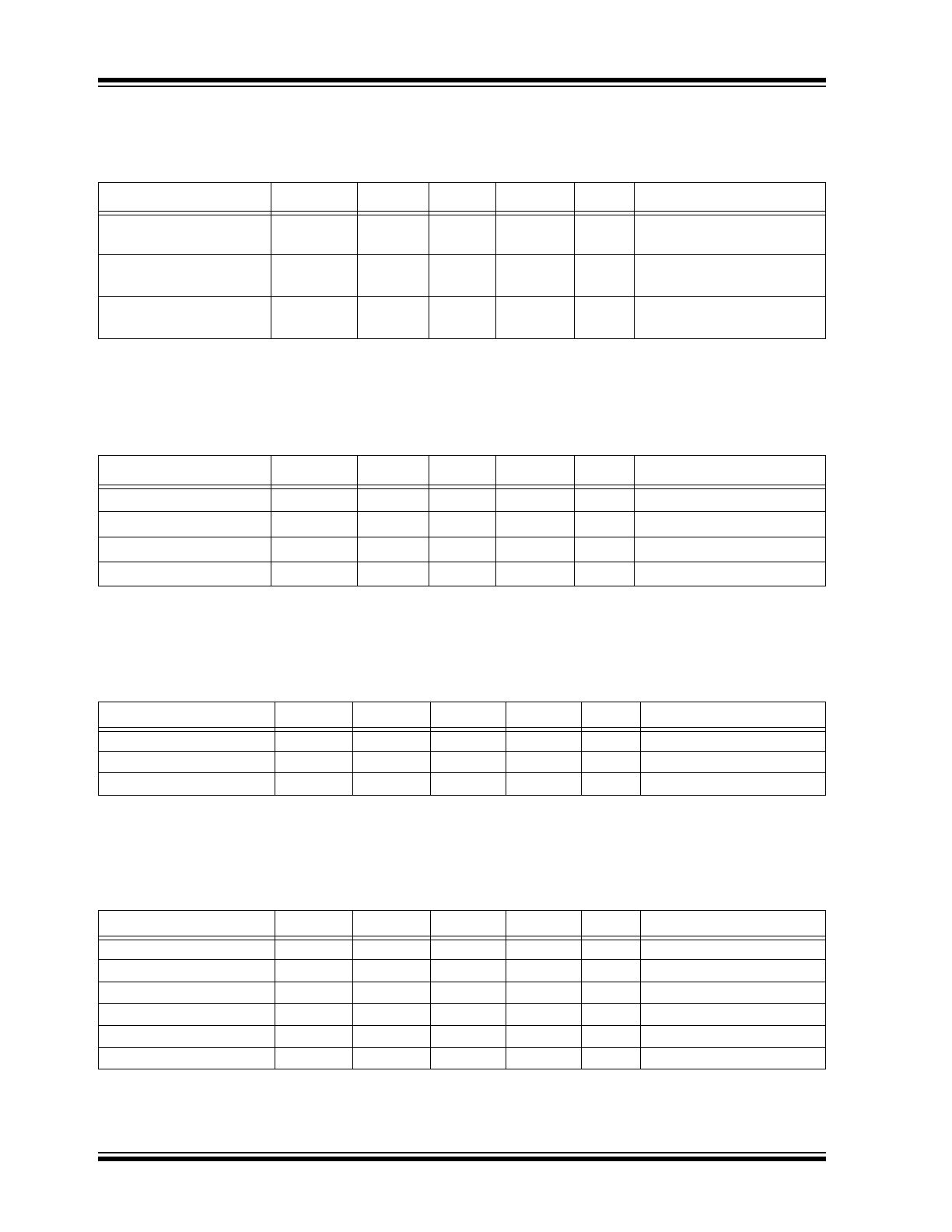

Package Types

SM803XXX

Option 1: 10 outputs

48-Pin

7 mm x 7 mm QFN

Top View

SM803XXX

Option 3: 8 outputs

with FSEL 48-Pin

7 mm x 7 mm QFN

Top View

SM803XXX

Option 2: 8 outputs

with OE 48-Pin

7 mm x 7 mm QFN

Top View

1

2

3

4

5

6

7

8

33

32

31

30

29

28

27

26

12

13 14 15 16 17 18 19

44 43 42 41 40 39 38 37

VDDAP2

VDD

QC1

VDDOC

/QC1

QC2

/QC2

QD1

/QA1

QA1

VDDOA

/QA2

QA2

/QA3

VDDOA

QA3

XT

AL_OUT

REFIN2

/REFIN2

VSS

VSS

XT

AL_IN

VDDI2

VDDI1

9

10

11

25

20 21 22

VDDOD

/QD1

VSS

/QB1

QB1

VSS

VSS

REFIN1

/REFIN1

GND

/QD3

QD3

/QD2

VDDOD

DNC

DNC

DNC

VDDOB

QB2

DNC

23 24

34

35

36

45

46

47

48

QD2

/QB2

VDD

VDDAP1

1

2

3

4

5

6

7

8

33

32

31

30

29

28

27

26

12

13 14 15 16 17 18 19

44 43 42 41 40 39 38 37

VDDAP2

VDD

QC1

VDDOC

/QC1

QC2

/QC2

OEC1/2/3

/QA1

QA1

VDDOA

/QA2

QA2

VDDOA

OEA1/2/3

/QB1

XT

AL_OUT

REFIN2

/REFIN2

VSS

VSS

XT

AL_IN

VDDI2

VDDI1

9

10

11

25

20 21 22

QD1

VDDOD

/QD1

QB1

VSS

OEB1/2/3

VSS

REFIN1

/REFIN1

GND

/QD3

QD3

VDDOD

OED1/2/3

DNC

DNC

DNC

VDDOB

QB2

DNC

23 24

34

35

36

45

46

47

48

VSS

/QB2

VDD

VDDAP1

1

2

3

4

5

6

7

8

33

32

31

30

29

28

27

26

12

13 14 15 16 17 18 19

44 43 42 41 40 39 38 37

VDDAP2

VDD

QC1

VDDOC

/QC1

QC2

/QC2

QD1

/QA1

QA1

VDDOA

/QA2

QA2

VDDOA

/QB1

QB1

XT

AL_OUT

REFIN2

/REFIN2

VSS

VSS

XT

AL_IN

VDDI2

VDDI1

9

10

11

25

20 21 22

VDDOD

/QD1

FSD

FSA

VSS

FSB

VSS

REFIN1

/REFIN1

GND

/QD3

QD3

VDDOD

FSC

DNC

DNC

DNC

VDDOB

QB2

DNC

23 24

34

35

36

45

46

47

48

VSS

/QB2

VDD

VDDAP1

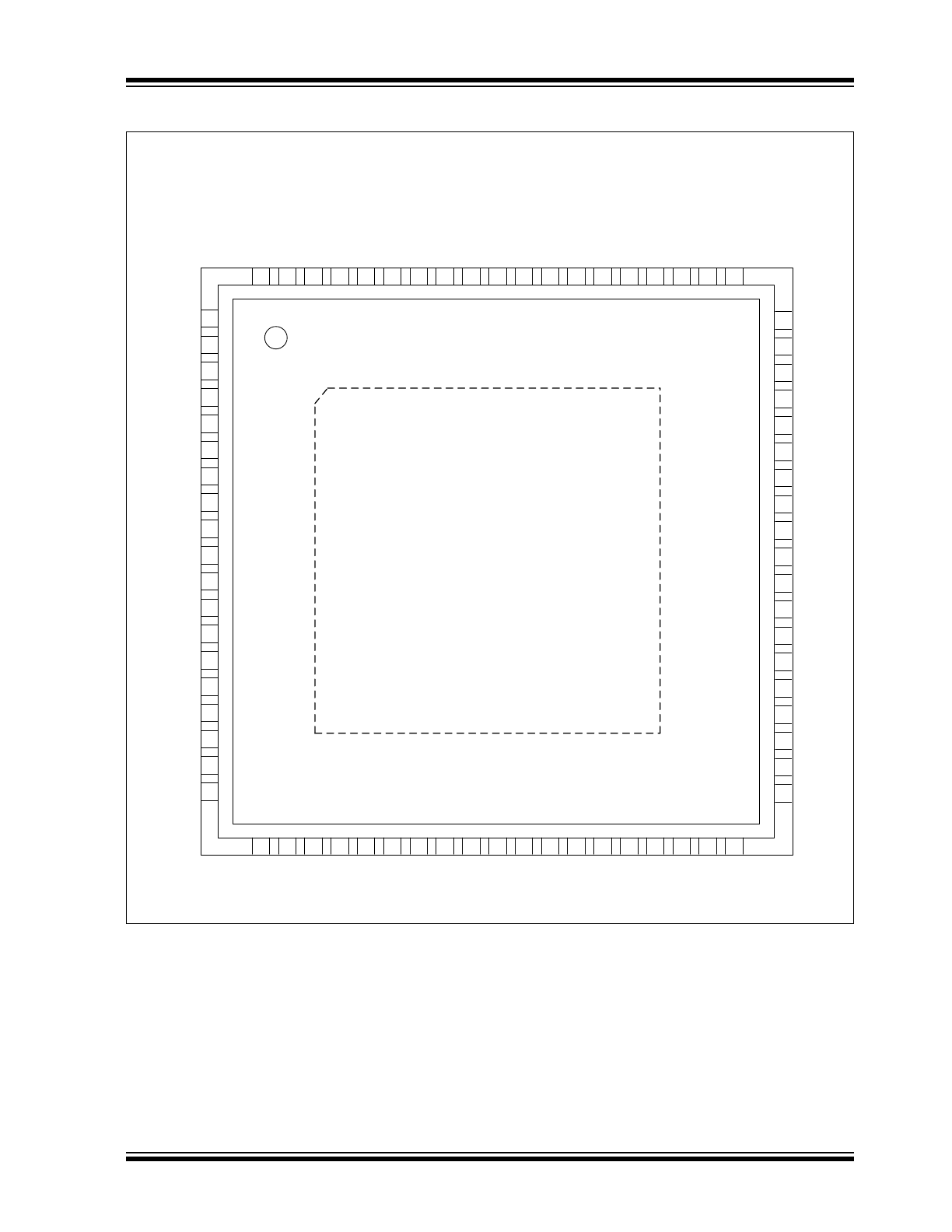

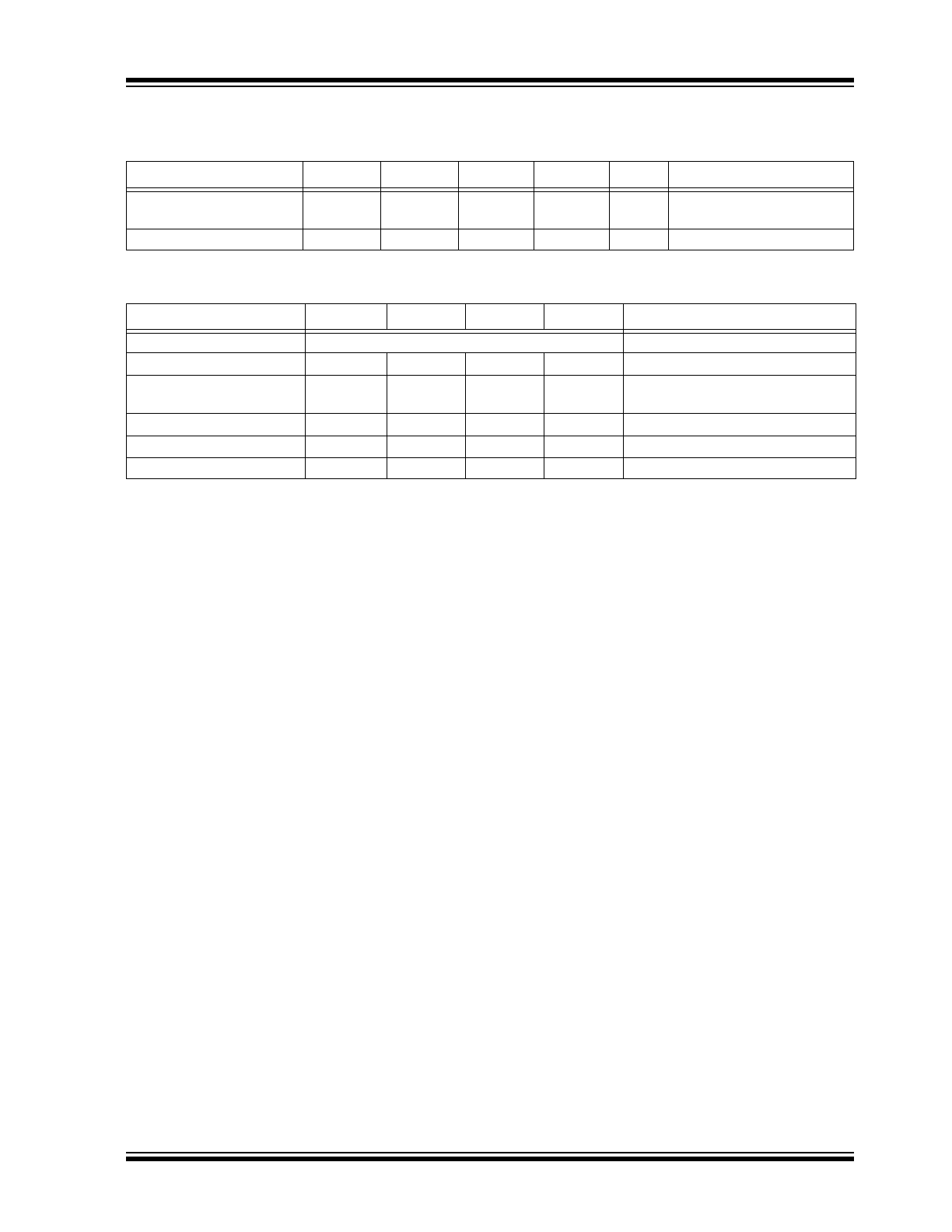

SM803XXX

Option 4: 76-Pin

9 mm x 9 mm QFN

Top View

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

REFIN1

/REFIN1

DNC

DNC

DNC

FBIN1

/FBIN1

FBIN2

/FBIN2

XTAL_IN

XTAL_OUT

VSS

REFIN2

/REFIN2

VSS

DNC

DNC

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

53

52

54

55

56

57

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

VD

DA

P2

VD

D

QC

1

VD

DO

C

/QC1

VS

S

QC

2

/Q

C

2

QC

3

VD

DO

C

/Q

C

3

OE

C

QD

1

VD

DO

D

/QD1

V

DDO

D

FS

D

FS

C

OED

QD2

/QD2

QD3

/QD3

VSS

DNC

DNC

DNC

DNC

DNC

QB3

VSS

VDDOD

VDDOB

/QB3

QB2

/QB2

OEB

FS

B

FS

A

VD

DO

B

QB

1

/QB1

VD

DO

B

OE

A

QA

3

VD

DO

A

/QA

3

QA

2

VS

S

/QA

2

QA

1

VD

DO

A

/QA1

VD

DO

A

VD

D

VD

DA

P

1

EPAD

VDDI1/2

VDD

OC

2018 Microchip Technology Inc.

DS20005667A-page 3

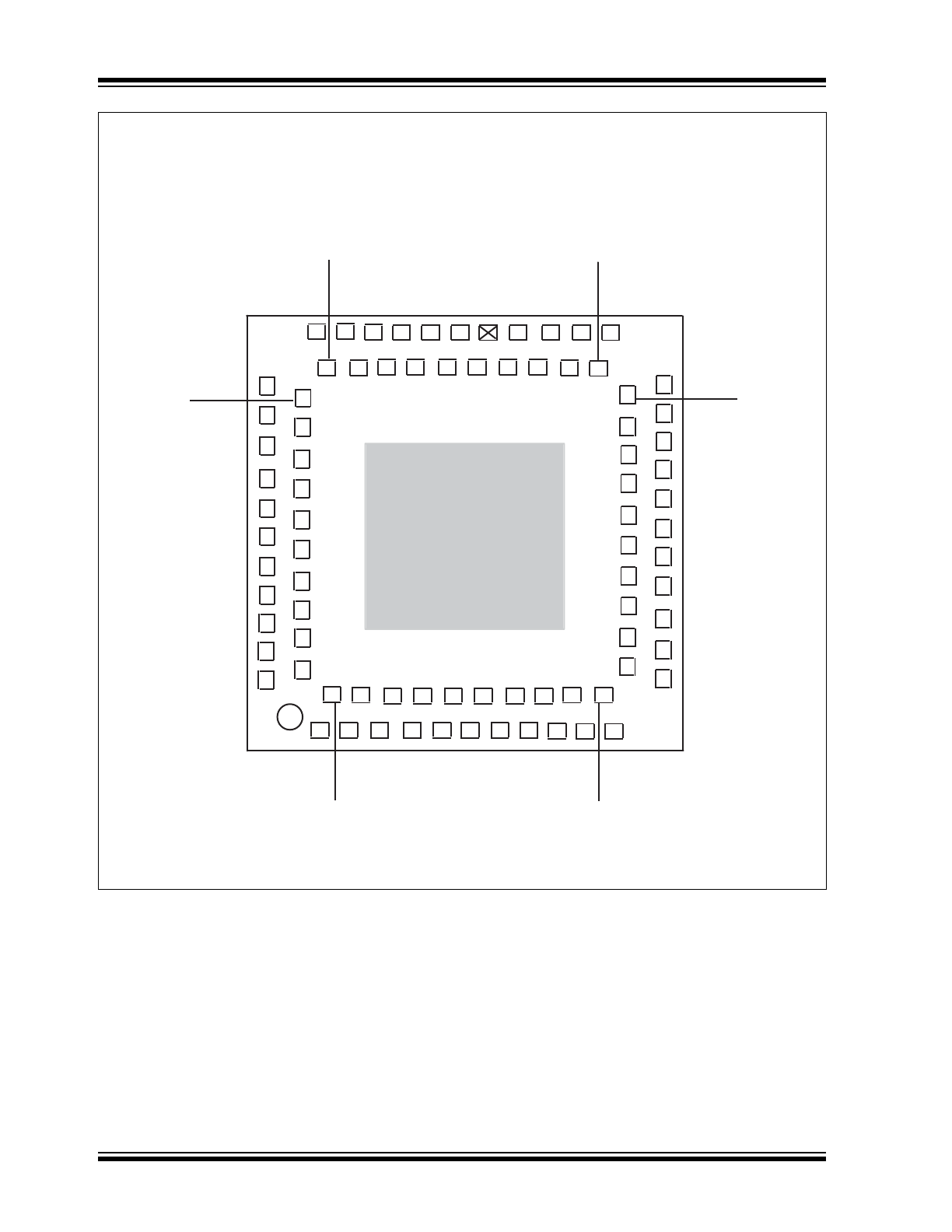

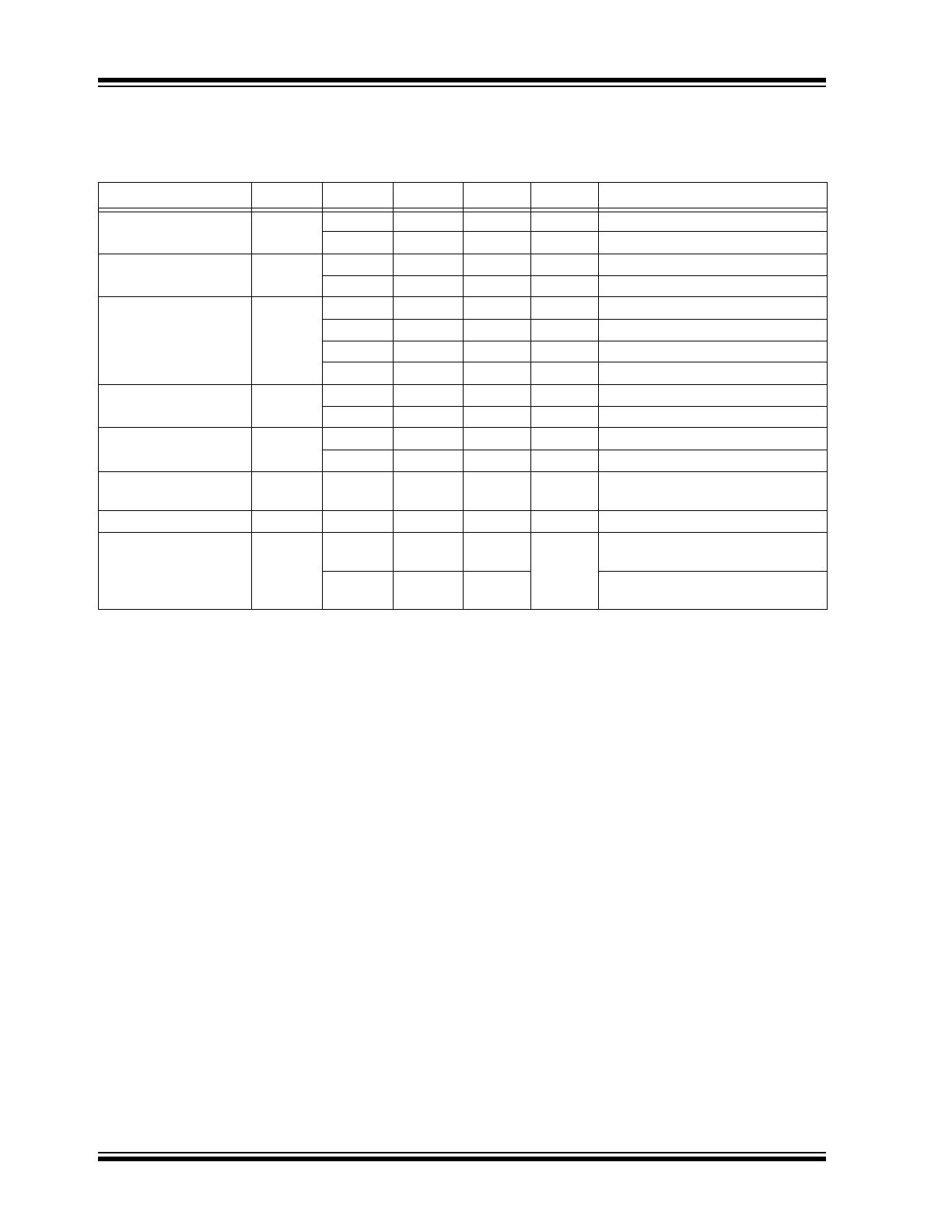

SM803XXX

SM803XXX

Option 5: 84-Pin

7 mm x 7 mm QFN

Top View

VSSAP2

VDD

QC1

/QC1

QC2

/QC2

QC3

/QC3

XIN

XOUIT

VSSI2

DNC

DNC

VDDI2

NC

DNC

QD1

/QD1

FSD

VSSI1

GND

DNC

OEB

41

44

A

B

A

A

A

B

B

B

1

2

3

4

5

6

7

8

9

10

11

1

2

3

4

5

6

7

8

9

10

12

13

14

15

16

17

18

19

20

21

22

11

12

13

14

15

16

17

18

19

20

23

24

25

26

27

28

29

30

31

32

33

21

22

23

24

25

26

27

28

29

30

34

35

36

37

38

39

40

42

43

31

32

33

34

35

36

37

38

39

40

QD2

/QD2

QD3

/QD3

OED

VDDOD

VDDOD

VSSOD

DNC

DNC

DNC

VDDOB

VDDOB

VSSOB

GND

DNC

DNC

QB3

/QB3

QB2

/QB2

QB1

/QB1

QA3

/QA3

QA2

/QA2

QA1

/QA1

VDD

VSSAP1

FSA

FSB

VSSOB

OEA

VSSOA

VSSOA

VDDOA

VDDOA

NC

VDDAP1

FSC

VSSOD

OEC

VDDOC

NC

VSSOC

VSSOC

VDDOC

NC

VDDAP2

/REFIN1

REFIN1

EP

AD

REFIN2

/REFIN2

/FBIN2

FBIN2

VDDI1

/FBIN1

FBIN1

SM803XXX

DS20005667A-page 4

2018 Microchip Technology Inc.

2018 Microchip Technology Inc.

DS20005667A-page 5

SM803XXX

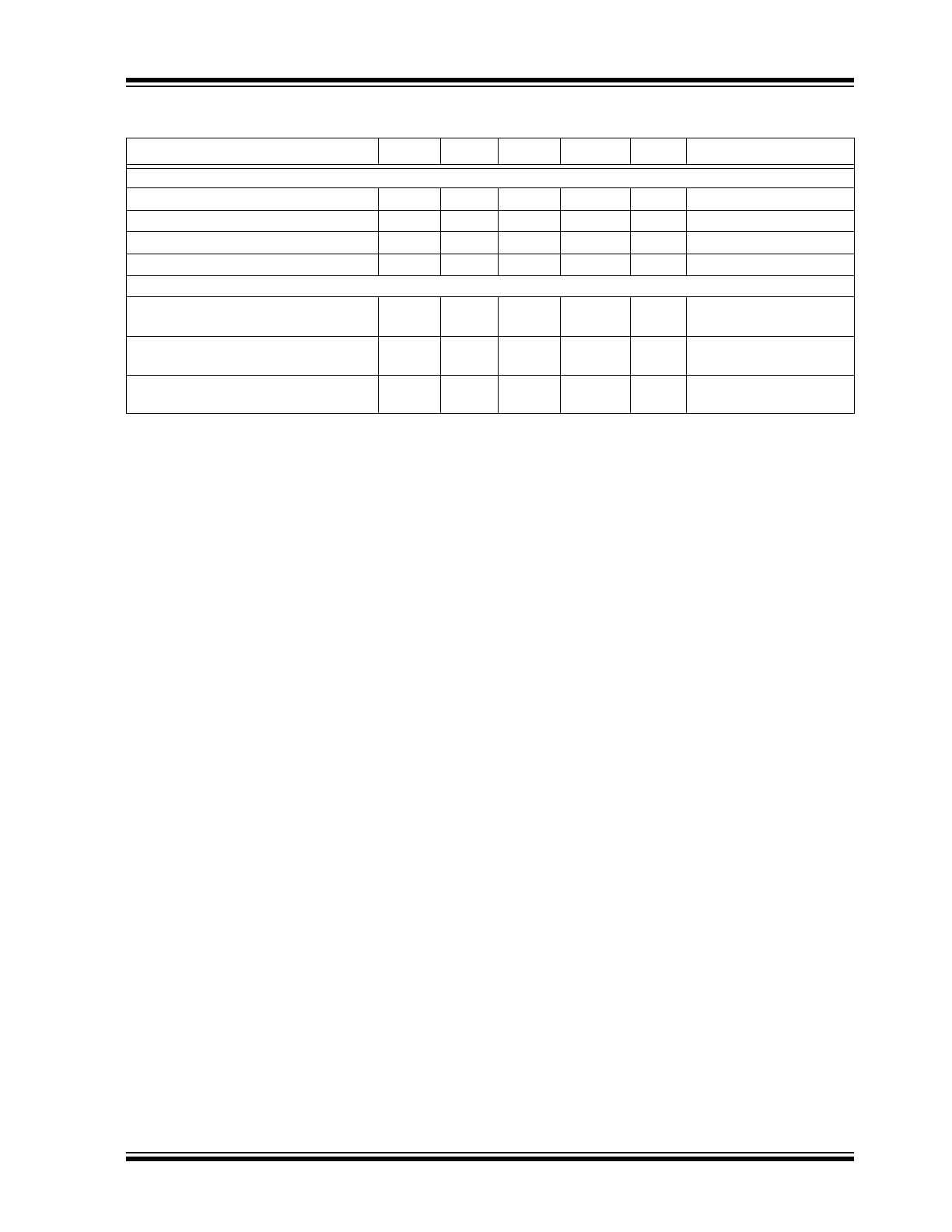

1.0

ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings †

Supply Voltage (V

DD

, V

DDA

, V

DDI

, V

DDO

).................................................................................................................+4.6V

Input Voltage (V

IN

) .................................................................................................................................. –0.50V to +4.6V

ESD Machine Model .................................................................................................................................................200V

ESD Human Body Model ........................................................................................................................................2000V

Operating Ratings ††

Supply Voltage (V

DD

, V

DDO

) ............................................................................................................. +2.375V to +3.465V

†

Notice: Exceeding the absolute maximum ratings may damage the device.

††

Notice: The device is not guaranteed to function outside its operating ratings.

ELECTRICAL CHARACTERISTICS

Electrical Characteristics:

Unless otherwise indicated, typical values are for T

A

= +25°C. The min. and max. values

are for –40°C ≤ T

A

≤ +85°C.

Parameters

Sym.

Min.

Typ.

Max.

Units

Conditions

Supply Voltage

V

DD

, V

DDO

2.375

2.5

2.625

V

2.5V Operation

3.135

3.3

3.465

3.3V Operation

Analog Supply Voltage

V

DDI1,

V

DDI2

2.375

—

3.465

V

—

PLL Core Voltage

V

DDA

2.375

—

3.465

V

—

PLL Core Current

Consumption

I

DDA

—

—

60

mA

Per active PLL

Analog Current

Consumption

I

DDI

—

—

10

mA

—

Output Stage Current

Consumption

I

DDO

—

—

70

mA

Per output bank, unloaded

SPI and Miscellaneous

Logic

I

DD

—

—

8

mA

—

LVPECL DC ELECTRICAL CHARACTERISTICS

Electrical Characteristics:

V

DDCore

= V

DD

= V

DD0

= 3.3V ±5% or 2.5V ±5%, T

A

= –40°C to +85°C, unless otherwise

noted. R

L

= 50Ω to V

DDO

– 2V.

Parameters

Sym.

Min.

Typ.

Max.

Units

Conditions

Output High Voltage

V

OH

V

DDO

–

1.35

V

DDO

–

1.01

V

DDO

– 0.8

V

50Ω to V

DDO

2V

Output Low Voltage

V

OL

V

DDO

– 2

V

DDO

–

1.78

V

DDO

– 1.6

V

50Ω to V

DDO

– 2V

Peak-to-Peak Output

Voltage

V

SWING

0.65

0.77

0.95

V

Figure 5-3

SM803XXX

DS20005667A-page 6

2018 Microchip Technology Inc.

LVDS DC ELECTRICAL CHARACTERISTICS

Electrical Characteristics:

V

DDCore

= V

DD

= V

DD0

= 3.3V ±5% or 2.5V ±5%, T

A

= –40°C to +85°C, unless otherwise

noted. R

L

= 100Ω between Q and /Q.

Parameters

Sym.

Min.

Typ.

Max.

Units

Conditions

Differential Output Voltage

V

OD

245

350

454

mV

Figure 5-3

Common Mode Voltage

V

CM

1.125

1.2

1.375

V

—

Output High Voltage

V

OH

1.248

1.375

1.602

V

—

Output Low Voltage

V

OL

0.898

1.025

1.252

V

—

HCSL DC ELECTRICAL CHARACTERISTICS

Electrical Characteristics:

V

DDCore

= V

DD

= V

DD0

= 3.3V ±5% or 2.5V ±5%, T

A

= –40°C to +85°C, unless otherwise

noted. R

L

= 50Ω to V

SS

.

Parameters

Sym.

Min.

Typ.

Max.

Units

Conditions

Output High Voltage

V

OH

660

700

850

mV

—

Output Low Voltage

V

OL

–150

0

27

mV

—

Crossing Point Voltage

V

CROSS

—

350

—

V

—

LVCMOS DC ELECTRICAL CHARACTERISTICS

Electrical Characteristics:

V

DDCore

= V

DD

= V

DD0

= 3.3V ±5% or 2.5V ±5%, T

A

= –40°C to +85°C, unless otherwise

noted. R

L

= 50Ω to V

DDO

/2.

Parameters

Sym.

Min.

Typ.

Max.

Units

Conditions

Output High Voltage

V

OH

V

DD

– 0.8

—

—

V

Highest Drive (Default)

Output Low Voltage

V

OL

—

—

0.5

V

—

Input High Voltage

V

IH

V

DD

0.7

—

V

DD

+ 0.3

V

—

Input Low Voltage

V

IL

V

SS

0.3

—

0.3 × V

DD

V

—

Input High Current

I

IH

—

—

5

µA

V

DD

= V

IN

= 3.465V

Input Low Current

I

IL

150

—

—

µA

V

DD

= 3.465V, V

IN

= 0V

2018 Microchip Technology Inc.

DS20005667A-page 7

SM803XXX

REF_IN DC ELECTRICAL CHARACTERISTICS

Electrical Characteristics:

V

DD

= 3.3V ±5% to 2.5V ±5%, T

A

= –40°C to +85°C.

Parameters

Sym.

Min.

Typ.

Max.

Units

Conditions

Input Common Mode

Voltage

V

CMR

0.3

—

V

DD

– 0.3

V

—

Input Voltage Swing

V

SWING

0.2

—

—

V

PP

—

CRYSTAL CHARACTERISTICS

Parameters

Min.

Typ.

Max.

Units

Conditions

Mode of Oscillation

Fundamental, Parallel Resonant

12 pF load typical

Frequency

12

—

62.5

MHz

—

Equivalent Series

Resistance (ESR)

—

—

60

Ω

—

Load Capacitance, C

L

—

12

±0.5

pF

—

Shunt Capacitor, C0

—

1

2.5

pF

—

Correlation Drive Level

—

10

100

µW

—

SM803XXX

DS20005667A-page 8

2018 Microchip Technology Inc.

AC ELECTRICAL CHARACTERISTICS

Electrical Characteristics:

V

DD

= V

DDO1/2

= 3.3V ±5% or 2.5V ±5%; V

DD

= 3.3V ±5%, V

DDO1/2

= 3.3V ±5% or 2.5V

±5%; T

A

= –40°C to +85°C

Parameters

Sym.

Min.

Typ.

Max.

Units

Conditions

Input Frequency

F

IN

12

—

62.5

MHz

XO

12

—

850

MHz

Reference input

Output Frequency

F

OUT

12

—

850

MHz

LVPECL, LVDS, HCSL

12

—

250

MHz

LVCMOS

Output Rise/Fall Time

(

Note 1

)

T

R

/T

F

85

135

350

ps

LVPECL output

85

140

300

ps

LVDS output

175

200

400

ps

HCSL output

100

200

400

ps

LVCMOS output (default drive)

Output Duty Cycle

ODC

45

50

55

%

All output frequencies

48

50

52

%

< 350 MHz output frequencies

Input to Output

Propagation Delay

T

pd

100

—

100

ps

ZDB mode

—

4

—

ns

Synthesizer/Bypass mode

Output-to-Output Skew

(

Note 2

)

T

SKEW

—

—

50

ps

Note 3

, same output bank

PLL Lock Time

T

LOCK

—

5

20

ms

—

RMS Phase Jitter

(

Note 4

,

5

)

T

jit

(

)

—

182

—

fs

Integration range

(12 kHz - 20 MHz)

—

74

—

Integration range

(1.875 MHz - 20 MHz)

Note 1:

See

Figure 5-4

.

2:

Output-to-output skew is defined as skew between outputs at the same supply voltage and with equal load

conditions. It is measured at the output differential crossing points.

3:

Output-to-output skew is only defined for outputs in the same PLL bank [A:B, C:D] with the same output

logic type setting.

4:

All phase noise measurements were taken with an Agilent 5052B phase noise system.

5:

Measured using a 50 MHz crystal as the input reference source. If using an external reference input, use a

low phase noise source. With an external reference, the phase noise will follow the input source phase

noise up to about 1 MHz.

TEMPERATURE SPECIFICATIONS (

Note 1

)

Parameters

Sym.

Min.

Typ.

Max.

Units

Conditions

Temperature Ranges

Ambient Temperature Range

T

A

–40

—

+85

°C

—

Lead Temperature

—

—

+260

—

°C

Soldering, 20s

Case Temperature

—

—

+115

—

°C

—

Storage Temperature Range

T

S

–65

—

+150

°C

—

Package Thermal Resistances

Junction Thermal Resistance, 7 x 7

QFN-84Ld

JA

—

23.4

—

°C/W

—

Junction Thermal Resistance, 7 x 7

QFN Still Air QFN-48Ld

θ

JA

—

24.22

—

°C/W

—

Junction Thermal Resistance, 9 x 9

QFN Still Air QFN-76Ld

θ

JA

—

25

—

°C/W

—

Note 1:

The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable

junction temperature and the thermal resistance from junction to air (i.e., T

A

, T

J

, θ

JA

). Exceeding the

maximum allowable power dissipation will cause the device operating junction temperature to exceed the

maximum +85°C rating. Sustained junction temperatures above +85°C can impact the device reliability.

2018 Microchip Technology Inc.

DS20005667A-page 9

SM803XXX

SM803XXX

DS20005667A-page 10

2018 Microchip Technology Inc.

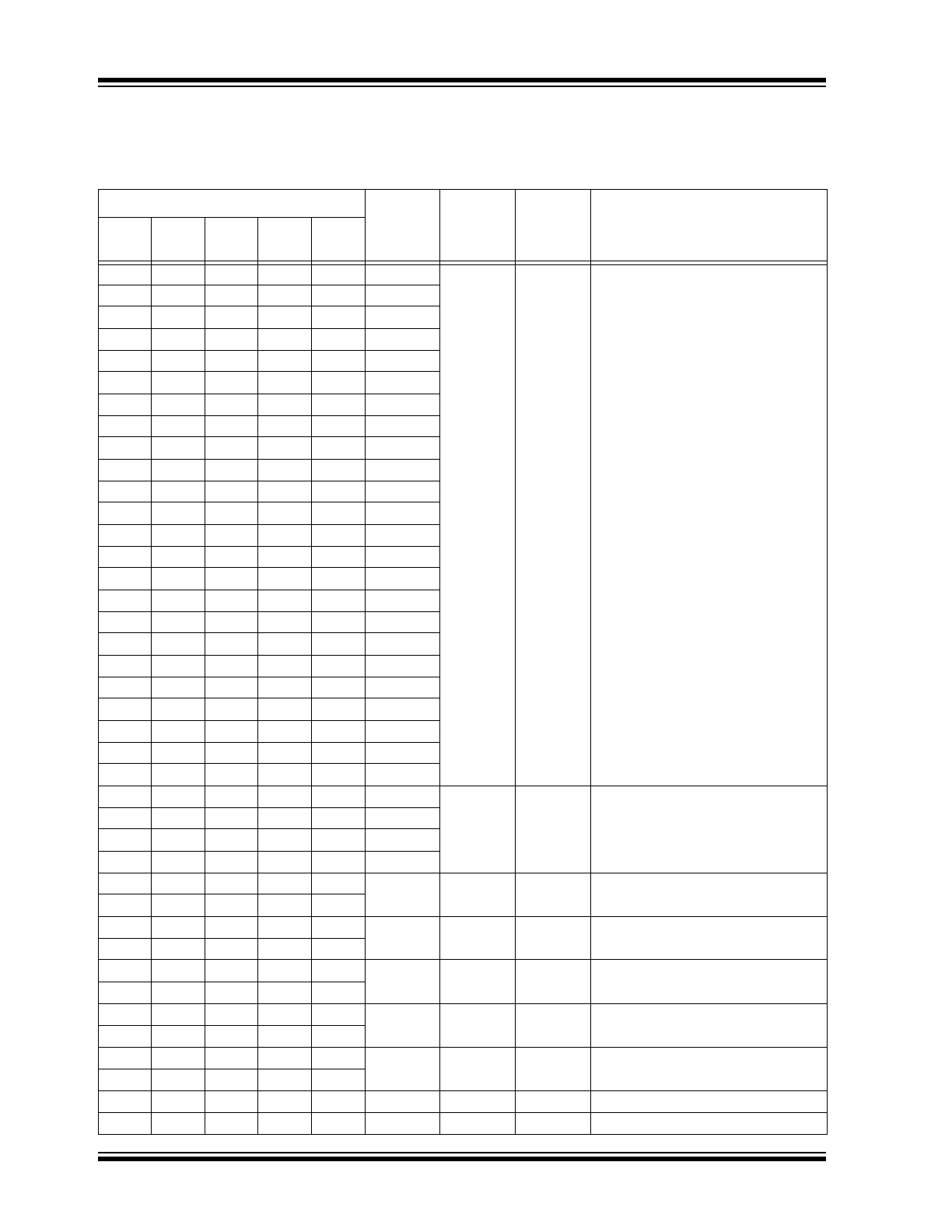

2.0

PIN DESCRIPTIONS

The descriptions of the pins are listed in

Table 2-1

.

TABLE 2-1:

PIN FUNCTION TABLE

Pin Numbers by Package Option

Pin Name

Pin Type

Pin Level

Pin Function

#1

48-pin

#2

48-pin

#3

48-pin

#4

76-pin

#5

84-pin

34

34

34

72

A19

QA1

O,

(DIF/SE)

LVPECL

LVDS

HCSL

LVCMOS

(Q only)

Differential /

SE Clock Output (LVCMOS)

35

35

35

74

A20

/QA1

31

31

31

69

A17

QA2

32

32

32

70

A18

/QA2

28

—

—

65

A15

QA3

30

—

—

67

A16

/QA3

26

27

28

61

A13

QB1

27

28

29

63

A14

/QB1

22

22

22

55

A10

QB2

24

24

24

56

A11

/QB2

—

—

—

52

A8

QB3

—

—

—

54

A9

/QB3

3

3

3

22

A36

QC1

5

5

5

24

A37

/QC1

6

6

6

26

A38

QC2

7

7

7

27

A39

/QC2

—

—

—

29

A40

QC3

—

—

—

31

A41

/QC3

8

9

8

33

A42

QD1

10

11

10

35

A43

/QD1

12

—

—

40

A1

QD2

14

—

—

41

A2

/QD2

15

15

15

43

A3

QD3

16

16

16

45

A4

/QD3

—

—

27

59

B12

FSA

I, (SE)

LVCMOS

Frequency Select,

on-chip 75 kΩ pull-up

1 = Primary Selection

0 = Secondary Selection

—

—

25

58

B11

FSB

—

—

13

38

B40

FSC

—

—

11

37

A44

FSD

2

2

2

1, 21

A21

V

DD

PWR

—

Power Supply

36

36

36

75

A35

29

30

29

66, 71

B18

V

DDOA

PWR

—

Power Supply for Outputs QA1

3

33

33

33

73

B17

23

23

23

53, 60

B8

V

DDOB

PWR

—

Power Supply for Outputs QB1

3

—

—

—

62

B9

4

4

4

23

B33

V

DDOC

PWR

—

Power Supply for Outputs QC1

3

—

—

—

28, 30

B37

9

10

9

34

B2

V

DDOD

PWR

—

Power Supply for Outputs QD1

3

13

14

14

36, 44

B3

37

37

37

76

B20

V

DDAP1

PWR

—

Power Supply for PLL1

1

1

1

20

B31

V

DDAP2

PWR

—

Power Supply for PLL2