FDC37C669

PC 98/99 Compliant Super I/O Floppy

Disk Controller with Infrared Support

FEATURES

• 5 Volt Operation

• Intelligent Auto Power Management

• 16 Bit Address Qualification (Optional)

• 2.88MB Super I/O Floppy Disk Controller

-

Licensed CMOS 765B Floppy Disk Controller

-

Software and Register Compatible with SMSC's

Proprietary 82077AA Compatible Core

-

Supports Two Floppy Drives Directly

-

Supports Vertical Recording Format

-

16 Byte Data FIFO

-

100% IBM Compatibility

-

Detects All Overrun and Underrun Conditions

-

Sophisticated Power Control Circuitry (PCC)

Including Multiple Powerdown Modes for

Reduced Power Consumption

-

DMA Enable Logic

-

Data Rate and Drive Control Registers

-

Swap Drives A and B

-

Non-Burst Mode DMA option

-

48 Base I/O Address, Seven IRQ and Three

DMA Options

• Floppy Disk Available on Parallel Port Pins

• Enhanced Digital Data Separator

-

2 Mbps, 1 Mbps, 500 Kbps, 300 Kbps, 250 Kbps

Data Rates

-

Programmable Precompensation Modes

• Serial

Ports

-

Two High Speed NS16C550 Compatible UARTs

with Send/Receive 16 Byte FIFOs

-

Supports 230k and 460k Baud

-

Programmable Baud Rate Generator

-

Modem Control Circuitry

-

Infrared - IrDA (HPSIR) and Amplitude Shift

Keyed IR (ASKIR)

-

Alternate IR Pins (Optional)

-

96 Base I/O Address and Eight IRQ Options

• Multi-Mode Parallel Port with ChiProtect

- Standard

Mode

-

IBM PC/XT, PC/AT, and PS/2 Compatible

Bidirectional Parallel Port

-

Enhanced Parallel Port (EPP) Compatible

-

EPP 1.7 and EPP 1.9 (IEEE 1284 Compliant)

-

Enhanced Capabilities Port (ECP) Compatible

(IEEE 1284 Compliant)

-

Incorporates ChiProtect Circuitry for Protection

Against Damage Due to Printer Power-On

-

192 Base I/O Address, Seven IRQ and Three

DMA Options

• ISA Host Interface

• IDE Interface (Optional)

-

On-Chip Decode and Select Logic Compatible

with IBM PC/XT and PC/AT Embedded Hard

Disk Drives

-

48 Base I/O Address and Seven IRQ Options

• Game Port Select Logic

-

48 Base I/O Addresses

• General Purpose Address Decoder

-

16 Byte Block decode

-

48 Base I/O Address Options

• 100 Pin QFP and TQFP Packages; Lead-Free RoHS

Compliant Packages also available

ORDER NUMBER(S)

FDC37C669QFP for 100 pin, QFP Package

FDC37C669-MS for 100 pin, QFP Lead-Free RoHS Compliant Package

FDC37C669TQFP for 100 pin, TQFP Package

FDC37C669-MT for 100 pin, TQFP Lead-Free RoHS Compliant Package

2

TABLE OF CONTENTS

FEATURES .................................................................................................................................................................. 1

GENERAL DESCRIPTION .......................................................................................................................................... 3

PIN CONFIGURATION ................................................................................................................................................. 4

DESCRIPTION OF PIN FUNCTIONS........................................................................................................................... 6

FUNCTIONAL DESCRIPTION................................................................................................................................... 17

SUPER

I/O

REGISTERS ....................................................................................................................................... 17

HOST

PROCESSOR INTERFACE ....................................................................................................................... 17

FLOPPY

DISK

CONTROLLER ............................................................................................................................. 18

FLOPPY DISK CONTROLLER INTERNAL REGISTERS ...................................................................................... 18

COMMAND SET/DESCRIPTIONS ............................................................................................................................ 41

INSTRUCTION SET.................................................................................................................................................... 45

PARALLEL PORT FLOPPY DISK CONTROLLER ...................................................................................................... 71

SERIAL PORT (UART) ............................................................................................................................................... 73

INFRARED INTERFACE ............................................................................................................................................. 87

PARALLEL PORT ...................................................................................................................................................... 88

IBM XT/AT COMPATIBLE, BI-DIRECTIONAL AND EPP MODES ........................................................................ 90

EXTENDED

CAPABILITIES PARALLEL PORT.................................................................................................... 96

AUTO POWER MANAGEMENT ................................................................................................................................ 108

INTEGRATED DRIVE ELECTRONICS INTERFACE .............................................................................................. 114

CONFIGURATION .................................................................................................................................................... 118

OPERATIONAL DESCRIPTION ............................................................................................................................... 136

MAXIMUM

GUARANTEED RATINGS ................................................................................................................ 136

DC

ELECTRICAL

CHARACTERISTICS ............................................................................................................ 136

TIMING DIAGRAMS ................................................................................................................................................. 139

ECP

PARALLEL

PORT TIMING .......................................................................................................................... 156

3

GENERAL DESCRIPTION

The SMSC FDC37C669 PC 95 Compatible Super I/O

Floppy Disk Controller with Infrared Support utilizes

SMSC's proven SuperCell technology for increased

product reliability and functionality. The FDC37C669 is

PC95 compliant and is optimized for motherboard

applications. The FDC37C669 supports both 1 Mbps and

2 Mbps data rates and vertical vertical recording

operation at 1 Mbps Data Rate.

The FDC37C669 incorporates SMSC's true CMOS

765B floppy disk controller, advanced digital data

separator, 16 byte data FIFO, two 16C550 compatible

UARTs, one Multi-Mode parallel port which includes

ChiProtect circuitry plus EPP and ECP support, IDE

interface, on-chip 12 mA AT bus drivers, game port chip

select and two floppy direct drive support. The true

CMOS 765B core provides 100% compatibility with IBM

PC/XT and PC/AT architectures in addition to providing

data overflow and underflow protection. The SMSC

advanced digital data separator incorporates SMSC's

patented data separator technology, allowing for ease of

testing and use. Both on-chip UARTs are compatible

with the NS16C550. One UART includes additional

support for a Serial Infrared Interface, complying with

IrDA, HPSIR, and ASKIR

formats (used by Sharp, Apple Newton, and other PDAs).

The parallel port, the IDE interface, and the game port

select logic are compatible with IBM PC/AT

architectures. The FDC37C669 incorporates

sophisticated power control circuitry (PCC). The PCC

supports multiple low power down modes.

The FDC37C669 Floppy Disk Controller incorporates

Software Configurable Logic (SCL) for ease of use. Use

of the SCL feature allows programmable system

configuration of key functions such as the FDC, parallel

port, and UARTs. The parallel port ChiProtect prevents

damage caused by the printer being powered when the

FDC37C669 is not powered.

The FDC37C669 does not require any external filter

components, and is, therefore easy to use and offers

lower system cost and reduced board area. The

FDC37C669 is software and register compatible with

SMSC's proprietary 82077AA core.

4

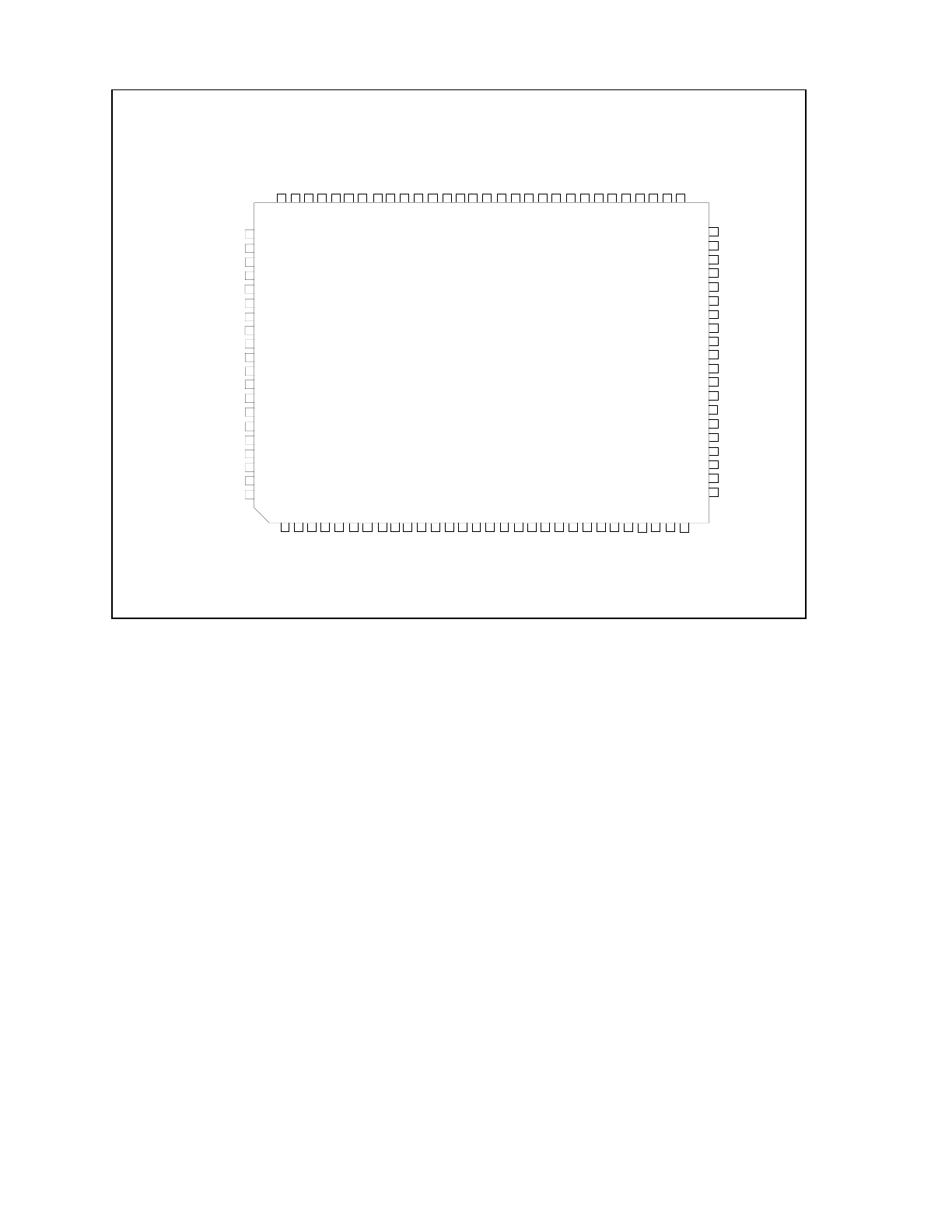

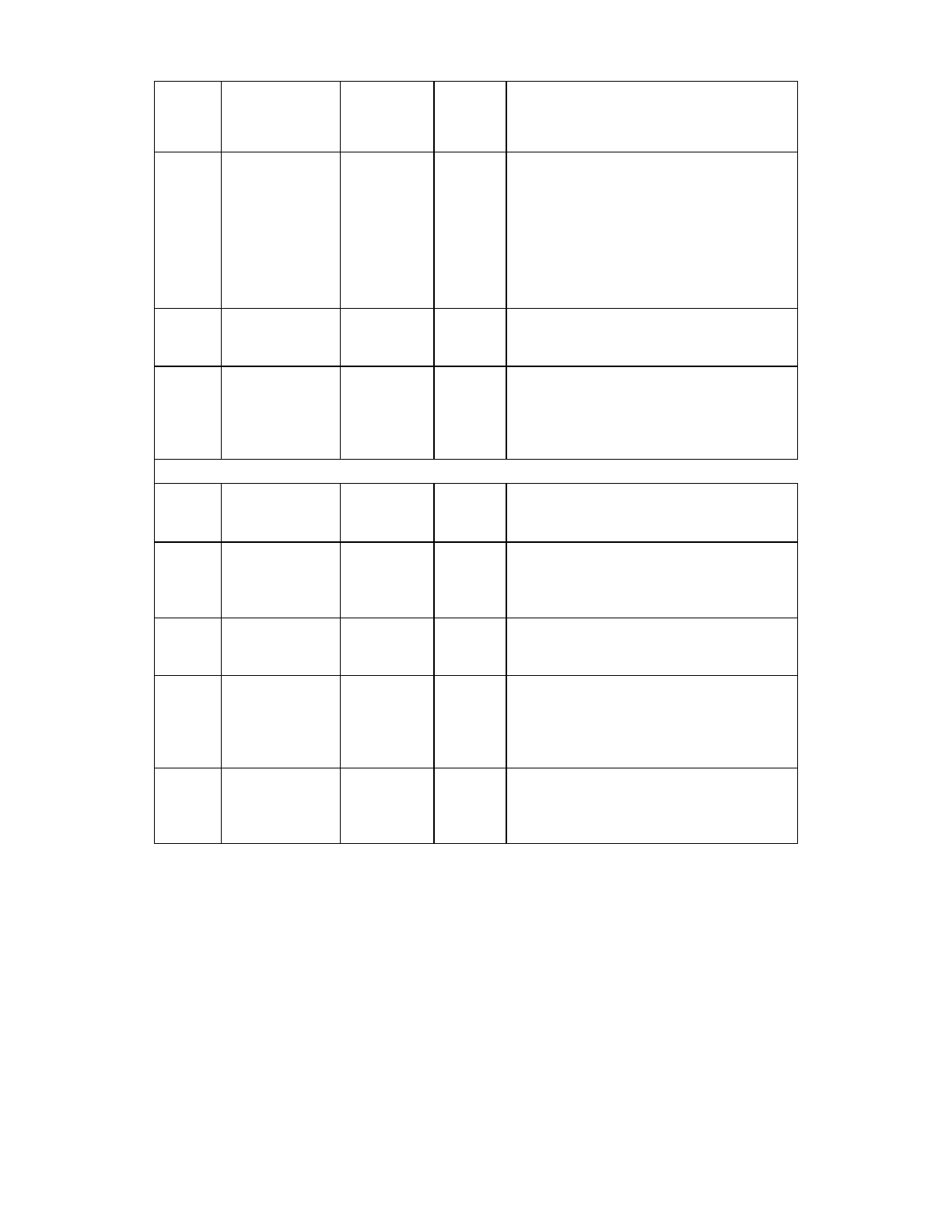

PIN CONFIGURATION

FDC37C669

100 PIN QFP

DR

V

D

EN

0

nM

T

R

0

nD

S1

nD

S0

nMTR1

VSS

nD

IR

nS

T

E

P

nW

D

A

T

A

nW

GA

T

E

nH

DS

EL

n

INDE

X

nT

RK

0

nWR

T

P

R

T

VC

C

nRD

A

T

A

n

D

SKC

H

G

DR

VD

EN1

IRQ

_

A

CL

K

1

4

DR

Q_

A

nD

A

C

K

_

A

IR

Q

IN

n

IDE

EN/IR

Q_

H

nH

DC

S0

/IRR

X

2

nHDCS1

/IR

TX2

nC

S

A0

A1

A2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

D2

D1

D0

VSS

AEN

nIOW

nIOR

A9

A8

A7

IRQ_F

IRQ_E

IRQ_D

IRQ_C

nDACK_B

TC

A6

A5

A4

A3

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

nD

SR1

TX

D1

RX

D

1

nS

T

R

O

B

E

n

A

U

T

OFD

nE

R

R

OR

nI

N

IT

nS

LCT

IN

VCC

PD

0

PD1

PD2

PD

3

VS

S

PD4

PD5

PD

6

PD

7

nA

C

K

BU

S

Y

PE

SLCT

PW

RGD/G

A

M

E

CS

RE

SE

T

D7

D6

D5

D4

DR

Q

_

B

D3

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

nRTS1

nCTS1

nDTR1

nRI1

nDCD1

nRI2

nDCD2

RXD2/IRRX

TXD2/IRTX

nDSR2

nRTS2

nCTS2

nDTR2

DRV2/ADRX/IRQ_B

VSS

nDACK_C

A10

NC

DRQ_C

IOCHRDY

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

5

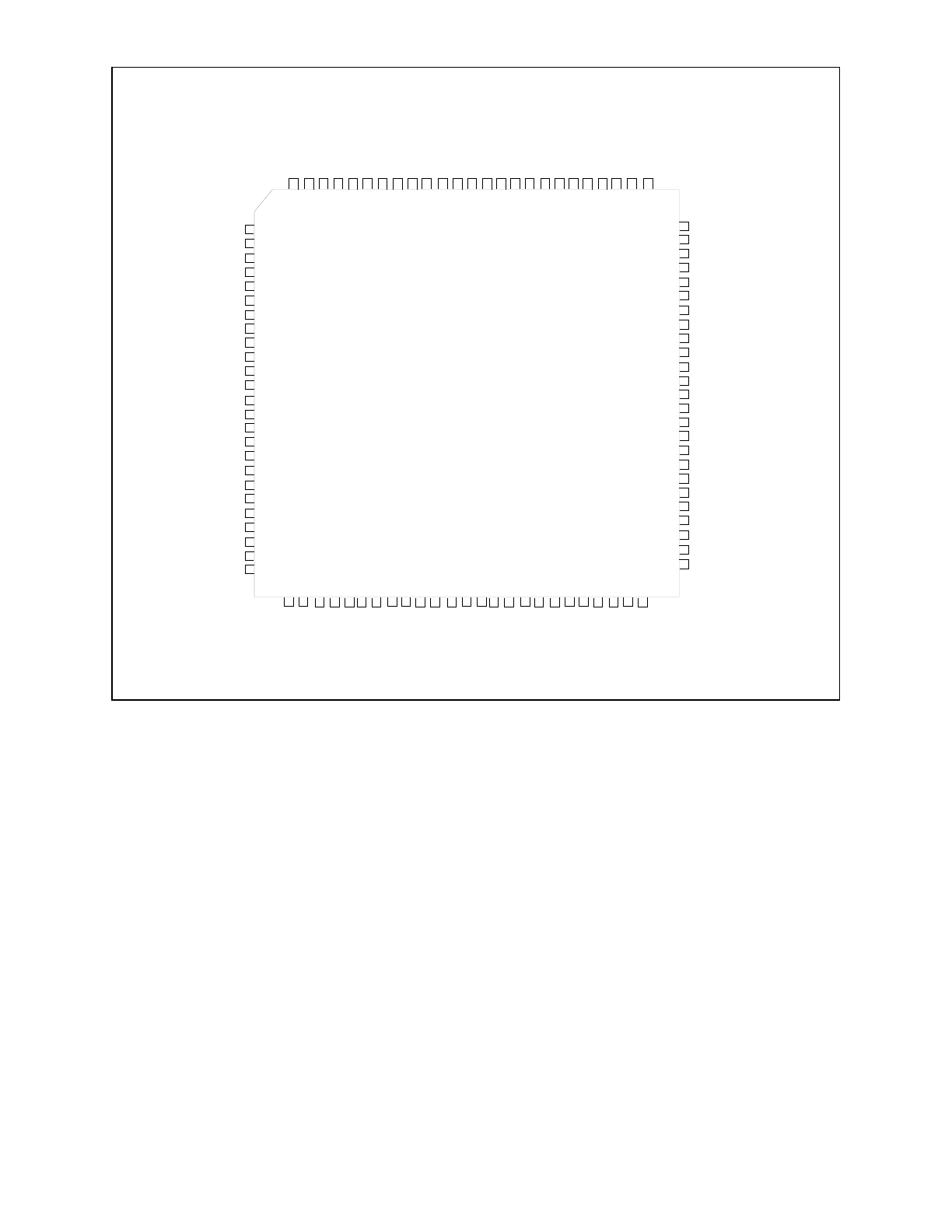

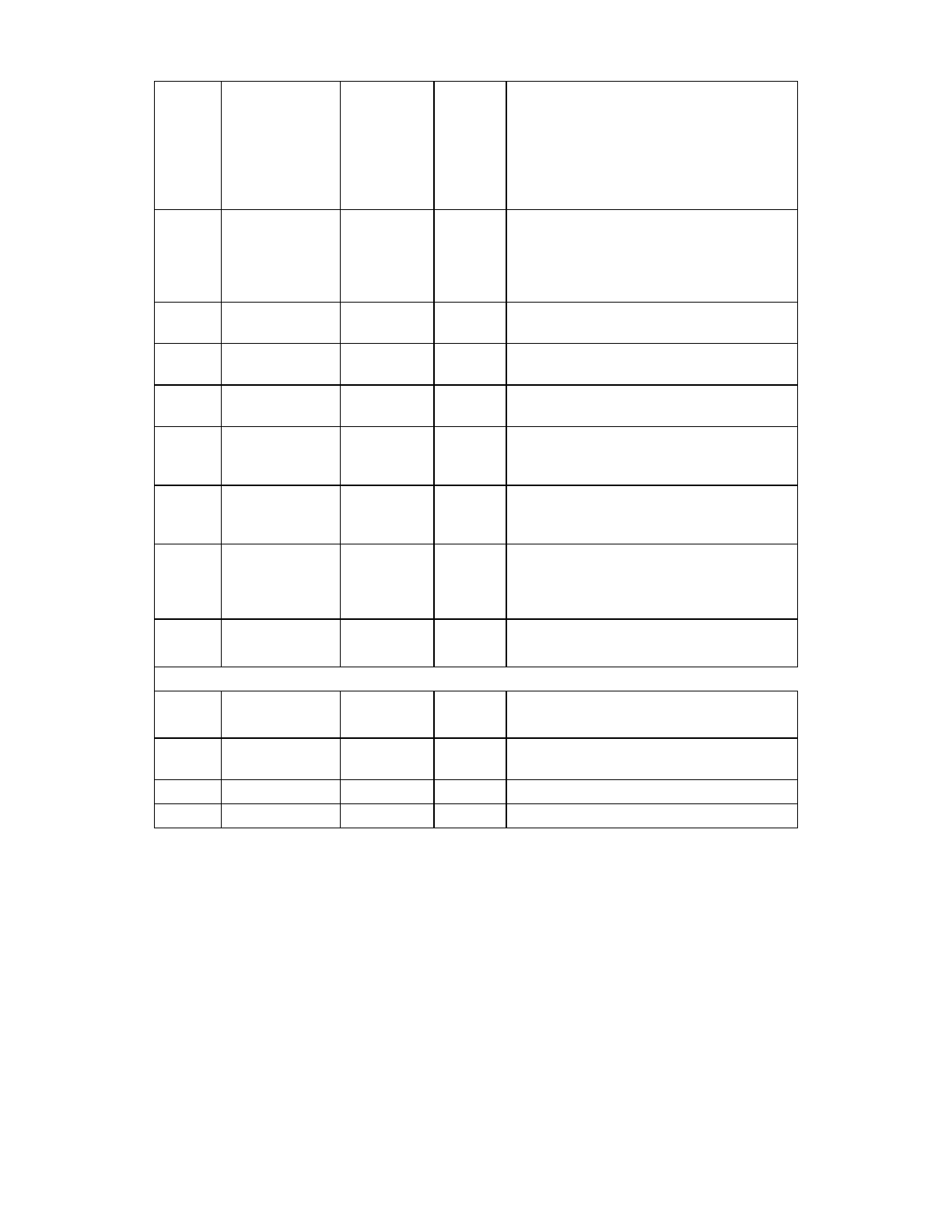

FDC37C669

100 PIN TQFP

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

DRVDEN0

nMTR0

nDS1

nDS0

nMTR1

VSS

nDIR

nSTEP

nWDATA

nWGATE

nHDSEL

nINDEX

nTRK0

nWRTPRT

VCC

nRDATA

nDSKCHG

DRVDEN1

IRQ_A

CLK14

DRQ_A

nDACK_A

IRQIN

nIDEEN/IRQ_H

nHDCS0/IRRX2

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

nERROR

nINIT

nSLCTIN

VCC

PD0

PD1

PD2

PD3

VSS

PD4

PD5

PD6

PD7

nACK

BUSY

PE

SLCT

PWRGD/GAMECS

RESET

D7

D6

D5

D4

DRQ_B

D3

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

nHD

C

S

1

/I

R

T

X

2

nC

S

A0

A1

A2

A3

A4

A5

A6

TC

nD

A

C

K_B

IR

Q

_

C

IR

Q

_

D

IR

Q

_

E

IR

Q

_

F

A7

A8

A9

nI

O

R

nI

O

W

AEN

VS

S

D0

D1

D2

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

IO

CH

RD

Y

DRQ

_

C

NC

A1

0

nD

A

C

K_

C

VS

S

DR

V2

/A

D

R

X/

IR

Q

_

B

nD

TR2

nC

TS

2

nR

T

S

2

nD

SR2

TXD

2

/I

R

T

X

RX

D2

/I

R

R

X

nD

C

D

2

nR

I2

nD

C

D

1

nR

I1

nDTR

1

nC

TS1

nR

T

S

1

nDS

R

1

TXD

1

RXD1

nS

T

R

O

B

E

nA

UT

O

F

D

6

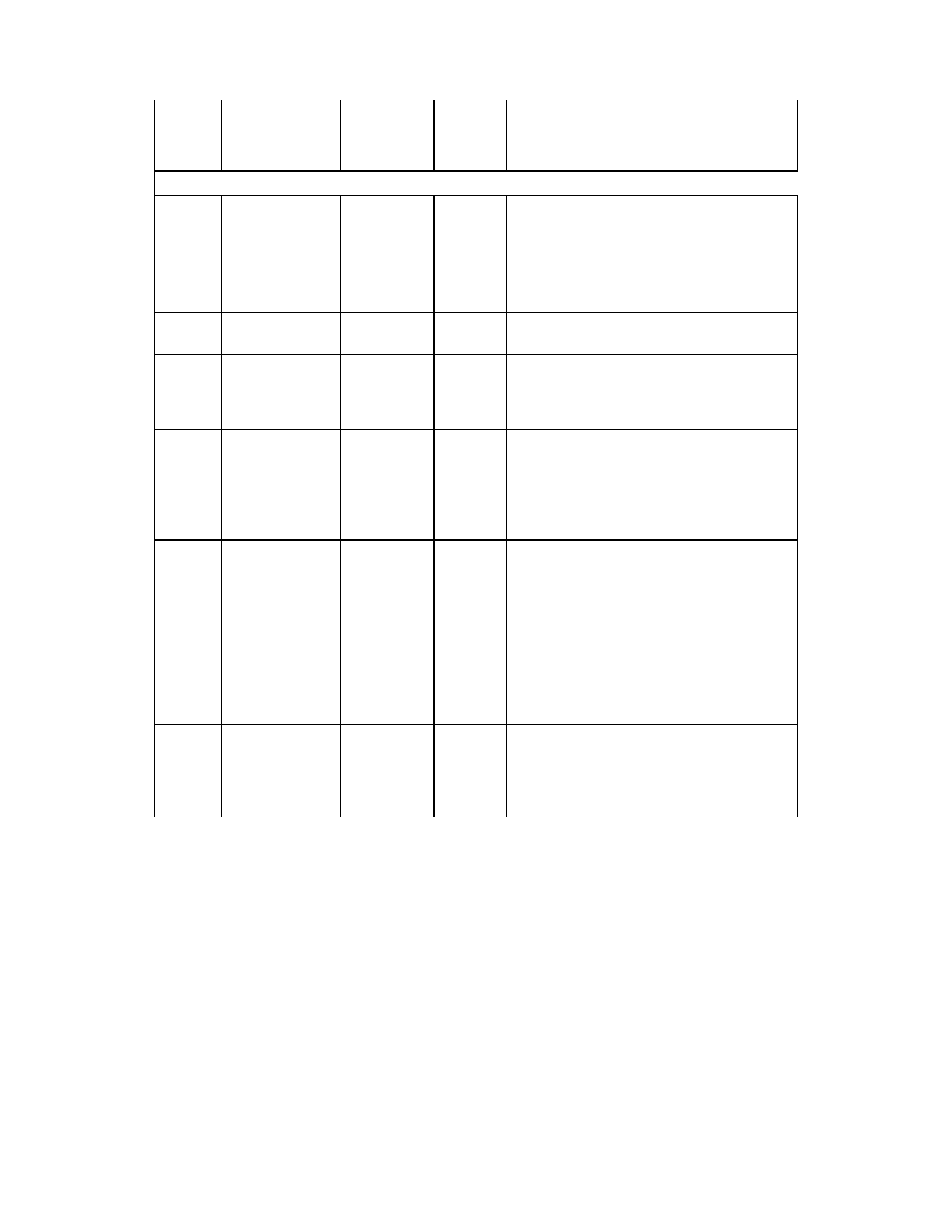

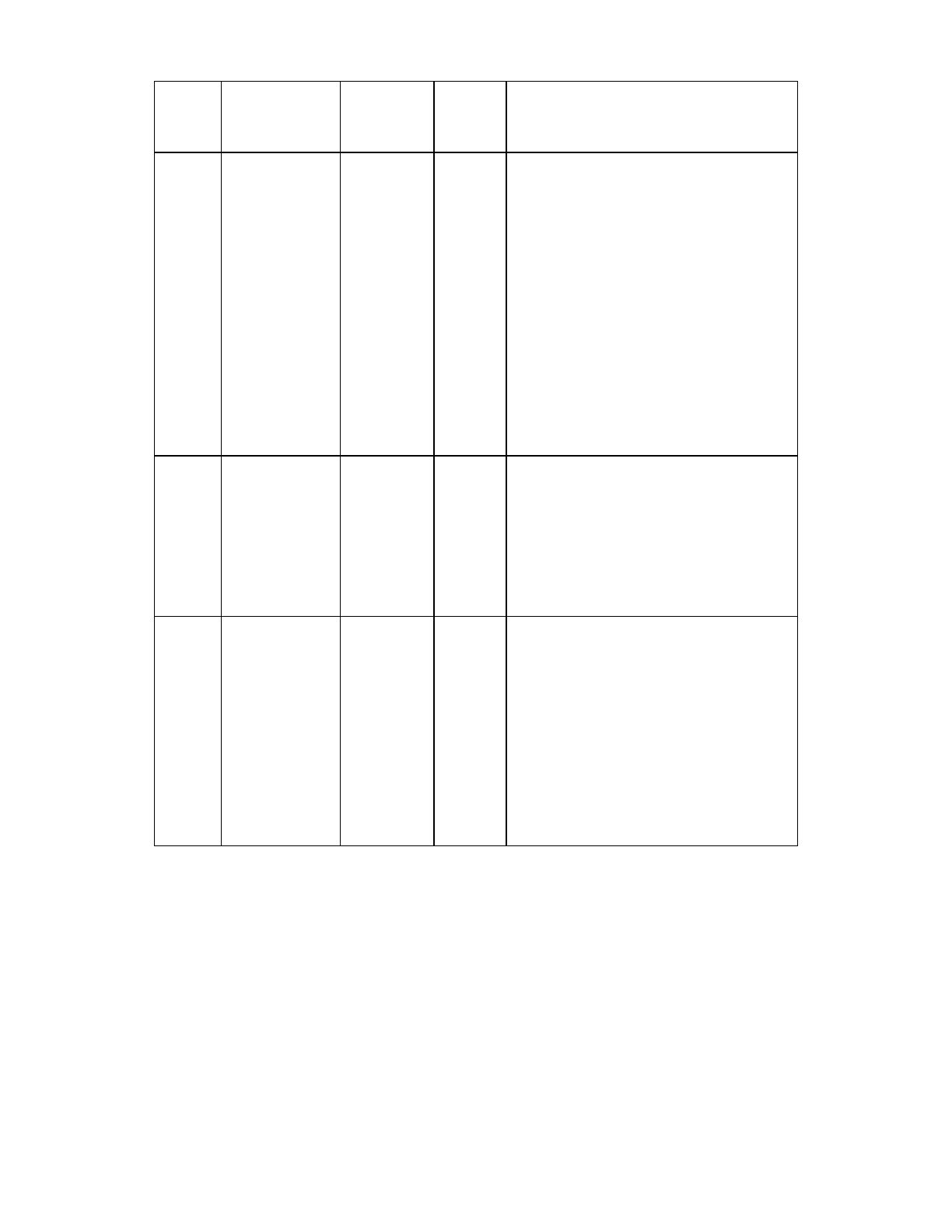

DESCRIPTION OF PIN FUNCTIONS

QFP/

TQFP

PIN NO.

NAME

SYMBOL

BUFFER

TYPE

DESCRIPTION

HOST PROCESSOR INTERFACE

48-51

53-56

Data Bus 0-7

D0-D7

I/O24

The data bus connection used by the host

microprocessor to transmit data to and from

the chip. These pins are in a high-impedance

state when not in the output mode.

44

nI/O Read

nIOR

I

This active low signal is issued by the host

microprocessor to indicate a read operation.

45

nI/O Write

nIOW

I

This active low signal is issued by the host

microprocessor to indicate a write operation.

46

Address Enable

AEN

I

Active high Address Enable indicates DMA

operations on the host data bus. Used

internally to qualify appropriate address

decodes.

28-34

41-43,

97

I/O Address

A0-A10

I

These host address bits determine the I/O

address to be accessed during nIOR and

nIOW cycles. These bits are latched internally

by the leading edge of nIOR and nIOW. All

internal address decodes use the full A0 to

A10 address bits.

21,52,

99

DMA Request

A, B, C

DRQ_A

DRQ_B

DRQ_C

O24

This active high output is the DMA request for

byte transfers of data between the host and

the chip. This signal is cleared on the last

byte of the data transfer by the nDACK signal

going low (or by nIOR going low if nDACK was

already low as in demand mode).

22,36,

96

nDMA

Acknowledge

A, B, C

nDACK_A

nDACK_B

nDACK_C

I

An active low input acknowledging the request

for a DMA transfer of data between the host

and the chip. This input enables the DMA

read or write internally.

35

Terminal Count

TC

I

This signal indicates to the chip that DMA data

transfer is complete. TC is only accepted

when nDACK_x is low. In AT and PS/2 model

30 modes, TC is active high and in PS/2

mode, TC is active low.

7

DESCRIPTION OF PIN FUNCTIONS

QFP/

TQFP

PIN NO.

NAME

SYMBOL

BUFFER

TYPE

DESCRIPTION

19,

37-40,

Interrupt Request

A, C, D,

E, F,

IRQ_A

IRQ_C

IRQ_D

IRQ_E

IRQ_F

O24

OD24

The interrupt request from the logical device

or IRQIN is output on one of the IRQA-G

signals. Refer to the configuration registers

for more information.

If EPP or ECP Mode is enabled, this output is

pulsed low, then released to allow sharing of

interrupts.

27

Chip Select Input nCS

I

When enabled, this active low pin serves as

an input for an external decoder circuit which

is used to qualify address lines above A10.

57

Reset

RESET

IS

This active high signal resets the chip and

must be valid for 500 ns minimum. The effect

on the internal registers is described in the

appropriate section. The configuration

registers are not affected by this reset.

FLOPPY DISK INTERFACE

16

nRead Disk Data nRDATA

IS

Raw serial bit stream from the disk drive, low

active. Each falling edge represents a flux

transition of the encoded data.

10 nWrite

Gate

nWGATE

OD48

This active low high current driver allows

current to flow through the write head. It

becomes active just prior to writing to the

diskette.

9 nWrite

Data

nWDATA

OD48

This active low high current driver provides the

encoded data to the disk drive. Each falling

edge causes a flux transition on the media.

11 nHead

Select

nHDSEL

OD48

This high current output selects the floppy disk

side for reading or writing. A logic "1" on this

pin means side 0 will be accessed, while a

logic "0" means side 1 will be accessed.

7 Direction

Control

nDIR

OD48

This high current low active output determines

the direction of the head movement. A logic

"1" on this pin means outward motion, while a

logic "0" means inward motion.

8

DESCRIPTION OF PIN FUNCTIONS

QFP/

TQFP

PIN NO.

NAME

SYMBOL

BUFFER

TYPE

DESCRIPTION

8 nStep

Pulse nSTEP

OD48

This active low high current driver issues a low

pulse for each track-to-track movement of the

head.

17 Disk

Change nDSKCHG

IS This

input

senses that the drive door is open

or that the diskette has possibly been changed

since the last drive selection. This input is

inverted and read via bit 7 of I/O address

3F7H.

4,3

nDrive Select O,1 nDS0,1

OD48

Active low open drain outputs select drives 0-

1.

2,5

nMotor On 0,1

nMTR0,1

OD48

These active low open drain outputs select

motor drives 0-1.

1 DRVDEN0

DRVDEN0 OD48

Indicates the drive and media selected. Refer

to configuration registers CR03, CR0B, CR1F.

14 nWrite

Protected

nWRTPRT

IS

This active low Schmitt Trigger input senses

from the disk drive that a disk is write

protected. Any write command is ignored.

13

wTrack 00

nTRK00

IS

This active low Schmitt Trigger input senses

from the disk drive that the head is positioned

over the outermost track.

12

nIndex

nINDEX

IS

This active low Schmitt Trigger input senses

from the disk drive that the head is positioned

over the beginning of a track, as marked by an

index hole.

18 DRVDEN1

DRVDEN 1

OD48

Indicates the drive and media selected. Refer

to configuration registers CR03, CR0B, CR1F.

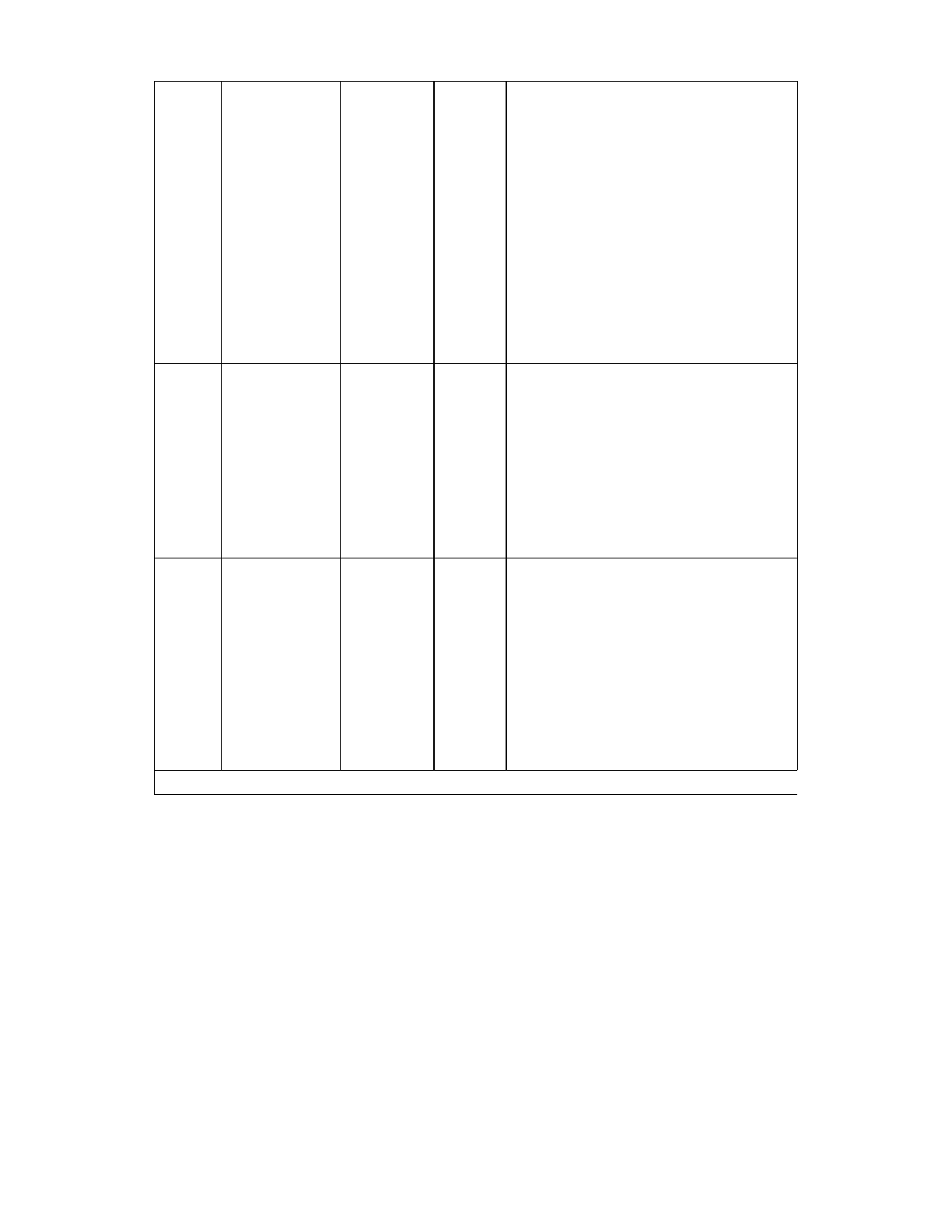

SERIAL PORT INTERFACE

88

Receive Data 2

RXD2/IRRX

I

Receiver serial data input for port 2. IR

Receive Data

89

Transmit Data 2

TXD2/IRTX

O24

Transmit serial data output for port 2. IR

transmit data.

78

Receive Data 1

RXD1

I

Reciever serial data input for port 1.

79

Transmit Data 1

TXD1

024

Transmit serial data output for port 1.

9

DESCRIPTION OF PIN FUNCTIONS

QFP/

TQFP

PIN NO.

NAME

SYMBOL

BUFFER

TYPE

DESCRIPTION

81,91 nRequest

to

Send

(System Option)

nRTS1

nRTS2

(SYSOPT)

O4

Active low Request to Send outputs for the

Serial Port. Handshake output signal notifies

modem that the UART is ready to transmit

data. This signal can be programmed by

writing to bit 1 of Modem Control Register

(MCR). The hardware reset will reset the

nRTS signal to inactive mode (high). Forced

inactive during loop mode operation.

At the trailing edge of hardware reset, the

nRTS2 input is latched to determine the

configuration base address.

0 : INDEX Base I/O Address = 3F0 Hex

1 : INDEX Base I/O Address = 370 Hex

83,93 nData

Terminal

Ready

nDTR1

nDTR2

O4

Active low Data Terminal Ready outputs for

the serial port. Handshake output signal

notifies modem that the UART is ready to

establish data communication link. This signal

can be programmed by writing to bit 0 of

Modem Control Register (MCR). The

hardware reset will reset the nDTR signal to

inactive mode (high). Forced inactive during

loop mode operation.

82,92

nClear to Send

nCTS1

nCTS2

I

Active low Clear to Send inputs for the serial

port. Handshake signal which notifies the

UART that the modem is ready to receive

data. The CPU can monitor the status of

nCTS signal by reading bit 4 of Modem Status

Register (MSR). A nCTS signal state change

from low to high after the last MSR read will

set MSR bit 0 to a 1. If bit 3 of Interrupt

Enable Register is set, the interrupt is

generated when nCTS changes state. The

nCTS signal has no effect on the transmitter.

Note: Bit 4 of MSR is the complement of

nCTS.

10

DESCRIPTION OF PIN FUNCTIONS

QFP/

TQFP

PIN NO.

NAME

SYMBOL

BUFFER

TYPE

DESCRIPTION

80,90

nData Set Ready nDSR1

nDSR2

I

Active low Data Set Ready inputs for the serial

port. Handshake signal which notifies the

UART that the modem is ready to establish

the communication link. The CPU can

monitor the status of nDSR signal by reading

bit 5 of Modem Status Register (MSR). A

nDSR signal state change from low to high

after the last MSR read will set MSR bit 1 to a

1. If bit 3 of Interrupt Enable Register is set,

the interrupt is generated when nDSR

changes state. Note: Bit 5 of MSR is the

complement of nDSR.

85,87 nData

Carrier

Detect

nDCD1

nDCD2

I

Active low Data Carrier Detect inputs for the

serial port. Handshake signal which notifies

the UART that carrier signal is detected by the

modem. The CPU can monitor the status of

nDCD signal by reading bit 7 of Modem Status

Register (MSR). A nDCD signal state change

from low to high after the last MSR read will

set MSR bit 3 to a 1. If bit 3 of Interrupt

Enable Register is set, the interrupt is

generated when nDCD changes state. Note:

Bit 7 of MSR is the complement of nDCD.

84,86 nRing

Indicator nRI1

nRI2

I

Active low Ring Indicator inputs for the serial

port. Handshake signal which notifies the

UART that the telephone ring signal is

detected by the modem. The CPU can

monitor the status of nRI signal by reading bit

6 of Modem Status Register (MSR). A nRI

signal state change from low to high after the

last MSR read will set MSR bit 2 to a 1. If bit 3

of Interrupt Enable Register is set, the

interrupt is generated when nRI changes

state. Note: Bit 6 of MSR is the complement

of nRI.

PARALLEL PORT INTERFACE