2017 Microchip Technology Inc.

DS20005703A-page 1

DN3135

Features

• High Input Impedance

• Low Input Capacitance

• Fast Switching Speeds

• Low On-resistance

• Free from Secondary Breakdown

• Low Input and Output Leakage

Applications

• Normally-on Switches

• Solid State Relays

• Converters

• Linear Amplifiers

• Constant-current Sources

• Power Supply Circuits

• Telecommunications

General Description

The DN3135 is a low-threshold, Depletion-mode

(normally-on) transistor that utilizes an advanced

vertical DMOS structure and a well-proven silicon gate

manufacturing process. This combination produces a

device with the power handling capabilities of bipolar

transistors and the high input impedance and positive

temperature coefficient inherent in MOS devices.

Characteristic of all MOS structures, this device is free

from thermal runaway and thermally induced

secondary breakdown.

Microchip’s vertical DMOS FETs are ideally suited to a

wide range of switching and amplifying applications

where very low threshold voltage, high breakdown

voltage, high input impedance, low input capacitance

and fast switching speeds are desired.

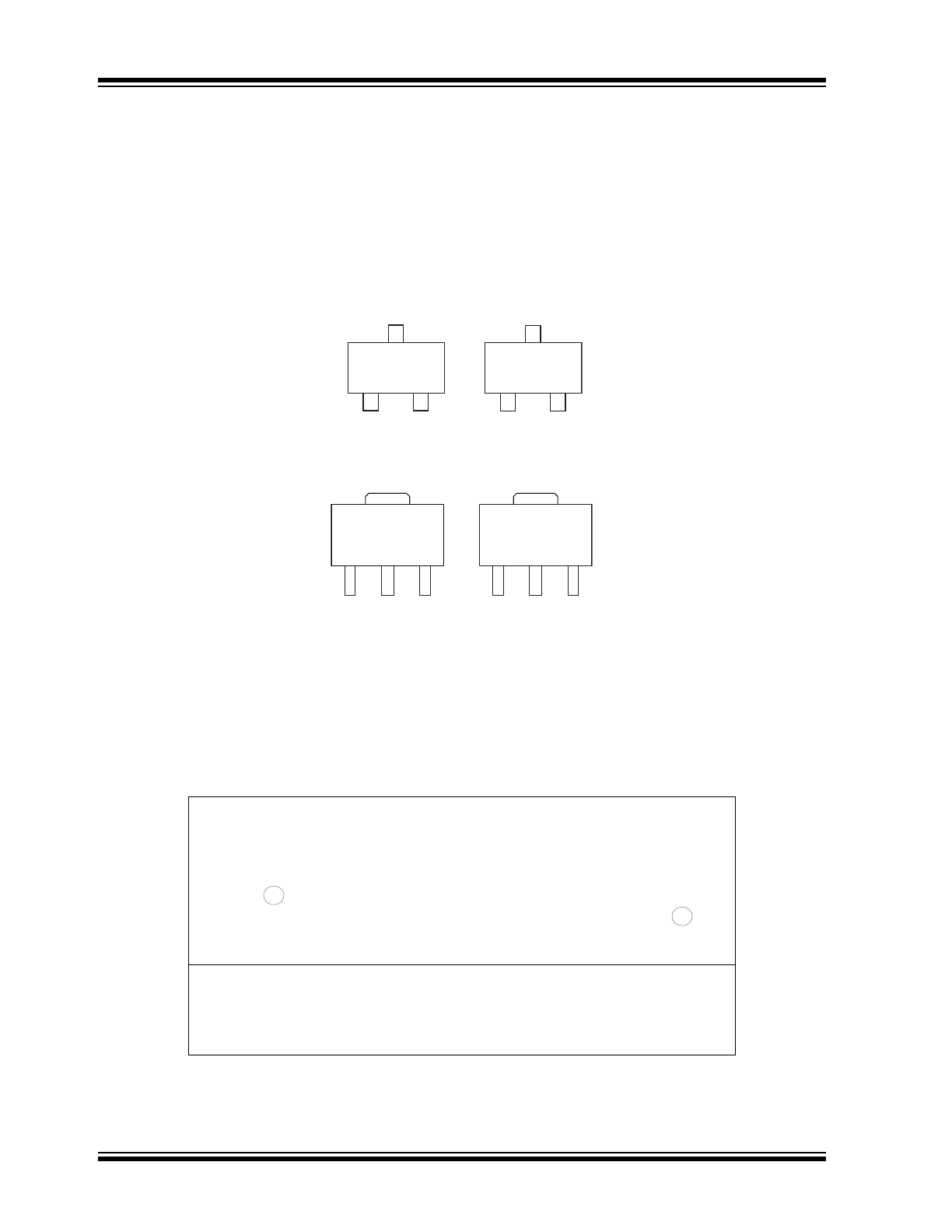

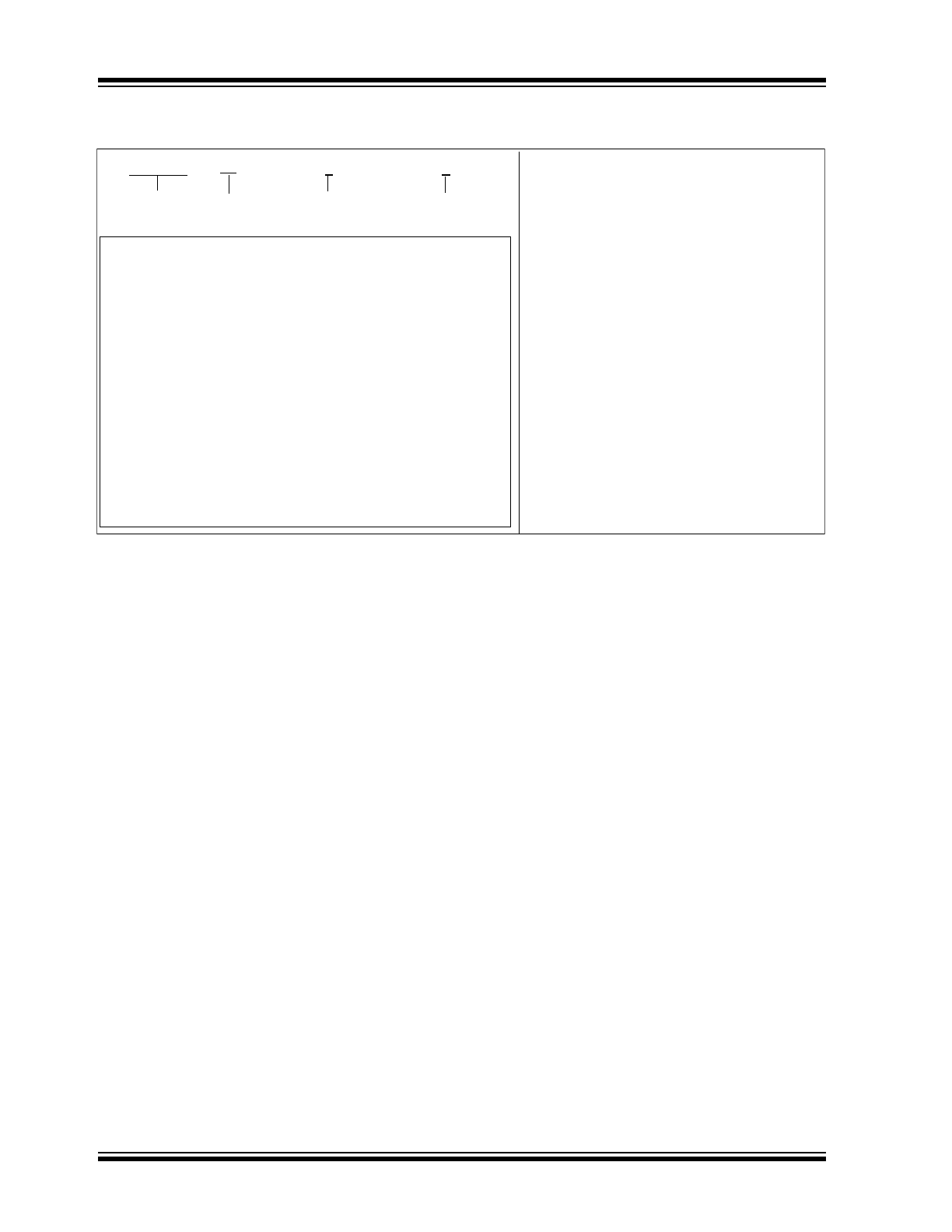

Package Type

SOT-23 (TO-236AB)

(Top view)

See

Table 2-1

for pin information.

DRAIN

SOURCE

GATE

GATE

SOURCE

DRAIN

DRAIN

SOT-89 (TO-243AA)

(Top view)

s

N-Channel Depletion-Mode Vertical DMOS FET

DN3135

DS20005703A-page 2

2017 Microchip Technology Inc.

1.0

ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings†

Drain-to-source Voltage........................................................................................................................................ BV

DSX

Drain-to-gate Voltage ........................................................................................................................................... BV

DGX

Gate-to-source Voltage ........................................................................................................................................... ±20V

Operating Ambient Temperature, T

A

................................................................................................... –55°C to +150°C

Storage Temperature, T

S

...................................................................................................................... –55°C to +150°C

† Notice: Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the

device. This is a stress rating only, and functional operation of the device at those or any other conditions above those

indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for

extended periods may affect device reliability.

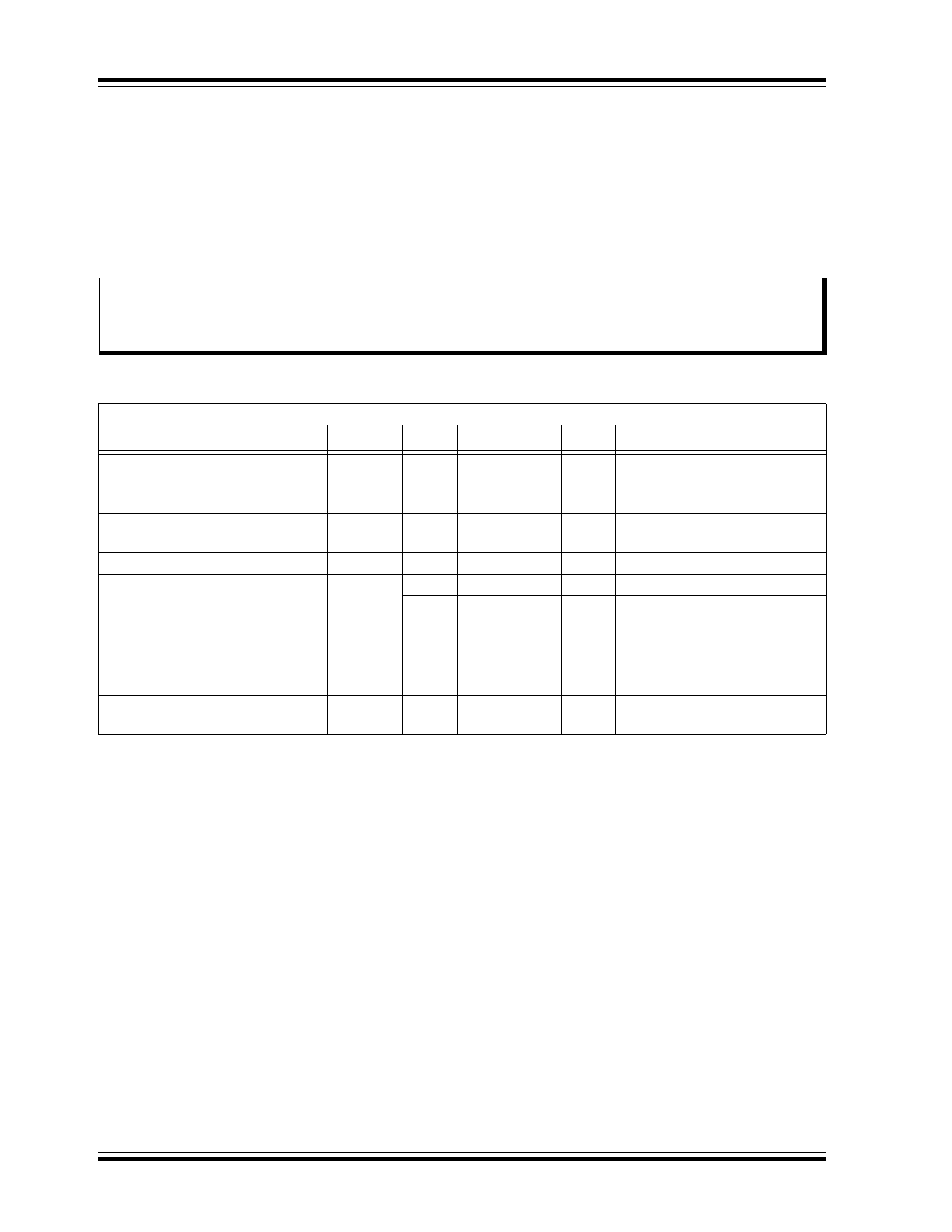

DC ELECTRICAL CHARACTERISTICS

1

Electrical Specifications: Unless otherwise specified, for all specifications T

A

=T

J

= +25°C.

Parameter

Sym.

Min.

Typ.

Max.

Unit

Conditions

Drain-to-source Breakdown

Voltage

BV

DSX

350

—

—

V

V

GS

= –5V, I

D

= 100 µA

Gate-to-source Off Voltage

V

GS(OFF)

–1.5

—

–3.5

V

V

DS

= 15V, I

D

= 10 µA

Change in V

GS(OFF)

with

Temperature

∆V

GS(OFF)

—

—

–4.5

mV/°C V

DS

= 15V, I

D

= 10 µA (

Note 2

)

Gate Body Leakage Current

I

GSS

—

—

100

nA

V

GS

= ±20V, V

DS

= 0V

Drain-to-source Leakage Current

I

D(OFF)

—

—

1

µA

V

DS

= Max rating, V

GS

= –5V

—

—

1

mA

V

DS

= 0.8 Max Rating,

V

GS

= –5V, T

A

= 125°C (

Note 2

)

Saturated Drain-to-source Current

I

DSS

180

—

—

mA

V

GS

= 0V, V

DS

= 15V

Static Drain-to-source On-state

Resistance

R

DS(ON)

—

—

35

Ω

V

GS

= 0V, I

D

= 150 mA

Change in R

DS(ON)

with

Temperature

∆R

DS(ON)

—

—

1.1

%/°C

V

GS

= 0V, I

D

= 150 mA (

Note 2

)

Note 1: All DC parameters are 100% tested at 25°C unless otherwise stated. Pulse test: 300 µs pulse, 2% duty

cycle.

2: Specification is obtained by characterization and is not 100% tested.

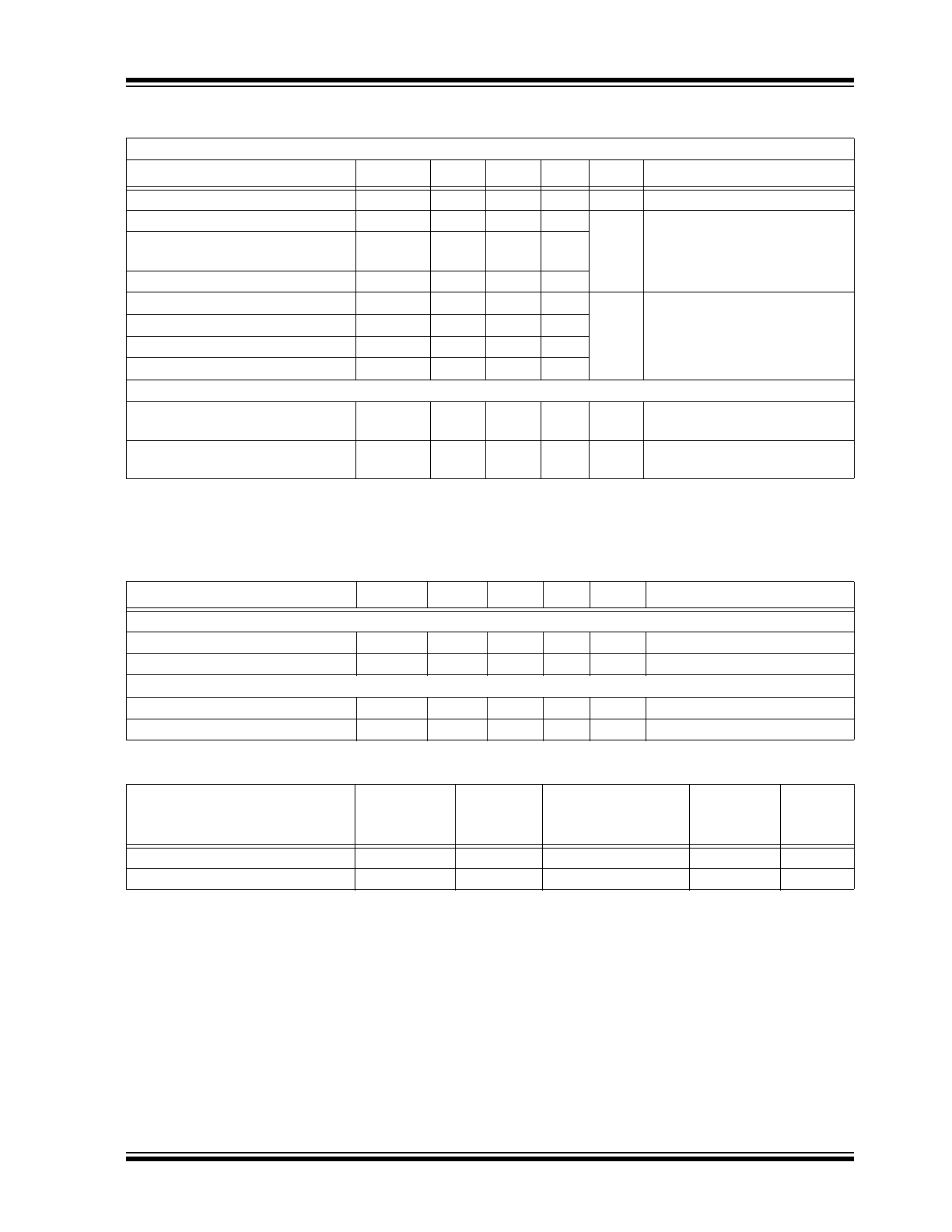

AC ELECTRICAL CHARACTERISTICS

2

Electrical Specifications: Unless otherwise specified, for all specifications T

A

=T

J

= +25°C.

Parameter

Sym.

Min.

Typ.

Max.

Unit

Conditions

Forward Transconductance

G

FS

140

—

—

mmho V

DS

= 10V, I

D

= 100 mA

Input Capacitance

C

ISS

—

60

120

pF

V

GS

= –5V,

V

DS

= 25V,

f = 1 MHz

Common Source Output

Capacitance

C

OSS

—

6

15

Reverse Transfer Capacitance

C

RSS

—

3

10

Turn-on Delay Time

t

d(ON)

—

—

10

ns

V

DD

= 25V,

I

D

= 150 mA,

R

GEN

= 25Ω,

V

GS

= 0V to –10V

Rise Time

t

r

—

—

15

Turn-off Delay Time

t

d(OFF)

—

—

15

Fall Time

t

f

—

—

20

DIODE PARAMETER

Diode Forward Voltage Drop

V

SD

—

—

1.8

V

V

GS

= –5V, I

SD

= 150 mA

(

Note 1

)

Reverse Recovery Time

t

rr

—

800

—

ns

V

GS

= –5V, I

SD

= 150 mA

(

Note 2

)

Note 1: All DC parameters are 100% tested at 25°C unless otherwise stated. Pulse test: 300 µs pulse, 2% duty

cycle.

2: Specification is obtained by characterization and is not 100% tested.

TEMPERATURE SPECIFICATIONS

Parameter

Sym.

Min.

Typ.

Max.

Unit

Conditions

TEMPERATURE RANGE

Operating Ambient Temperature

T

A

–55

—

+150

°C

Storage Temperature

T

S

–55

—

+150

°C

PACKAGE THERMAL RESISTANCE

SOT-23

JA

—

203

—

°C/W

SOT-89

JA

—

133

—

°C/W

THERMAL CHARACTERISTICS

Package

I

D

(

1

)

(Continuous)

(mA)

I

D

(Pulsed)

(mA)

Power Dissipation at

T

A

= 25°C

(W)

I

DR

(

1

)

(mA)

I

DRM

(mA)

SOT-23

72

300

0.36

72

300

SOT-89

135

300

1.3

(

2

)

135

300

Note 1: I

D

(continuous) is limited by maximum T

J

.

2: Mounted on FR4 board, 25 mm x 25 mm x 1.57 mm

2017 Microchip Technology Inc.

DS20005703A-page 3

DN3135

DN3135

DS20005703A-page 4

2017 Microchip Technology Inc.

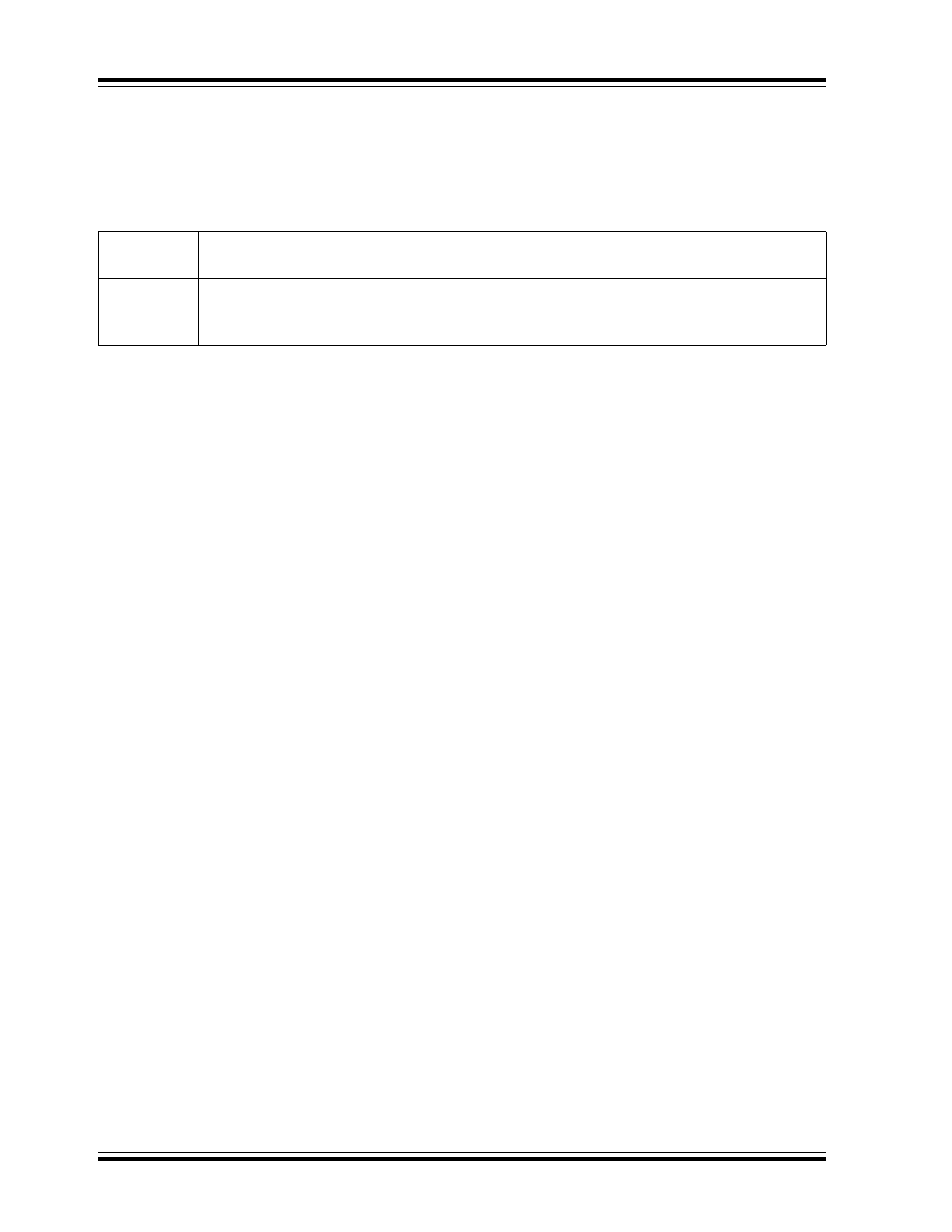

2.0

PIN DESCRIPTION

Table 2-1

shows the description of pins in DN3135

SOT-23 and SOT-89. Refer to

Package Types

for the

location of pins.

TABLE 2-1:

PIN FUNCTION TABLE

SOT-23

Pin Number

SOT-89

Pin Number

Pin Name

Description

1

1

Gate

Gate

2

3

Source

Source

3

2, 4

Drain

Drain

2017 Microchip Technology Inc.

DS20005703A-page 5

DN3135

3.0

FUNCTIONAL DESCRIPTION

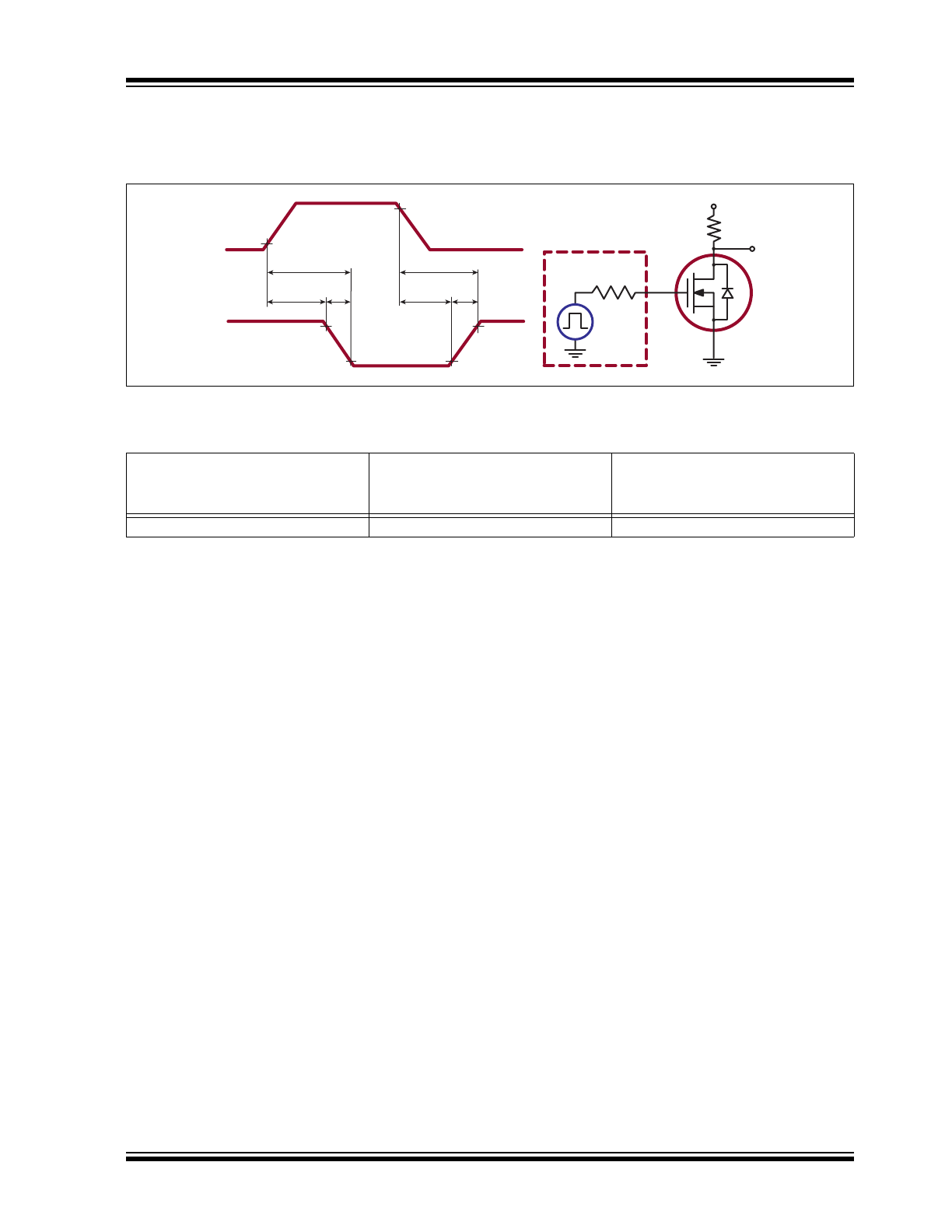

Figure 3-1

illustrates the switching waveforms and test

circuit for DN3135.

90%

10%

90%

90%

10%

10%

Pulse

Generator

VDD

R

L

OUTPUT

D.U.T.

t

(ON)

t

d(ON)

t

(OFF)

t

d(OFF)

t

r

INPUT

INPUT

OUTPUT

0V

VDD

R

GEN

0V

-10V

t

f

FIGURE 3-1:

Switching Waveforms and Test Circuit.

PRODUCT SUMMARY

BV

DSX

/BV

DGX

(V)

R

DS(ON)

(Maximum)

(Ω)

I

DSS

(Minimum)

(mA)

350

35

180

DN3135

DS20005703A-page 6

2017 Microchip Technology Inc.

4.0

PACKAGING INFORMATION

4.1

Package Marking Information

Legend: XX...X

Product Code or Customer-specific information

Y

Year code (last digit of calendar year)

YY

Year code (last 2 digits of calendar year)

WW

Week code (week of January 1 is week ‘01’)

NNN

Alphanumeric traceability code

Pb-free JEDEC

®

designator for Matte Tin (Sn)

*

This package is Pb-free. The Pb-free JEDEC designator ( )

can be found on the outer packaging for this package.

Note:

In the event the full Microchip part number cannot be marked on one line, it will

be carried over to the next line, thus limiting the number of available

characters for product code or customer-specific information. Package may or

not include the corporate logo.

3

e

3

e

XXXNNN

N1S894

3-lead SOT-23

Example

3-lead SOT-89

Example

XXXXYWW

NNN

DN1S732

987

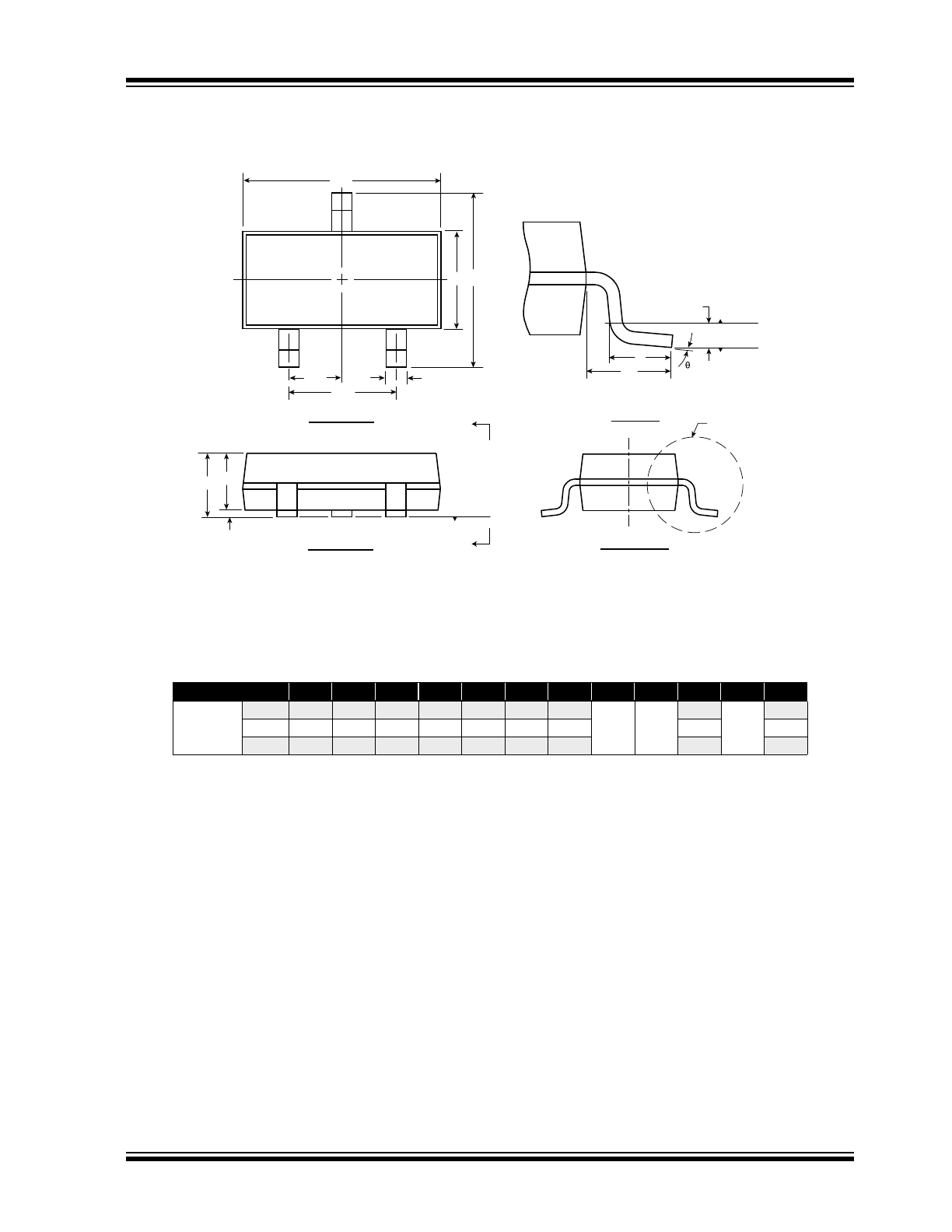

3-Lead TO-236AB (SOT-23) Package Outline (K1/T)

2.90x1.30mm body, 1.12mm height (max), 1.90mm pitch

Symbol

A

A1

A2

b

D

E

E1

e

e1

L

L1

ș

Dimension

(mm)

MIN

0.89

0.01

0.88

0.30

2.80

2.10

1.20

0.95

BSC

1.90

BSC

0.20

†

0.54

REF

0

O

NOM

-

-

0.95

-

2.90

-

1.30

0.50

-

MAX

1.12

0.10

1.02

0.50

3.04

2.64

1.40

0.60

8

O

JEDEC Registration TO-236, Variation AB, Issue H, Jan. 1999.

† This dimension differs from the JEDEC drawing.

Drawings not to scale.

View B

View A - A

Side View

Top View

View B

Gauge

Plane

Seating

Plane

0.25

L1

L

E1 E

D

3

1

2

e

e1

b

A

A

Seating

Plane

A

A2

A1

Note: For the most current package drawings, see the Microchip Packaging Specification at www.microchip.com/packaging.

Note: For the most current package drawings, see the Microchip Packaging Specification at www.microchip.com/packaging.

2017 Microchip Technology Inc.

DS20005703A-page 7

DN3135

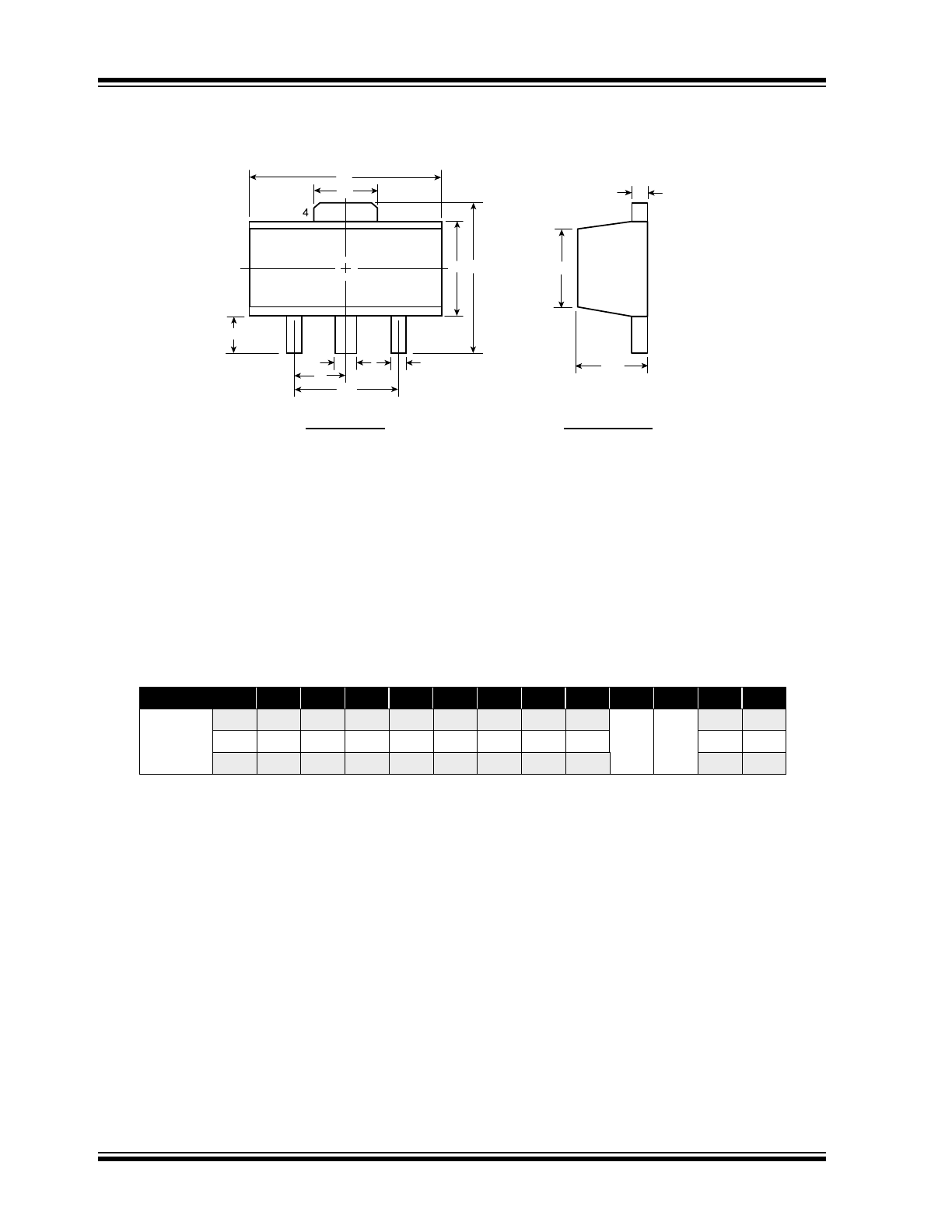

3-Lead TO-243AA (SOT-89) Package Outline (N8)

Symbol

A

b

b1

C

D

D1

E

E1

e

e1

H

L

Dimensions

(mm)

MIN

1.40

0.44

0.36

0.35

4.40

1.62

2.29

2.00

†

1.50

BSC

3.00

BSC

3.94

0.73

†

NOM

-

-

-

-

-

-

-

-

-

-

MAX

1.60

0.56

0.48

0.44

4.60

1.83

2.60

2.29

4.25

1.20

JEDEC Registration TO-243, Variation AA, Issue C, July 1986.

† This dimension differs from the JEDEC drawing

Drawings not to scale.

b

b1

D

D1

E H

E1

C

A

1

2

3

e

e1

Top View

Side View

L

Note: For the most current package drawings, see the Microchip Packaging Specification at www.microchip.com/packaging.

Note: For the most current package drawings, see the Microchip Packaging Specification at www.microchip.com/packaging.

DN3135

DS20005703A-page 8

2017 Microchip Technology Inc.

2017 Microchip Technology Inc.

DS20005703A-page 9

DN3135

APPENDIX A: REVISION HISTORY

Revision A (April 2017)

• Converted Supertex Doc# DSFP-DN3135 to

Microchip DS20005703A

• Changed the packaging format

• Made minor text changes throughout the docu-

ment

DN3135

DS20005703A-page 10

2017 Microchip Technology Inc.

PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office

.

Examples:

a) DN3135K1-G: N-Channel Depletion-Mode

Vertical DMOS FET, 3-lead SOT-23,

3000/Reel

b) DN3135N8-G: N-Channel Depletion-Mode Vertical

DMOS FET, 3-lead SOT-89,

2000/Reel

PART NO.

Device

Device:

DN3135

=

N-Channel Depletion-Mode Vertical DMOS

FET

Packages:

K1

=

3-lead SOT-23

N8

=

3-lead SOT-89

Environmental:

G

=

Lead (Pb)-free/RoHS-compliant Package

Media Type:

(blank)

=

3000/Reel for a K1 Package

2000/Reel for an N8 Package

XX

Package

-

X - X

Environmental Media Type

Options