This is a summary document.

The complete document is

available on the Atmel website

at www.atmel.com.

6175KS–ATARM–25-Oct-12

Features

•

Incorporates the ARM7TDMI

®

ARM

®

Thumb

®

Processor

– High-performance 32-bit RISC Architecture

– High-density 16-bit Instruction Set

– Leader in MIPS/Watt

– EmbeddedICE

™

In-circuit Emulation, Debug Communication Channel Support

•

Internal High-speed Flash

– 512 Kbytes (SAM7S512) Organized in Two Contiguous Banks of 1024 Pages of 256

Bytes (Dual Plane)

– 256 Kbytes (SAM7S256) Organized in 1024 Pages of 256 Bytes (Single Plane)

– 128 Kbytes (SAM7S128) Organized in 512 Pages of 256 Bytes (Single Plane)

– 64 Kbytes (SAM7S64) Organized in 512 Pages of 128 Bytes (Single Plane)

– 32 Kbytes (SAM7S321/32) Organized in 256 Pages of 128 Bytes (Single Plane)

– 16 Kbytes (SAM7S161/16) Organized in 256 Pages of 64 Bytes (Single Plane)

– Single Cycle Access at Up to 30 MHz in Worst Case Conditions

– Prefetch Buffer Optimizing Thumb Instruction Execution at Maximum Speed

– Page Programming Time: 6 ms, Including Page Auto-erase, Full Erase Time: 15 ms

– 10,000 Write Cycles, 10-year Data Retention Capability, Sector Lock Capabilities, Flash

Security Bit

– Fast Flash Programming Interface for High Volume Production

•

Internal High-speed SRAM, Single-cycle Access at Maximum Speed

– 64 Kbytes (SAM7S512/256)

– 32 Kbytes (SAM7S128)

– 16 Kbytes (SAM7S64)

– 8 Kbytes (SAM7S321/32)

– 4 Kbytes (SAM7S161/16)

•

Memory Controller (MC)

– Embedded Flash Controller, Abort Status and Misalignment Detection

•

Reset Controller (RSTC)

– Based on Power-on Reset and Low-power Factory-calibrated Brown-out Detector

– Provides External Reset Signal Shaping and Reset Source Status

•

Clock Generator (CKGR)

– Low-power RC Oscillator, 3 to 20 MHz On-chip Oscillator and one PLL

•

Power Management Controller (PMC)

– Software Power Optimization Capabilities, Including Slow Clock Mode (Down to 500

Hz) and Idle Mode

– Three Programmable External Clock Signals

•

Advanced Interrupt Controller (AIC)

– Individually Maskable, Eight-level Priority, Vectored Interrupt Sources

– Two (SAM7S512/256/128/64/321/161) or One (SAM7S32/16) External Interrupt Source(s)

and One Fast Interrupt Source, Spurious Interrupt Protected

AT91SAM

ARM-based Flash MCU

SAM7S512 SAM7S256 SAM7S128 SAM7S64

SAM7S321 SAM7S32 SAM7S161 SAM7S16

Summary

2

SAM7S Series [DATASHEET]

6175KS–ATARM–25-Oct-12

•

Debug Unit (DBGU)

– 2-wire UART and Support for Debug Communication Channel interrupt, Programmable ICE Access Prevention

– Mode for General Purpose 2-wire UART Serial Communication

•

Periodic Interval Timer (PIT)

– 20-bit Programmable Counter plus 12-bit Interval Counter

•

Windowed Watchdog (WDT)

– 12-bit key-protected Programmable Counter

– Provides Reset or Interrupt Signals to the System

– Counter May Be Stopped While the Processor is in Debug State or in Idle Mode

•

Real-time Timer (RTT)

– 32-bit Free-running Counter with Alarm

– Runs Off the Internal RC Oscillator

•

One Parallel Input/Output Controller (PIOA)

– Thirty-two (SAM7S512/256/128/64/321/161) or twenty-one (SAM7S32/16) Programmable I/O Lines Multiplexed with up to

Two Peripheral I/Os

– Input Change Interrupt Capability on Each I/O Line

– Individually Programmable Open-drain, Pull-up resistor and Synchronous Output

•

Eleven (SAM7S512/256/128/64/321/161) or Nine (SAM7S32/16) Peripheral DMA Controller (PDC) Channels

•

One USB 2.0 Full Speed (12 Mbits per Second) Device Port (Except for the SAM7S32/16).

– On-chip Transceiver, 328-byte Configurable Integrated FIFOs

•

One Synchronous Serial Controller (SSC)

– Independent Clock and Frame Sync Signals for Each Receiver and Transmitter

– I²S Analog Interface Support, Time Division Multiplex Support

– High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer

•

Two (SAM7S512/256/128/64/321/161) or One (SAM7S32/16) Universal Synchronous/Asynchronous Receiver Transmitters

(USART)

– Individual Baud Rate Generator, IrDA

®

Infrared Modulation/Demodulation

– Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support

– Full Modem Line Support on USART1 (SAM7S512/256/128/64/321/161)

•

One Master/Slave Serial Peripheral Interface (SPI)

– 8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects

•

One Three-channel 16-bit Timer/Counter (TC)

– Three External Clock Input and Two Multi-purpose I/O Pins per Channel (SAM7S512/256/128/64/321/161)

– One External Clock Input and Two Multi-purpose I/O Pins for the first Two Channels Only (SAM7S32/16)

– Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

•

One Four-channel 16-bit PWM Controller (PWMC)

•

One Two-wire Interface (TWI)

– Master Mode Support Only, All Two-wire Atmel EEPROMs and I

2

C Compatible Devices Supported

(SAM7S512/256/128/64/321/32)

– Master, Multi-Master and Slave Mode Support, All Two-wire Atmel EEPROMs and I

2

C Compatible Devices Supported

(SAM7S161/16)

•

One 8-channel 10-bit Analog-to-Digital Converter, Four Channels Multiplexed with Digital I/Os

•

SAM-BA

™

Boot Assistant

– Default Boot program

– Interface with SAM-BA Graphic User Interface

•

IEEE

®

1149.1 JTAG Boundary Scan on All Digital Pins

•

5V-tolerant I/Os, including Four High-current Drive I/O lines, Up to 16 mA Each (SAM7S161/16 I/Os Not 5V-tolerant)

•

Power Supplies

– Embedded 1.8V Regulator, Drawing up to 100 mA for the Core and External Components

– 3.3V or 1.8V VDDIO I/O Lines Power Supply, Independent 3.3V VDDFLASH Flash Power Supply

– 1.8V VDDCORE Core Power Supply with Brown-out Detector

3

SAM7S Series [DATASHEET]

6175KS–ATARM–25-Oct-12

•

Fully Static Operation: Up to 55 MHz at 1.65V and 85

⋅ C Worst Case Conditions

•

Available in 64-lead LQFP Green or 64-pad QFN Green Package (SAM7S512/256/128/64/321/161) and 48-lead LQFP Green or

48-pad QFN Green Package (SAM7S32/16)

1.

Description

Atmel’s SAM7S is a series of low pincount Flash microcontrollers based on the 32-bit ARM RISC processor. It fea-

tures a high-speed Flash and an SRAM, a large set of peripherals, including a USB 2.0 device (except for the

SAM7S32 and SAM7S16), and a complete set of system functions minimizing the number of external components.

The device is an ideal migration path for 8-bit microcontroller users looking for additional performance and

extended memory.

The embedded Flash memory can be programmed in-system via the JTAG-ICE interface or via a parallel interface

on a production programmer prior to mounting. Built-in lock bits and a security bit protect the firmware from acci-

dental overwrite and preserves its confidentiality.

The SAM7S Series system controller includes a reset controller capable of managing the power-on sequence of

the microcontroller and the complete system. Correct device operation can be monitored by a built-in brownout

detector and a watchdog running off an integrated RC oscillator.

The SAM7S Series are general-purpose microcontrollers. Their integrated USB Device port makes them ideal devices

for peripheral applications requiring connectivity to a PC or cellular phone. Their aggressive price point and high level of

integration pushes their scope of use far into the cost-sensitive, high-volume consumer market.

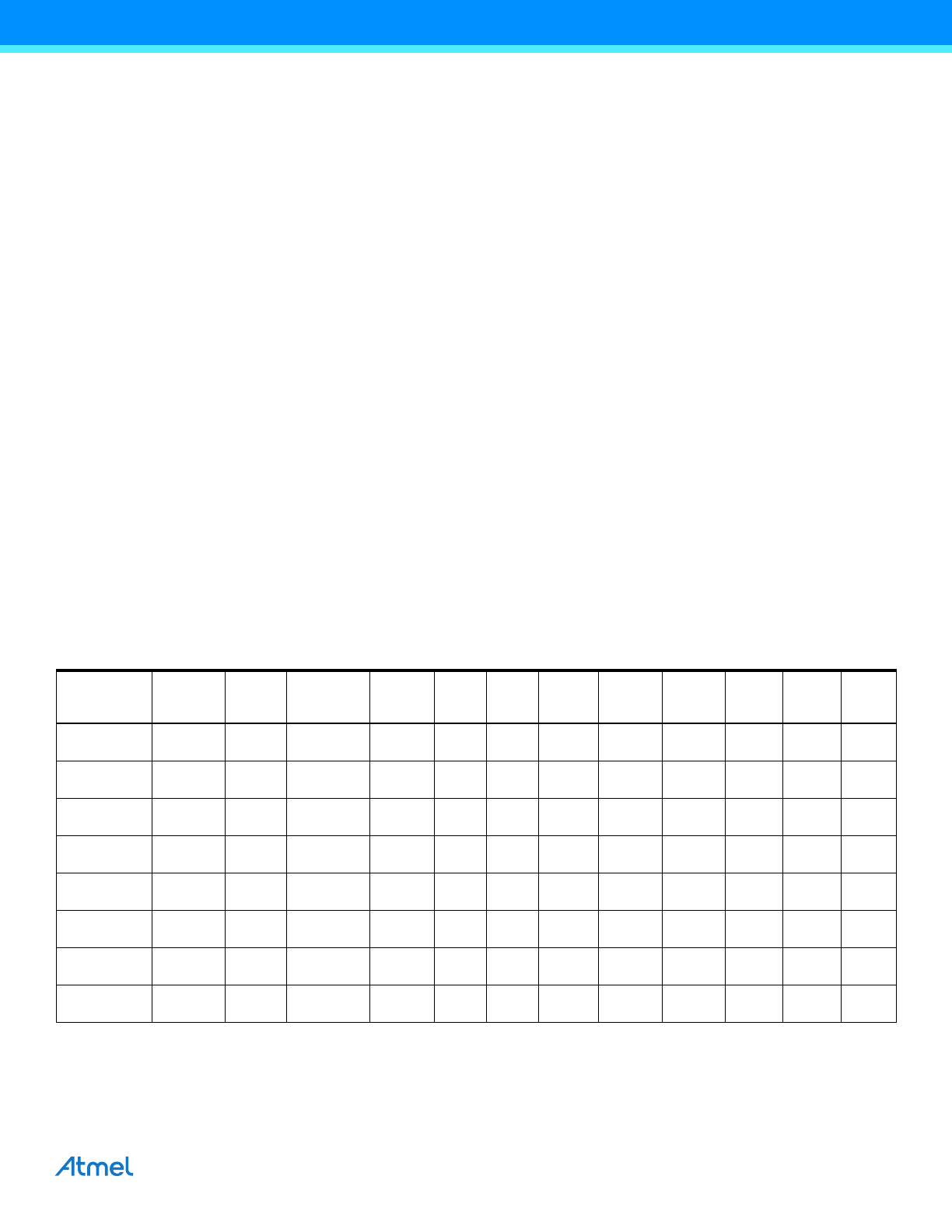

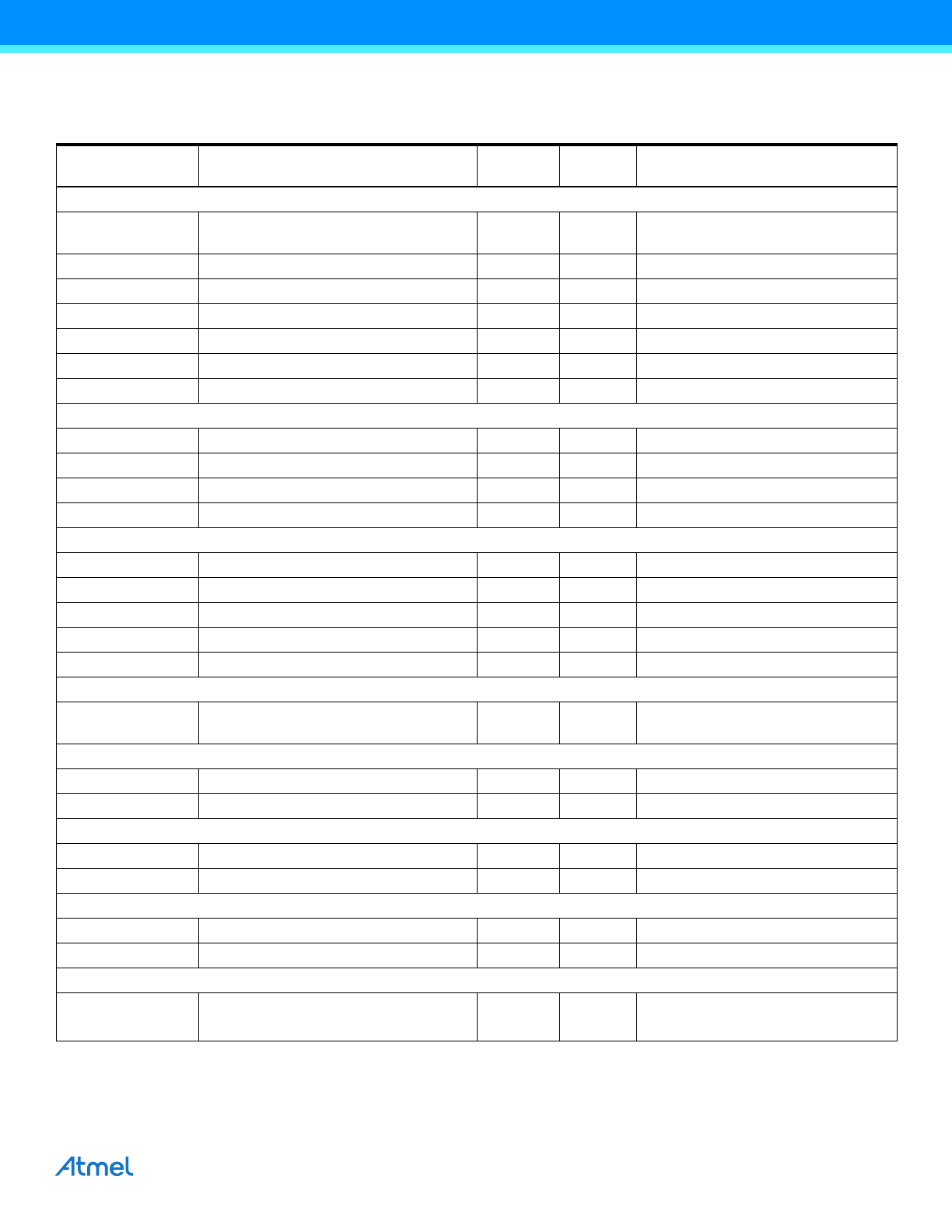

1.1

Configuration Summary of the SAM7S512, SAM7S256, SAM7S128, SAM7S64, SAM7S321,

SAM7S32, SAM7S161 and SAM7S16

The SAM7S512, SAM7S256, SAM7S128, SAM7S64, SAM7S321, SAM7S32, SAM7S161 and SAM7S16 differ in

memory size, peripheral set and package.

Table 1-1

summarizes the configuration of the six devices.

Except for the SAM7S32/16, all other SAM7S devices are package and pinout compatible.

Notes: 1. Fractional Baud Rate.

2. Full modem line support on USART1.

3. Only two TC channels are accessible through the PIO.

Table 1-1.

Configuration Summary

Device

Flash

TWI

Flash

Organization SRAM

USB

Device

Port

USART

External

Interrupt

Source

PDC

Channels

TC

Channels

I/O 5V

Tolerant

I/O

Lines

Package

SAM7S512

512 Kbytes Master

dual plane

64 Kbytes 1

2

(1)

(2)

2

11

3

Yes

32

LQFP/

QFN 64

SAM7S256

256 Kbytes Master

single plane

64 Kbytes 1

2

(1)

(2)

2

11

3

Yes

32

LQFP/

QFN 64

SAM7S128

128 Kbytes Master

single plane

32 Kbytes 1

2

(1)

(2)

2

11

3

Yes

32

LQFP/

QFN 64

SAM7S64

64 Kbytes

Master

single plane

16 Kbytes 1

2

(2)

2

11

3

Yes

32

LQFP/

QFN 64

SAM7S321

32 Kbytes

Master

single plane

8 Kbytes

1

2

(2)

2

11

3

Yes

32

LQFP/

QFN 64

SAM7S32

32 Kbytes

Master

single plane

8 Kbytes

not

present

1

1

9

3

(3)

Yes

21

LQFP/

QFN 48

SAM7S161

16 Kbytes

Master/

Slave

single plane

4 Kbytes

1

2

(2)

2

11

3

No

32

LQFP

SAM7S16

16 Kbytes

Master/

Slave

single plane

4 Kbytes

not

present

1

1

9

3

(3)

No

21

LQFP/

QFN 48

4

SAM7S Series [DATASHEET]

6175KS–ATARM–25-Oct-12

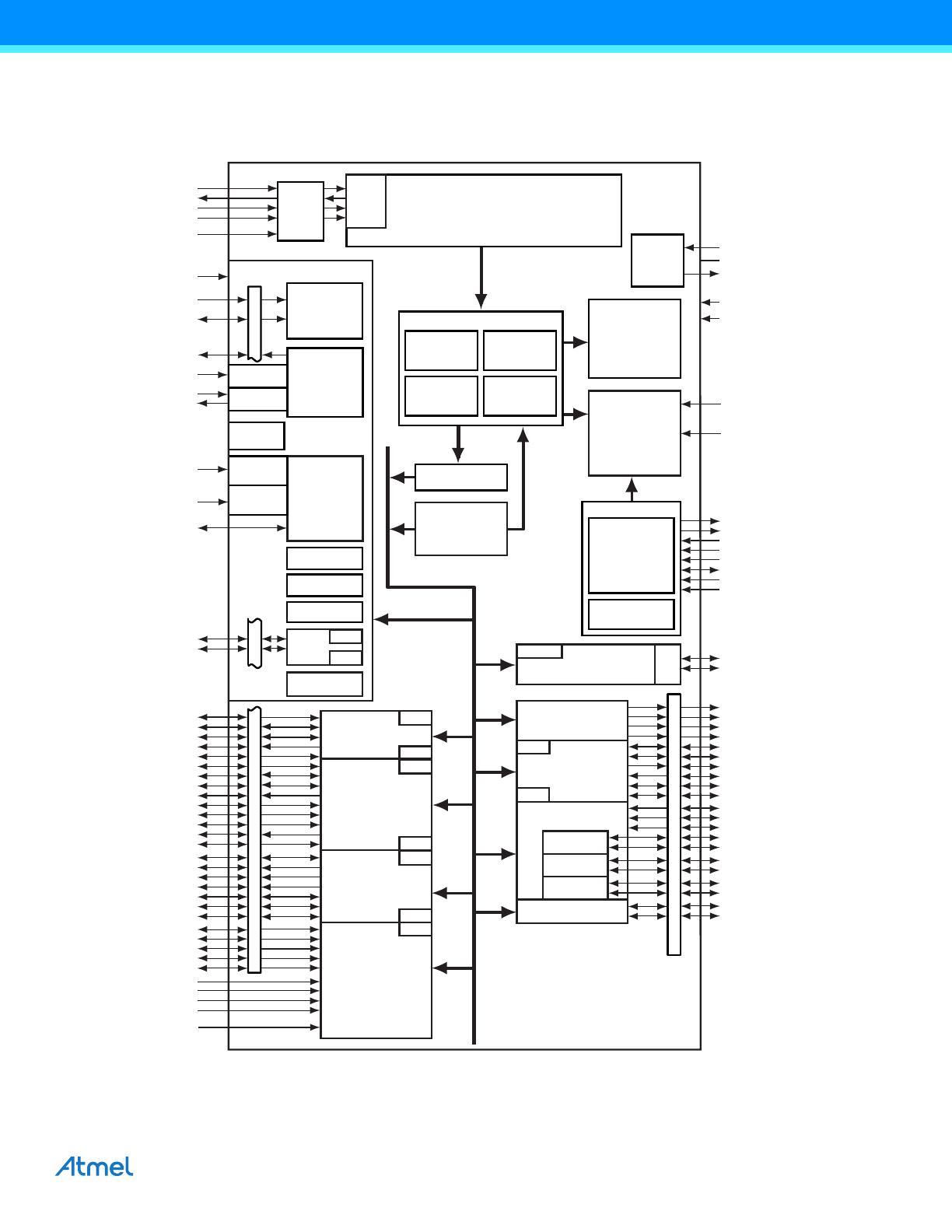

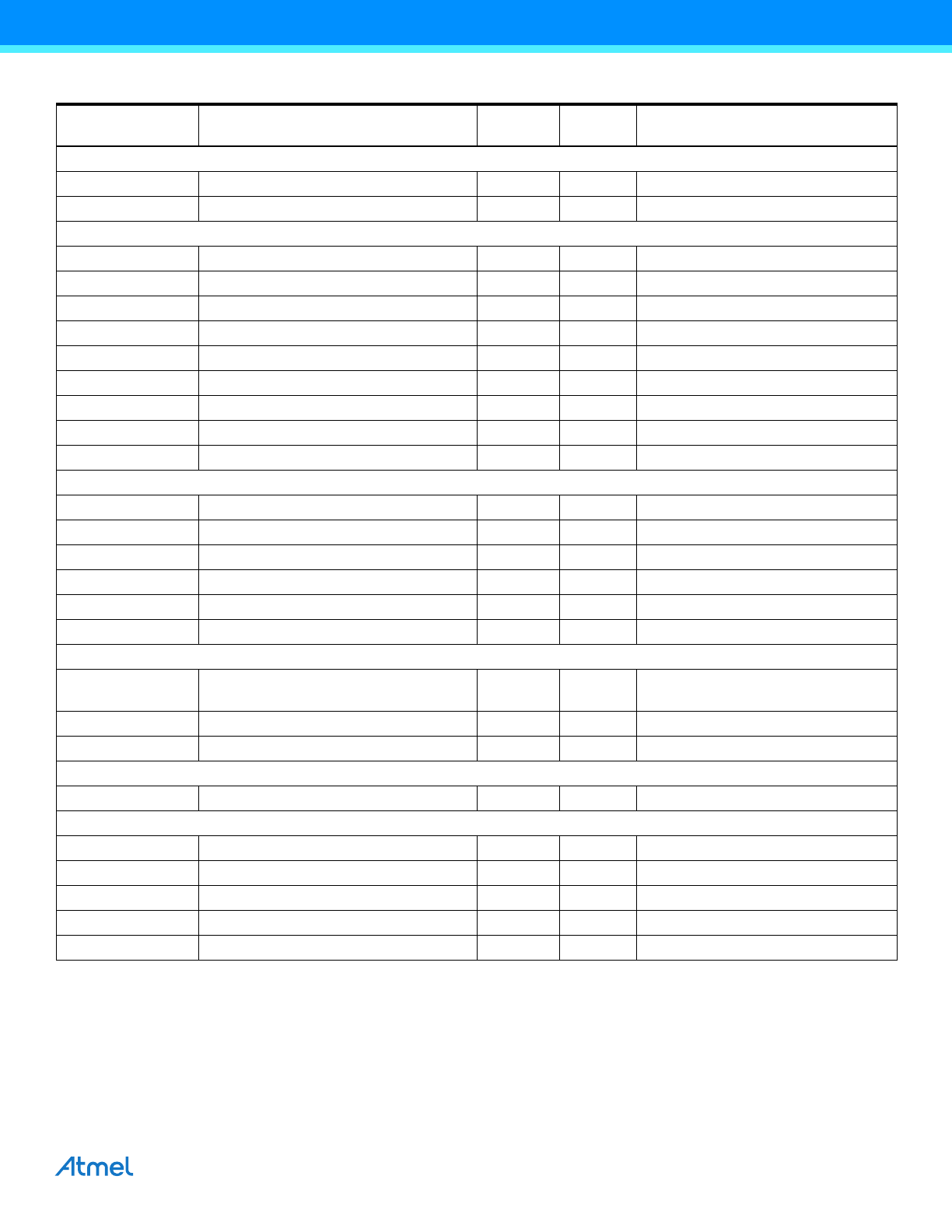

2.

Block Diagram

Figure 2-1. SAM7S512/256/128/64/321/161 Block Diagram

TDI

TDO

TMS

TCK

NRST

FIQ

IRQ0-IRQ1

PCK0-PCK2

PMC

Peripheral Bridge

Peripheral Data

Controller

AIC

PLL

RCOSC

SRAM

64/32/16/8/4 Kbytes

ARM7TDMI

Processor

ICE

JTAG

SCAN

JTAGSEL

PIOA

USART0

SSC

Timer Counter

RXD0

TXD0

SCK0

RTS0

CTS0

NPCS0

NPCS1

NPCS2

NPCS3

MISO

MOSI

SPCK

Flash

512/256/

128/64/32/16 Kbytes

Reset

Controller

DRXD

DTXD

TF

TK

TD

RD

RK

RF

TCLK0

TCLK1

TCLK2

TIOA0

TIOB0

TIOA1

TIOB1

TIOA2

TIOB2

Memory Controller

Abort

Status

Address

Decoder

Misalignment

Detection

PIO

PIO

APB

POR

Embedded

Flash

Controller

AD0

AD1

AD2

AD3

ADTRG

PLLRC

11 Channels

PDC

PDC

USART1

RXD1

TXD1

SCK1

RTS1

CTS1

DCD1

DSR1

DTR1

RI1

PDC

PDC

PDC

PDC

SPI

PDC

ADC

ADVREF

PDC

PDC

TC0

TC1

TC2

TWD

TWCK

TWI

OSC

XIN

XOUT

VDDIN

PWMC

PWM0

PWM1

PWM2

PWM3

1.8 V

Voltage

Regulator

USB Device

FIFO

DDM

DDP

T

ransceiv

er

GND

VDDOUT

BOD

VDDCORE

VDDCORE

AD4

AD5

AD6

AD7

VDDFLASH

Fast Flash

Programming

Interface

ERASE

PIO

PGMD0-PGMD15

PGMNCMD

PGMEN0-PGMEN2

PGMRDY

PGMNVALID

PGMNOE

PGMCK

PGMM0-PGMM3

VDDIO

TST

DBGU

PDC

PDC

PIO

PIT

WDT

RTT

System Controller

VDDCORE

SAM-BA

ROM

5

SAM7S Series [DATASHEET]

6175KS–ATARM–25-Oct-12

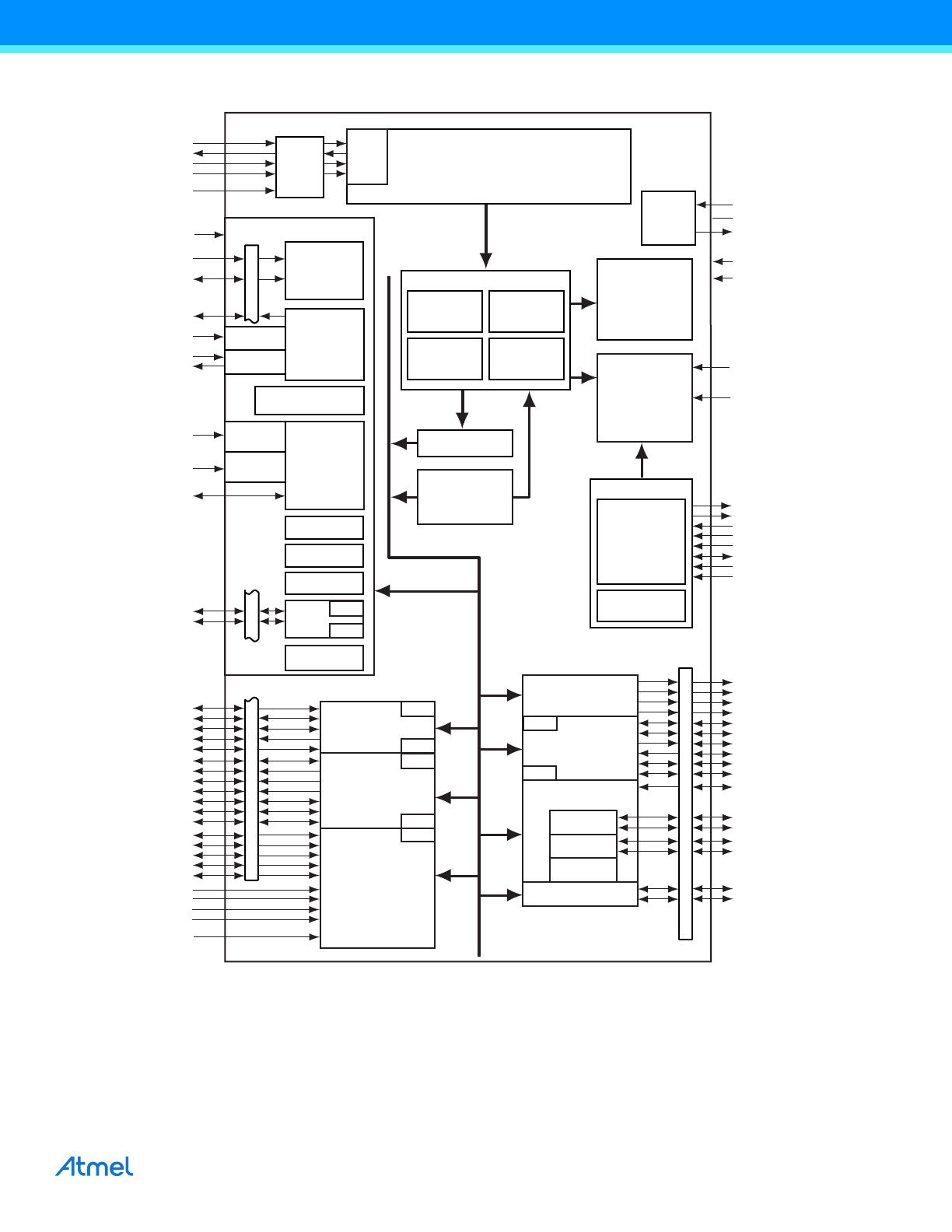

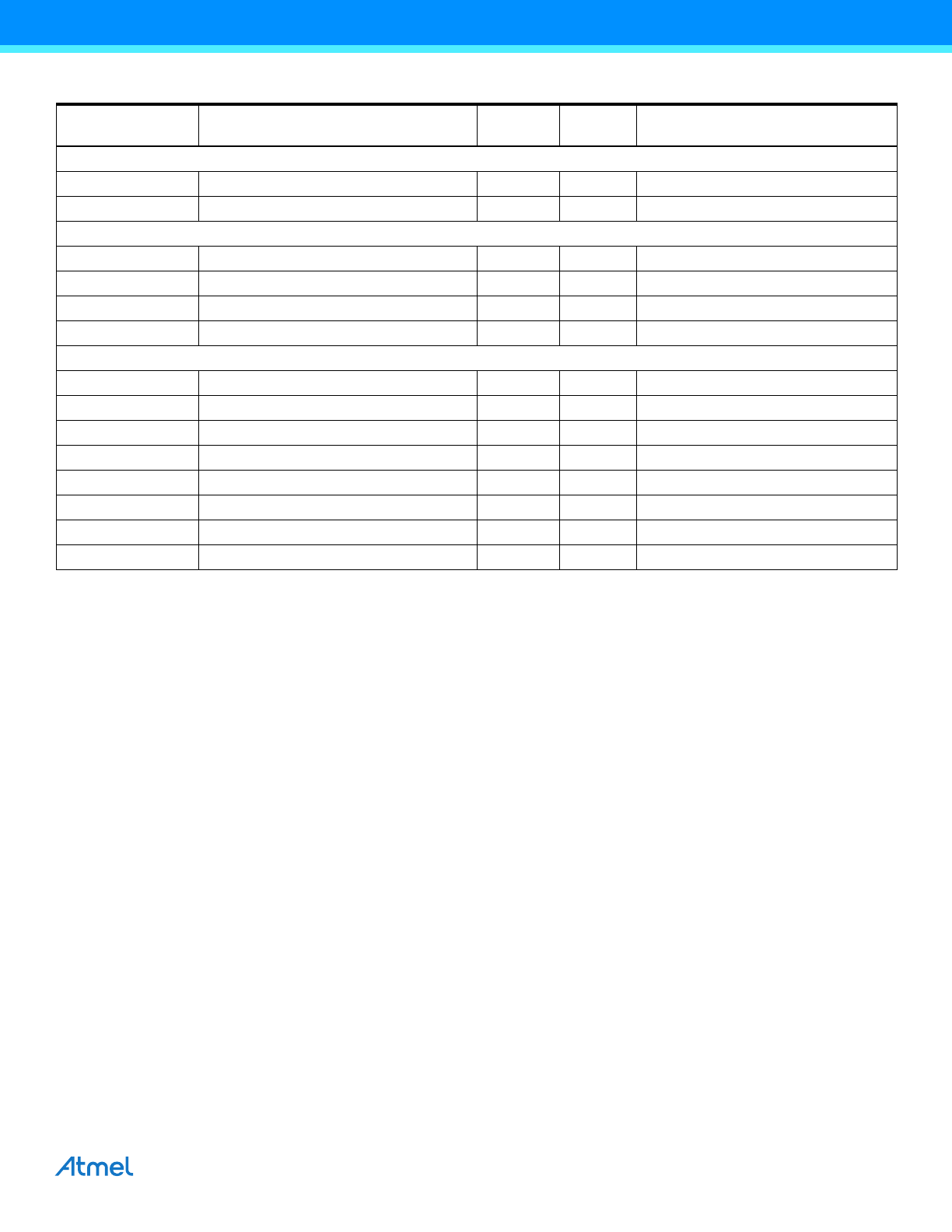

Figure 2-2. SAM7S32/16 Block Diagram

ROM

TDI

TDO

TMS

TCK

NRST

FIQ

IRQ0

PCK0-PCK2

JTAGSEL

RXD0

TXD0

SCK0

RTS0

CTS0

NPCS0

NPCS1

NPCS2

NPCS3

MISO

MOSI

SPCK

DRXD

DTXD

TF

TK

TD

RD

RK

RF

TCLK0

TIOA0

TIOB0

TIOA1

TIOB1

AD0

AD1

AD2

AD3

ADTRG

PLLRC

9 Channels

ADVREF

TWD

TWCK

XIN

XOUT

VDDIN

PWM0

PWM1

PWM2

PWM3

GND

VDDOUT

VDDCORE

VDDCORE

AD4

AD5

AD6

AD7

VDDFLASH

ERASE

PGMD0-PGMD7

PGMNCMD

PGMEN0-PGMEN2

PGMRDY

PGMNVALID

PGMNOE

PGMCK

PGMM0-PGMM3

VDDIO

TST

VDDCORE

SRAM

8/4 Kbytes

ARM7TDMI

Processor

Flash

32/16 Kbytes

APB

SAM-BA

PMC

Peripheral Bridge

Peripheral DMA

Controller

AIC

PLL

RCOSC

ICE

JTAG

SCAN

PIOA

USART0

SSC

Timer Counter

Reset

Controller

Memory Controller

Abort

Status

Address

Decoder

Misalignment

Detection

PIO

PIO

POR

Embedded

Flash

Controller

PDC

PDC

PDC

PDC

SPI

PDC

ADC

PDC

PDC

TC0

TC1

TC2

TWI

OSC

PWMC

1.8 V

Voltage

Regulator

BOD

Fast Flash

Programming

Interface

PIO

DBGU

PDC

PDC

PIO

PIT

WDT

RTT

System Controller

6

SAM7S Series [DATASHEET]

6175KS–ATARM–25-Oct-12

3.

Signal Description

Table 3-1.

Signal Description List

Signal Name

Function

Type

Active

Level

Comments

Power

VDDIN

Voltage and ADC Regulator Power Supply

Input

Power

3.0 to 3.6V

VDDOUT

Voltage Regulator Output

Power

1.85V nominal

VDDFLASH

Flash Power Supply

Power

3.0V to 3.6V

VDDIO

I/O Lines Power Supply

Power

3.0V to 3.6V or 1.65V to 1.95V

VDDCORE

Core Power Supply

Power

1.65V to 1.95V

VDDPLL

PLL

Power

1.65V to 1.95V

GND

Ground

Ground

Clocks, Oscillators and PLLs

XIN

Main Oscillator Input

Input

XOUT

Main Oscillator Output

Output

PLLRC

PLL Filter

Input

PCK0 - PCK2

Programmable Clock Output

Output

ICE and JTAG

TCK

Test Clock

Input

No pull-up resistor

TDI

Test Data In

Input

No pull-up resistor

TDO

Test Data Out

Output

TMS

Test Mode Select

Input

No pull-up resistor

JTAGSEL

JTAG Selection

Input

Pull-down resistor

(1)

Flash Memory

ERASE

Flash and NVM Configuration Bits Erase

Command

Input

High

Pull-down resistor

(1)

Reset/Test

NRST

Microcontroller Reset

I/O

Low

Open-drain with pull-Up resistor

TST

Test Mode Select

Input

High

Pull-down resistor

(1)

Debug Unit

DRXD

Debug Receive Data

Input

DTXD

Debug Transmit Data

Output

AIC

IRQ0 - IRQ1

External Interrupt Inputs

Input

IRQ1 not present on SAM7S32/16

FIQ

Fast Interrupt Input

Input

PIO

PA0 - PA31

Parallel IO Controller A

I/O

Pulled-up input at reset

PA0 - PA20 only on SAM7S32/16

7

SAM7S Series [DATASHEET]

6175KS–ATARM–25-Oct-12

USB Device Port

DDM

USB Device Port Data -

Analog

not present on SAM7S32/16

DDP

USB Device Port Data +

Analog

not present on SAM7S32/16

USART

SCK0 - SCK1

Serial Clock

I/O

SCK1 not present on SAM7S32/16

TXD0 - TXD1

Transmit Data

I/O

TXD1 not present on SAM7S32/16

RXD0 - RXD1

Receive Data

Input

RXD1 not present on SAM7S32/16

RTS0 - RTS1

Request To Send

Output

RTS1 not present on SAM7S32/16

CTS0 - CTS1

Clear To Send

Input

CTS1 not present on SAM7S32/16

DCD1

Data Carrier Detect

Input

not present on SAM7S32/16

DTR1

Data Terminal Ready

Output

not present on SAM7S32/16

DSR1

Data Set Ready

Input

not present on SAM7S32/16

RI1

Ring Indicator

Input

not present on SAM7S32/16

Synchronous Serial Controller

TD

Transmit Data

Output

RD

Receive Data

Input

TK

Transmit Clock

I/O

RK

Receive Clock

I/O

TF

Transmit Frame Sync

I/O

RF

Receive Frame Sync

I/O

Timer/Counter

TCLK0 - TCLK2

External Clock Inputs

Input

TCLK1 and TCLK2 not present on

SAM7S32/16

TIOA0 - TIOA2

I/O Line A

I/O

TIOA2 not present on SAM7S32/16

TIOB0 - TIOB2

I/O Line B

I/O

TIOB2 not present on SAM7S32/16

PWM Controller

PWM0 - PWM3

PWM Channels

Output

SPI

MISO

Master In Slave Out

I/O

MOSI

Master Out Slave In

I/O

SPCK

SPI Serial Clock

I/O

NPCS0

SPI Peripheral Chip Select 0

I/O

Low

NPCS1-NPCS3

SPI Peripheral Chip Select 1 to 3

Output

Low

Table 3-1.

Signal Description List (Continued)

Signal Name

Function

Type

Active

Level

Comments

8

SAM7S Series [DATASHEET]

6175KS–ATARM–25-Oct-12

Note:

1. Refer to

Section 6. “I/O Lines Considerations” on page 14

.

Two-Wire Interface

TWD

Two-wire Serial Data

I/O

TWCK

Two-wire Serial Clock

I/O

Analog-to-Digital Converter

AD0-AD3

Analog Inputs

Analog

Digital pulled-up inputs at reset

AD4-AD7

Analog Inputs

Analog

Analog Inputs

ADTRG

ADC Trigger

Input

ADVREF

ADC Reference

Analog

Fast Flash Programming Interface

PGMEN0-PGMEN2

Programming Enabling

Input

PGMM0-PGMM3

Programming Mode

Input

PGMD0-PGMD15

Programming Data

I/O

PGMD0-PGMD7 only on SAM7S32/16

PGMRDY

Programming Ready

Output

High

PGMNVALID

Data Direction

Output

Low

PGMNOE

Programming Read

Input

Low

PGMCK

Programming Clock

Input

PGMNCMD

Programming Command

Input

Low

Table 3-1.

Signal Description List (Continued)

Signal Name

Function

Type

Active

Level

Comments

9

SAM7S Series [DATASHEET]

6175KS–ATARM–25-Oct-12

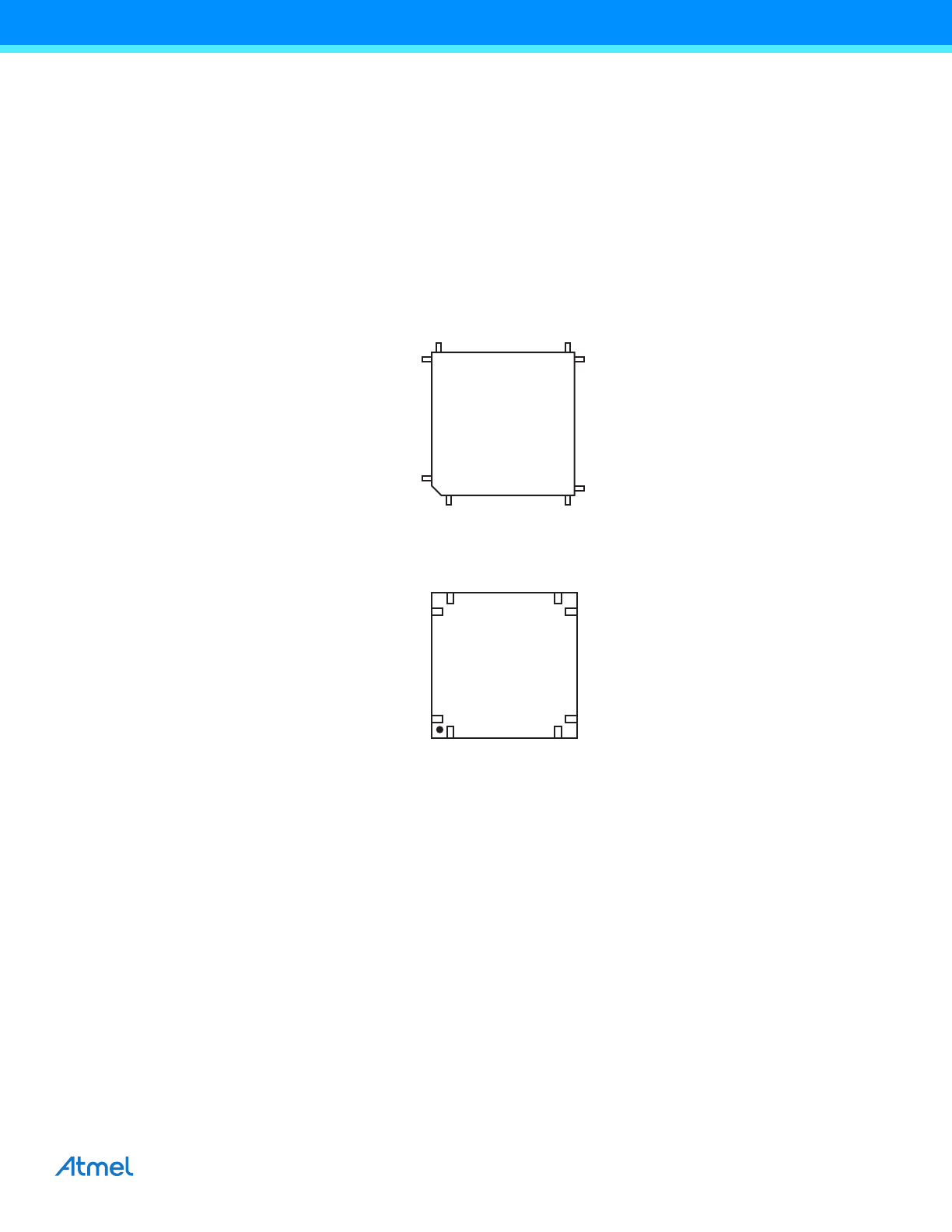

4.

Package and Pinout

The SAM7S512/256/128/64/321 are available in a 64-lead LQFP or 64-pad QFN package.

The SAM7S161 is available in a 64-Lead LQFP package.

The SAM7S32/16 are available in a 48-lead LQFP or 48-pad QFN package.

4.1

64-lead LQFP and 64-pad QFN Package Outlines

Figure 4-1

and

Figure 4-2

show the orientation of the 64-lead LQFP and the 64-pad QFN package. A detailed

mechanical description is given in the section Mechanical Characteristics of the full datasheet.

Figure 4-1. 64-lead LQFP Package (Top View)

Figure 4-2. 64-pad QFN Package (Top View)

1

16

17

32

33

48

49

64

33

48

16

1

49

64

32

17

10

SAM7S Series [DATASHEET]

6175KS–ATARM–25-Oct-12

4.2

64-lead LQFP and 64-pad QFN Pinout

Note:

1. The bottom pad of the QFN package must be connected to ground.

Table 4-1.

SAM7S512/256/128/64/321/161 Pinout

(1)

1

ADVREF

17

GND

33

TDI

49

TDO

2

GND

18

VDDIO

34

PA6/PGMNOE

50

JTAGSEL

3

AD4

19

PA16/PGMD4

35

PA5/PGMRDY

51

TMS

4

AD5

20

PA15/PGMD3

36

PA4/PGMNCMD

52

PA31

5

AD6

21

PA14/PGMD2

37

PA27/PGMD15

53

TCK

6

AD7

22

PA13/PGMD1

38

PA28

54

VDDCORE

7

VDDIN

23

PA24/PGMD12

39

NRST

55

ERASE

8

VDDOUT

24

VDDCORE

40

TST

56

DDM

9

PA17/PGMD5/AD0

25

PA25/PGMD13

41

PA29

57

DDP

10

PA18/PGMD6/AD1

26

PA26/PGMD14

42

PA30

58

VDDIO

11

PA21/PGMD9

27

PA12/PGMD0

43

PA3

59

VDDFLASH

12

VDDCORE

28

PA11/PGMM3

44

PA2/PGMEN2

60

GND

13

PA19/PGMD7/AD2

29

PA10/PGMM2

45

VDDIO

61

XOUT

14

PA22/PGMD10

30

PA9/PGMM1

46

GND

62

XIN/PGMCK

15

PA23/PGMD11

31

PA8/PGMM0

47

PA1/PGMEN1

63

PLLRC

16

PA20/PGMD8/AD3

32

PA7/PGMNVALID

48

PA0/PGMEN0

64

VDDPLL