© 2008 Microchip Technology Inc.

DS21949C-page 1

TC1303A/TC1303B/

TC1303C/TC1304

Features

• Dual-Output Regulator (500 mA Buck Regulator

and 300 mA Low-Dropout Regulator)

• Power-Good Output with 300 ms Delay

• Total Device Quiescent Current = 65 µA, Typical

• Independent Shutdown for Buck and LDO

Outputs (TC1303)

• Both Outputs Internally Compensated

• Synchronous Buck Regulator:

- Over 90% Typical Efficiency

- 2.0 MHz Fixed-Frequency PWM

(Heavy Load)

- Low Output Noise

- Automatic PWM to PFM mode transition

- Adjustable (0.8V to 4.5V) and Standard

Fixed-Output Voltages (0.8V, 1.2V, 1.5V,

1.8V, 2.5V, 3.3V)

• Low-Dropout Regulator:

- Low-Dropout Voltage = 137 mV Typical @

200 mA

- Standard Fixed-Output Voltages

(1.5V, 1.8V, 2.5V, 3.3V)

• Power-Good Function:

- Monitors Buck Output Function (TC1303A)

- Monitors LDO Output Function (TC1303B)

- Monitors Both Buck and LDO Output

Functions (TC1303C and TC1304)

- 300 ms Delay Used for Processor Reset

• Sequenced Startup and Shutdown (TC1304)

• Small 10-pin 3x3 DFN or MSOP Package Options

• Operating Junction Temperature Range:

- -40°C to +125°C

• Undervoltage Lockout (UVLO)

• Output Short Circuit Protection

• Overtemperature Protection

Applications

• Cellular Phones

• Portable Computers

• USB-Powered Devices

• Handheld Medical Instruments

• Organizers and PDAs

Description

The TC1303/TC1304 combines a 500 mA

synchronous buck regulator and 300 mA Low-Dropout

Regulator (LDO) with a power-good monitor to provide

a highly integrated solution for devices that require

multiple supply voltages. The unique combination of an

integrated buck switching regulator and low-dropout

linear regulator provides the lowest system cost for

dual-output voltage applications that require one lower

processor core voltage and one higher bias voltage.

The 500 mA synchronous buck regulator switches at a

fixed frequency of 2.0 MHz when the load is heavy,

providing a low noise, small-size solution. When the

load on the buck output is reduced to light levels, it

changes operation to a Pulse Frequency Modulation

(PFM) mode to minimize quiescent current draw from

the battery. No intervention is necessary for smooth

transition from one mode to another.

The LDO provides a 300 mA auxiliary output that

requires a single 1 µF ceramic output capacitor,

minimizing board area and cost. The typical dropout

voltage for the LDO output is 137 mV for a 200 mA

load.

For the TC1303/TC1304, the power-good output is

based on the regulation of the buck regulator output, the

LDO output or the combination of both. The TC1304

features start-up and shutdown output sequencing.

The TC1303/TC1304 is available in either the 10-pin

DFN or MSOP package.

Additional protection features include: UVLO,

overtemperature and overcurrent protection on both

outputs.

For a complete listing of TC1303/TC1304 standard

parts, consult your Microchip representative.

500 mA Synchronous Buck Regulator,

+ 300 mA LDO with Power-Good Output

TC1303A/TC1303B/TC1303C/TC1304

DS21949C-page 2

© 2008 Microchip Technology Inc.

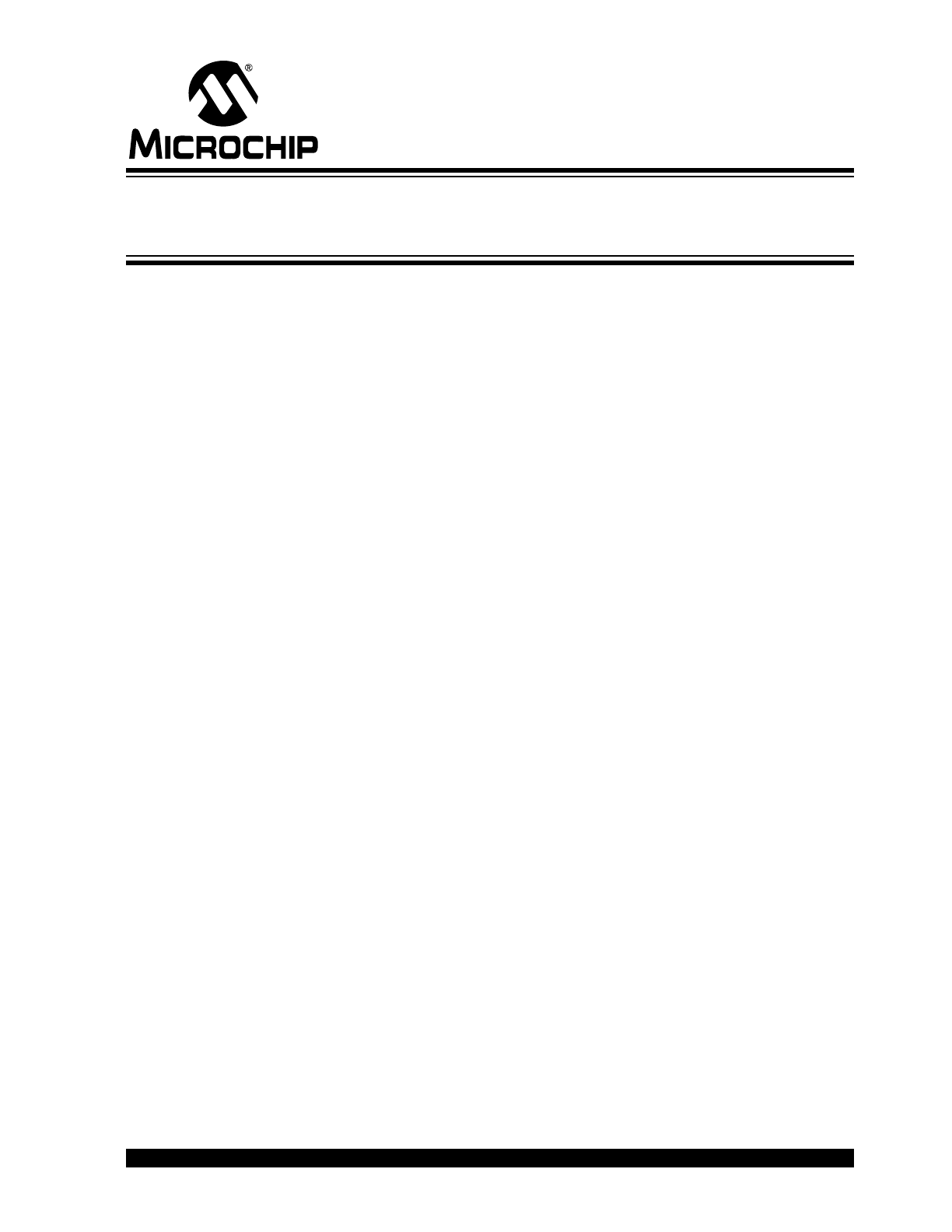

Package Types

10-Lead DFN

V

FB1

/V

OUT1

10-Lead MSOP

1

2

6

8

7

9

10

5

4

3

SHDN2

V

IN2

V

OUT2

A

GND

P

GND

LX

VIN1

SHDN1

V

FB1

/V

OUT1

PG

10-Lead DFN

10-Lead MSOP

1

2

6

8

7

9

10

5

4

3

SHDN

V

IN2

V

OUT2

A

GND

P

GND

L

X

V

IN1

V

FB1

/V

OUT1

PG

A

GND

TC1303A,B,C

TC1304

V

OUT2

V

IN2

PG

L

X

V

IN1

1

2

3

4

10

9

8

7 SHDN1

P

GND

SHDN2

EP

11

5

6

A

GND

V

FB1

/V

OUT1

V

OUT2

V

IN2

PG

L

X

V

IN1

1

2

3

4

10

9

8

7 A

GND

P

GND

SHDN

EP

11

5

6

A

GND

© 2008 Microchip Technology Inc.

DS21949C-page 3

TC1303A/TC1303B/TC1303C/TC1304

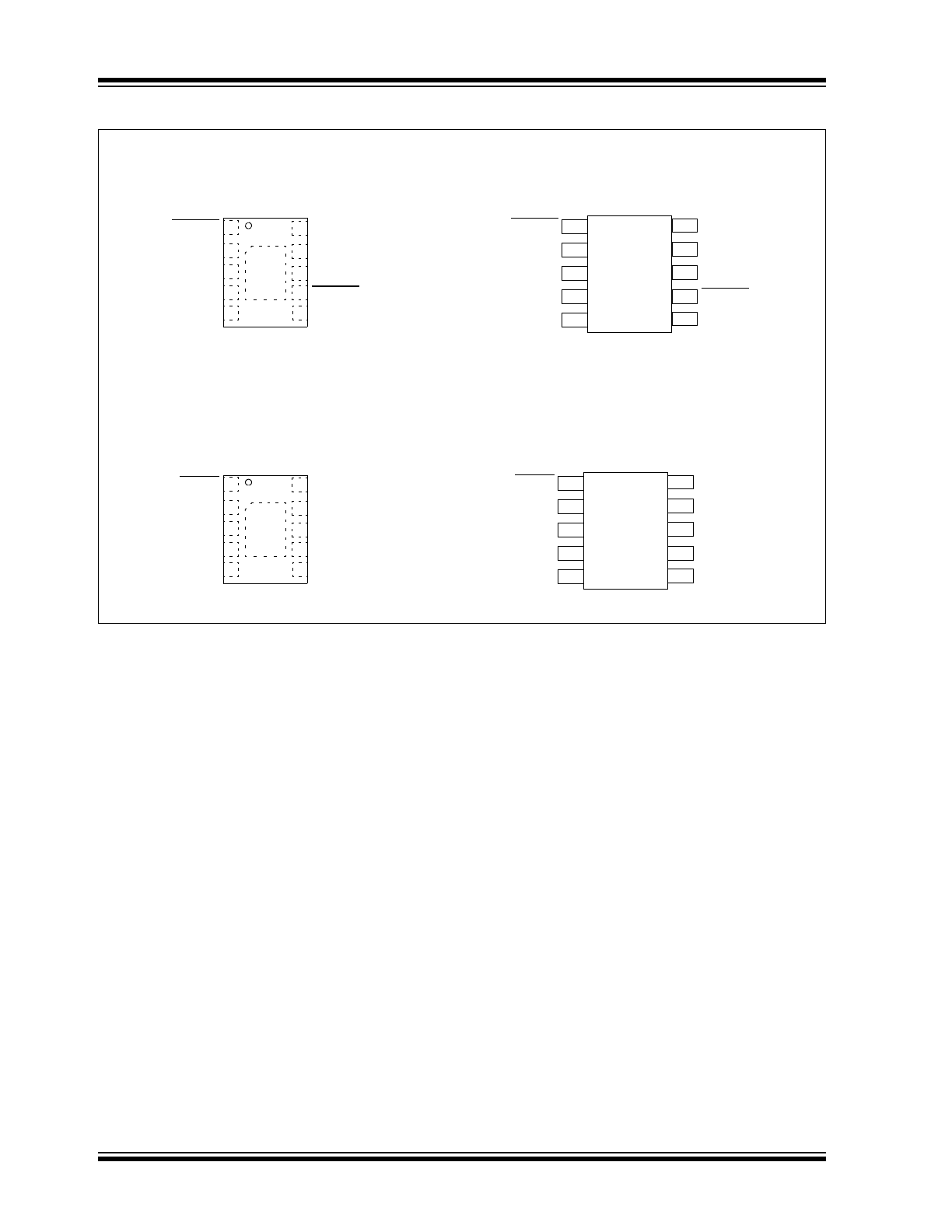

Functional Block Diagram – TC1303

Synchronous Buck Regulator

NDRV

PDRV

P

GND

V

IN1

L

X

Driver

P

GND

Control

V

OUT1

/V

FB1

V

IN2

SHDN1

PG

V

REF

LDO

V

OUT2

A

GND

A

GND

P

GND

Undervoltage Lockout

UVLO

UVLO

SHDN2

V

REF

TC1303A

(1)

,B

(2)

,C

(1)

options

PG Generator with Delay

(UVLO)

Sense LDO for B,C

Sense Switcher for A,C

Note 1: PG open-drain for A,C options

2: PG push-pull output for B option

TC1303A/TC1303B/TC1303C/TC1304

DS21949C-page 4

© 2008 Microchip Technology Inc.

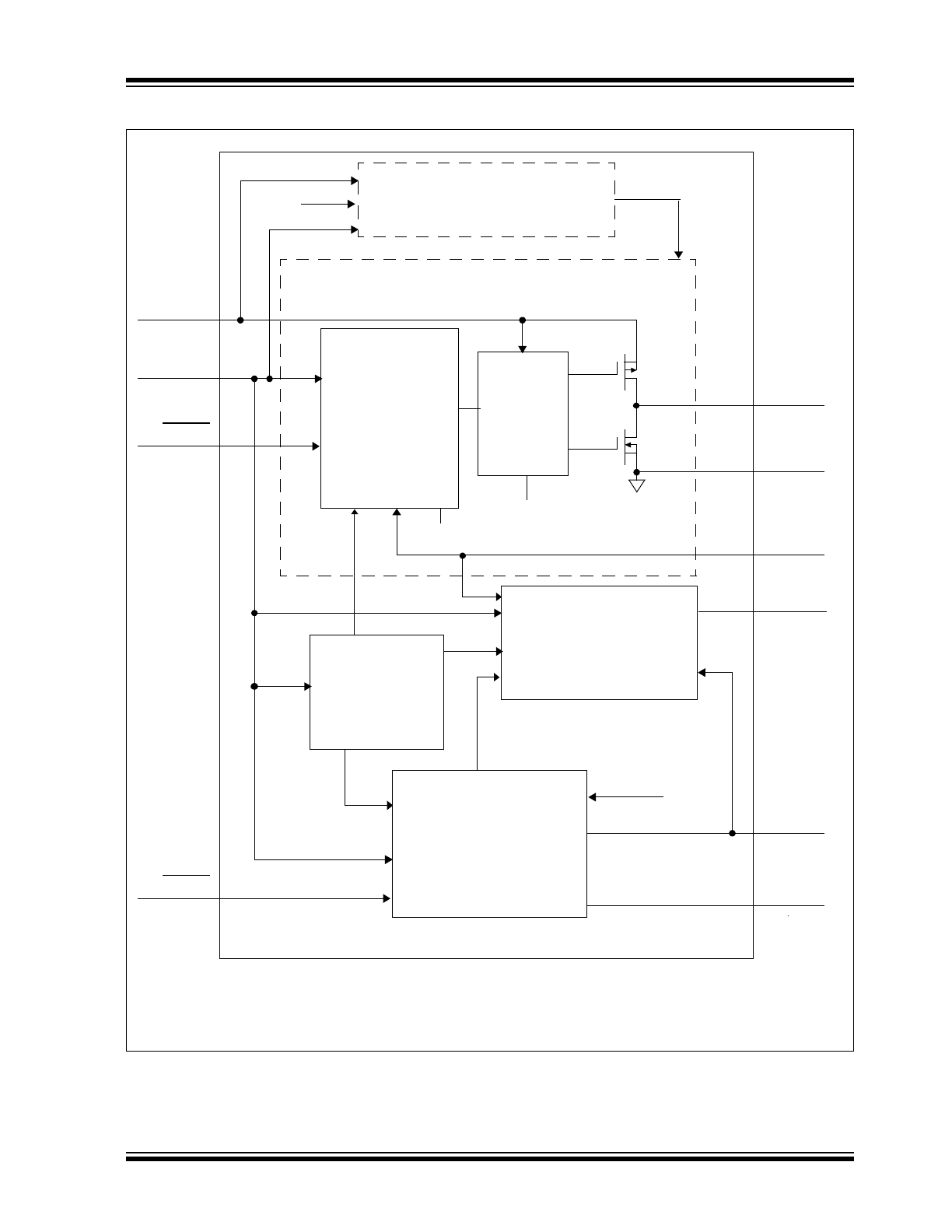

Functional Block Diagram – TC1304

Synchronous Buck Regulator

NDRV

PDRV

P

GND

V

IN1

L

X

Driver

P

GND

Control

V

OUT1

/V

FB1

V

IN2

SHDN

PG

V

REF

LDO

V

OUT2

A

GND

A

GND

P

GND

Undervoltage Lockout

UVLO

UVLO

V

REF

TC1304

(Note)

PG Generator with Delay

(UVLO)

Output Voltage

Sequencer ckt.

A

GND

Note:

PG open-drain for TC1304

© 2008 Microchip Technology Inc.

DS21949C-page 5

TC1303A/TC1303B/TC1303C/TC1304

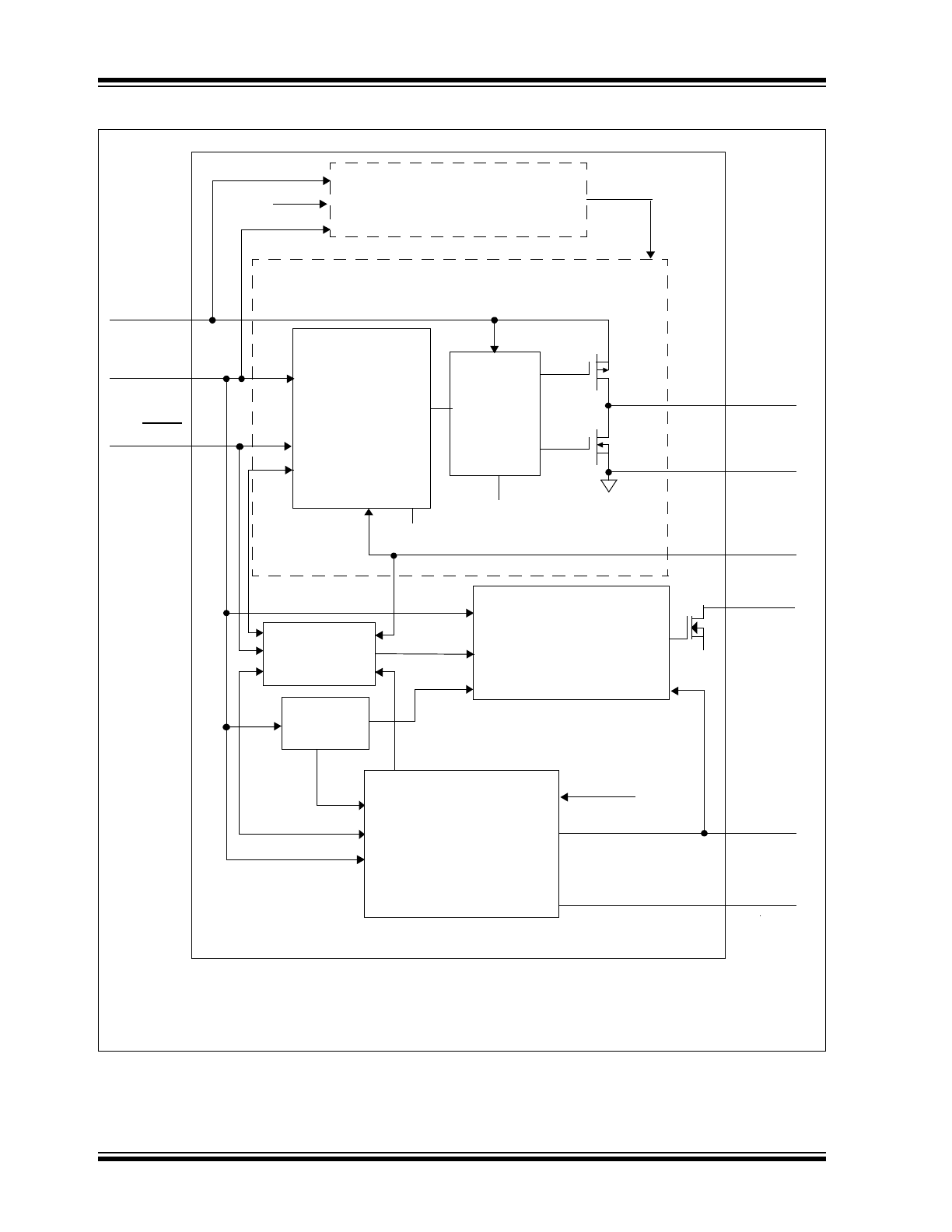

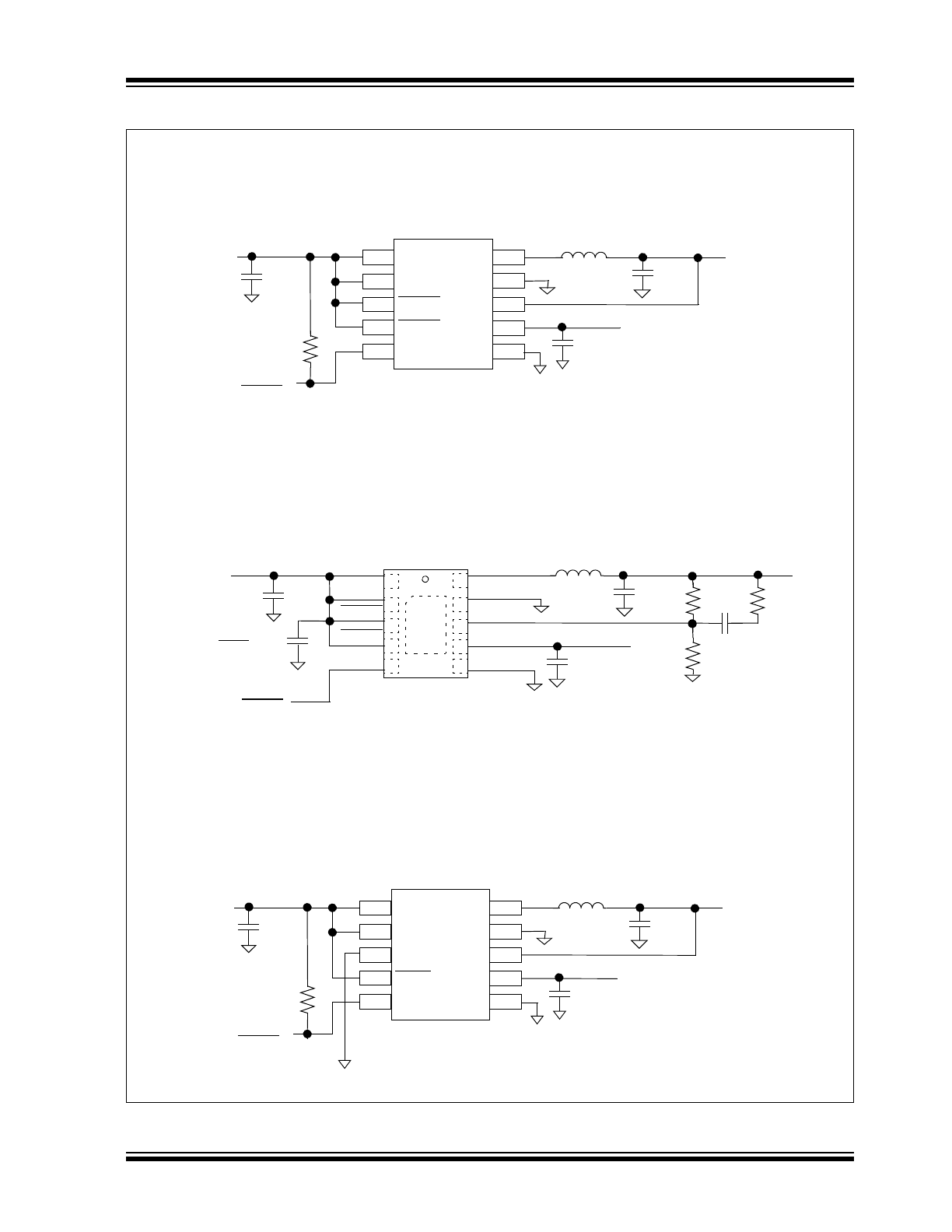

Typical Application Circuits

10-Lead DFN

1

2

6

8

7

9

10

5

4

3

SHDN2

V

IN2

V

OUT2

A

GND

P

GND

L

X

V

IN1

SHDN1

V

OUT1

PG

4.7 μF

Processor

RESET

Input

Voltage

4.7 μH

4.7

Μ

F

2.1V @

1

Μ

F

3.3V @

4.5V to 5.5V

Adjustable-Output Application

121 kΩ

200 kΩ

4.99 kΩ

33 pF

1

2

6

8

7

9

10

5

4

3

SHDN2

V

IN2

V

OUT2

A

GND

P

GND

L

X

V

IN1

SHDN1

V

OUT1

PG

4.7 μF

Processor

RESET

4.7 μH

4.7 μF

1.5V @ 500 mA

1 μF

2.5V @ 300 mA

2.7V to 4.2V

TC1303B

V

OUT1

V

OUT2

V

IN

V

OUT1

V

OUT2

1.0 μF

*Optional

Capacitor

V

IN2

300 mA

500 mA

Note: Connect DFN package exposed pad to A

GND

.

10-Lead MSOP

Fixed-Output Application

TC1303A

(Note)

R

PULLUP

1

2

6

8

7

9

10

5

4

3

SHDN

V

IN2

V

OUT2

A

GND

P

GND

L

X

V

IN1

V

OUT1

PG

4.7 μF

Processor

RESET

4.7 μH

4.7

Μ

F

1.2V @ 500 mA

1 μF

2.5V @ 300 mA

2.7V to 4.2V

V

OUT1

V

OUT2

V

IN

10-Lead MSOP

Fixed-Output Application

TC1304

R

PULLUP

A

GND

EP

11

TC1303A/TC1303B/TC1303C/TC1304

DS21949C-page 6

© 2008 Microchip Technology Inc.

NOTES:

© 2008 Microchip Technology Inc.

DS21949C-page 7

TC1303A/TC1303B/TC1303C/TC1304

1.0

ELECTRICAL

CHARACTERISTICS

Absolute Maximum Ratings †

V

IN

- A

GND

.......................................................................6.0V

All Other I/O ...............................(A

GND

- 0.3V) to (V

IN

+ 0.3V)

L

X

to P

GND

...............................................-0.3V to (V

IN

+ 0.3V)

P

GND

to A

GND

.................................................. -0.3V to +0.3V

Output Short Circuit Current ................................ Continuous

Power Dissipation (Note 7) .......................... Internally Limited

Storage temperature .....................................-65°C to +150°C

Ambient Temp. with Power Applied ................-40°C to +85°C

Operating Junction Temperature...................-40°C to +125°C

ESD protection on all pins (HBM)

....................................... 3 kV

† Notice: Stresses above those listed under “Maximum

Ratings” may cause permanent damage to the device. This is

a stress rating only and functional operation of the device at

those or any other conditions above those indicated in the

operational listings of this specification is not implied.

Exposure to maximum rating conditions for extended periods

may affect device reliability.

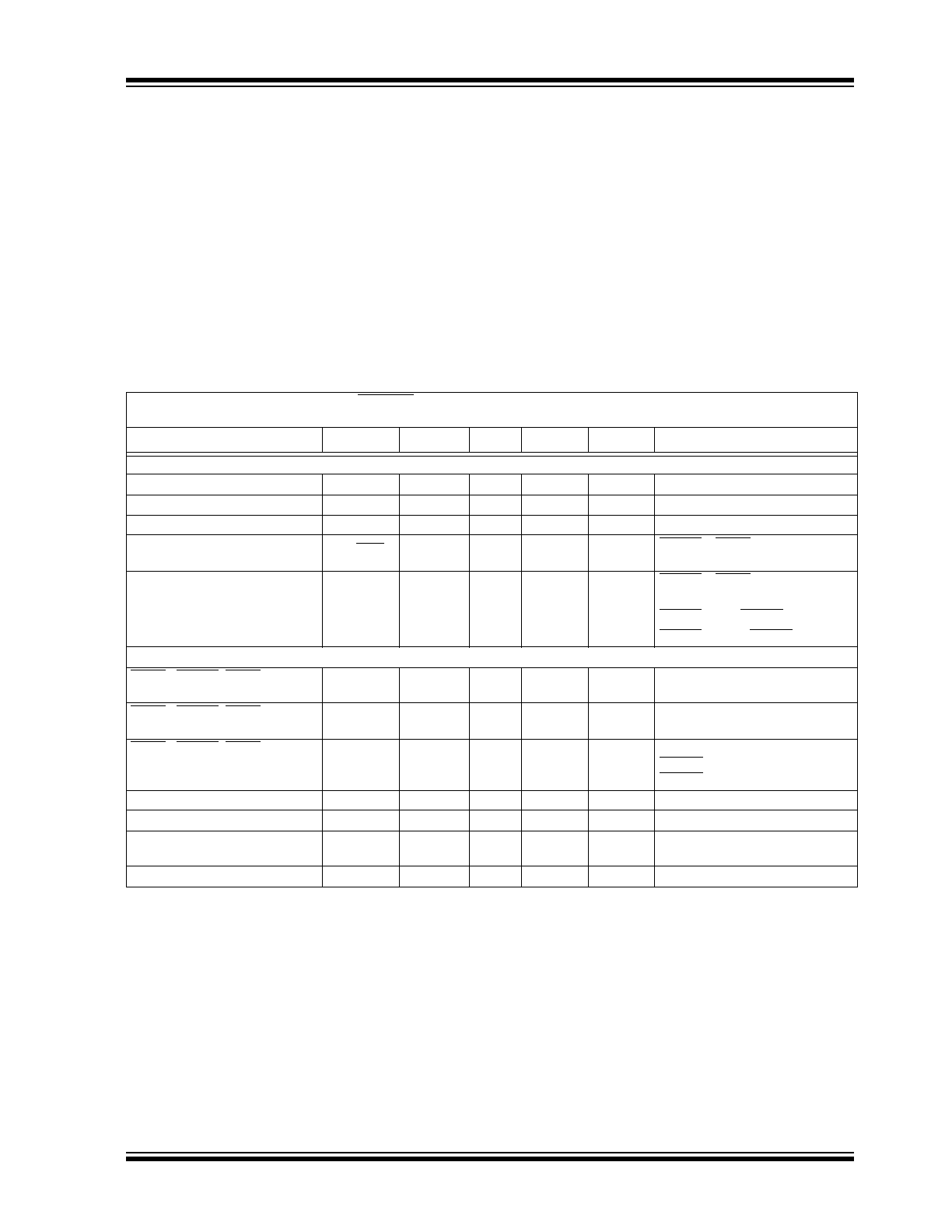

DC CHARACTERISTICS

Electrical Characteristics: V

IN1

=V

IN2

= SHDN1,2 = 3.6V, C

OUT1

= C

IN

= 4.7 µF, C

OUT2

= 1 µF, L

= 4.7 µH, V

OUT1

(ADJ) = 1.8V,

I

OUT1

= 100 mA, I

OUT2

= 0.1 mA T

A

= +25°C. Boldface specifications apply over the T

A

range of -40°C to +85°C.

Parameters

Sym

Min

Typ

Max

Units

Conditions

Input/Output Characteristics

Input Voltage

V

IN

2.7

—

5.5

V

Note 1, Note 2, Note 8

Maximum Output Current

I

OUT1_MAX

500

—

—

mA

Note 1

Maximum Output Current

I

OUT2_MAX

300

—

—

mA

Note 1

Shutdown Current

Combined V

IN1

and V

IN2

Current

I

IN_SHDN

—

0.05

1

µA

SHDN1 = SHDN2 = GND

TC1303A,B Operating I

Q

TC1303C, TC1304 Operating I

Q

I

Q

I

Q

—

65.0

70.1

110

110

µA

SHDN1 = SHDN2 = V

IN2

I

OUT1

= 0 mA, I

OUT2

= 0 mA

Synchronous Buck I

Q

—

38

—

µA

SHDN1 = V

IN

, SHDN2 = GND

LDO I

Q

—

46

—

µA

SHDN1 = GND, SHDN2 = V

IN2

Shutdown/UVLO/Thermal Shutdown Characteristics

SHDN1,SHDN2, SHDN (TC1304)

Logic Input Voltage Low

V

IL

—

—

15

%V

IN

V

IN1

=V

IN2

= 2.7V to 5.5V

SHDN1,SHDN2, SHDN (TC1304)

Logic Input Voltage High

V

IH

45

—

—

%V

IN

V

IN1

=V

IN2

= 2.7V to 5.5V

SHDN1,SHDN2, SHDN (TC1304)

Input Leakage Current

I

IN

-1.0

±0.01

1.0

µA

V

IN1

=V

IN2

= 2.7V to 5.5V

SHDNX = GND

SHDNY = V

IN

Thermal Shutdown

T

SHD

—

165

—

°C

Note 6, Note 7

Thermal Shutdown Hysteresis

T

SHD-HYS

—

10

—

°C

Undervoltage Lockout

(V

OUT1

and V

OUT2

)

UVLO

2.4

2.55

2.7

V

V

IN1

Falling

Undervoltage Lockout Hysteresis

UVLO

-

HYS

—

200

—

mV

Note 1:

The Minimum V

IN

has to meet two conditions: V

IN

≥ 2.7V and V

IN

≥ V

RX

+ V

DROPOUT,

V

RX

= V

R1

or V

R2

.

2:

V

RX

is the regulator output voltage setting.

3:

TCV

OUT2

= ((V

OUT2max

– V

OUT2min

) * 10

6

)/(V

OUT2

* D

T

).

4:

Regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is tested

over a load range from 0.1 mA to the maximum specified output current.

5:

Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its

nominal value measured at a 1V differential.

6:

The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction

temperature and the thermal resistance from junction to air. (i.e. T

A

, T

J

,

θ

JA

). Exceeding the maximum allowable power

dissipation causes the device to initiate thermal shutdown.

7:

The integrated MOSFET switches have an integral diode from the L

X

pin to V

IN

, and from L

X

to P

GND

. In cases where

these diodes are forward-biased, the package power dissipation limits must be adhered to. Thermal protection is not

able to limit the junction temperature for these cases.

8:

V

IN1

and V

IN2

are supplied by the same input source.

TC1303A/TC1303B/TC1303C/TC1304

DS21949C-page 8

© 2008 Microchip Technology Inc.

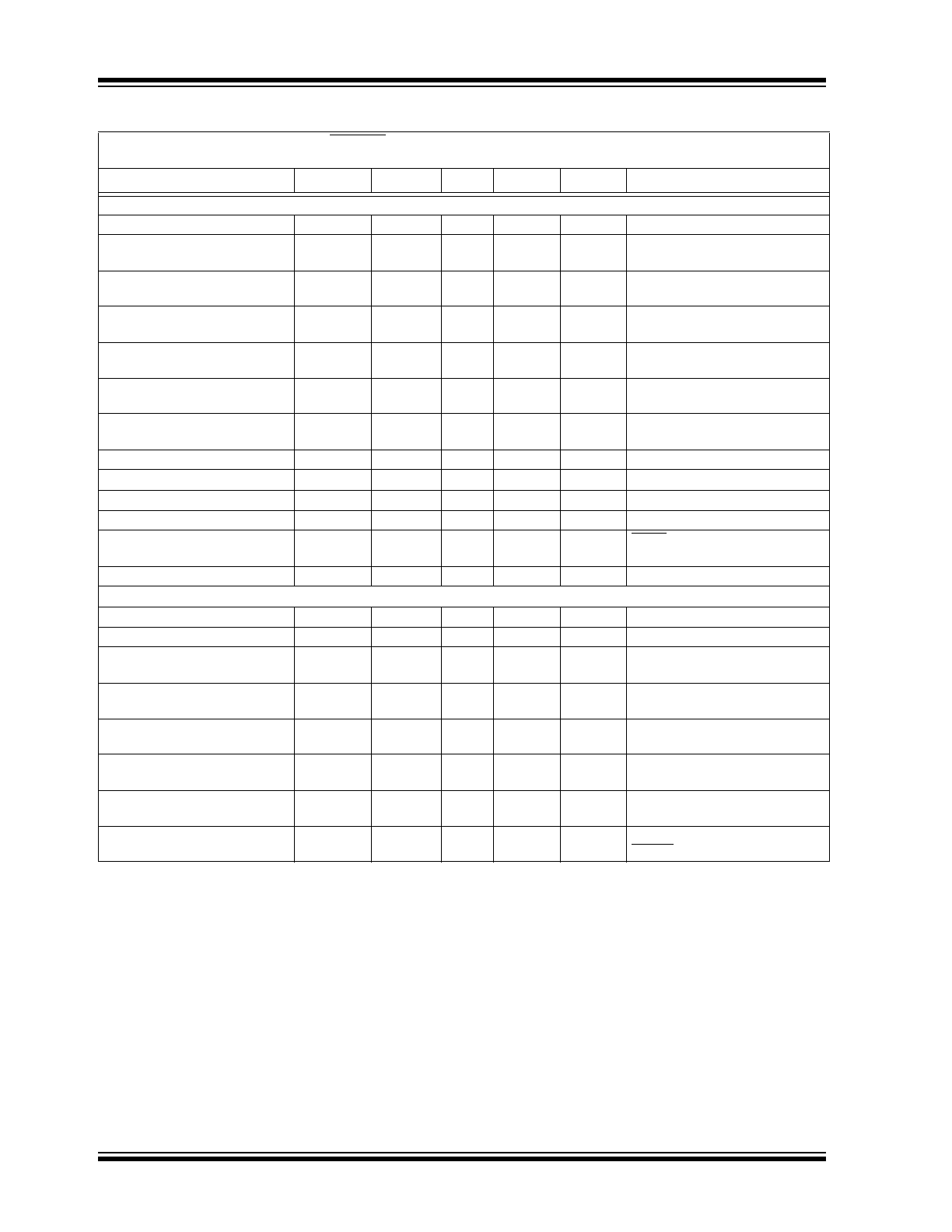

Synchronous Buck Regulator (V

OUT1

)

Adjustable Output Voltage Range

V

OUT1

0.8

—

4.5

V

Adjustable Reference Feedback

Voltage (V

FB1

)

V

FB1

0.78

0.8

0.82

V

Feedback Input Bias Current

(

IFB1

)

I

VFB1

—

-1.5

—

nA

Output Voltage Tolerance Fixed

(V

OUT1

)

V

OUT1

-2.5

±0.3

+2.5

%

Note 2

Line Regulation (V

OUT1

)

V

LINE-REG

—

0.2

—

%/V

V

IN

=V

R

+1V to 5.5V,

I

LOAD

= 100 mA

Load Regulation (V

OUT1

)

V

LOAD-REG

—

0.2

—

%

V

IN

= V

R

+ 1.5V, I

LOAD

= 100 mA to

500 mA (Note 1)

Dropout Voltage V

OUT1

V

IN

– V

OUT1

—

280

—

mV

I

OUT1

= 500 mA, V

OUT1

= 3.3V

(Note 5)

Internal Oscillator Frequency

F

OSC

1.6

2.0

2.4

MHz

Start Up Time

T

SS

—

0.5

—

ms

T

R

= 10% to 90%

R

DSon

P-Channel

R

DSon-P

—

450

—

m

Ω

I

P

=100 mA

R

DSon

N-Channel

R

DSon-N

—

450

—

m

Ω

I

N

=100 mA

L

X

Pin Leakage Current

I

LX

-1.0

±0.01

1.0

μA

SHDN = 0V, V

IN

= 5.5V, L

X

= 0V,

L

X

= 5.5V

Positive Current Limit Threshold

+I

LX(MAX)

—

700

—

mA

LDO Output (V

OUT2

)

Output Voltage Tolerance (V

OUT2

)

V

OUT2

-2.5

±0.3

+2.5

%

Note 2

Temperature Coefficient

TCV

OUT

—

25

—

ppm/°C

Note 3

Line Regulation

∆V

OUT2

/

∆V

IN

-0.2

±0.02

+0.2

%/V

(V

R

+1V)

≤ V

IN

≤ 5.5V

Load Regulation, V

OUT2

≥ 2.5V

∆V

OUT2

/

I

OUT2

-0.75

-0.08

+0.75

%

I

OUT2

= 0.1 mA to 300 mA

(Note 4)

Load Regulation, V

OUT2

< 2.5V

∆V

OUT2

/

I

OUT2

-0.9

-0.18

+0.9

%

I

OUT2

= 0.1 mA to 300 mA

(Note 4)

Dropout Voltage V

OUT2

> 2.5V

V

IN

– V

OUT2

—

137

205

300

500

mV

I

OUT2

= 200 mA (Note 5)

I

OUT2

= 300 mA

Power Supply Rejection Ratio

PSRR

—

62

—

dB

f

≤ 100 Hz, I

OUT1

= I

OUT2

= 50 mA,

C

IN

= 0 µF

Output Noise

eN

—

1.8

—

µV/(Hz)

½

f

≤ 1 kHz, I

OUT2

= 50 mA,

SHDN1 = GND

DC CHARACTERISTICS (CONTINUED)

Electrical Characteristics: V

IN1

=V

IN2

= SHDN1,2 = 3.6V, C

OUT1

= C

IN

= 4.7 µF, C

OUT2

= 1 µF, L

= 4.7 µH, V

OUT1

(ADJ) = 1.8V,

I

OUT1

= 100 mA, I

OUT2

= 0.1 mA T

A

= +25°C. Boldface specifications apply over the T

A

range of -40°C to +85°C.

Parameters

Sym

Min

Typ

Max

Units

Conditions

Note 1:

The Minimum V

IN

has to meet two conditions: V

IN

≥ 2.7V and V

IN

≥ V

RX

+ V

DROPOUT,

V

RX

= V

R1

or V

R2

.

2:

V

RX

is the regulator output voltage setting.

3:

TCV

OUT2

= ((V

OUT2max

– V

OUT2min

) * 10

6

)/(V

OUT2

* D

T

).

4:

Regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is tested

over a load range from 0.1 mA to the maximum specified output current.

5:

Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its

nominal value measured at a 1V differential.

6:

The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction

temperature and the thermal resistance from junction to air. (i.e. T

A

, T

J

,

θ

JA

). Exceeding the maximum allowable power

dissipation causes the device to initiate thermal shutdown.

7:

The integrated MOSFET switches have an integral diode from the L

X

pin to V

IN

, and from L

X

to P

GND

. In cases where

these diodes are forward-biased, the package power dissipation limits must be adhered to. Thermal protection is not

able to limit the junction temperature for these cases.

8:

V

IN1

and V

IN2

are supplied by the same input source.

© 2008 Microchip Technology Inc.

DS21949C-page 9

TC1303A/TC1303B/TC1303C/TC1304

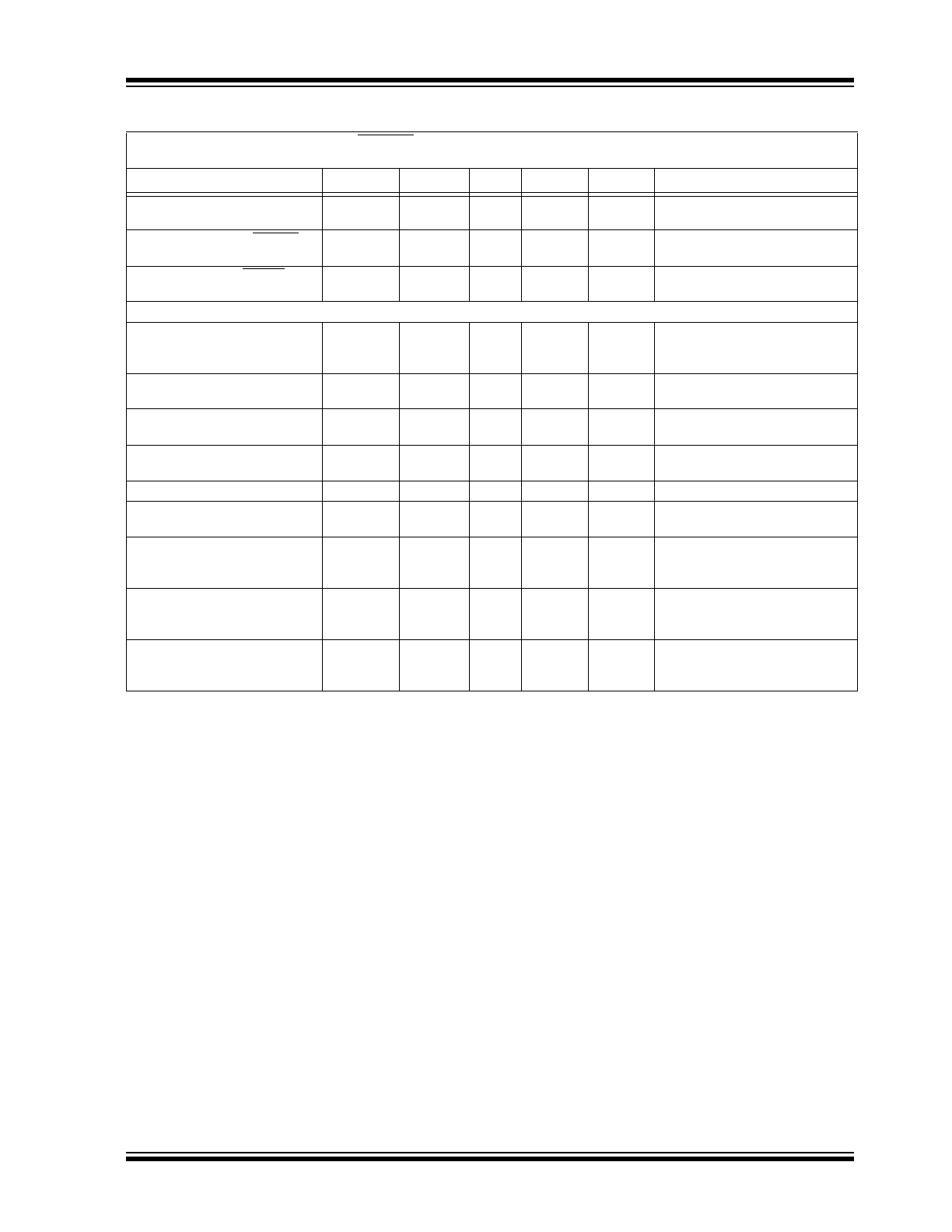

Output Short Circuit Current

(Average)

I

OUTsc2

—

240

—

mA

R

LOAD2

≤ 1Ω

Wake-Up Time (From SHDN2

mode), (V

OUT2

)

t

WK

—

31

100

µs

I

OUT1

= I

OUT2

= 50 mA

Settling Time (From SHDN2

mode), (V

OUT2

)

t

S

—

100

—

µs

I

OUT1

= I

OUT2

= 50 mA

Power-Good (PG)

Voltage Range PG

V

PG

1.0

1.2

—

5.5

5.5

V

T

A

= 0°C to +70°C

T

A

= -40°C to +85°C

V

IN

≤ 2.7 I

SINK

= 100 µA

PG Threshold High

(V

OUT1

or V

OUT2

)

V

TH_H

—

94

96

% of

V

OUTX

On Rising V

OUT1

or V

OUT2

V

OUTX

= V

OUT1

or V

OUT2

PG Threshold Low

(V

OUT1

or V

OUT2

)

V

TH_L

89

92

—

% of

V

OUTX

On Falling V

OUT1

or V

OUT2

V

OUTX

= V

OUT1

or V

OUT2

PG Threshold Hysteresis

(V

OUT1

and V

OUT2

)

V

TH_HYS

—

2

—

% of

V

OUTX

V

OUTX

= V

OUT1

or V

OUT2

PG Threshold Tempco

ΔV

TH

/

ΔT

—

30

—

ppm/°C

PG Delay

t

RPD

—

165

—

µs

V

OUT1

or V

OUT2

= (V

TH

+ 100 mV)

to (V

TH

- 100 mV)

PG Active Time-out Period

t

RPU

140

262

560

ms

V

OUT1

or V

OUT2

= V

TH

- 100 mV

to V

TH +

100 mV,

I

SINK

= 1.2 mA

PG Output Voltage Low

PG_V

OL

—

—

0.2

V

V

OUT1

or V

OUT2

= V

TH

- 100 mV

,

I

PG

= 1.2 mA V

IN2

> 2.7V

I

PG

= 100 µA, 1.0V < V

IN2

< 2.7V

PG Output Voltage High

(TC1303B only)

PG_V

OH

0.9* V

OUT2

—

—

V

V

OUT1

or V

OUT2

= V

TH

+ 100 mV

V

OUT2

≥ 1.8V, I

PG

= - 500 µA

V

OUT2

< 1.8V,I

PG

= - 300 µA

DC CHARACTERISTICS (CONTINUED)

Electrical Characteristics: V

IN1

=V

IN2

= SHDN1,2 = 3.6V, C

OUT1

= C

IN

= 4.7 µF, C

OUT2

= 1 µF, L

= 4.7 µH, V

OUT1

(ADJ) = 1.8V,

I

OUT1

= 100 mA, I

OUT2

= 0.1 mA T

A

= +25°C. Boldface specifications apply over the T

A

range of -40°C to +85°C.

Parameters

Sym

Min

Typ

Max

Units

Conditions

Note 1:

The Minimum V

IN

has to meet two conditions: V

IN

≥ 2.7V and V

IN

≥ V

RX

+ V

DROPOUT,

V

RX

= V

R1

or V

R2

.

2:

V

RX

is the regulator output voltage setting.

3:

TCV

OUT2

= ((V

OUT2max

– V

OUT2min

) * 10

6

)/(V

OUT2

* D

T

).

4:

Regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is tested

over a load range from 0.1 mA to the maximum specified output current.

5:

Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its

nominal value measured at a 1V differential.

6:

The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction

temperature and the thermal resistance from junction to air. (i.e. T

A

, T

J

,

θ

JA

). Exceeding the maximum allowable power

dissipation causes the device to initiate thermal shutdown.

7:

The integrated MOSFET switches have an integral diode from the L

X

pin to V

IN

, and from L

X

to P

GND

. In cases where

these diodes are forward-biased, the package power dissipation limits must be adhered to. Thermal protection is not

able to limit the junction temperature for these cases.

8:

V

IN1

and V

IN2

are supplied by the same input source.

TC1303A/TC1303B/TC1303C/TC1304

DS21949C-page 10

© 2008 Microchip Technology Inc.

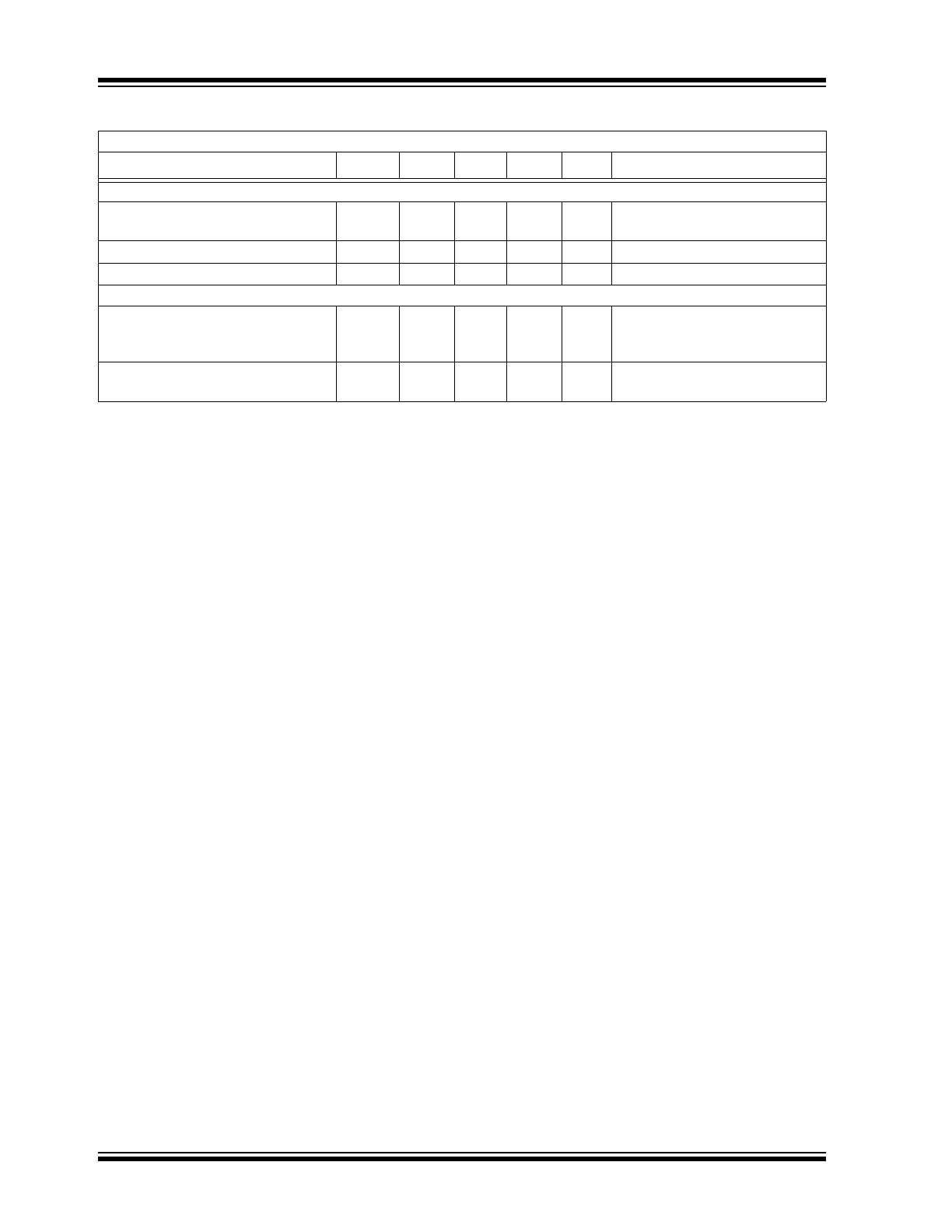

TEMPERATURE SPECIFICATIONS

Electrical Specifications: Unless otherwise indicated, all limits are specified for: V

IN

= +2.7V to +5.5V

Parameters

Sym

Min

Typ

Max

Units

Conditions

Temperature Ranges

Operating Junction Temperature

Range

T

J

-40

—

+125

°C

Steady state

Storage Temperature Range

T

A

-65

—

+150

°C

Maximum Junction Temperature

T

J

—

—

+150

°C

Transient

Thermal Package Resistances

Thermal Resistance, 10L-DFN

θ

JA

—

41

—

°C/W Typical 4-layer Board with

Internal Ground Plane and 2 Vias

in Thermal Pad

Thermal Resistance, 10L-MSOP

θ

JA

—

113

—

°C/W Typical 4-layer Board with

Internal Ground Plane