© 2008 Microchip Technology Inc.

DS22056B-page 1

MCP1825/MCP1825S

Features

• 500 mA Output Current Capability

• Input Operating Voltage Range: 2.1V to 6.0V

• Adjustable Output Voltage Range: 0.8V to 5.0V

(MCP1825 only)

• Standard Fixed Output Voltages:

- 0.8V, 1.2V, 1.8V, 2.5V, 3.0V, 3.3V, 5.0V

• Other Fixed Output Voltage Options Available

Upon Request

• Low Dropout Voltage: 210 mV Typical at 500 mA

• Typical Output Voltage Tolerance: 0.5%

• Stable with 1.0 µF Ceramic Output Capacitor

• Fast response to Load Transients

• Low Supply Current: 120 µA (typical)

• Low Shutdown Supply Current: 0.1 µA (typical)

(MCP1825 only)

• Fixed Delay on Power Good Output

(MCP1825 only)

• Short Circuit Current Limiting and

Overtemperature Protection

• TO-263-5 (DDPAK-5), TO-220-5, SOT-223-5

Package Options (MCP1825).

• TO-263-3 (DDPAK-3), TO-220-3, SOT-223-3

Package Options (MCP1825S).

Applications

• High-Speed Driver Chipset Power

• Networking Backplane Cards

• Notebook Computers

• Network Interface Cards

• Palmtop Computers

• 2.5V to 1.XV Regulators

Description

The MCP1825/MCP1825S is a 500 mA Low Dropout

(LDO) linear regulator that provides high current and

low output voltages. The MCP1825 comes in a fixed or

adjustable output voltage version, with an output

voltage range of 0.8V to 5.0V. The 500 mA output

current capability, combined with the low output voltage

capability, make the MCP1825 a good choice for new

sub-1.8V output voltage LDO applications that have

high current demands. The MCP1825S is a 3-pin fixed

voltage version.

The MCP1825/MCP1825S is stable using ceramic

output capacitors that inherently provide lower output

noise and reduce the size and cost of the entire

regulator solution. Only 1 µF of output capacitance is

needed to stabilize the LDO.

Using CMOS construction, the quiescent current

consumed by the MCP1825/MCP1825S is typically

less than 120 µA over the entire input voltage range,

making it attractive for portable computing applications

that demand high output current. The MCP1825

versions have a Shutdown (SHDN) pin. When shut

down, the quiescent current is reduced to less than

0.1 µA.

On the MCP1825 fixed output versions, the scaled-

down output voltage is internally monitored and a

power good (PWRGD) output is provided when the

output is within 92% of regulation (typical). The

PWRGD delay is internally fixed at 110 µs (typical).

The overtemperature and short circuit current-limiting

provide additional protection for the LDO during system

fault conditions.

500 mA, Low Voltage, Low Quiescent Current LDO Regulator

MCP1825/MCP1825S

DS22056B-page 2

© 2008 Microchip Technology Inc.

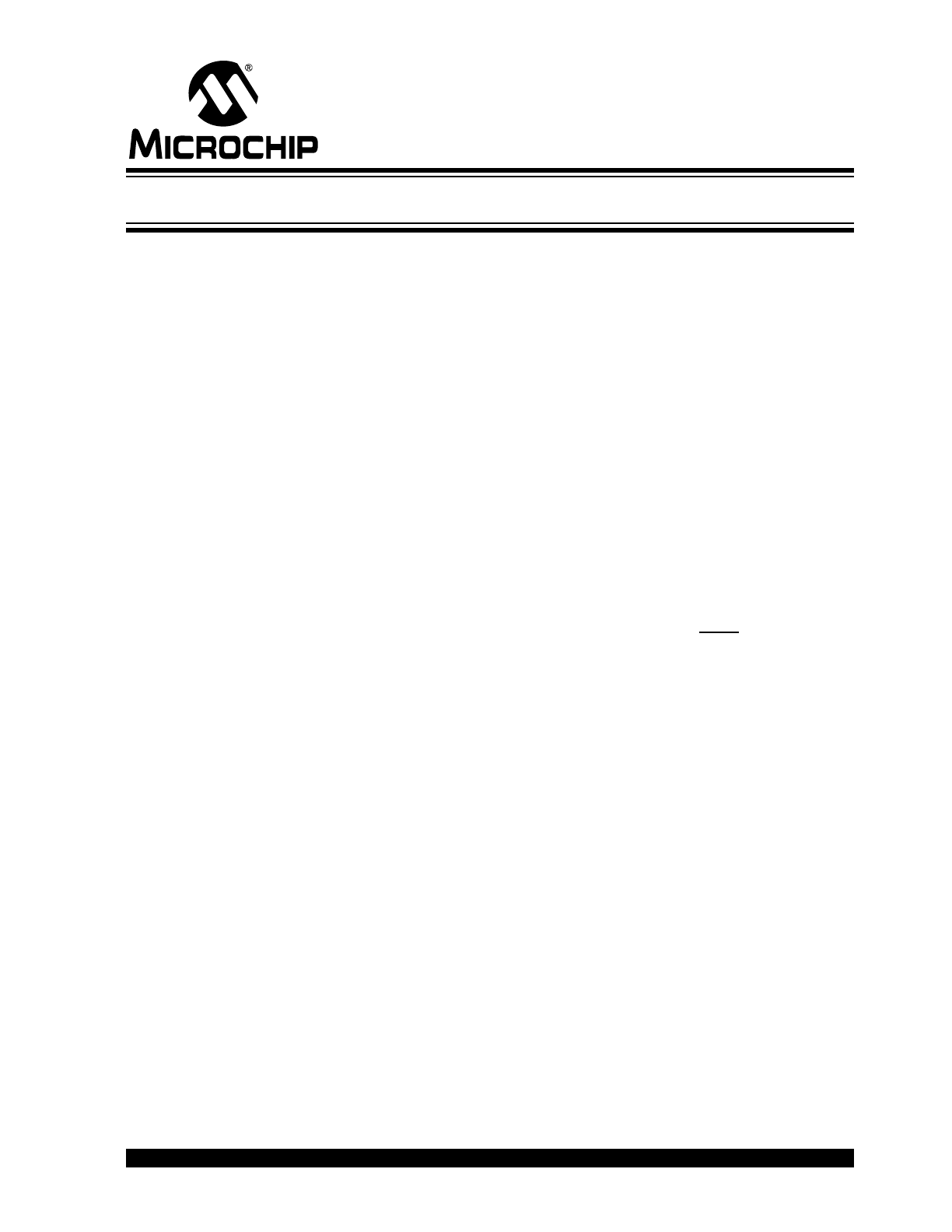

Package Types

MCP1825

1

2

3

4

5

6

SOT-223-5

Pin

Fixed

Adjustable

1

SHDN

SHDN

2

V

IN

V

IN

3

GND (TAB)

GND (TAB)

4

V

OUT

V

OUT

5

PWRGD

ADJ

6

GND (TAB)

GND (TAB)

1

2

3

SOT-223-3

4

MCP1825S

Pin

1

V

IN

2

GND (TAB)

3

V

OUT

4

GND (TAB)

Fixed/Adjustable

DDPAK-3

DDPAK-5

TO-220-3

TO-220-5

1 2 3 4 5

1 2 3 4 5

1

2

3

1

2

3

© 2008 Microchip Technology Inc.

DS22056B-page 3

MCP1825/MCP1825S

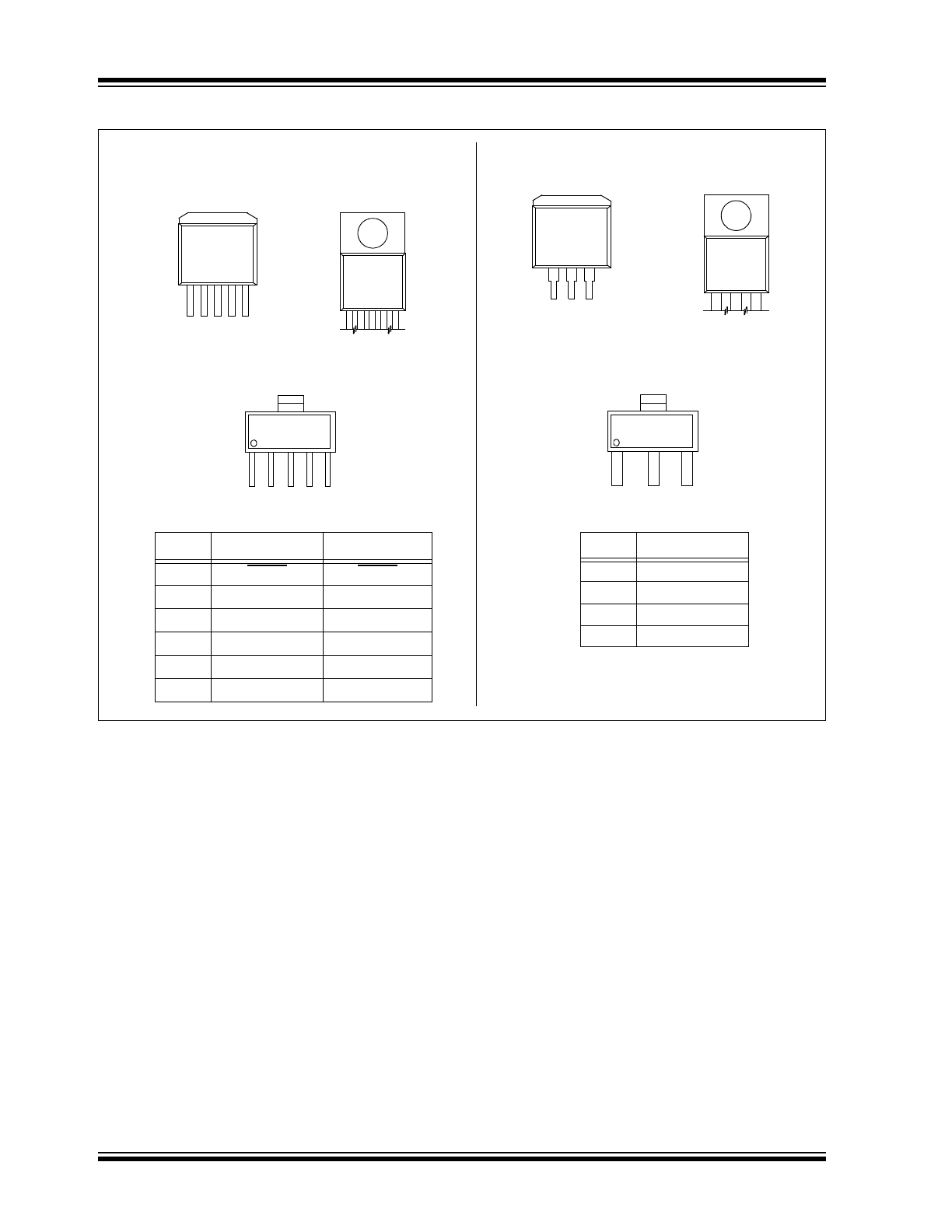

Typical Applications

MCP1825 Adjustable Output Voltage

MCP1825 Fixed Output Voltage

V

OUT

= 1.8V @ 500 mA

V

IN

= 2.3V to 2.8V

On

Off

1 µF

100 k

Ω

4.7 µF

C

1

C

2

R

1

SHDN

V

IN

GND

V

OUT

PWRGD

20 k

Ω

R

2

V

OUT

= 1.2V @ 500 mA

V

IN

= 2.1V to 2.8V

On

Off

1 µF

40 k

Ω

4.7 µF

C

1

C

2

R

1

SHDN

V

IN

GND

V

OUT

V

ADJ

1

1

MCP1825/MCP1825S

DS22056B-page 4

© 2008 Microchip Technology Inc.

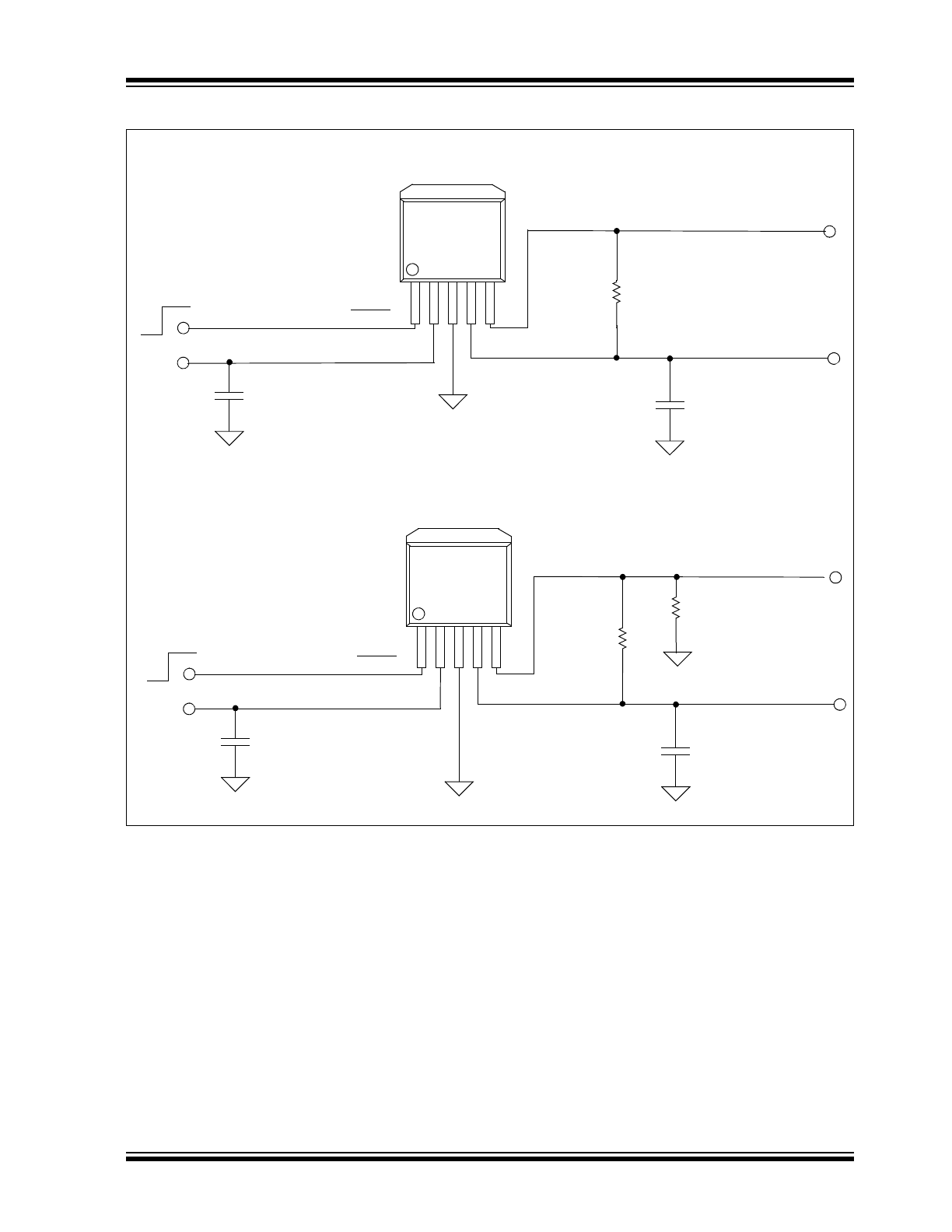

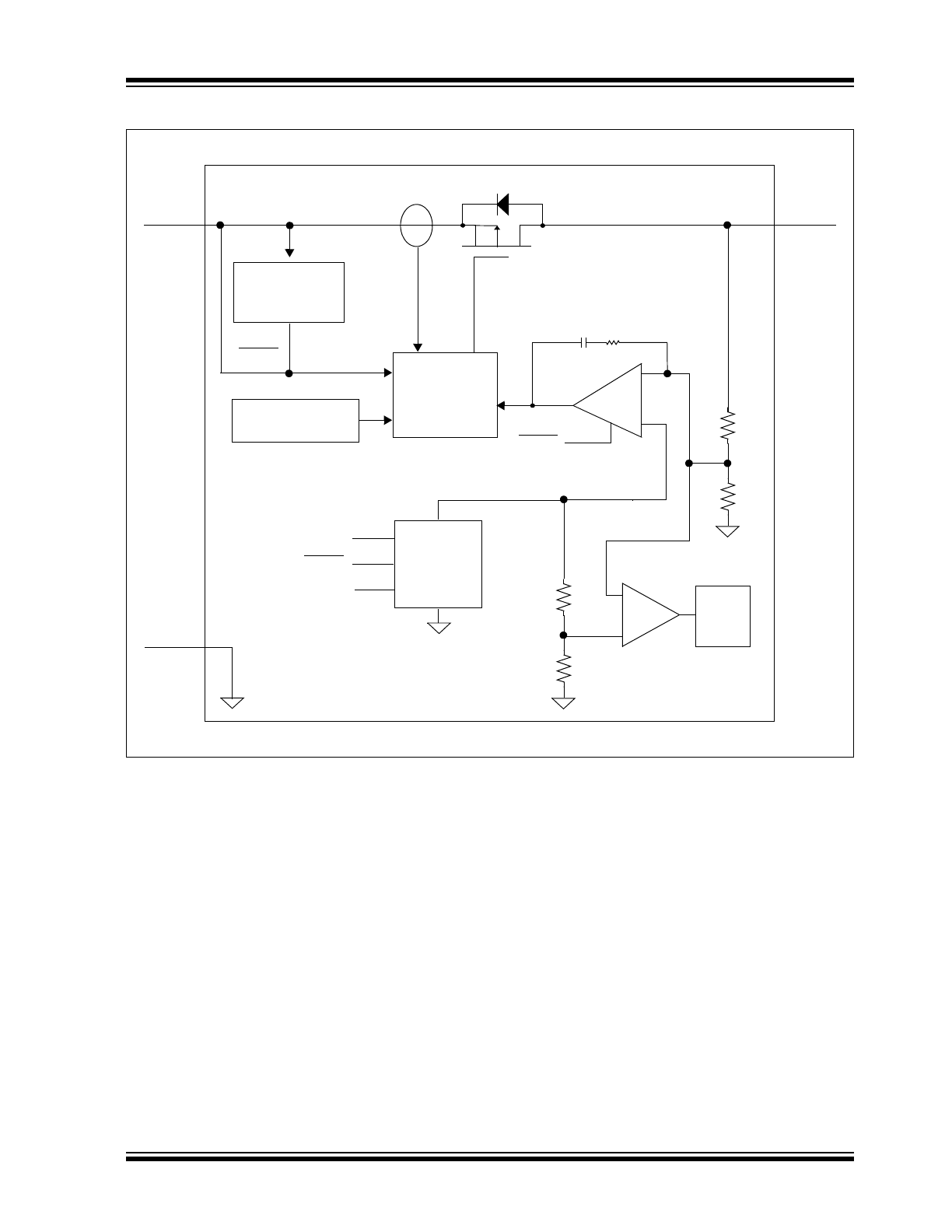

Functional Block Diagram - Adjustable Output

EA

+

–

V

OUT

PMOS

R

f

C

f

I

SNS

Overtemperature

V

REF

Comp

92% of V

REF

T

DELAY

V

IN

Driver w/limit

and SHDN

GND

Soft-Start

ADJ/SENSE

Undervoltage

Lock Out

VIN

Reference

SHDN

SHDN

SHDN

Sensing

(UVLO)

© 2008 Microchip Technology Inc.

DS22056B-page 5

MCP1825/MCP1825S

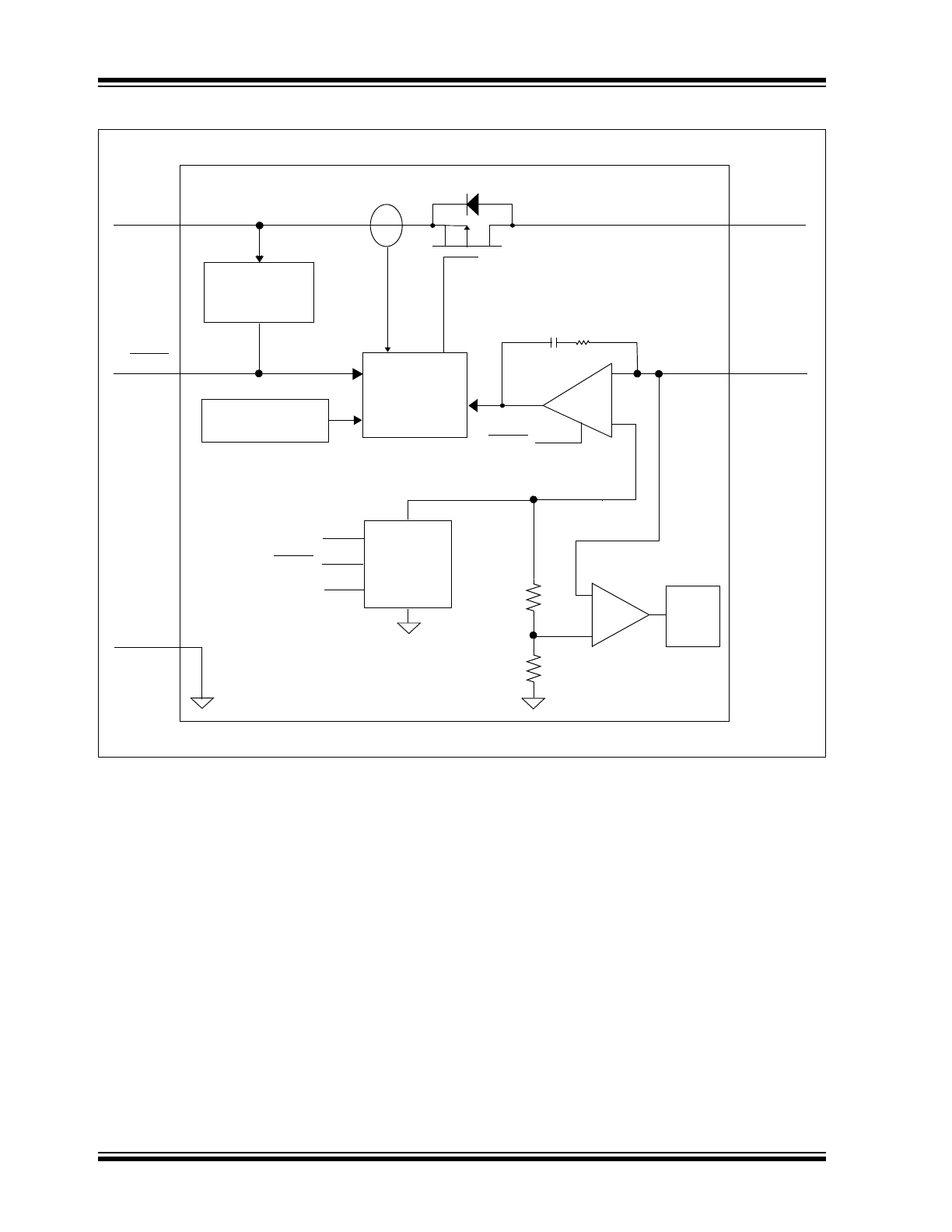

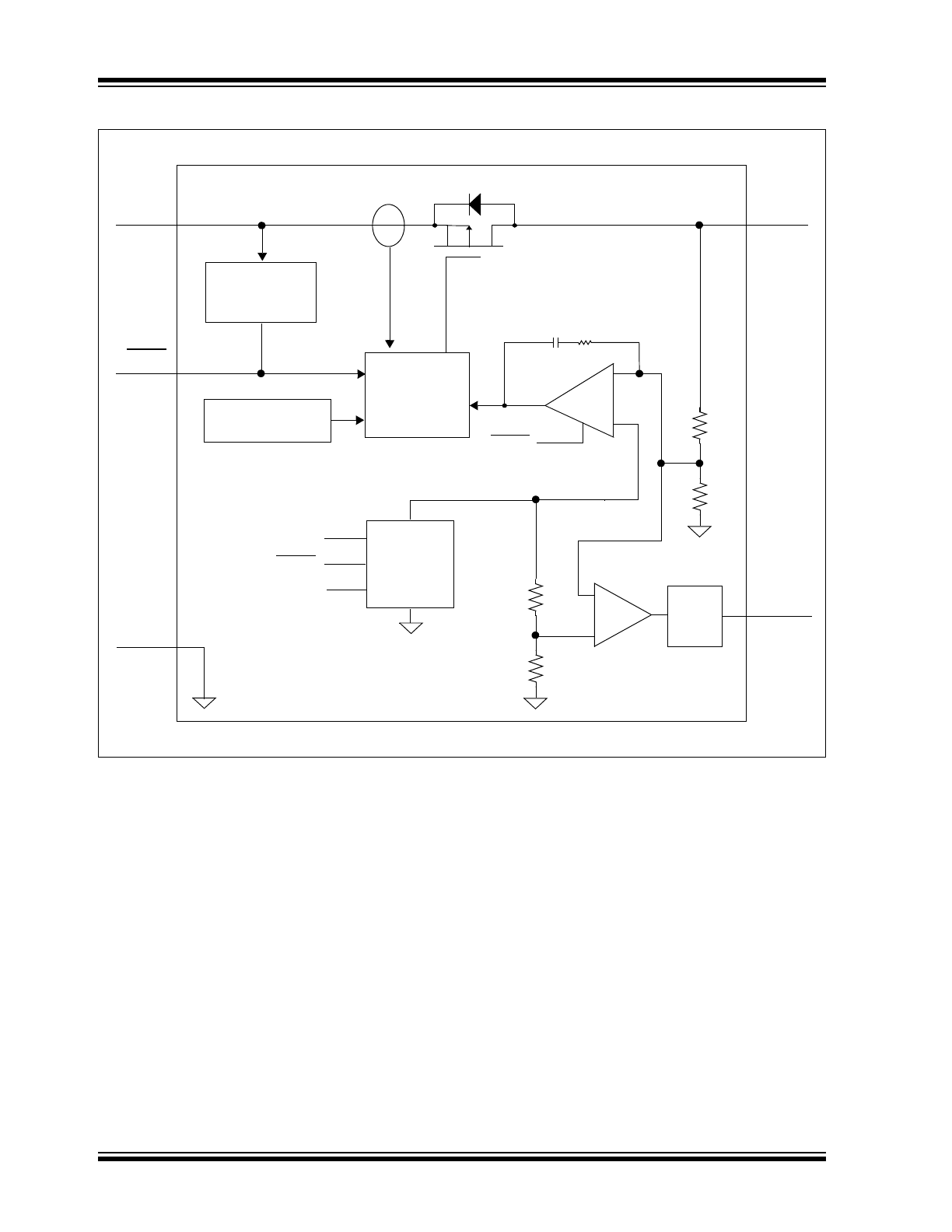

Functional Block Diagram - Fixed Output (3-Pin)

EA

+

–

V

OUT

PMOS

R

f

C

f

I

SNS

Overtemperature

V

REF

Comp

92% of V

REF

T

DELAY

V

IN

Driver w/limit

and SHDN

GND

Soft-Start

Sense

Undervoltage

Lock Out

VIN

Reference

SHDN

SHDN

SHDN

Sensing

(UVLO)

MCP1825/MCP1825S

DS22056B-page 6

© 2008 Microchip Technology Inc.

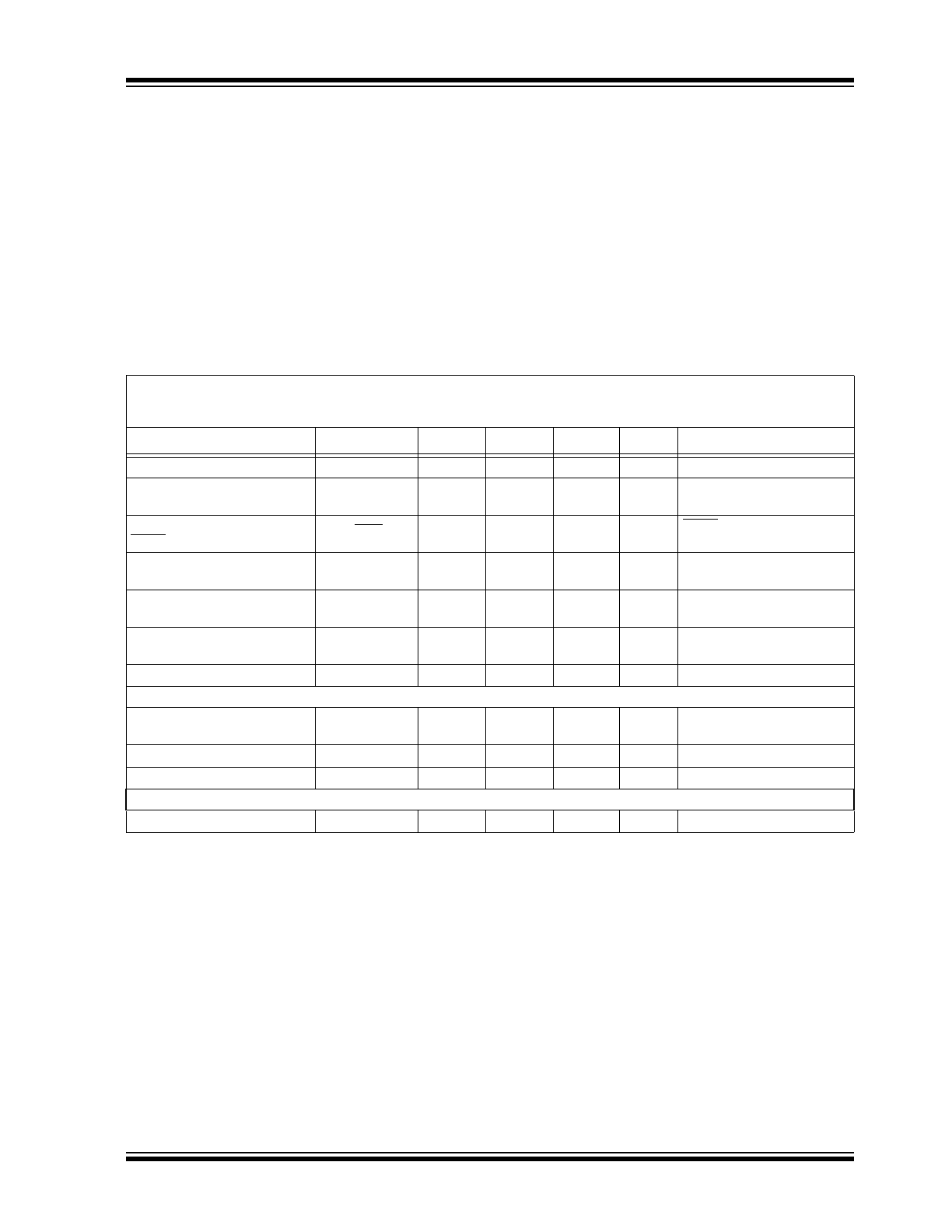

Functional Block Diagram - Fixed Output (5-Pin)

EA

+

–

V

OUT

PMOS

R

f

C

f

I

SNS

Overtemperature

V

REF

Comp

92% of V

REF

T

DELAY

V

IN

Driver w/limit

and SHDN

GND

Soft-Start

Sense

Undervoltage

Lock Out

VIN

Reference

SHDN

SHDN

SHDN

Sensing

(UVLO)

PWRGD

© 2008 Microchip Technology Inc.

DS22056B-page 7

MCP1825/MCP1825S

1.0

ELECTRICAL

CHARACTERISTICS

Absolute Maximum Ratings †

V

IN

....................................................................................6.5V

Maximum Voltage on Any Pin .. (GND – 0.3V) to (V

DD

+ 0.3)V

Maximum Power Dissipation......... Internally-Limited (

Note 6)

Output Short Circuit Duration ................................ Continuous

Storage temperature .....................................-65°C to +150°C

Maximum Junction Temperature, T

J

........................... +150°C

ESD protection on all pins (HBM/MM)

........... ≥

4 kV;

≥

300V

† Notice: Stresses above those listed under “Maximum Rat-

ings” may cause permanent damage to the device. This is a

stress rating only and functional operation of the device at

those or any other conditions above those indicated in the

operational listings of this specification is not implied. Expo-

sure to maximum rating conditions for extended periods may

affect device reliability.

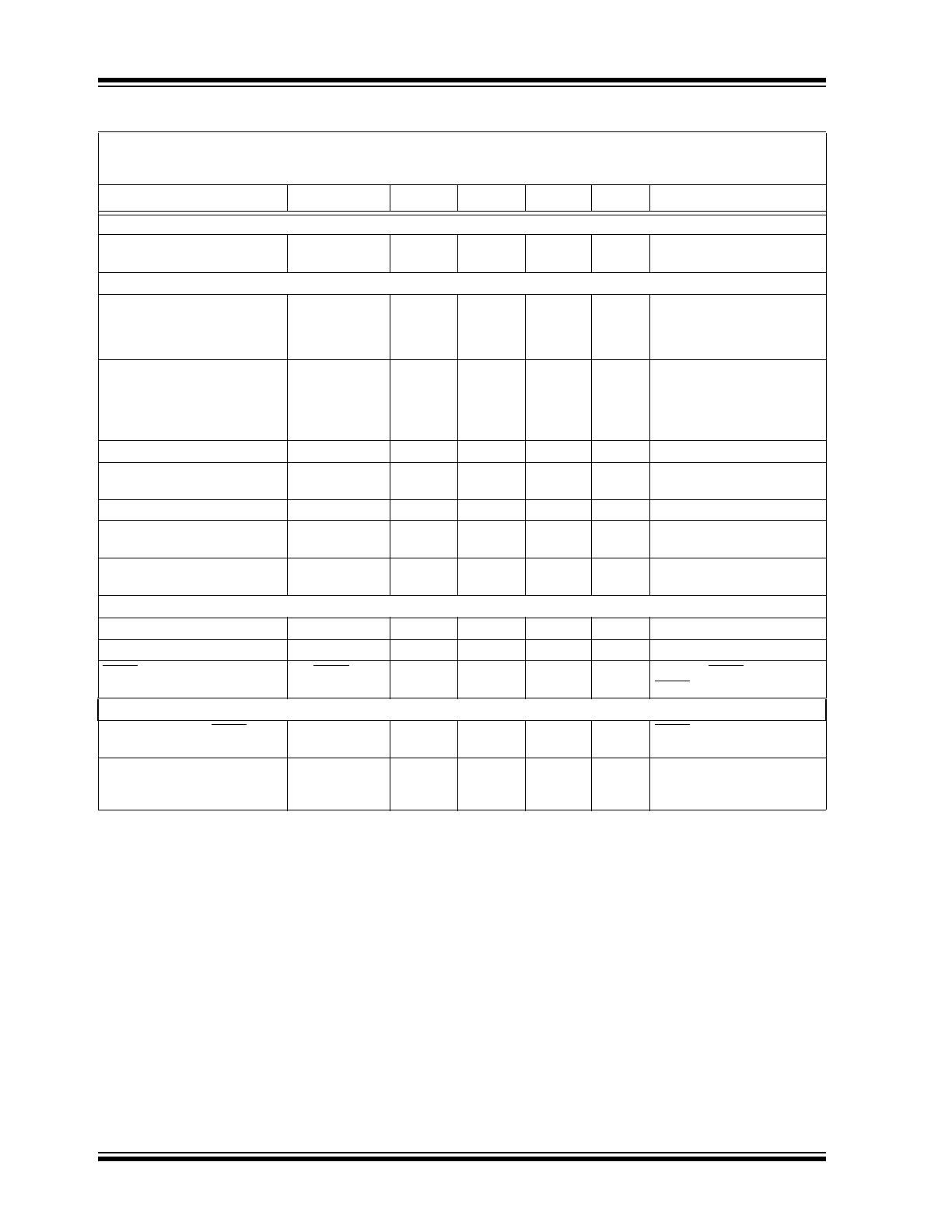

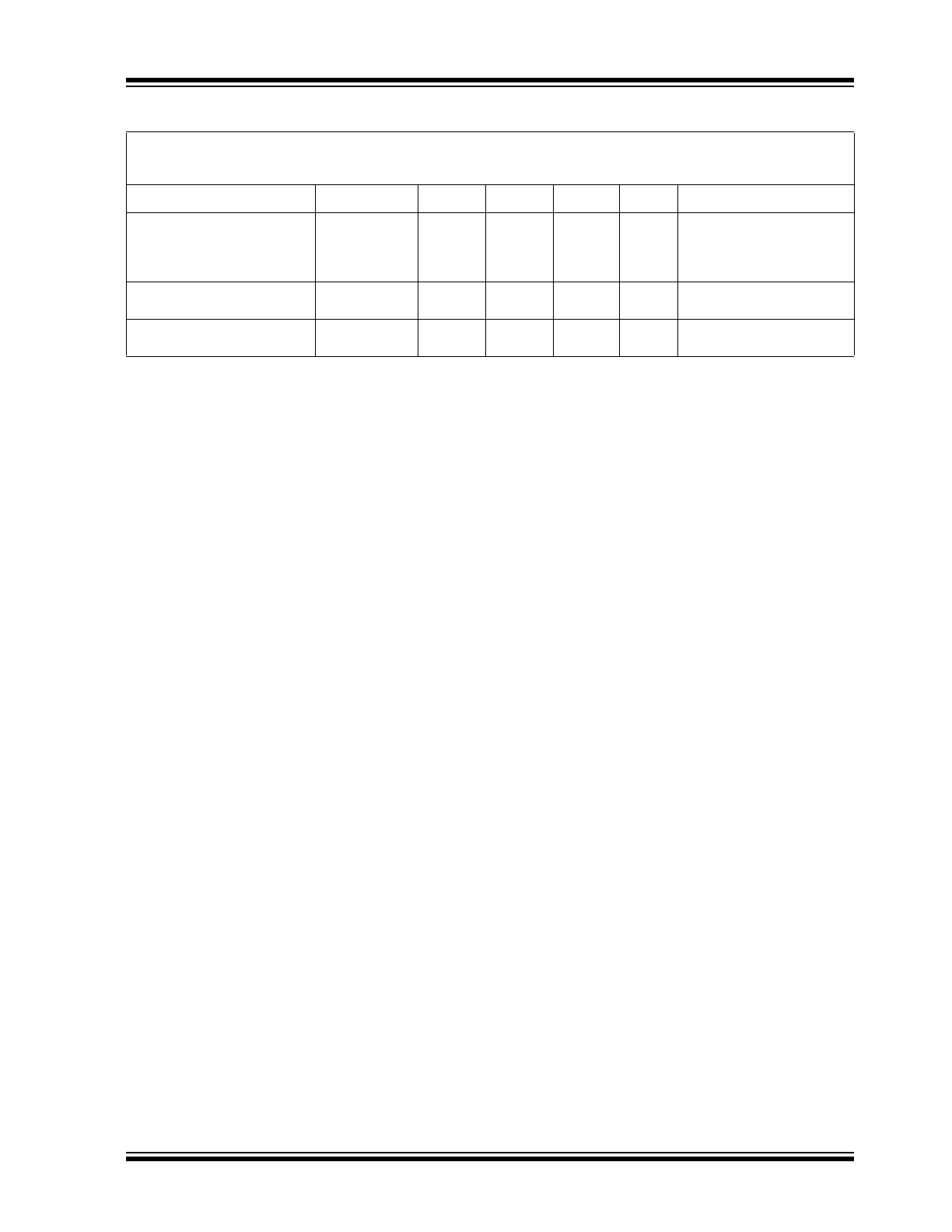

AC/DC CHARACTERISTICS

Electrical Specifications: Unless otherwise noted, V

IN

= V

OUT(MAX)

+ V

DROPOUT(MAX)

,

Note 1, V

R

= 1.8V for Adjustable Output,

I

OUT

= 1 mA, C

IN

= C

OUT

= 4.7 µF (X7R Ceramic), T

A

= +25°C.

Boldface type applies for junction temperatures, T

J

(

Note 7) of -40°C to +125°C

Parameters

Sym

Min

Typ

Max

Units

Conditions

Input Operating Voltage

V

IN

2.1

6.0

V

Note 1

Input Quiescent Current

I

q

—

120

220

µA

I

L

= 0 mA, V

OUT

= 0.8V to

5.0V

Input Quiescent Current for

SHDN Mode

I

SHDN

—

0.1

3

µA

SHDN = GND

Maximum Output Current

I

OUT

500

—

—

mA

V

IN

= 2.1V to 6.0V

V

R

= 0.8V to 5.0V,

Note 1

Line Regulation

ΔV

OUT

/

(V

OUT

x

ΔV

IN

)

—

±0.05

±0.

16

%/V

(Note 1)

≤ V

IN

≤ 6V

Load Regulation

ΔV

OUT

/V

OUT

-1.0

±0.5

1.0

%

I

OUT

= 1 mA to 500 mA,

(

Note 4)

Output Short Circuit Current

I

OUT_SC

—

1.2

—

A

R

LOAD

< 0.1

Ω, Peak Current

Adjust Pin Characteristics (Adjustable Output Only)

Adjust Pin Reference Voltage

V

ADJ

0.402

0.410

0.418

V

V

IN

= 2.1V to V

IN

= 6.0V,

I

OUT

= 1 mA

Adjust Pin Leakage Current

I

ADJ

-10

±0.01

+10

nA

V

IN

= 6.0V, V

ADJ

= 0V to 6V

Adjust Temperature Coefficient

TCV

OUT

—

40

—

ppm/°C

Note 3

Fixed-Output Characteristics (Fixed Output Only)

Voltage Regulation

V

OUT

V

R

- 2.5% V

R

±0.5%

V

R

+ 2.5%

V

Note 2

Note 1:

The minimum V

IN

must meet two conditions: V

IN

≥ 2.1V and V

IN

≥ V

OUT(MAX)

+ V

DROPOUT(MAX).

2:

V

R

is the nominal regulator output voltage for the fixed cases. V

R

= 1.2V, 1.8V, etc. V

R

is the desired set point output

voltage for the adjustable cases. V

R

= V

ADJ

*

((R

1

/R

2

)+1).

Figure 4-1

.

3:

TCV

OUT

= (V

OUT-HIGH

– V

OUT-LOW

) *10

6

/ (V

R

*

ΔTemperature). V

OUT-HIGH

is the highest voltage measured over the

temperature range. V

OUT-LOW

is the lowest voltage measured over the temperature range.

4:

Load regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is

tested over a load range from 1 mA to the maximum specified output current.

5:

Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its

nominal value that was measured with an input voltage of V

IN

= V

OUT(MAX)

+ V

DROPOUT(MAX)

.

6:

The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction

temperature and the thermal resistance from junction to air. (i.e., T

A

, T

J

,

θ

JA

). Exceeding the maximum allowable power

dissipation will cause the device operating junction temperature to exceed the maximum +150°C rating. Sustained

junction temperatures above 150°C can impact device reliability.

7:

The junction temperature is approximated by soaking the device under test at an ambient temperature equal to the

desired junction temperature. The test time is small enough such that the rise in the junction temperature over the

ambient temperature is not significant.

MCP1825/MCP1825S

DS22056B-page 8

© 2008 Microchip Technology Inc.

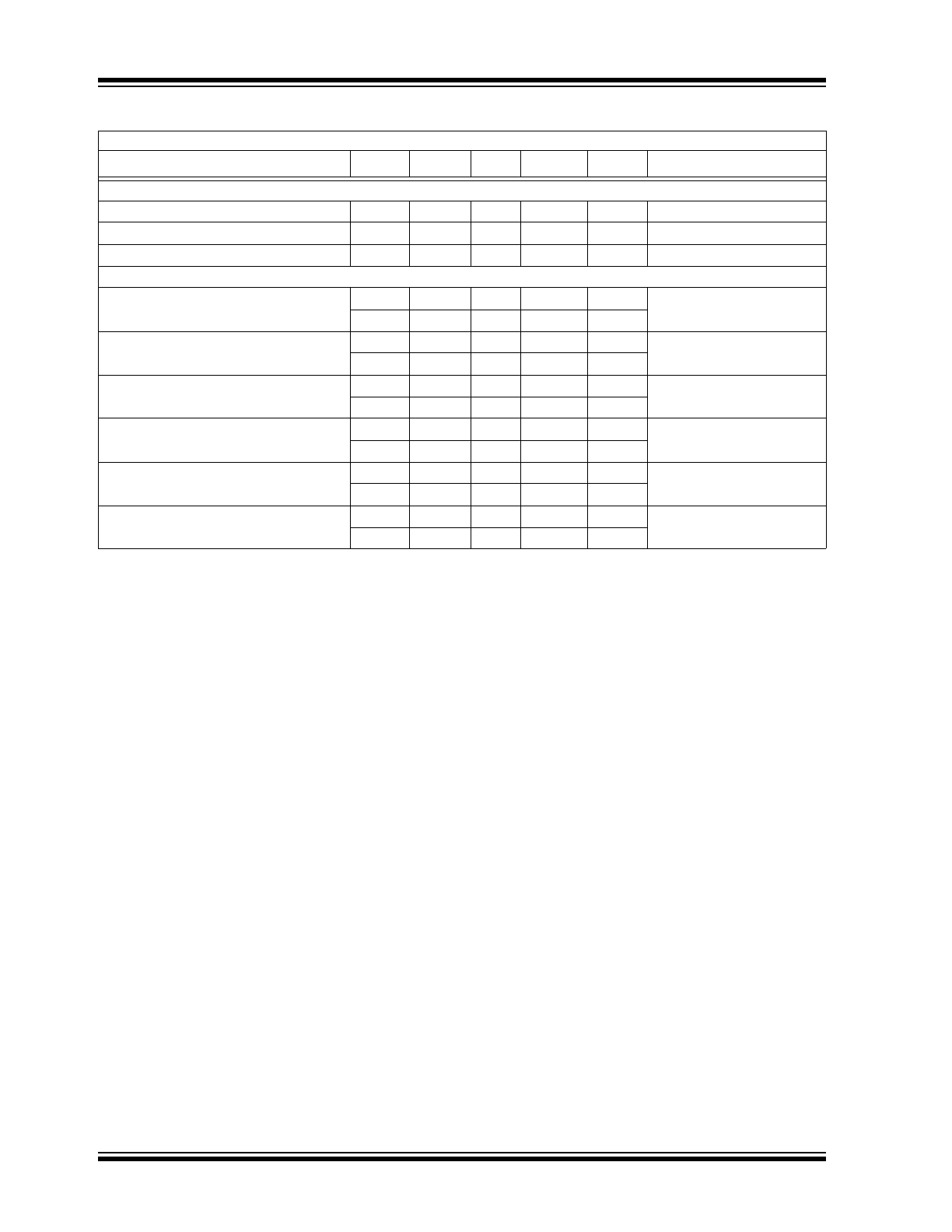

Dropout Characteristics

Dropout Voltage

V

DROPOUT

—

210

350

mV

Note 5, I

OUT

= 500 mA,

V

IN(MIN)

= 2.1V

Power Good Characteristics

PWRGD Input Voltage Operat-

ing Range

V

PWRGD_VIN

1.0

—

6.0

V

T

A

= +25°C

1.2

—

6.0

T

A

= -40°C to +125°C

For V

IN

< 2.1V, I

SINK

= 100 µA

PWRGD Threshold Voltage

(Referenced to V

OUT

)

V

PWRGD_TH

%V

OUT

Falling Edge

89

92

95

V

OUT

< 2.5V Fixed,

V

OUT

= Adj.

90

92

94

V

OUT

>= 2.5V Fixed

PWRGD Threshold Hysteresis

V

PWRGD_HYS

1.0

2.0

3.0

%V

OUT

PWRGD Output Voltage Low

V

PWRGD_L

—

0.2

0.4

V

I

PWRGD

SINK

= 1.2 mA,

ADJ = 0V

PWRGD Leakage

P

WRGD

_

LK

—

1

—

nA

V

PWRGD

= V

IN

= 6.0V

PWRGD Time Delay

T

PG

—

110

—

µs

Rising Edge

R

PULLUP

= 10 k

Ω

Detect Threshold to PWRGD

Active Time Delay

T

VDET-PWRGD

—

200

—

µs

V

OUT

= V

PWRGD_TH

+ 20 mV

to V

PWRGD_TH

- 20 mV

Shutdown Input

Logic High Input

V

SHDN-HIGH

45

—

—

%V

IN

V

IN

= 2.1V to 6.0V

Logic Low Input

V

SHDN-LOW

—

—

15

%V

IN

V

IN

= 2.1V to 6.0V

SHDN Input Leakage Current

SHDN

ILK

-0.1

±0.001

+0.1

µA

V

IN

= 6V, SHDN =V

IN

,

SHDN = GND

AC Performance

Output Delay From SHDN

T

OR

—

100

—

µs

SHDN = GND to V

IN

,

V

OUT

= GND to 95% V

R

Output Noise

e

N

—

2.0

—

µV/

√Hz I

OUT

= 200 mA, f = 1 kHz,

C

OUT

= 10 µF (X7R Ceramic),

V

OUT

= 2.5V

AC/DC CHARACTERISTICS (CONTINUED)

Electrical Specifications: Unless otherwise noted, V

IN

= V

OUT(MAX)

+ V

DROPOUT(MAX)

,

Note 1, V

R

= 1.8V for Adjustable Output,

I

OUT

= 1 mA, C

IN

= C

OUT

= 4.7 µF (X7R Ceramic), T

A

= +25°C.

Boldface type applies for junction temperatures, T

J

(

Note 7) of -40°C to +125°C

Parameters

Sym

Min

Typ

Max

Units

Conditions

Note 1:

The minimum V

IN

must meet two conditions: V

IN

≥ 2.1V and V

IN

≥ V

OUT(MAX)

+ V

DROPOUT(MAX).

2:

V

R

is the nominal regulator output voltage for the fixed cases. V

R

= 1.2V, 1.8V, etc. V

R

is the desired set point output

voltage for the adjustable cases. V

R

= V

ADJ

*

((R

1

/R

2

)+1).

Figure 4-1

.

3:

TCV

OUT

= (V

OUT-HIGH

– V

OUT-LOW

) *10

6

/ (V

R

*

ΔTemperature). V

OUT-HIGH

is the highest voltage measured over the

temperature range. V

OUT-LOW

is the lowest voltage measured over the temperature range.

4:

Load regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is

tested over a load range from 1 mA to the maximum specified output current.

5:

Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its

nominal value that was measured with an input voltage of V

IN

= V

OUT(MAX)

+ V

DROPOUT(MAX)

.

6:

The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction

temperature and the thermal resistance from junction to air. (i.e., T

A

, T

J

,

θ

JA

). Exceeding the maximum allowable power

dissipation will cause the device operating junction temperature to exceed the maximum +150°C rating. Sustained

junction temperatures above 150°C can impact device reliability.

7:

The junction temperature is approximated by soaking the device under test at an ambient temperature equal to the

desired junction temperature. The test time is small enough such that the rise in the junction temperature over the

ambient temperature is not significant.

© 2008 Microchip Technology Inc.

DS22056B-page 9

MCP1825/MCP1825S

Power Supply Ripple Rejection

Ratio

PSRR

—

60

—

dB

f = 100 Hz, C

OUT

= 4.7 µF,

I

OUT

= 100 µA,

V

INAC

= 100 mV pk-pk,

C

IN

= 0 µF

Thermal Shutdown Temperature

T

SD

—

150

—

°C

I

OUT

= 100 µA, V

OUT

= 1.8V,

V

IN

= 2.8V

Thermal Shutdown Hysteresis

ΔT

SD

—

10

—

°C

I

OUT

= 100 µA, V

OUT

= 1.8V,

V

IN

= 2.8V

AC/DC CHARACTERISTICS (CONTINUED)

Electrical Specifications: Unless otherwise noted, V

IN

= V

OUT(MAX)

+ V

DROPOUT(MAX)

,

Note 1, V

R

= 1.8V for Adjustable Output,

I

OUT

= 1 mA, C

IN

= C

OUT

= 4.7 µF (X7R Ceramic), T

A

= +25°C.

Boldface type applies for junction temperatures, T

J

(

Note 7) of -40°C to +125°C

Parameters

Sym

Min

Typ

Max

Units

Conditions

Note 1:

The minimum V

IN

must meet two conditions: V

IN

≥ 2.1V and V

IN

≥ V

OUT(MAX)

+ V

DROPOUT(MAX).

2:

V

R

is the nominal regulator output voltage for the fixed cases. V

R

= 1.2V, 1.8V, etc. V

R

is the desired set point output

voltage for the adjustable cases. V

R

= V

ADJ

*

((R

1

/R

2

)+1).

Figure 4-1

.

3:

TCV

OUT

= (V

OUT-HIGH

– V

OUT-LOW

) *10

6

/ (V

R

*

ΔTemperature). V

OUT-HIGH

is the highest voltage measured over the

temperature range. V

OUT-LOW

is the lowest voltage measured over the temperature range.

4:

Load regulation is measured at a constant junction temperature using low duty-cycle pulse testing. Load regulation is

tested over a load range from 1 mA to the maximum specified output current.

5:

Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its

nominal value that was measured with an input voltage of V

IN

= V

OUT(MAX)

+ V

DROPOUT(MAX)

.

6:

The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction

temperature and the thermal resistance from junction to air. (i.e., T

A

, T

J

,

θ

JA

). Exceeding the maximum allowable power

dissipation will cause the device operating junction temperature to exceed the maximum +150°C rating. Sustained

junction temperatures above 150°C can impact device reliability.

7:

The junction temperature is approximated by soaking the device under test at an ambient temperature equal to the

desired junction temperature. The test time is small enough such that the rise in the junction temperature over the

ambient temperature is not significant.

MCP1825/MCP1825S

DS22056B-page 10

© 2008 Microchip Technology Inc.

TEMPERATURE SPECIFICATIONS

Parameters

Sym

Min

Typ

Max

Units

Conditions

Temperature Ranges

Operating Junction Temperature Range

T

J

-40

—

+125

°C

Steady State

Maximum Junction Temperature

T

J

—

—

+150

°C

Transient

Storage Temperature Range

T

A

-65

—

+150

°C

Thermal Package Resistances

Thermal Resistance, 3LD DDPAK

θ

JA

—

31.4

—

°C/W

4-Layer JC51 Standard

Board

θ

JC

—

3.0

—

Thermal Resistance, 3LD TO-220

θ

JA

—

29.4

—

°C/W

4-Layer JC51 Standard

Board

θ

JC

—

2.0

—

Thermal Resistance, 3LD SOT-223

θ

JA

—

62

—

°C/W

EIA/JEDEC JESD51-751-7

4 Layer Board

θ

JC

—

15.0

—

Thermal Resistance, 5LD DDPAK

θ

JA

—

31.2

—

°C/W

4-Layer JC51 Standard

Board

θ

JC

—

3.0

—

Thermal Resistance, 5LD TO-220

θ

JA

—

29.3

—

°C/W

4-Layer JC51 Standard

Board

θ

JC

—

2.0

—

Thermal Resistance, 5LD SOT-223

θ

JA

—

62

—

°C/W

EIA/JEDEC JESD51-751-7

4 Layer Board

θ

JC

—

15.0

—