A Microchip Technology Company

©2011 Silicon Storage Technology, Inc.

DS25085A

10/11

Data Sheet

www.microchip.com

Features

• Firmware Hub for Intel 8xx Chipsets

• 8 Mbit SuperFlash memory array for code/data

storage

– 1024K x8

• Flexible Erase Capability

– Uniform 4 KByte Sectors

– Uniform 64 KByte overlay blocks

– 64 KByte Top Boot Block protection

– Chip-Erase for PP Mode Only

• Single 3.0-3.6V Read and Write Operations

• Superior Reliability

– Endurance:100,000 Cycles (typical)

– Greater than 100 years Data Retention

• Low Power Consumption

– Active Read Current: 6 mA (typical)

– Standby Current: 10 µA (typical)

• Fast Sector-Erase/Byte-Program Operation

– Sector-Erase Time: 18 ms (typical)

– Block-Erase Time: 18 ms (typical)

– Chip-Erase Time: 70 ms (typical)

– Byte-Program Time: 14 µs (typical)

– Chip Rewrite Time: 15 seconds (typical)

– Single-pulse Program or Erase

– Internal timing generation

• Two Operational Modes

– Firmware Hub Interface (FWH) Mode for

In-System operation

– Parallel Programming (PP) Mode for fast

production programming

• Firmware Hub Hardware Interface Mode

– 5-signal communication interface supporting byte Read

and Write

– 33 MHz clock frequency operation

– WP# and TBL# pins provide hardware write

protect for entire chip and/or top Boot Block

– Block Locking Register for all blocks

– Standard SDP Command Set

– Data# Polling and Toggle Bit for End-of-Writedetection

– 5 GPI pins for system design flexibility

– 4 ID pins for multi-chip selection

• Parallel Programming (PP) Mode

– 11-pin multiplexed address and

8-pin data I/O interface

– Supports fast In-System or PROM programming for

manufacturing

• CMOS and PCI I/O Compatibility

• Packages Available

– 32-lead PLCC

– 32-lead TSOP (8mm x 14mm)

– 40-lead TSOP (10mm x 20mm)

– Non-Pb (lead-free) packages available

• All non-Pb (lead-free) devices are RoHS compliant

8 Mbit Firmware Hub

SST49LF008A

The SST49LF008A flash memory devices are designed to be read-compatible

with the Intel® 82802 Firmware Hub (FWH) device for PC-BIOS application.

These devices provide protection for the storage and update of code and data in

addition to adding system design flexibility through five general purpose inputs.

Two interface modes are supported by the SST49LF008A: Firmware Hub (FWH)

Interface mode for in-system programming and Parallel Programming (PP) mode

for fast factory programming of PC-BIOS applications.

©2011 Silicon Storage Technology, Inc.

DS25085A

10/11

2

8 Mbit Firmware Hub

SST49LF008A

Data Sheet

A Microchip Technology Company

Product Description

The SST49LF008A flash memory devices are designed to be read-compatible with the Intel® 82802

Firmware Hub (FWH) device for PC-BIOS application. These devices provide protection for the storage

and update of code and data in addition to adding system design flexibility through five general pur-

pose inputs. Two interface modes are supported by the SST49LF008A: Firmware Hub (FWH) Interface

mode for in-system programming and Parallel Programming (PP) mode for fast factory programming of

PC-BIOS applications.

The SST49LF008A flash memory devices are manufactured with SST’s proprietary, high performance

SuperFlash technology. The split-gate cell design and thick-oxide tunneling injector attain better reli-

ability and manufacturability compared with alternate approaches. The SST49LF008A devices signifi-

cantly improve performance and reliability, while lowering power consumption.

The SST49LF008A devices write (Program or Erase) with a single 3.0-3.6V power supply. They use

less energy during Erase and Program than alternative flash memory technologies. The total energy

consumed is a function of the applied voltage, current and time of application. Since for any given volt-

age range, the SuperFlash technology uses less current to program and has a shorter Erase time, the

total energy consumed during any Erase or Program operation is less than alternative flash memory

technologies. The SST49LF008A products provide a maximum Byte-Program time of 20 µsec. The

entire memory can be erased and programmed byte-by-byte typically in 15 seconds when using status

detection features such as Toggle Bit or Data# Polling to indicate the completion of Program operation.

The SuperFlash technology provides fixed Erase and Program times independent of the number of

Erase/Program cycles performed. Therefore the system software or hardware does not have to be cal-

ibrated or correlated to the cumulated number of Erase/Program cycles as is necessary with alterna-

tive flash memory technologies, whose Erase and Program time increase with accumulated Erase/

Program cycles.

To protect against inadvertent write, the SST49LF008A devices employ hardware and software data

(SDP) protection schemes. It is offered with typical endurance of 100,000 cycles. Data retention is

rated at greater than 100 years.

To meet high density, surface mount requirements, the SST49LF008A devices are offered in a 32-lead

TSOP package. In addition, the SST49LF008A is offered in 32-lead PLCC and 40-lead TSOP pack-

ages. See Figures 2, 3, and 4 for pin assignments and Table 1 for pin descriptions.

©2011 Silicon Storage Technology, Inc.

DS25085A

10/11

3

8 Mbit Firmware Hub

SST49LF008A

Data Sheet

A Microchip Technology Company

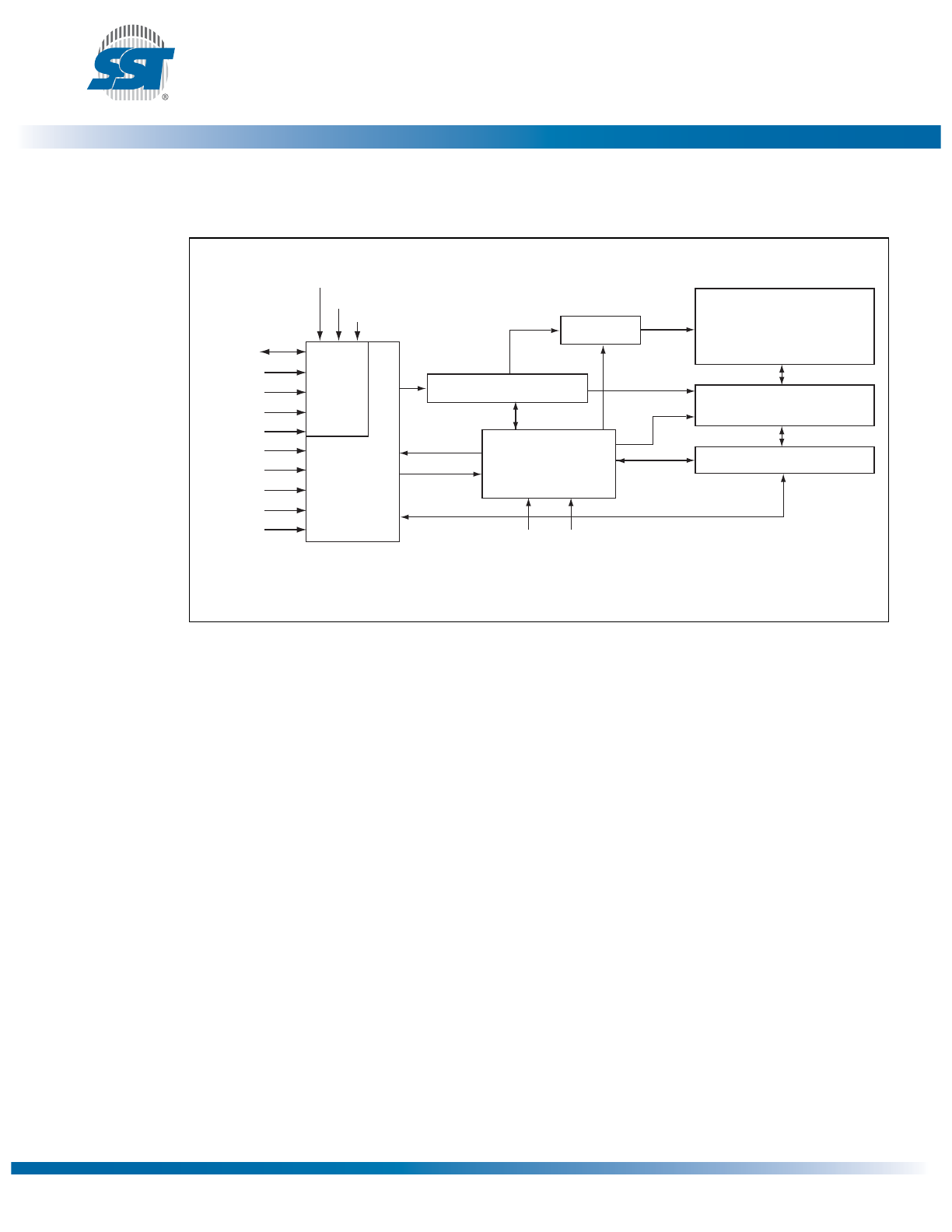

Functional Block Diagram

Figure 1: Functional Block Diagram

1161 B1.2

Y-Decoder

I/O Buffers and Data Latches

Address Buffers Latches

X-Decoder

SuperFlash

Memory

Control Logic

CLK

RST#

IC

FGPI[4:0]

Programmer

Interface

WP#

TBL#

INIT#

ID[3:0]

FWH4

R/C#

OE#

WE#

A[10:0]

DQ[7:0]

FWH[3:0]

FWH

Interface

©2011 Silicon Storage Technology, Inc.

DS25085A

10/11

4

8 Mbit Firmware Hub

SST49LF008A

Data Sheet

A Microchip Technology Company

Pin Assignments

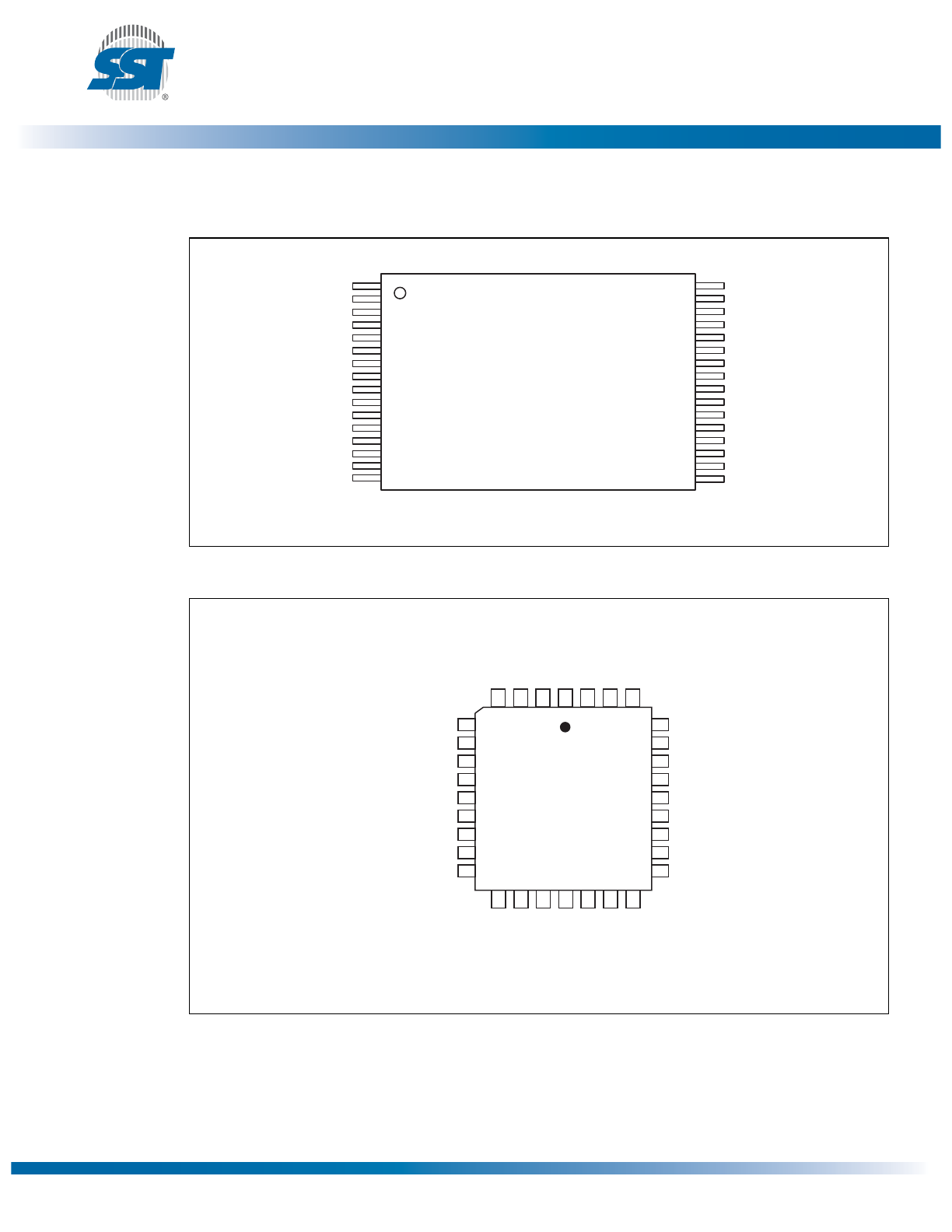

Figure 2: Pin Assignments for 32-lead TSOP (8mm x 14mm)

Figure 3: Pin Assignments for 32-lead PLCC

NC

NC

NC

VSS (VSS)

IC (IC)

A10 (FGPI4)

R/C# (CLK)

VDD (VDD)

NC

RST# (RST#)

A9 (FGPI3)

A8 (FGPI2)

A7 (FGPI1)

A6 (FGPI0)

A5 (WP#)

A4 (TBL#)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

OE# (INIT#)

WE# (FWH4)

VDD (VDD)

DQ7 (RES)

DQ6 (RES)

DQ5 (RES)

DQ4 (RES)

DQ3 (FWH3)

VSS (VSS)

DQ2 (FWH2)

DQ1 (FWH1)

DQ0 (FWH0)

A0 (ID0)

A1 (ID1)

A2 (ID2)

A3 (ID3)

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

1161 32-tsop P1.0

Standard Pinout

Top View

Die Up

( ) Designates FWH Mode

5

6

7

8

9

10

11

12

13

29

28

27

26

25

24

23

22

21

A7(FGPI1)

A6 (FGPI0)

A5 (WP#)

A4 (TBL#)

A3 (ID3)

A2 (ID2)

A1 (ID1)

A0 (ID0)

DQ0 (FWH0)

IC (IC)

VSS (VSS)

NC

NC

VDD (VDD)

OE# (INIT#)

WE# (FWH4)

NC

DQ7 (RES)

4

3

2

1

32

31 30

A8

(FGPI2)

A9

(FGPI3)

RST#

(RST#)

NC

V

DD

(V

DD

)

R/C#

(CLK)

A10

(FGPI4)

32-lead PLCC

Top View

1161 32-plcc P2.3

14

15

16

17 18

19

20

DQ1

(FWH1)

DQ2

(FWH2)

V

SS

(V

SS

)

DQ3

(FWH3)

DQ4

(RES)

DQ5

(RES)

DQ6

(RES)

( ) Designates FWH Mode

©2011 Silicon Storage Technology, Inc.

DS25085A

10/11

5

8 Mbit Firmware Hub

SST49LF008A

Data Sheet

A Microchip Technology Company

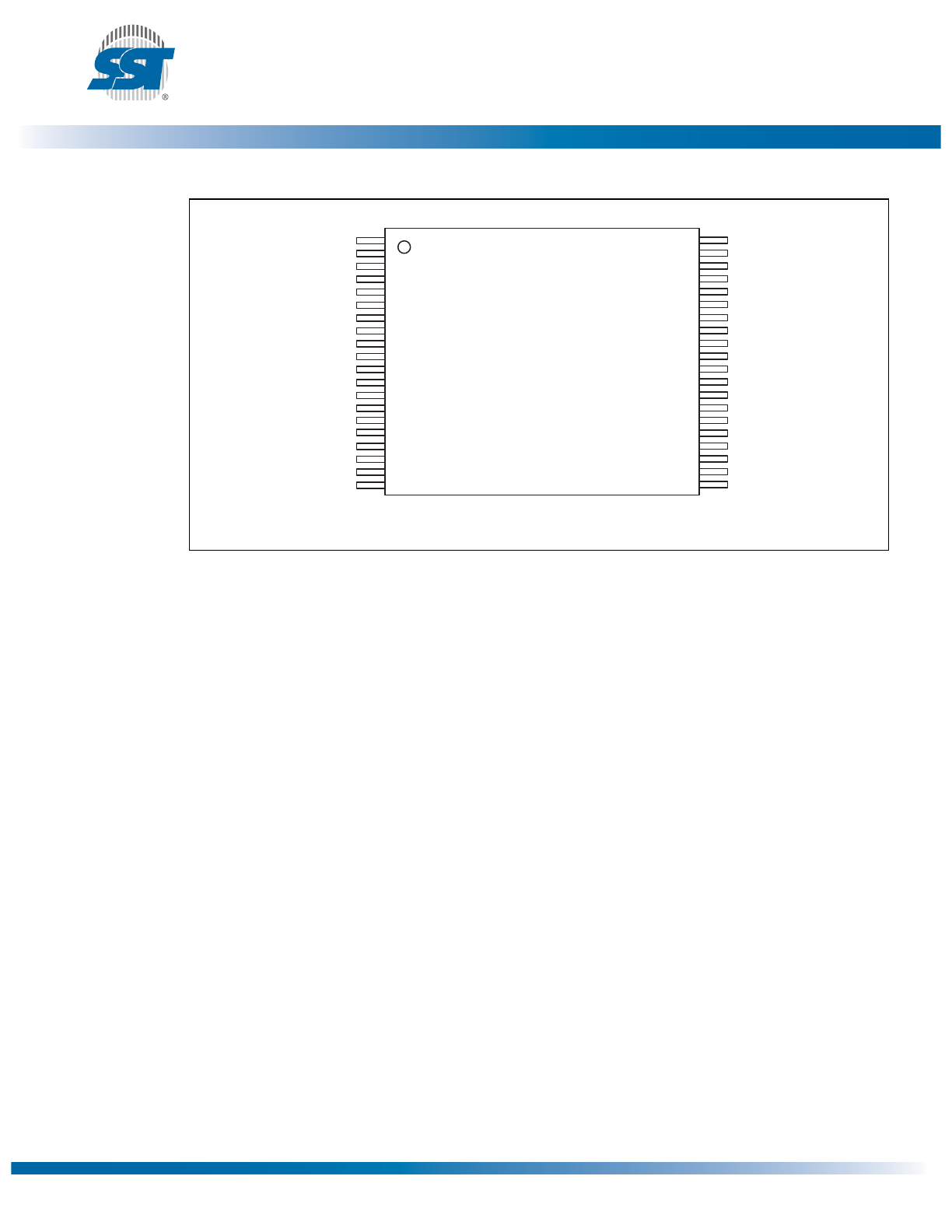

Figure 4: Pin Assignments for 40-lead TSOP

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

1232 40-tsop P1.0

Standard Pinout

Top View

Die Up

NC (NC)

IC (IC)

NC (NC)

NC (NC)

NC (NC)

NC (NC)

A10 (FGPI4)

NC (NC)

R/C# (CLK)

VDD

NC (NC)

RST# (RST#)

NC (NC)

NC (NC)

A9 (FGPI3)

A8 (FGPI2)

A7 (FGPI1)

A6 (FGPI0)

A5 (WP#)

A4 (TBL#)

VSS

VDD

(FWH4) WE#

(INIT#) OE#

(NC) NC

(RES) DQ7

(RES) DQ6

(RES) DQ5

(RES) DQ4

(NC) NC

VSS

VSS

(FWH3) DQ3

(FWH2) DQ2

(FWH1) DQ1

(FWH0) DQ0

(ID0) A0

(ID1) A1

(ID2) A2

(ID3) A3

( ) Designates FWH Mode

©2011 Silicon Storage Technology, Inc.

DS25085A

10/11

6

8 Mbit Firmware Hub

SST49LF008A

Data Sheet

A Microchip Technology Company

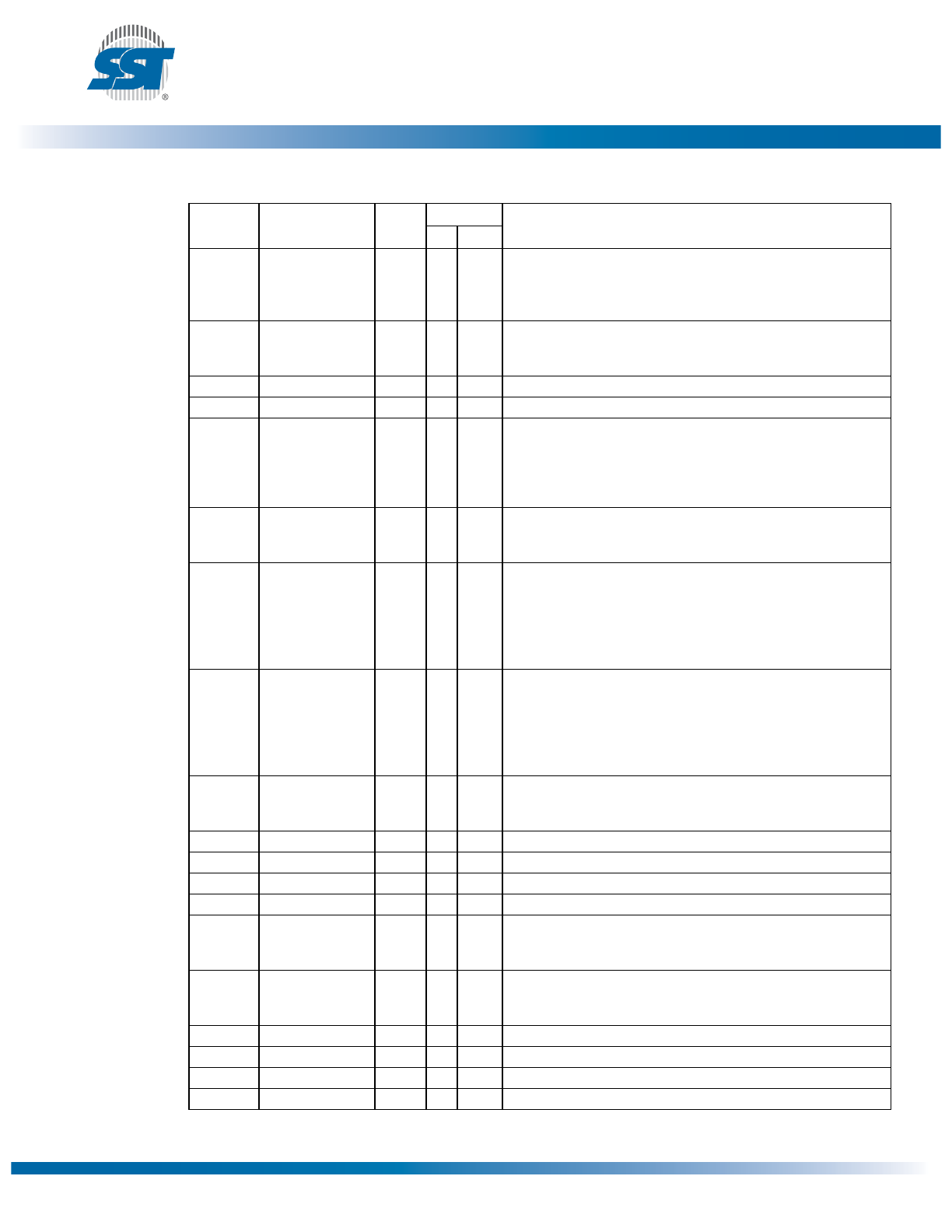

Table 1: Pin Description

Symbol

Pin Name

Type

1

Interface

Functions

PP FWH

A

10

-A

0

Address

I

X

Inputs for low-order addresses during Read and Write opera-

tions. Addresses are internally latched during a Write cycle. For

the programming interface, these addresses are latched by R/

C# and share the same pins as the high-order address inputs.

DQ

7

-DQ

0

Data

I/O

X

To output data during Read cycles and receive input data during

Write cycles. Data is internally latched during a Write cycle. The

outputs are in tri-state when OE# is high.

OE#

Output Enable

I

X

To gate the data output buffers

WE#

Write Enable

I

X

To control the Write operations

IC

Interface

Configuration

Pin

I

X

X

This pin determines which interface is operational. When held

high, programmer mode is enabled and when held low, FWH

mode is enabled. This pin must be setup at power-up or before

return from reset and not change during device operation. This pin

is internally pulled- down with a resistor between 20-100 K

INIT#

Initialize

I

X

This is the second reset pin for in-system use. This pin is inter-

nally combined with the RST# pin; If this pin or RST# pin is

driven low, identical operation is exhibited.

ID[3:0]

Identification

Inputs

I

X

These four pins are part of the mechanism that allows multiple

parts to be attached to the same bus. The strapping of these

pins is used to identify the component.The boot device must

have ID[3:0]=0000 and it is recommended that all subsequent

devices should use sequential up-count strapping. These pins

are internally pulled-down with a resistor between 20-100 K

FGPI[4:0] General Pur-

pose Inputs

I

X

These individual inputs can be used for additional board flexibil-

ity. The state of these pins can be read through GPI_REG regis-

ter. These inputs should be at their desired state before the start

of the PCI clock cycle during which the read is attempted, and

should remain in place until the end of the Read cycle. Unused

GPI pins must not be floated.

TBL#

Top Block Lock

I

X

When low, prevents programming to the Boot Block sectors at top of

memory. When TBL# is high it disables hardware write protection for

the top block sectors. This pin cannot be left unconnected.

FWH[3:0] FWH I/Os

I/O

X

I/O Communications

CLK

Clock

I

X

To provide a clock input to the control unit

FWH4

FWH Input

I

X

Input Communications

RST#

Reset

I

X

X

To reset the operation of the device

WP#

Write Protect

I

X

When low, prevents programming to all but the highest address-

able blocks. When WP# is high it disables hardware write protec-

tion for these blocks. This pin cannot be left unconnected.

R/C#

Row/Column

Select

I

X

Select For the Programming interface, this pin determines whether

the address pins are pointing to the row addresses, or to the column

addresses.

RES

Reserved

X

These pins must be left unconnected.

V

DD

Power Supply

PWR

X

X

To provide power supply (3.0-3.6V)

V

SS

Ground

PWR

X

X

Circuit ground (OV reference) All V

SS

pins must be grounded.

NC

No Connection

I

X

X

Unconnected pins

T1.4 25085

1. I = Input, O = Output

©2011 Silicon Storage Technology, Inc.

DS25085A

10/11

7

8 Mbit Firmware Hub

SST49LF008A

Data Sheet

A Microchip Technology Company

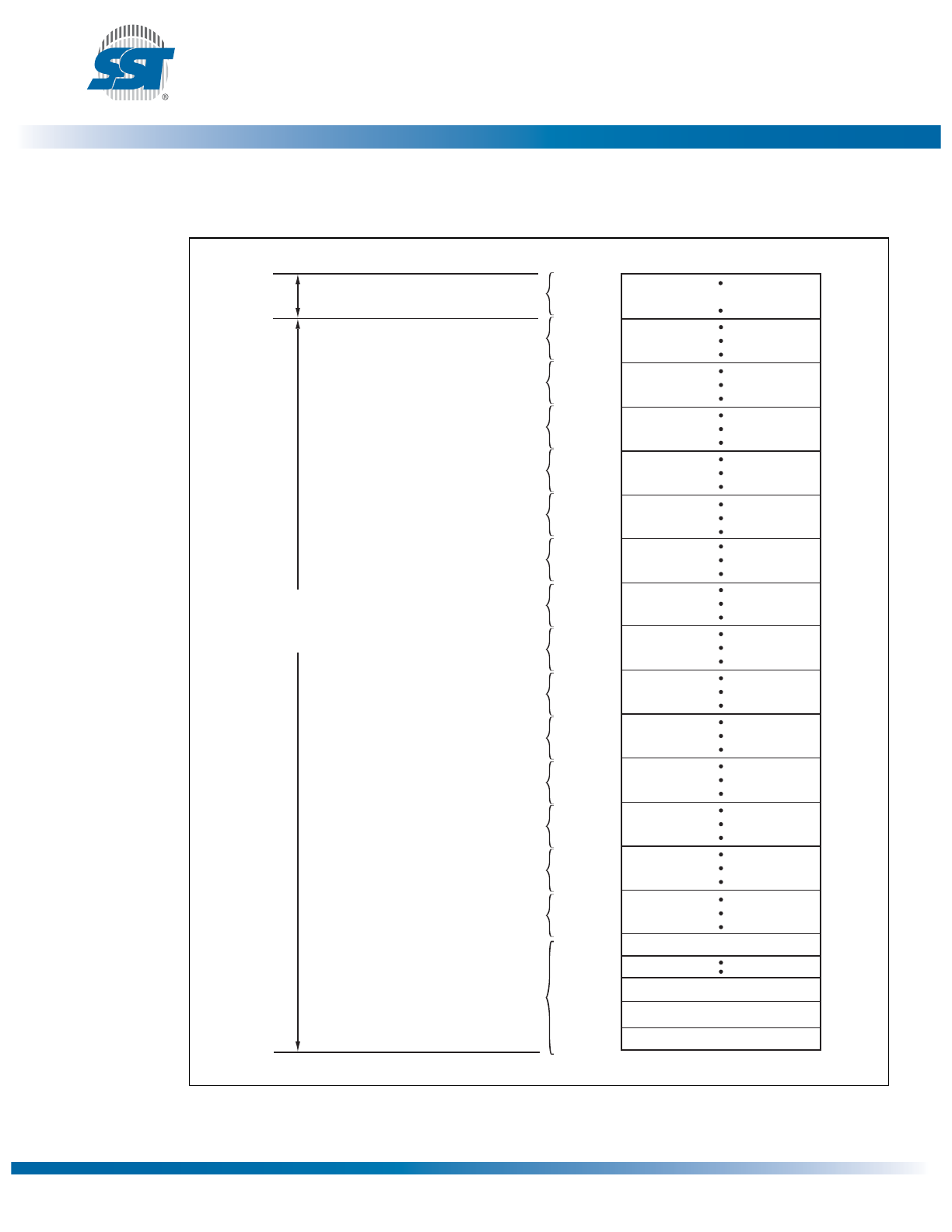

Device Memory Map

Figure 5: Device Memory Map for SST49LF008A

0FFFFFH

0F0000H

0EFFFFH

0E0000H

0DFFFFH

0D0000H

0CFFFFH

0C0000H

0BFFFFH

0B0000H

0AFFFFH

0A0000H

09FFFFH

090000H

08FFFFH

080000H

07FFFFH

070000H

06FFFFH

060000H

05FFFFH

050000H

04FFFFH

040000H

03FFFFH

030000H

02FFFFH

020000H

01FFFFH

010000H

00FFFFH

Block 7

Block 8

Block 6

Block 5

Block 4

Block 3

Block 2

Block 1

Block 15

Block 14

Block 13

Block 12

Block 11

Block 10

Block 9

Block 0

(64 KByte)

1161 F08.0

WP# for

Block 0 14

TBL#

4 KByte Sector 1

4 KByte Sector 2

4 KByte Sector 15

4 KByte Sector 0

Boot Block

002000H

001000H

000000H

©2011 Silicon Storage Technology, Inc.

DS25085A

10/11

8

8 Mbit Firmware Hub

SST49LF008A

Data Sheet

A Microchip Technology Company

Design Considerations

SST recommends a high frequency 0.1 µF ceramic capacitor to be placed as close as possible

between V

DD

and V

SS

less than 1 cm away from the V

DD

pin of the device. Additionally, a low fre-

quency 4.7 µF electrolytic capacitor from V

DD

to V

SS

should be placed within 1 cm of the V

DD

pin. If you

use a socket for programming purposes add an additional 1-10 µF next to each socket.

The RST# pin must remain stable at V

IH

for the entire duration of an Erase operation. WP# must

remain stable at V

IH

for the entire duration of the Erase and Program operations for non-Boot Block

sectors. To write data to the top Boot Block sectors, the TBL# pin must also remain stable at V

IH

for the

entire duration of the Erase and Program operations.

Product Identification

The product identification mode identifies the device as the SST49LF008A and manufacturer as SST.

Mode Selection

The SST49LF008A flash memory devices can operate in two distinct interface modes: the Firmware

Hub Interface (FWH) mode and the Parallel Programming (PP) mode. The IC (Interface Configuration

pin) is used to set the interface mode selection. If the IC pin is set to logic High, the device is in PP

mode; while if the IC pin is set Low, the device is in the FWH mode. The IC selection pin must be con-

figured prior to device operation. The IC pin is internally pulled down if the pin is not connected. In

FWH mode, the device is configured to interface with its host using Intel’s Firmware Hub proprietary

protocol. Communication between Host and the SST49LF008A occurs via the 4-bit I/O communication

signals, FWH [3:0] and the FWH4. In PP mode, the device is programmed via an 11-bit address and

an 8-bit data I/O parallel signals. The address inputs are multiplexed in row and column selected by

control signal R/C# pin. The column addresses are mapped to the higher internal addresses, and the

row addresses are mapped to the lower internal addresses. See the Device Memory Map in Figure 5

for address assignments.

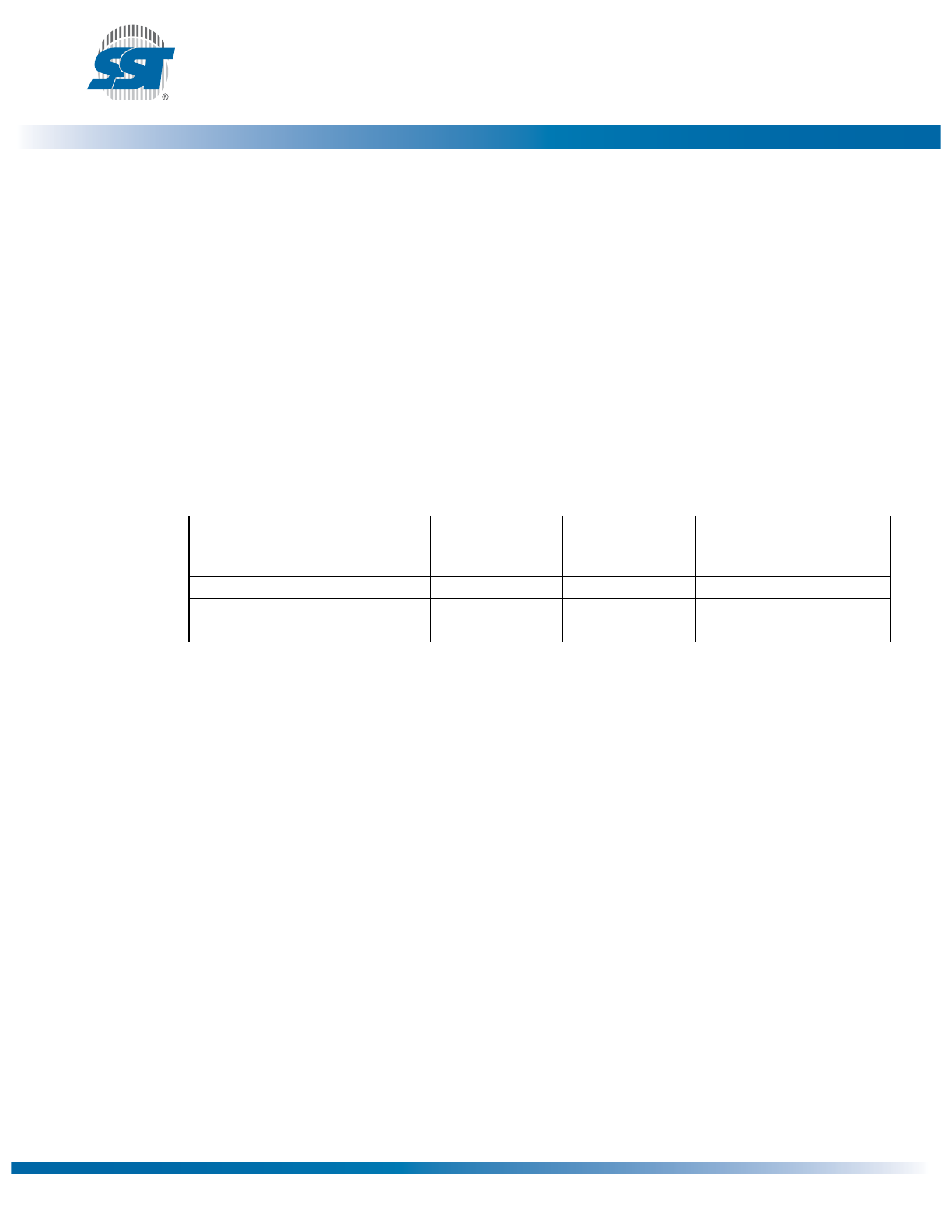

Table 2: Product Identification

Byte

Data

JEDEC ID

Address

Location

Manufacturer’s ID

0000H

BFH

FFBC0000H

Device ID

SST49LF008A

0001H

5AH

FFBC0001H

T2.7 25085

©2011 Silicon Storage Technology, Inc.

DS25085A

10/11

9

8 Mbit Firmware Hub

SST49LF008A

Data Sheet

A Microchip Technology Company

Firmware Hub (FWH) Mode

Device Operation

The FWH mode uses a 5-signal communication interface, FWH[3:0] and FWH4, to control operations

of the SST49LF008A. Operations such as Memory Read and Memory Write uses Intel FWH propriety

protocol. JEDEC Standard SDP (Software Data Protection) Byte-Program, Sector-Erase and Block-

Erase command sequences are incorporated into the FWH memory cycles. Chip-Erase is only avail-

able in PP Mode.

The device enters standby mode when FWH4 is high and no internal operation is in progress. The

device is in ready mode when FWH4 is low and no activity is on the FWH bus.

Firmware Hub Interface Cycles

Addresses and data are transferred to and from the SST49LF008A by a series of “fields,” where each

field contains 4 bits of data. SST49LF008A supports only single-byte Read and Write, and all fields are

one clock cycle in length. Field sequences and contents are strictly defined for Read and Write opera-

tions. Addresses in this section refer to addresses as seen from the SST49LF008A’s “point of view,”

some calculation will be required to translate these to the actual locations in the memory map (and

vice versa) if multiple memory devices are used on the bus. Tables 3 and 4 list the field sequences for

Read and Write cycles.

©2011 Silicon Storage Technology, Inc.

DS25085A

10/11

10

8 Mbit Firmware Hub

SST49LF008A

Data Sheet

A Microchip Technology Company

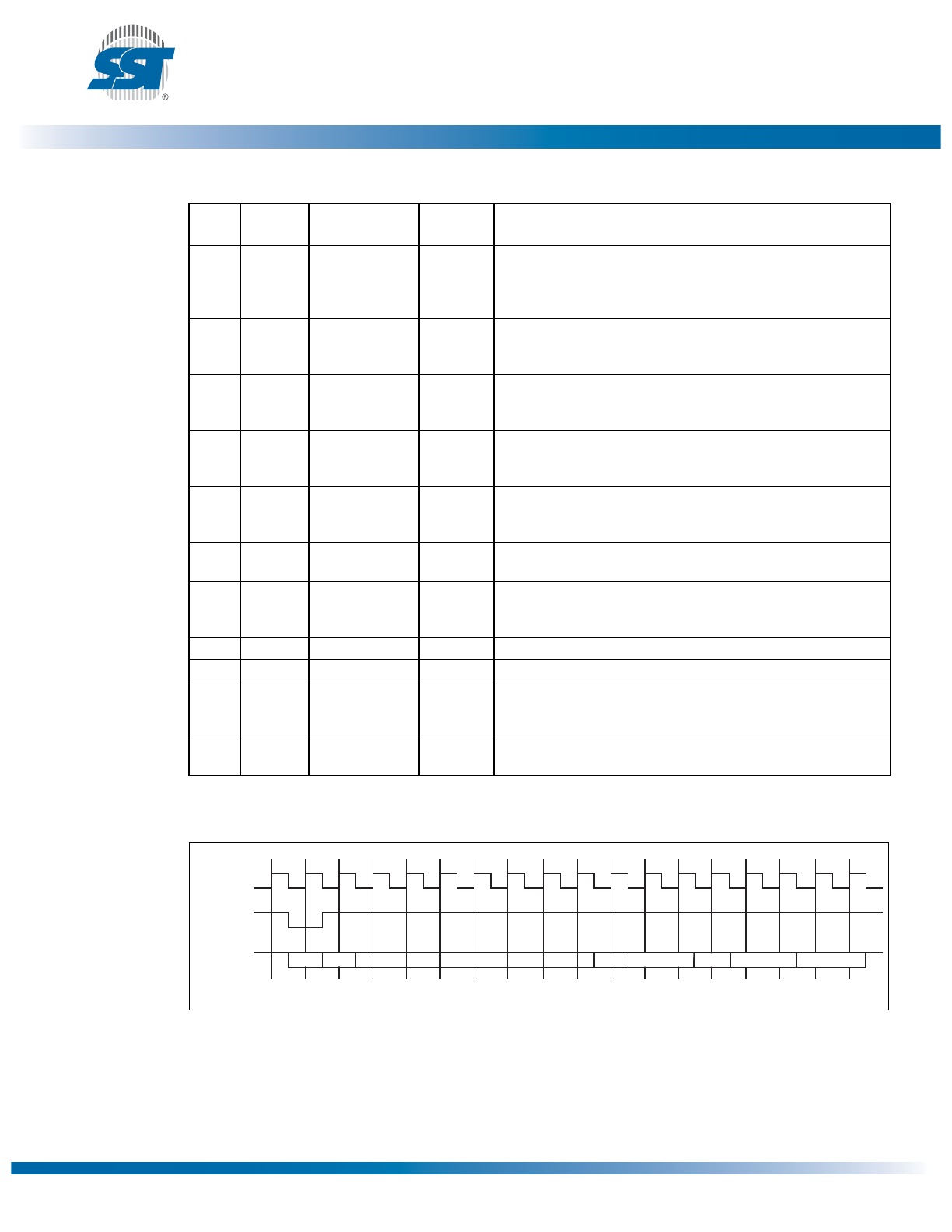

Figure 6: Single-Byte Read Waveforms

Table 3: FWH Read Cycle

Clock

Cycle

Field

Name

Field Contents

FWH[3:0]

1

FWH[3:0]

Direction

Comments

1

START

1101

IN

FWH4 must be active (low) for the part to respond. Only the

last start field (before FWH4 transitions high) should be recog-

nized. The START field contents indicate a FWH memory

Read cycle.

2

IDSEL

0000 to 1111

IN

Indicates which FWH device should respond. If the to IDSEL (ID

select) field matches the value ID[3:0], then that particular device will

respond to the whole bus cycle.

3-9

IMADDR

YYYY

IN

These seven clock cycles make up the 28-bit memory address.

YYYY is one nibble of the entire address. Addresses are trans-

ferred most-significant nibble first.

10

IMSIZE

0000 (1 byte)

IN

A field of this size indicates how many bytes will be or trans-

ferred during multi-byte operations. The SST49LF008A will only

support single-byte operation. IMSIZE=0000b

11

TAR0

1111

IN

then Float

In this clock cycle, the master (Intel ICH) has driven the bus

then float to all ‘1’s and then floats the bus, prior to the next

clock cycle. This is the first part of the bus “turnaround cycle.”

12

TAR1

1111 (float)

Float

then OUT

The SST49LF008A takes control of the bus during this cycle.

During the next clock cycle, it will be driving “sync data.”

13

RSYNC

0000 (READY)

OUT

During this clock cycle, the FWH will generate a “ready-sync”

(RSYNC) indicating that the least-significant nibble of the least-

significant byte will be available during the next clock cycle.

14

DATA

YYYY

OUT

YYYY is the least-significant nibble of the least-significant data byte.

15

DATA

YYYY

OUT

YYYY is the most-significant nibble of the least-significant data byte.

16

TAR0

1111

OUT

then Float

In this clock cycle, the SST49LF008A has driven the bus to all

ones and then floats the bus prior to the next clock cycle. This

is the first part of the bus “turnaround cycle.”

17

TAR1

1111 (float)

Float then

IN

The master (Intel ICH) resumes control of the bus during this

cycle.

T3.3 25085

1. Field contents are valid on the rising edge of the present clock cycle.

CLK

FWH4

FWH[3:0]

1161 F09.0

STR

TAR

RSYNC

IMS

IMADDR

IDS

DATA

TAR