IRFHM8337TRPbF

HEXFET

®

Power MOSFET

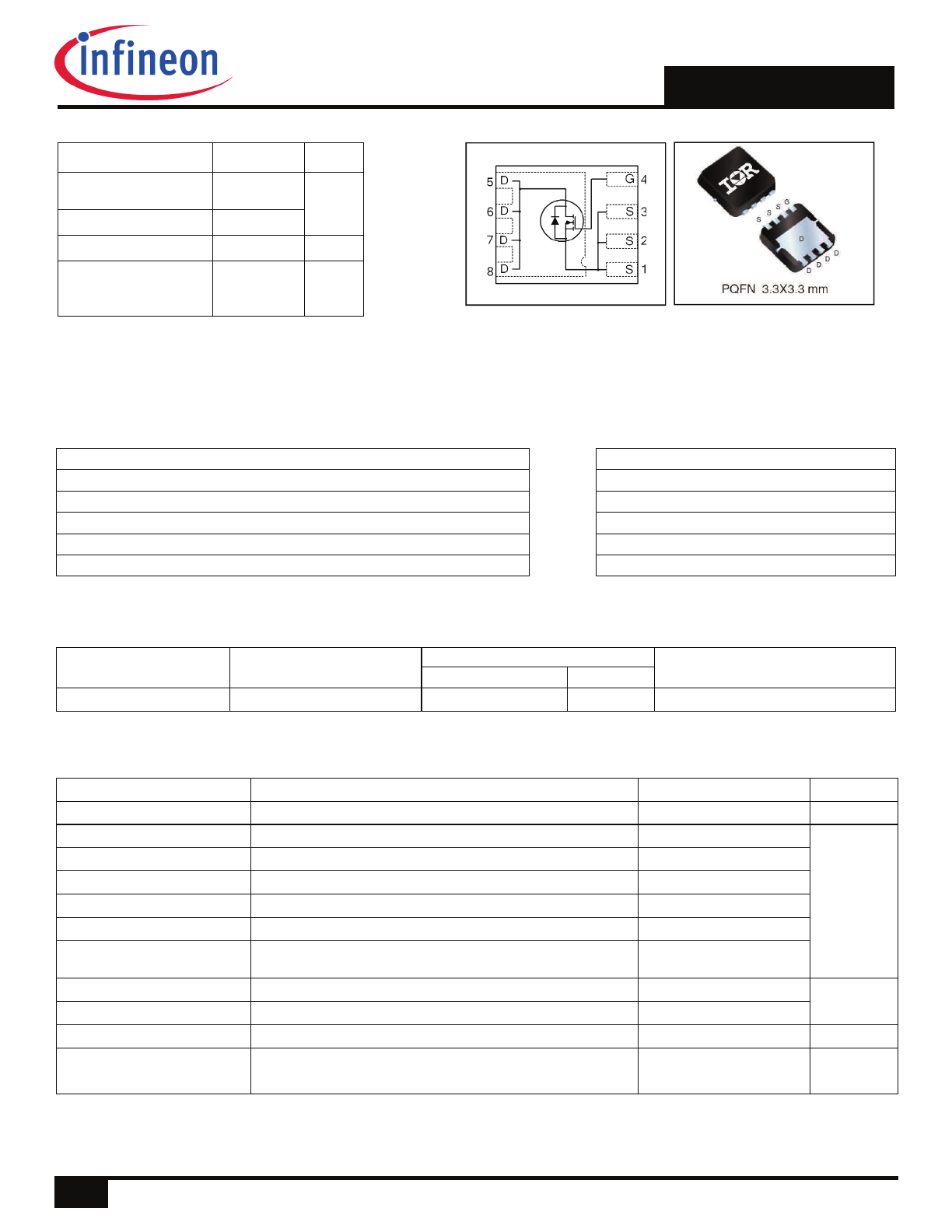

Base part number

Package Type

Standard Pack

Form

Quantity

IRFHM8337PbF

PQFN 3.3mm x 3.3mm

Tape and Reel

4000

IRFHM8337TRPbF

Orderable Part Number

V

DSS

30

V

R

DS(on)

max

(@ V

GS

= 10V)

12.4

(@ V

GS

= 4.5V)

17.9

Qg

(typical)

5.4

nC

I

D

(@T

C

= 25°C)

18 A

m

PQFN 3.3 x 3.3 mm

Features

Benefits

Low Thermal Resistance to PCB (< 5.0°C/W)

Enable better Thermal Dissipation

Low Profile (<1.05 mm)

results in Increased Power Density

Industry-Standard Pinout

Multi-Vendor Compatibility

Compatible with Existing Surface Mount Techniques

Easier Manufacturing

RoHS Compliant, Halogen-Free

Environmentally Friendlier

MSL1,Consumer Qualification

Increased Reliability

Notes through are on page 8

Absolute Maximum Ratings

Parameter Max.

Units

V

GS

Gate-to-Source Voltage

± 20

V

I

D

@ T

A

= 25°C

Continuous Drain Current, V

GS

@ 10V

12

A

I

D

@ T

A

= 70°C

Continuous Drain Current, V

GS

@ 10V

9.4

I

DM

Pulsed Drain Current 94

I

D

@ T

C(Bottom)

= 25°C

Continuous Drain Current, V

GS

@ 10V

35

I

D

@ T

C(Bottom)

= 100°C

Continuous Drain Current, V

GS

@ 10V

22

I

D

@ T

C

= 25°C

Continuous Drain Current, V

GS

@ 10V

(Source Bonding Technology Limited)

18

P

D

@T

A

= 25°C

Power Dissipation 2.8

W

P

D

@T

C(Bottom)

= 25°C

Power Dissipation 25

Linear Derating Factor 0.02

W/°C

T

J

Operating Junction and

-55 to + 150

°C

T

STG

Storage Temperature Range

Applications

System/load switch,

Charge or discharge switch for battery protection

1

2016-2-23

IRFHM8337TRPbF

2

2016-2-23

Static @ T

J

= 25°C (unless otherwise specified)

Parameter Min.

Typ.

Max.

Units

Conditions

BV

DSS

Drain-to-Source Breakdown Voltage

30

–––

–––

V

V

GS

= 0V, I

D

= 250µA

BV

DSS

/

T

J

Breakdown Voltage Temp. Coefficient

–––

0.02

–––

V/°C Reference to 25°C, I

D

= 1mA

R

DS(on)

Static Drain-to-Source On-Resistance

––– 9.4 12.4

m

V

GS

= 10V, I

D

= 12A

––– 14.5 17.9

V

GS

= 4.5V, I

D

=9.4A

V

GS(th)

Gate Threshold Voltage

1.35

1.8

2.35

V

V

DS

= V

GS

, I

D

= 25µA

V

GS(th)

Gate Threshold Voltage Coefficient

–––

-6.2

––– mV/°C

I

DSS

Drain-to-Source Leakage Current

––– ––– 1.0

µA

V

DS

= 24V, V

GS

= 0V

––– ––– 150

V

DS

= 24V, V

GS

= 0V,T

J

= 125°C

I

GSS

Gate-to-Source Forward Leakage –––

–––

100

µA

V

GS

= 20V

Gate-to-Source Reverse Leakage

–––

–––

-100

V

GS

=-20 V

gfs Forward

Transconductance

17

–––

–––

S

V

DS

= 15V, I

D

= 9.4A

Q

g

Total Gate Charge

–––

5.4

8.1

Q

gs1

Pre-Vth Gate-to-Source Charge

–––

1.1

–––

V

DS

= 15V

Q

gs2

Post-Vth Gate-to-Source Charge

–––

0.7

–––

nC V

GS

= 4.5V

Q

gd

Gate-to-Drain Charge

–––

2.2

–––

I

D

= 9.4A

Q

godr

Gate Charge Overdrive

–––

1.5

–––

Q

sw

Switch Charge (Q

gs2

+ Q

gd

) –––

2.9

–––

Q

oss

Output Charge

–––

3.8

–––

nC V

DS

= 16V, V

GS

= 0V

R

G

Gate Resistance

–––

2.0

–––

t

d(on)

Turn-On Delay Time

–––

9.0

–––

V

DD

= 15V, V

GS

= 4.5V

t

r

Rise Time

–––

11

–––

ns I

D

= 9.4A

t

d(off)

Turn-Off Delay Time

–––

9.9

–––

R

G

= 1.3

t

f

Fall Time

–––

5.6

–––

C

iss

Input Capacitance

–––

755

–––

V

GS

= 0V

C

oss

Output Capacitance

–––

171

–––

pF V

DS

= 15V

C

rss

Reverse Transfer Capacitance

–––

83

–––

ƒ = 1.0MHz

Parameter Typ.

Max.

Units

R

JC

(Bottom) Junction-to-Case –––

5.0

R

JC

(Top)

Junction-to-Case –––

50

°C/W

R

JA

Junction-to-Ambient –––

45

R

JA

(<10s)

Junction-to-Ambient –––

31

Thermal Resistance

Diode Characteristics

Parameter

Min.

Typ.

Max. Units

Conditions

I

S

Continuous Source Current

–––

–––

18 MOSFET

symbol

(Body Diode)

showing the

I

SM

Pulsed Source Current

–––

–––

94

integral reverse

(Body Diode)

p-n junction diode.

V

SD

Diode Forward Voltage

–––

–––

1.0

V

T

J

= 25°C, I

S

= 9.4A, V

GS

= 0V

t

rr

Reverse Recovery Time

–––

20

30

ns

T

J

= 25°C, I

F

= 9.4A, V

DD

= 15V

Q

rr

Reverse Recovery Charge

–––

27

41

nC di/dt = 200A/µs

A

Avalanche Characteristics

Parameter Typ.

Max.

Units

E

AS

Single Pulse Avalanche Energy –––

13 mJ

D

S

G

IRFHM8337TRPbF

3

2016-2-23

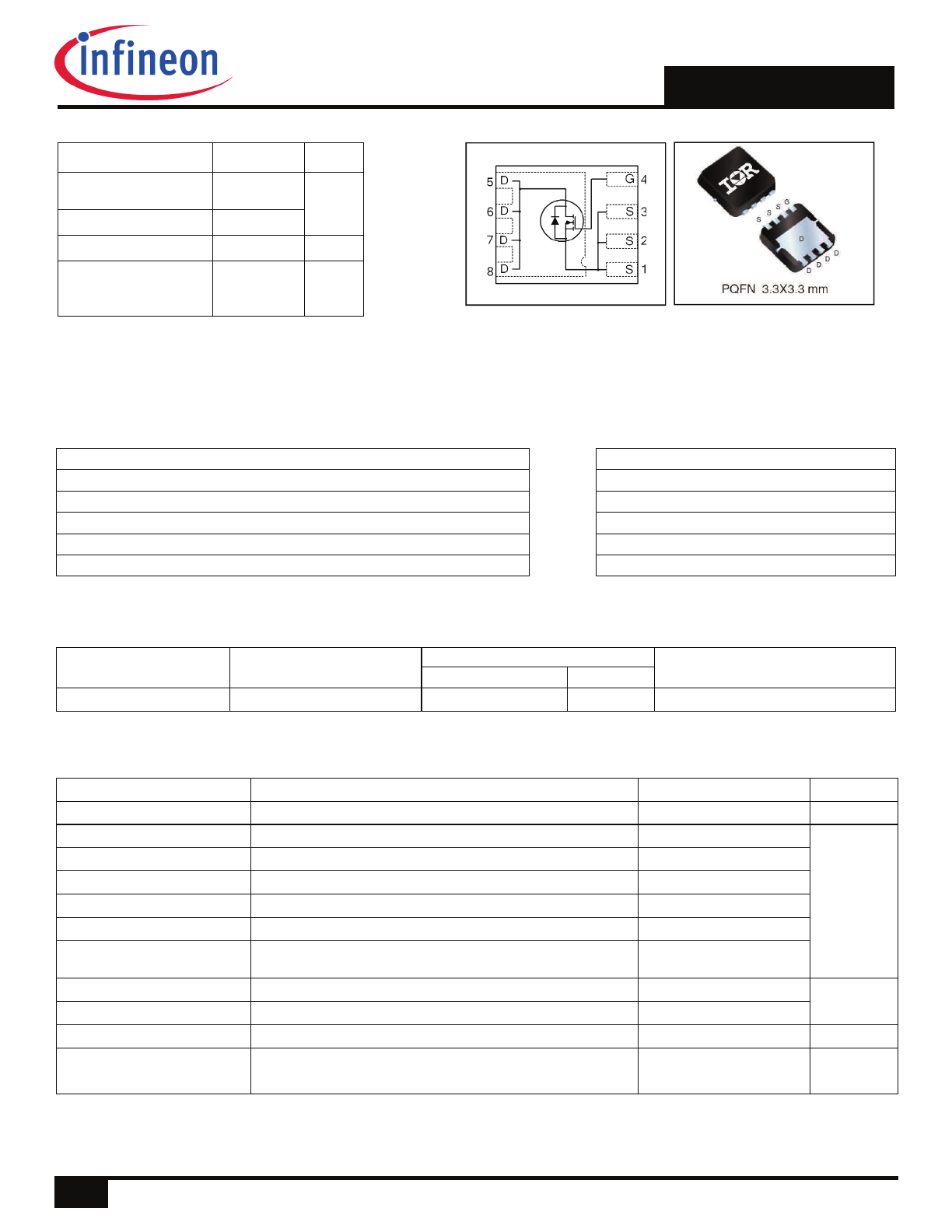

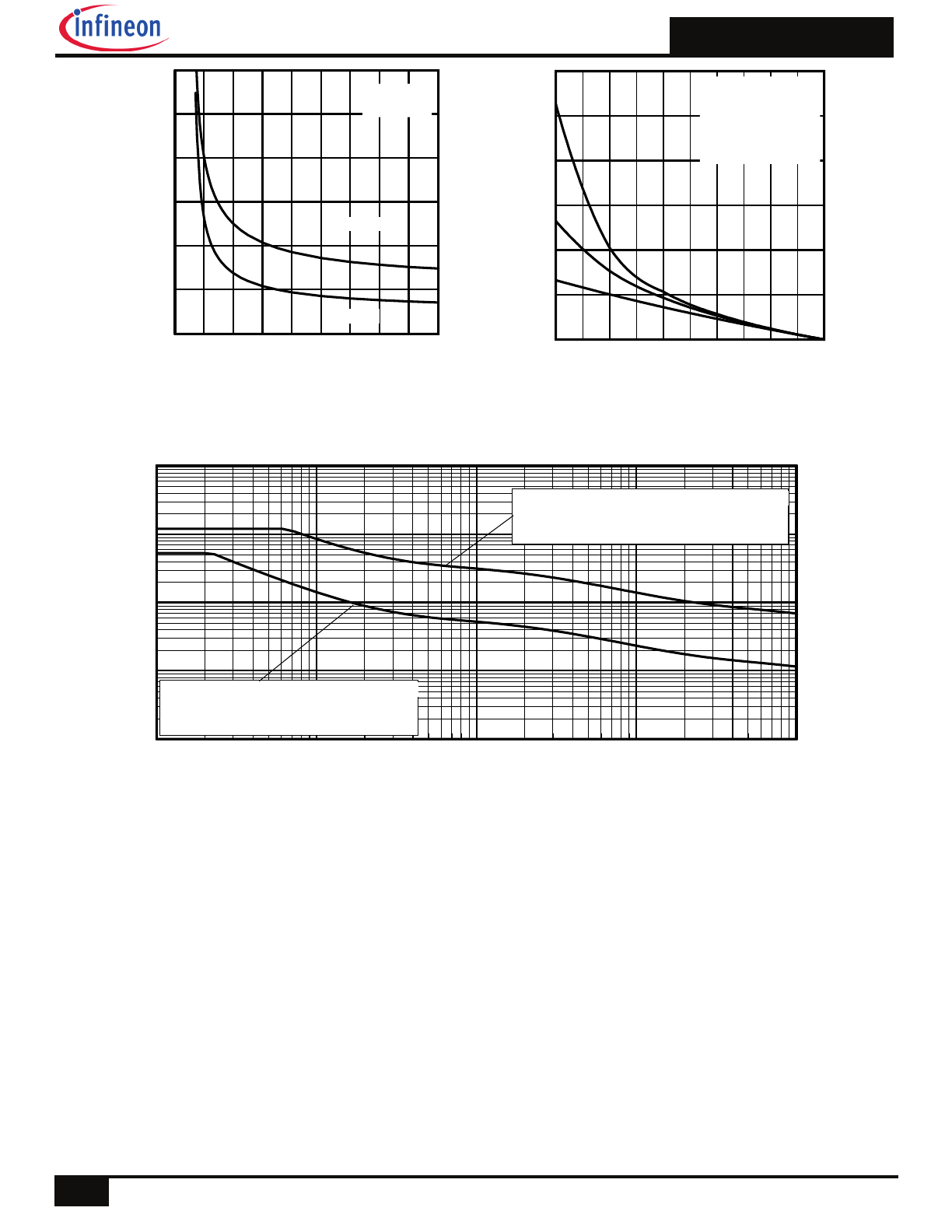

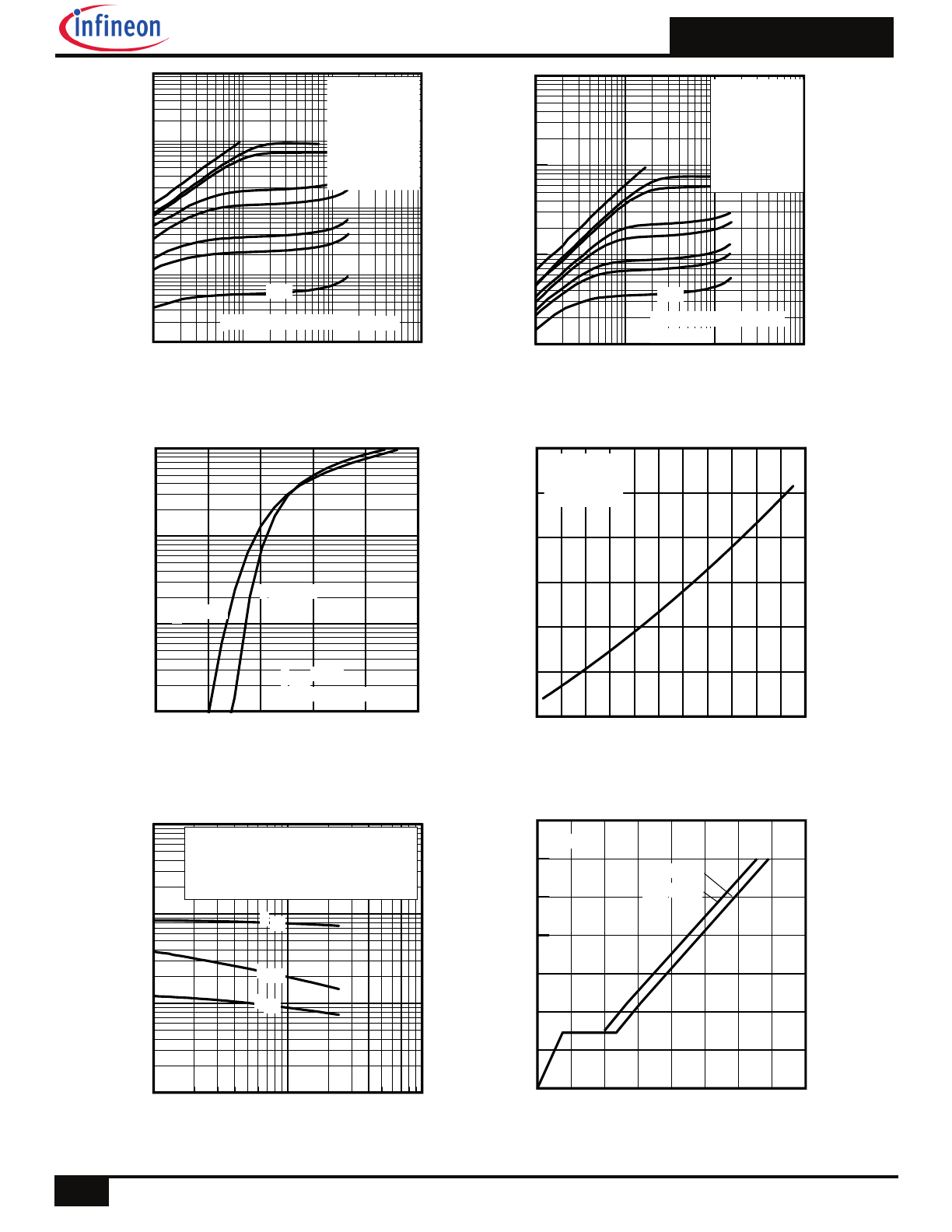

Fig 1. Typical Output Characteristics

Fig 4. Normalized On-Resistance vs. Temperature

Fig 5. Typical Capacitance vs. Drain-to-Source Voltage

Fig 6. Typical Gate Charge vs. Gate-to-Source Voltage

Fig 3. Typical Transfer Characteristics

Fig 2. Typical Output Characteristics

0.1

1

10

100

VDS, Drain-to-Source Voltage (V)

0.1

1

10

100

1000

I D

,

D

ra

in

-t

o

-S

ou

rc

e

C

u

rr

en

t

(A

)

VGS

TOP 10V

5.0V

4.5V

3.5V

3.3V

3.0V

2.9V

BOTTOM

2.7V

60µs PULSE WIDTH

Tj = 25°C

2.7V

0.1

1

10

100

VDS, Drain-to-Source Voltage (V)

1

10

100

1000

I D

, D

ra

in

-t

o-

S

o

ur

ce

C

u

rr

en

t

(A

)

2.7V

60µs PULSE WIDTH

Tj = 150°C

VGS

TOP 10V

5.0V

4.5V

3.5V

3.3V

3.0V

2.9V

BOTTOM

2.7V

1

2

3

4

5

6

VGS, Gate-to-Source Voltage (V)

0.1

1

10

100

I D

, D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(A

)

TJ = 25°C

TJ = 150°C

VDS = 15V

60µs PULSE WIDTH

-60 -40 -20 0 20 40 60 80 100 120 140 160

TJ , Junction Temperature (°C)

0.6

0.8

1.0

1.2

1.4

1.6

1.8

R

D

S

(o

n)

,

D

ra

in

-t

o-

S

ou

rc

e

O

n

R

es

is

ta

nc

e

(

N

or

m

al

iz

ed

)

ID = 12A

VGS = 10V

1

10

100

VDS, Drain-to-Source Voltage (V)

10

100

1000

10000

C

, C

ap

ac

ita

nc

e

(p

F

)

VGS = 0V, f = 1 MHZ

Ciss = Cgs + Cgd, C ds SHORTED

Crss = Cgd

Coss = Cds + Cgd

Coss

Crss

Ciss

0

2

4

6

8

10

12

14

16

QG, Total Gate Charge (nC)

0.0

2.0

4.0

6.0

8.0

10.0

12.0

14.0

V

G

S

, G

at

e-

to

-S

ou

rc

e

V

ol

ta

ge

(

V

)

VDS= 24V

VDS= 15V

ID= 9.4A

IRFHM8337TRPbF

4

2016-2-23

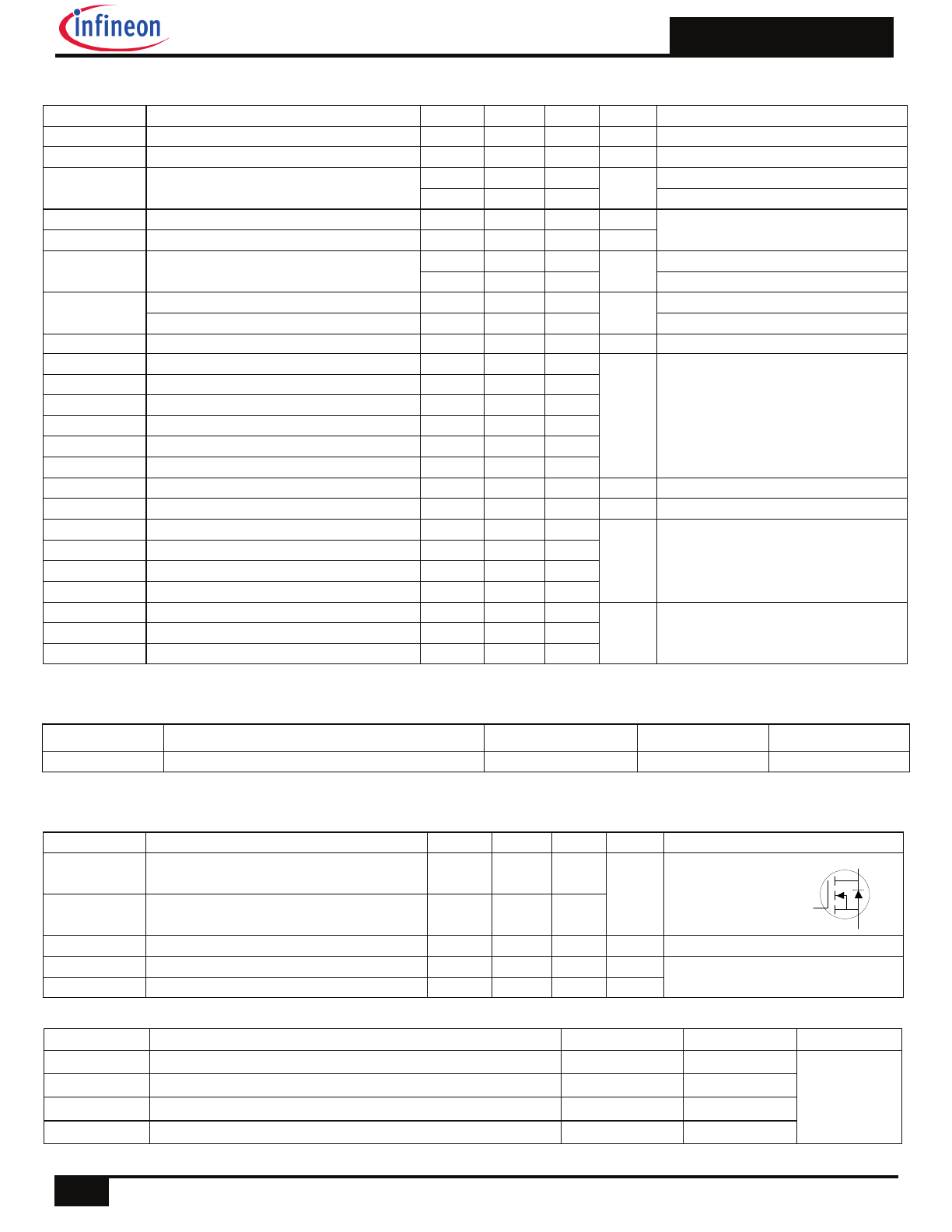

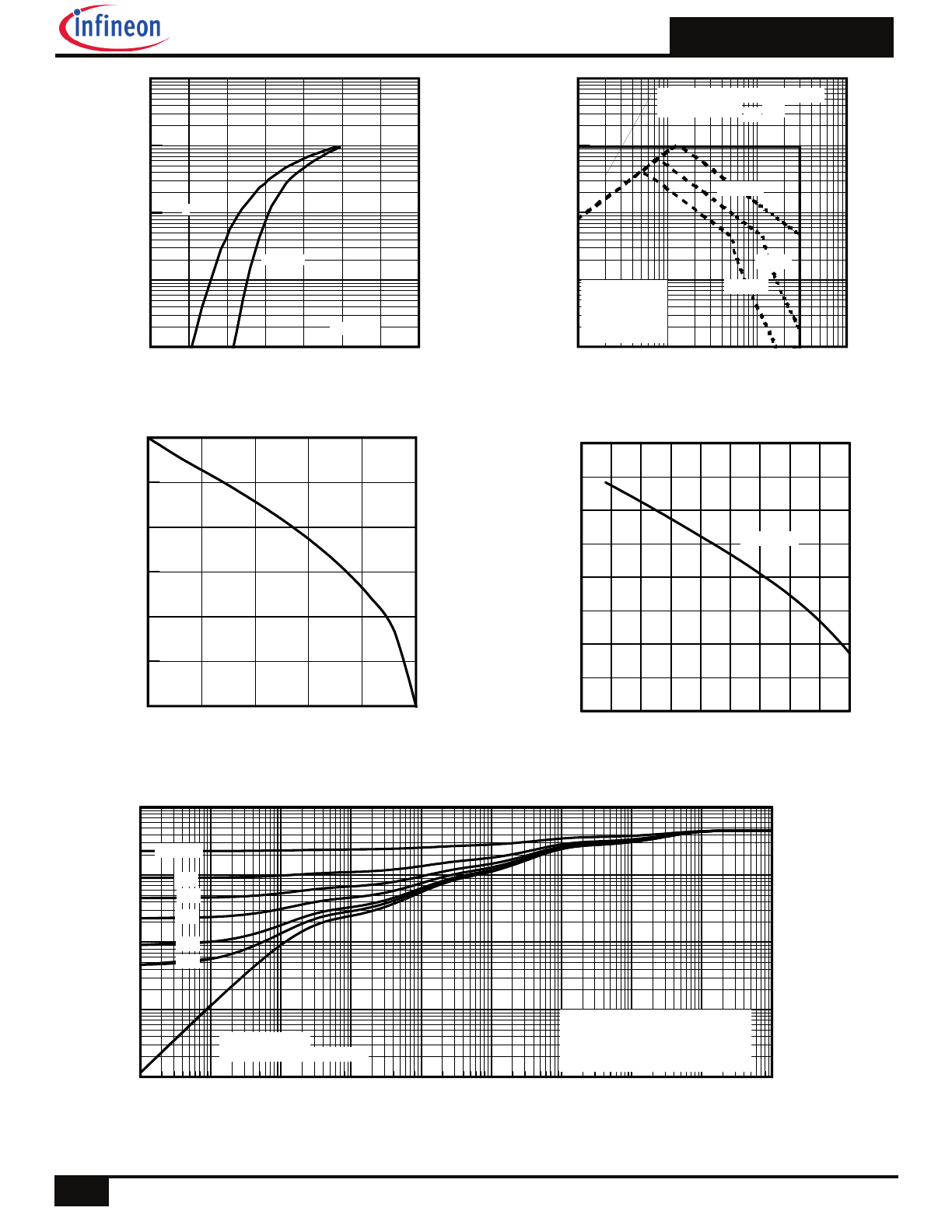

Fig 8. Maximum Safe Operating Area

Fig 7. Typical Source-Drain Diode Forward Voltage

25

50

75

100

125

150

TA , Ambient Temperature (°C)

0

2

4

6

8

10

12

I D

,

D

ra

in

C

ur

re

nt

(

A

)

Fig 9. Maximum Drain Current vs. Ambient Temperature

1E-006

1E-005

0.0001

0.001

0.01

0.1

1

10

100

1000

t1 , Rectangular Pulse Duration (sec)

0.01

0.1

1

10

100

T

he

rma

l R

es

po

ns

e

(

Z

th

JA

)

°

C

/W

0.20

0.10

D = 0.50

0.02

0.01

0.05

SINGLE PULSE

( THERMAL RESPONSE )

Notes:

1. Duty Factor D = t1/t2

2. Peak Tj = P dm x Zthja + TA

-75 -50 -25

0

25

50

75 100 125 150

TJ , Temperature ( °C )

0.5

1.0

1.5

2.0

2.5

V

G

S

(t

h)

, G

at

e

T

hr

es

ho

ld

V

ol

ta

ge

(

V

)

ID = 25µA

Fig 10.

Threshold Voltage Vs. Temperature

Fig 11. Maximum Effective Transient Thermal Impedance, Junction-to-Case

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

VSD, Source-to-Drain Voltage (V)

0.1

1

10

100

1000

I S

D

, R

ev

er

se

D

ra

in

C

ur

re

nt

(

A

)

TJ = 25°C

TJ = 150°C

VGS = 0V

0

1

10

100

VDS, Drain-to-Source Voltage (V)

0.1

1

10

100

1000

I D

,

D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(

A

)

OPERATION IN THIS AREA

LIMITED BY R DS(on)

TA = 25°C

Tj = 150°C

Single Pulse

100µsec

1msec

10msec

IRFHM8337TRPbF

5

2016-2-23

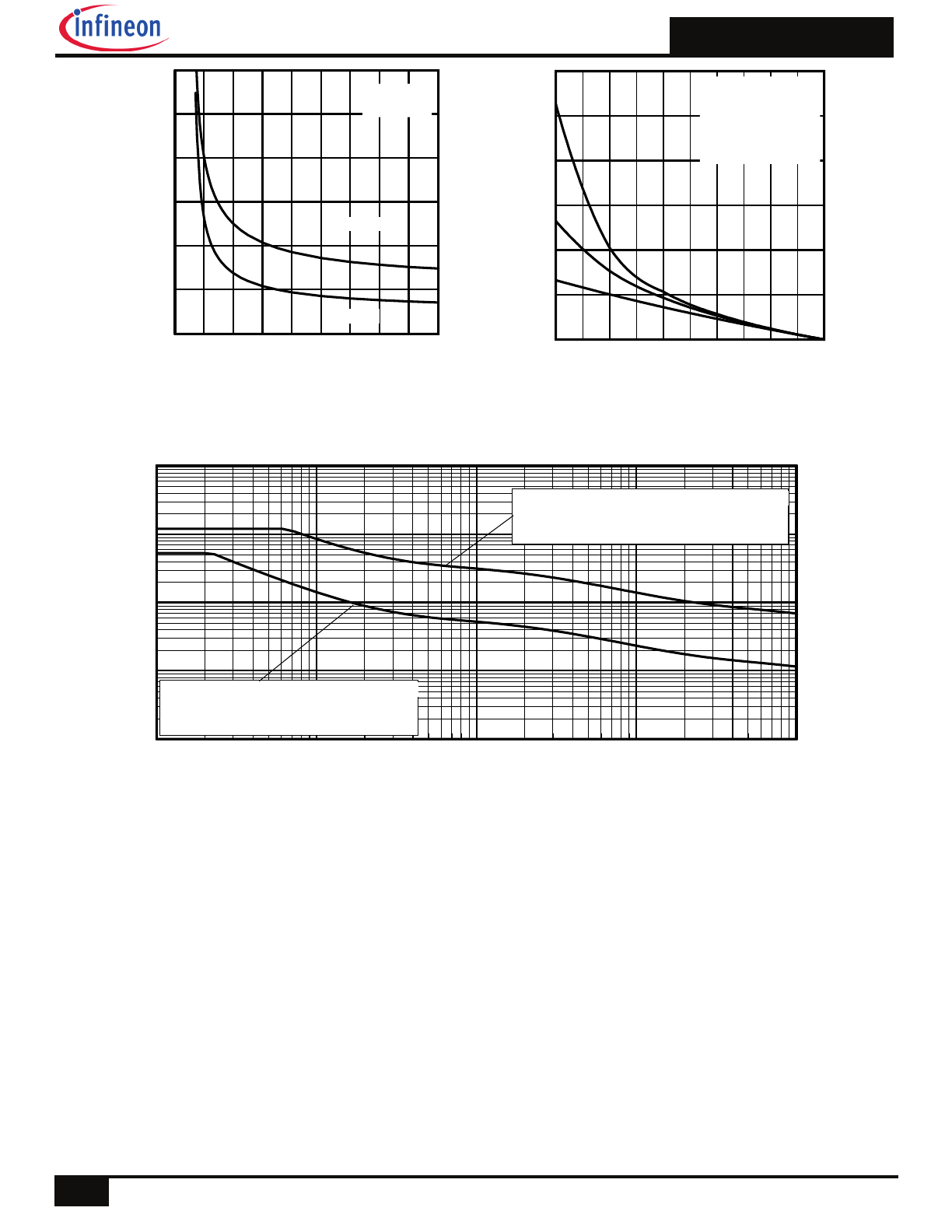

25

50

75

100

125

150

Starting TJ , Junction Temperature (°C)

0

10

20

30

40

50

60

E

A

S

,

S

in

gl

e

P

ul

se

A

va

la

nc

he

E

ne

rg

y

(m

J)

ID

TOP 2.95A

3.63A

BOTTOM 9.40A

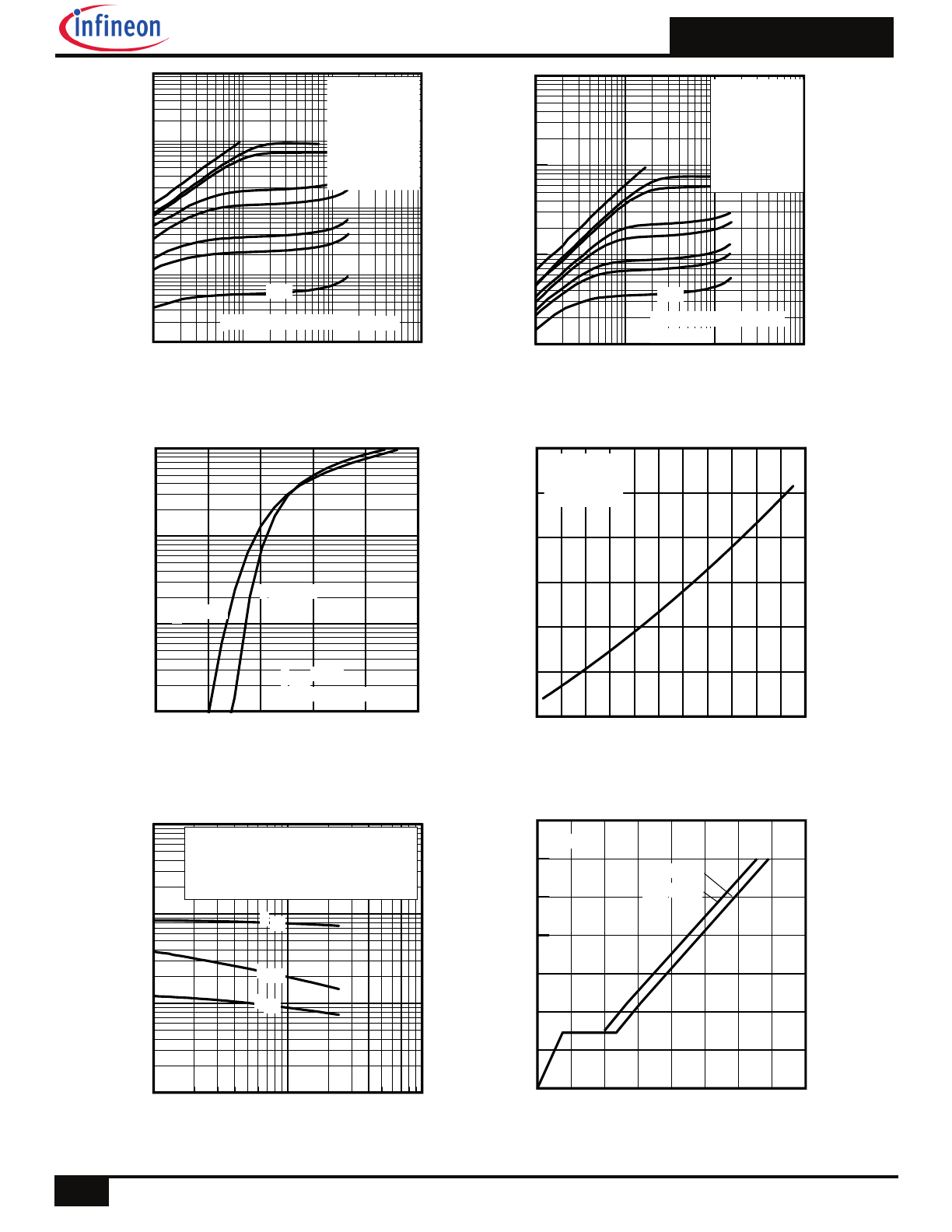

Fig 13. Maximum Avalanche Energy vs. Drain Current

Fig 14. Single avalanche event: pulse current vs. pulse width

2

4

6

8

10

12

14

16

18

20

VGS, Gate -to -Source Voltage (V)

5

10

15

20

25

30

35

R

D

S

(o

n)

,

D

ra

in

-t

o

-S

ou

rc

e

O

n

R

es

is

ta

nc

e

(m

)

ID = 12A

TJ = 25°C

TJ = 125°C

Fig 12. On– Resistance vs. Gate Voltage

1.0E-05

1.0E-04

1.0E-03

1.0E-02

1.0E-01

tav (sec)

0.01

0.1

1

10

100

A

va

la

nc

he

C

ur

re

nt

(

A

)

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming

j = 25°C and

Tstart = 125°C.

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming

Tj = 125°C and

Tstart =25°C (Single Pulse)

IRFHM8337TRPbF

6

2016-2-23

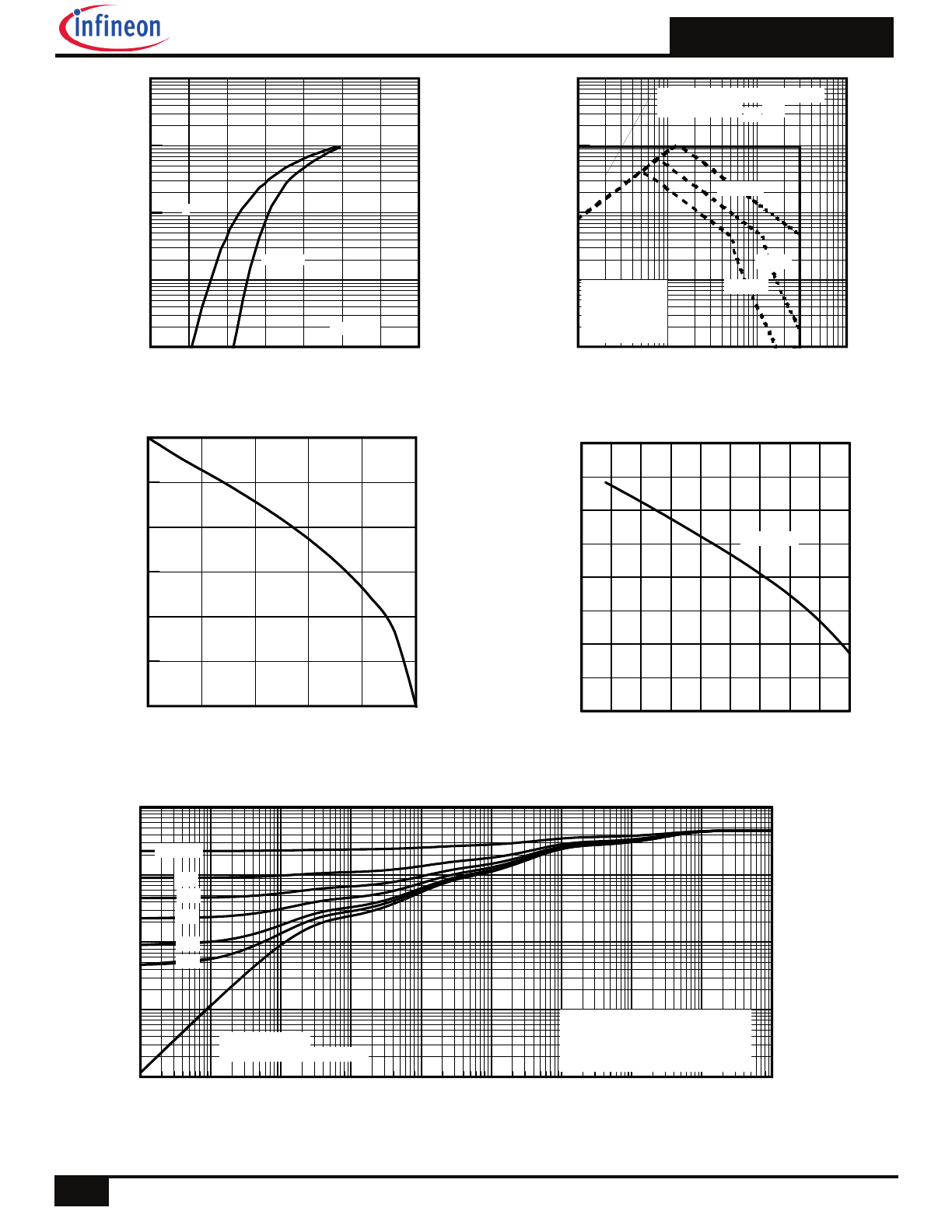

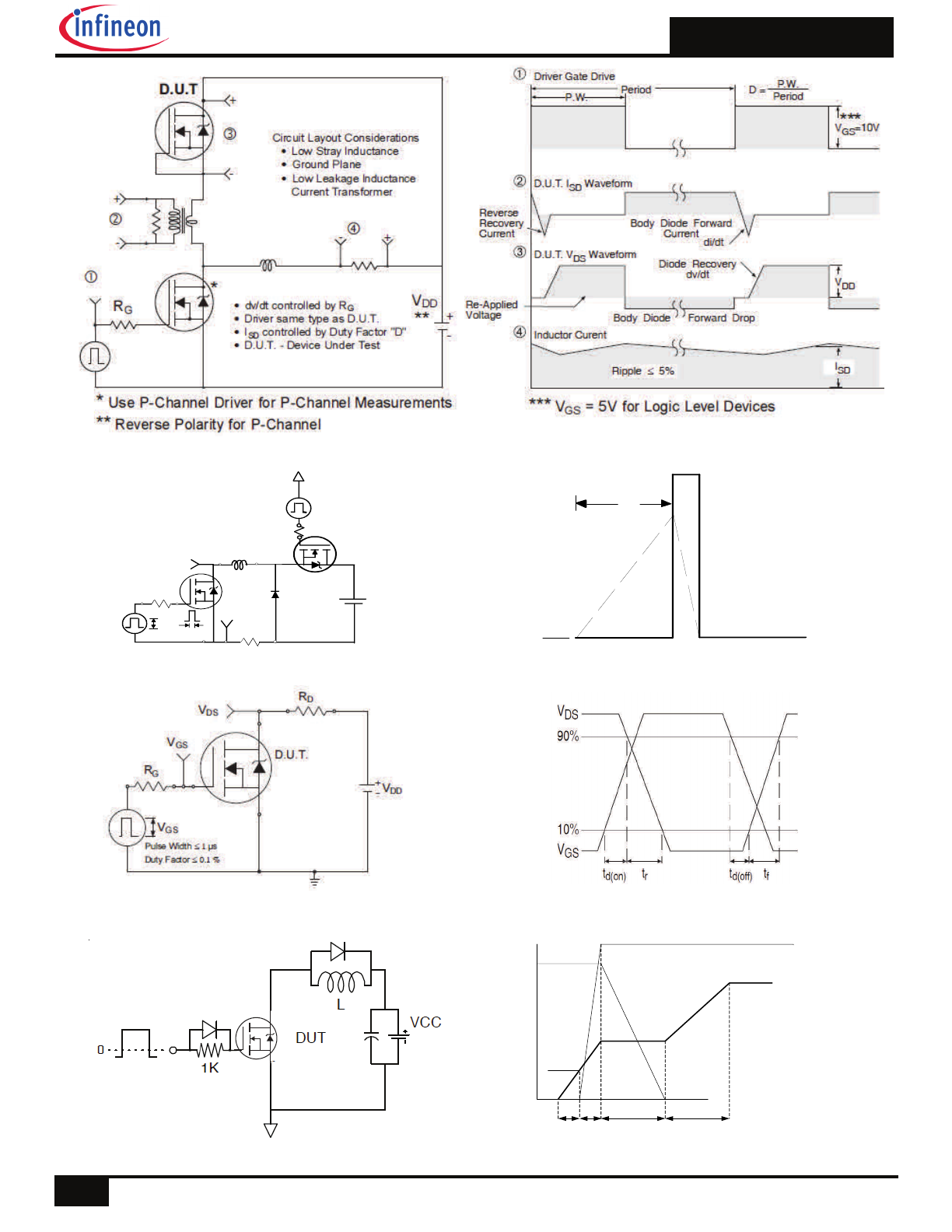

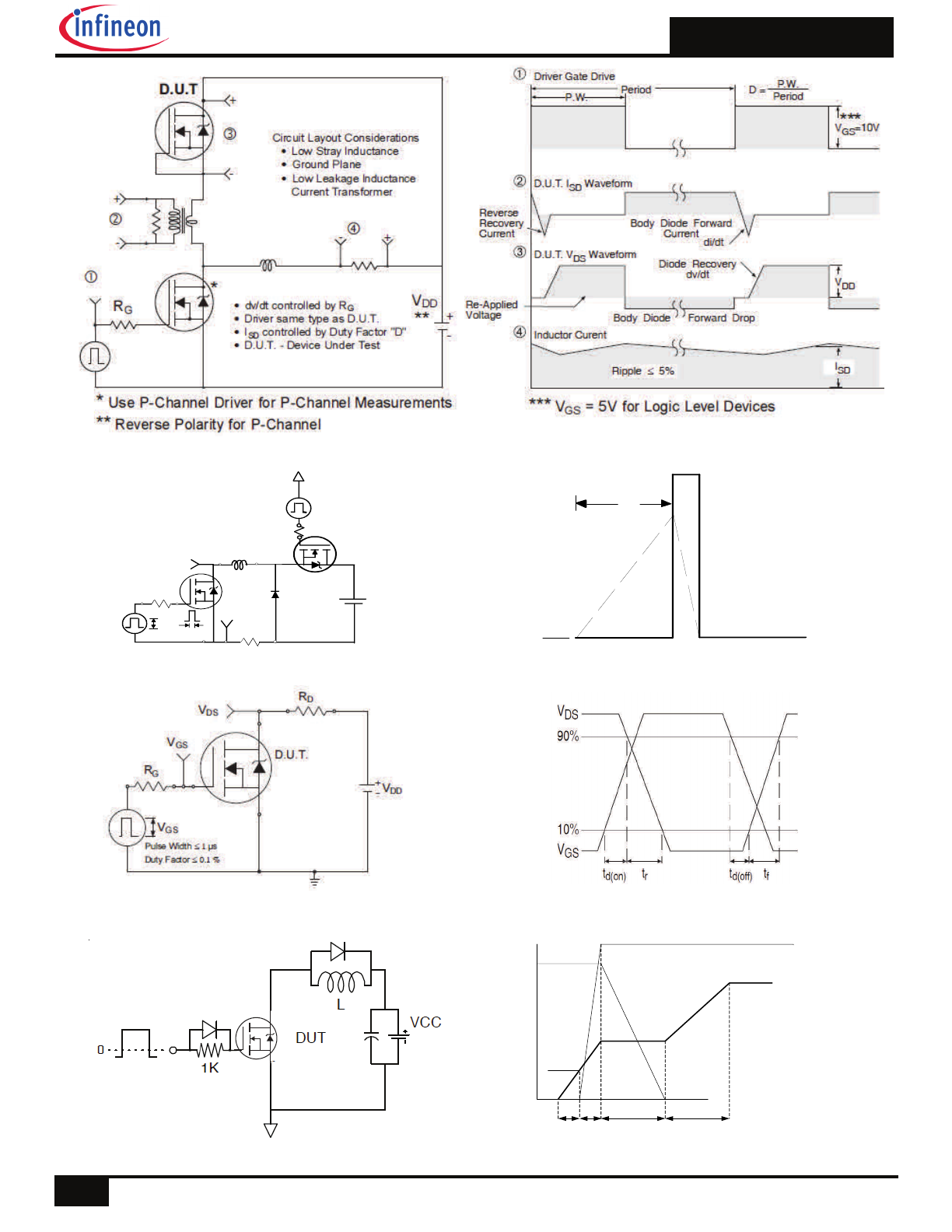

Fig 15. Peak Diode Recovery dv/dt Test Circuit for N-Channel HEXFET

®

Power MOSFETs

Fig 18. Gate Charge Test Circuit

Vds

Vgs

Id

Vgs(th)

Qgs1 Qgs2

Qgd

Qgodr

Fig 19. Gate Charge Waveform

Fig 17a. Switching Time Test Circuit

Fig 17b. Switching Time Waveforms

Fig 16a. Unclamped Inductive Test Circuit

R G

I

AS

0.01

tp

D.U.T

L

VDS

+

- VDD

DRIVER

A

15V

20V

tp

V

(BR)DSS

I

AS

Fig 16b. Unclamped Inductive Waveforms

IRFHM8337TRPbF

7

2016-2-23

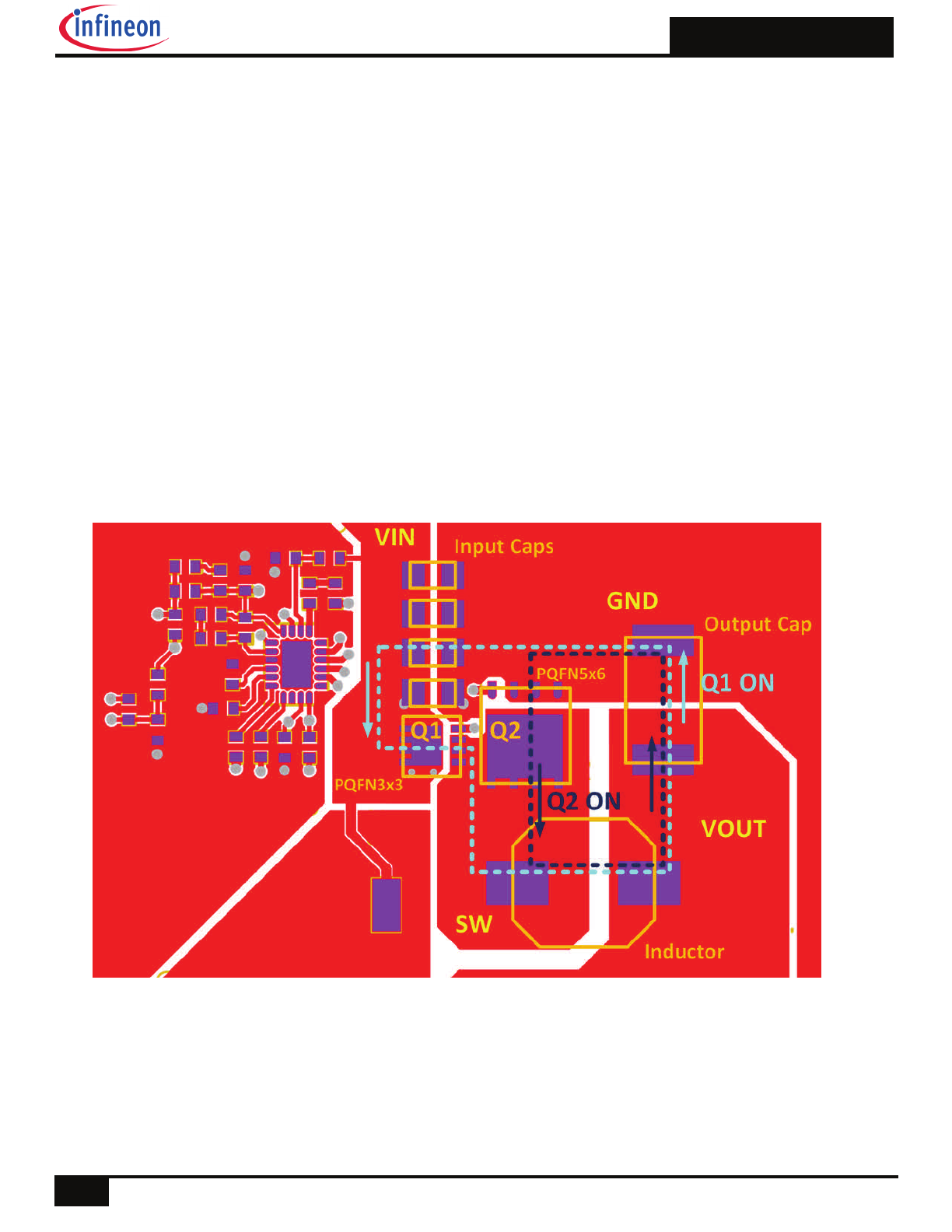

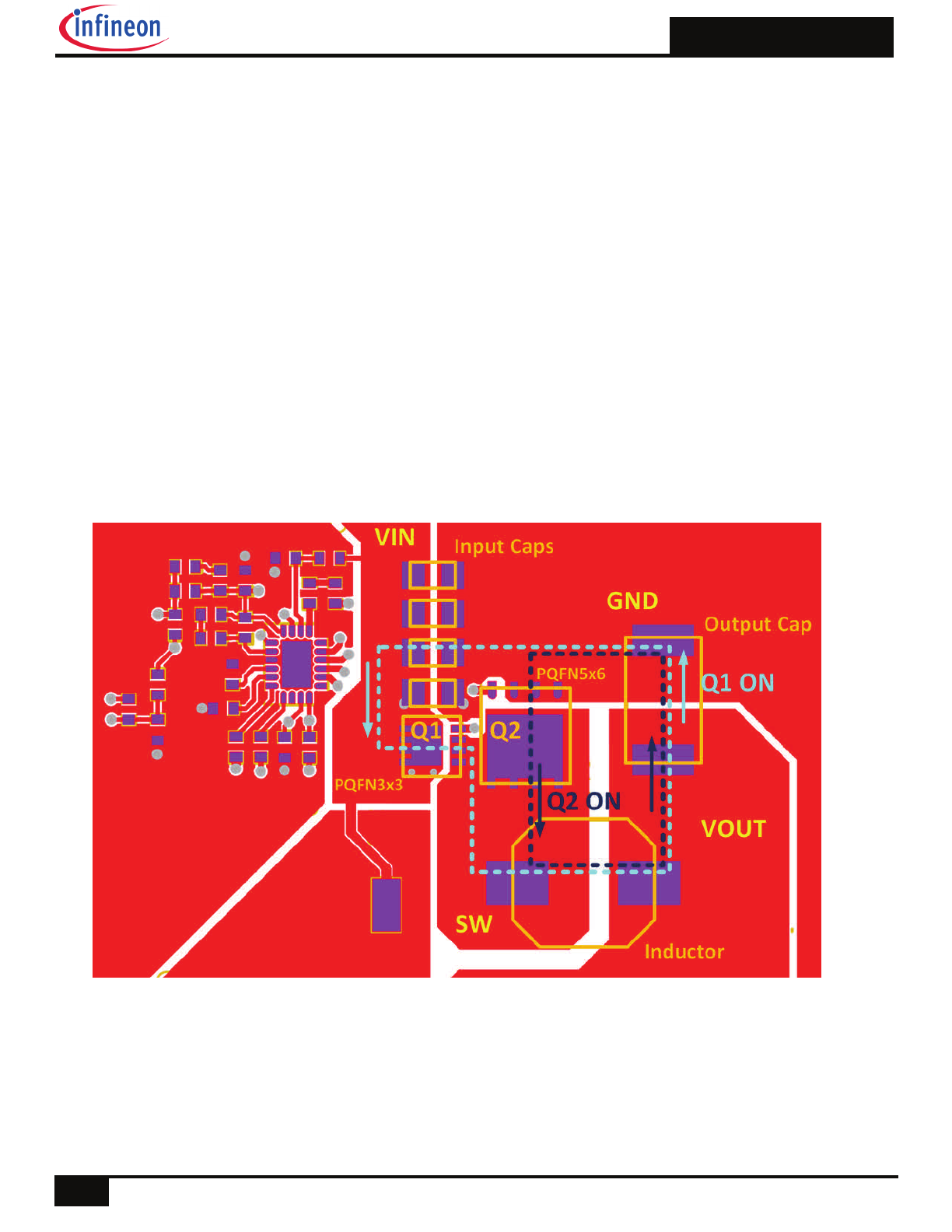

Placement and Layout Guidelines

The typical application topology for this product is the synchronous buck converter. These converters operate at high

frequencies (typically around 400 kHz). During turn-on and turn-off switching cycles, the high di/dt currents circulating in

the parasitic elements of the circuit induce high voltage ringing which may exceed the device rating and lead to undesir-

able effects. One of the major contributors to the increase in parasitics is the PCB power circuit inductance.

This section introduces a simple guideline that mitigates the effect of these parasitics on the performance of the circuit

and provides reliable operation of the devices.

To reduce high frequency switching noise and the effects of Electromagnetic Interference (EMI) when the control

MOSFET (Q1) is turned on, the layout shown in Figure 19 is recommended. The input bypass capacitors, control

MOSFET and output capacitors are placed in a tight loop to minimize parasitic inductance which in turn lowers the am-

plitude of the switch node ringing, and minimizes exposure of the MOSFETs to repetitive avalanche conditions.

When the synchronous MOSFET (Q2) is turned on, high average DC current flows through the path indicated in Figure

19. Therefore, the Q2 turn-on path should be laid out with a tight loop and wide traces at both ends of the inductor to

minimize loop resistance.

IRFHM8337TRPbF

8

2016-2-23

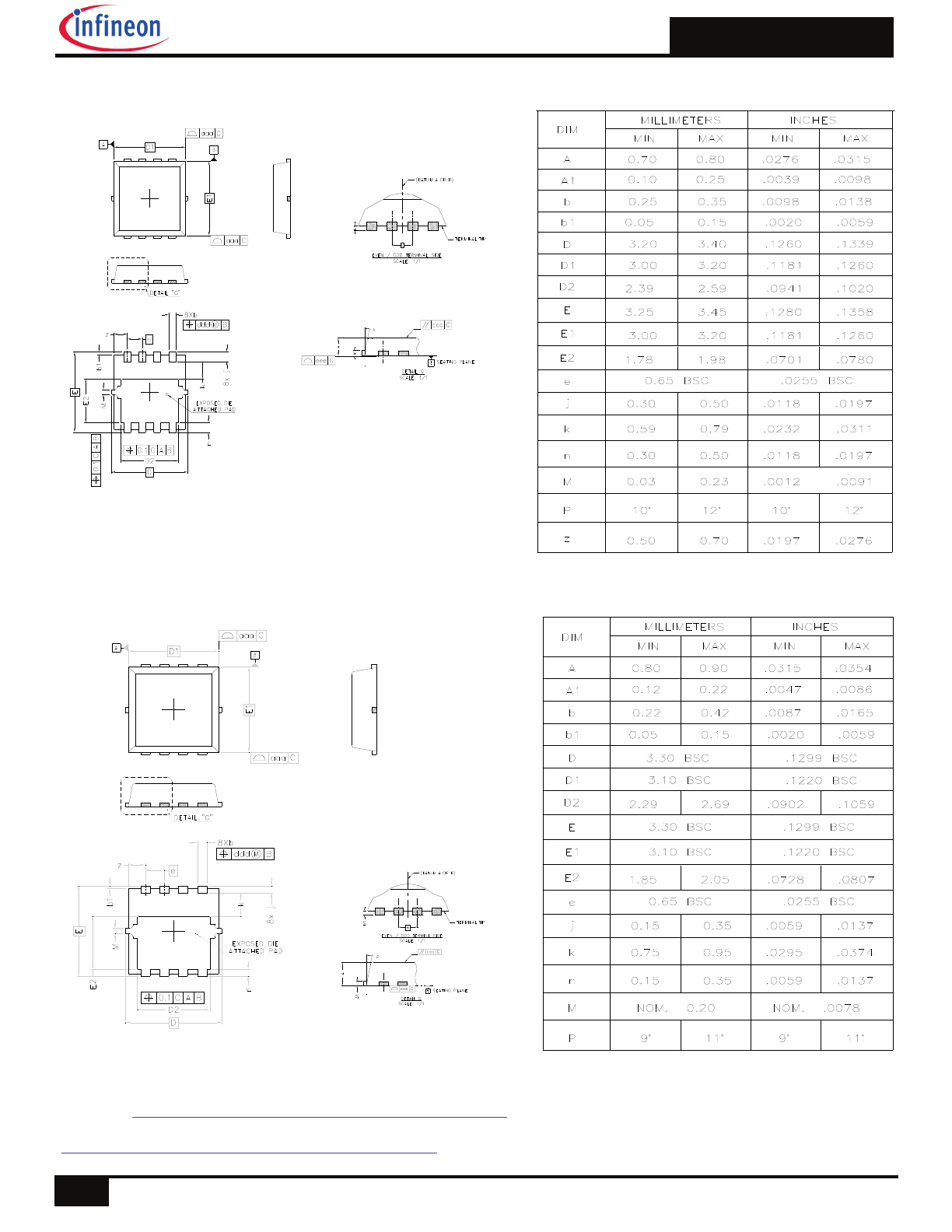

For more information on board mounting, including footprint and stencil recommendation, please refer to application note

AN-1136:

http://www.irf.com/technical-info/appnotes/an-1136.pdf

For more information on package inspection techniques, please refer to application note AN-1154:

http://www.irf.com/technical-info/appnotes/an-1154.pdf

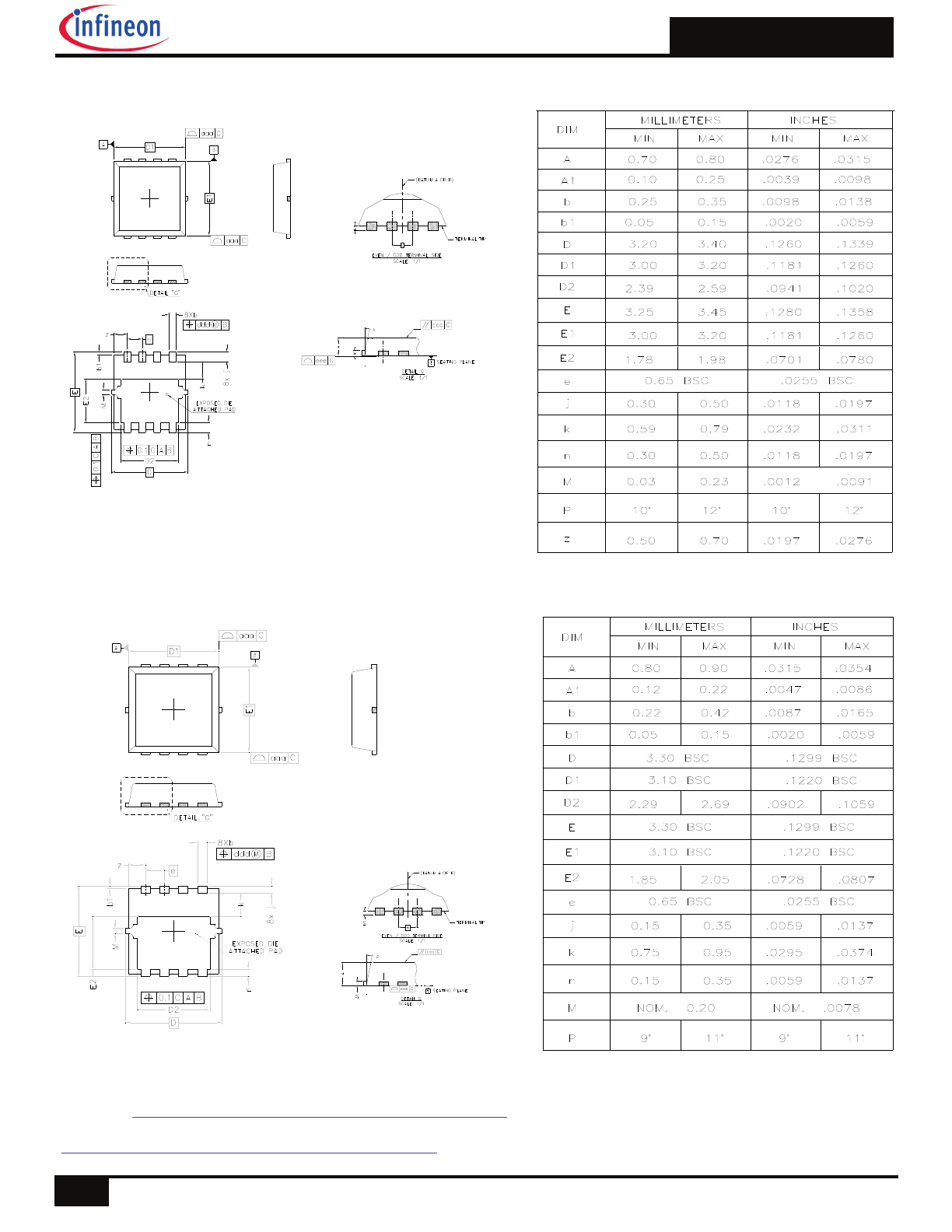

PQFN 3.3 x 3.3 Outline “C” Package Details

PQFN 3.3 x 3.3 Outline “G” Package Details

5

8

7

6

#1

3

2

4

#1

2

3

4

8

7

6

5

5

8

7

6

1

3

2

4

1

2

3

4

8

7

6

5

IRFHM8337TRPbF

9

2016-2-23

Note: For the most current drawing please refer to IR website at

http://www.irf.com/package/

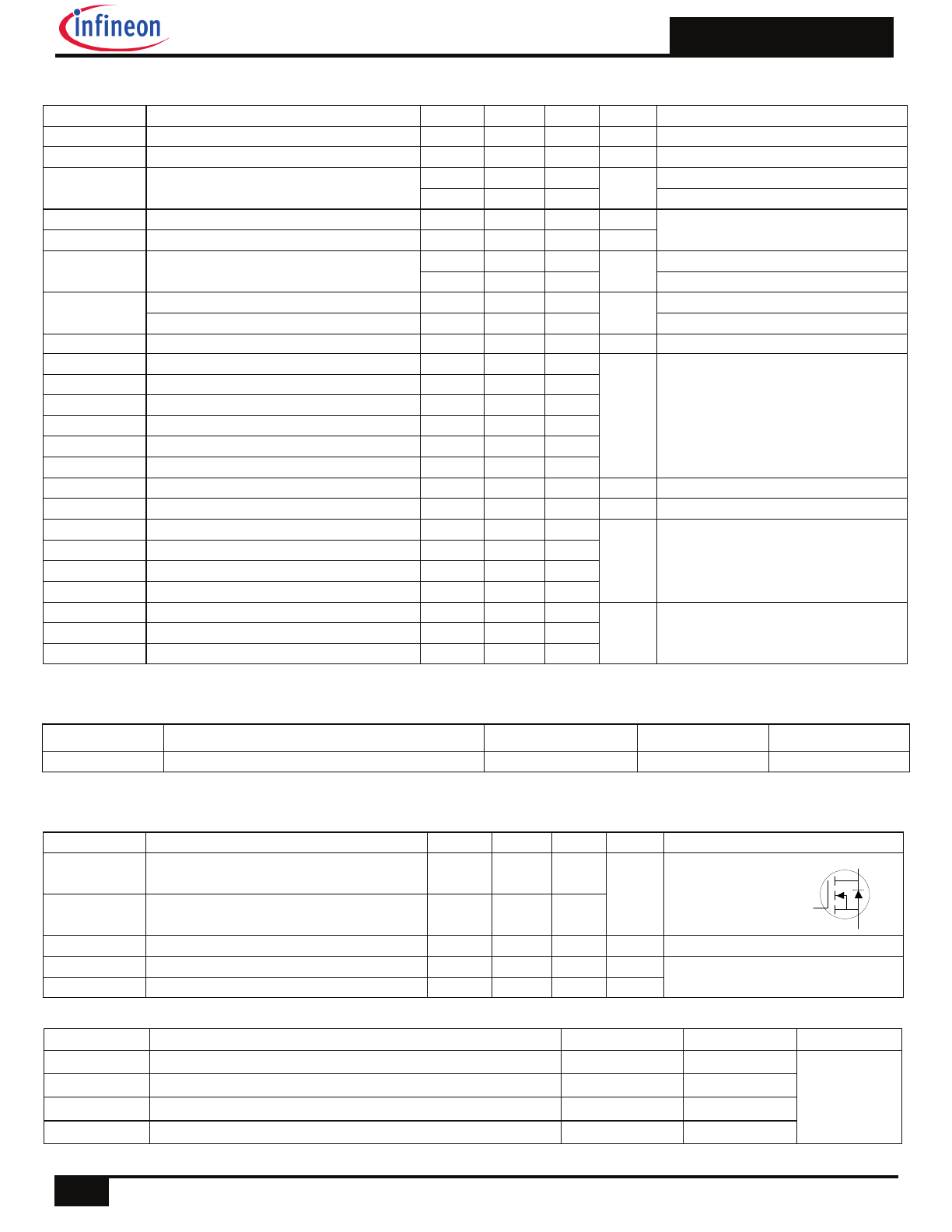

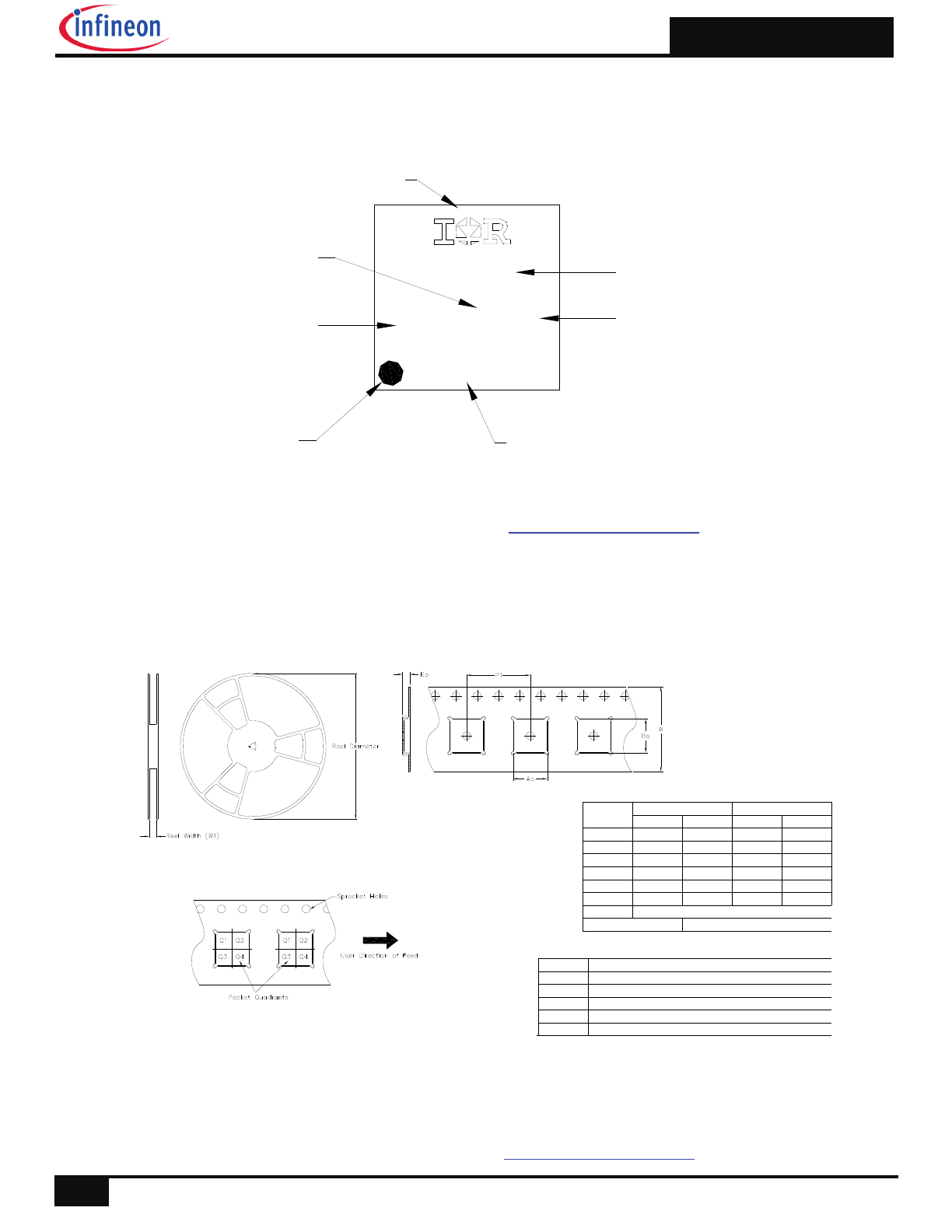

PQFN 3.3 x 3.3 Tape and Reel

Bo

W

P1

Ao

Ko

CODE

TAPE DIMENSIONS

REEL DIMENSIONS

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Dimension design to accommodate the component width

Dimension design to accommodate the component lenght

Dimension design to accommodate the component thickness

Pitch between successive cavity centers

Overall width of the carrier tape

Bo

W

P1

Ao

Ko

DIMENSION (MM)

CODE

MIN

MAX

DIMENSION (INCH)

MIN

MAX

3.50

3.70

.138

.146

1.10

1.30

7.90

8.10

.043

.051

11.80

12.20

.311

.319

12.30

12.50

.465

.480

.484

.492

3.50

3.70

.138

.146

DESCRIPTION

W1

Qty

4000

Reel Diameter

13 Inches

Note: For the most current drawing please refer to IR website at

http://www.irf.com/package/

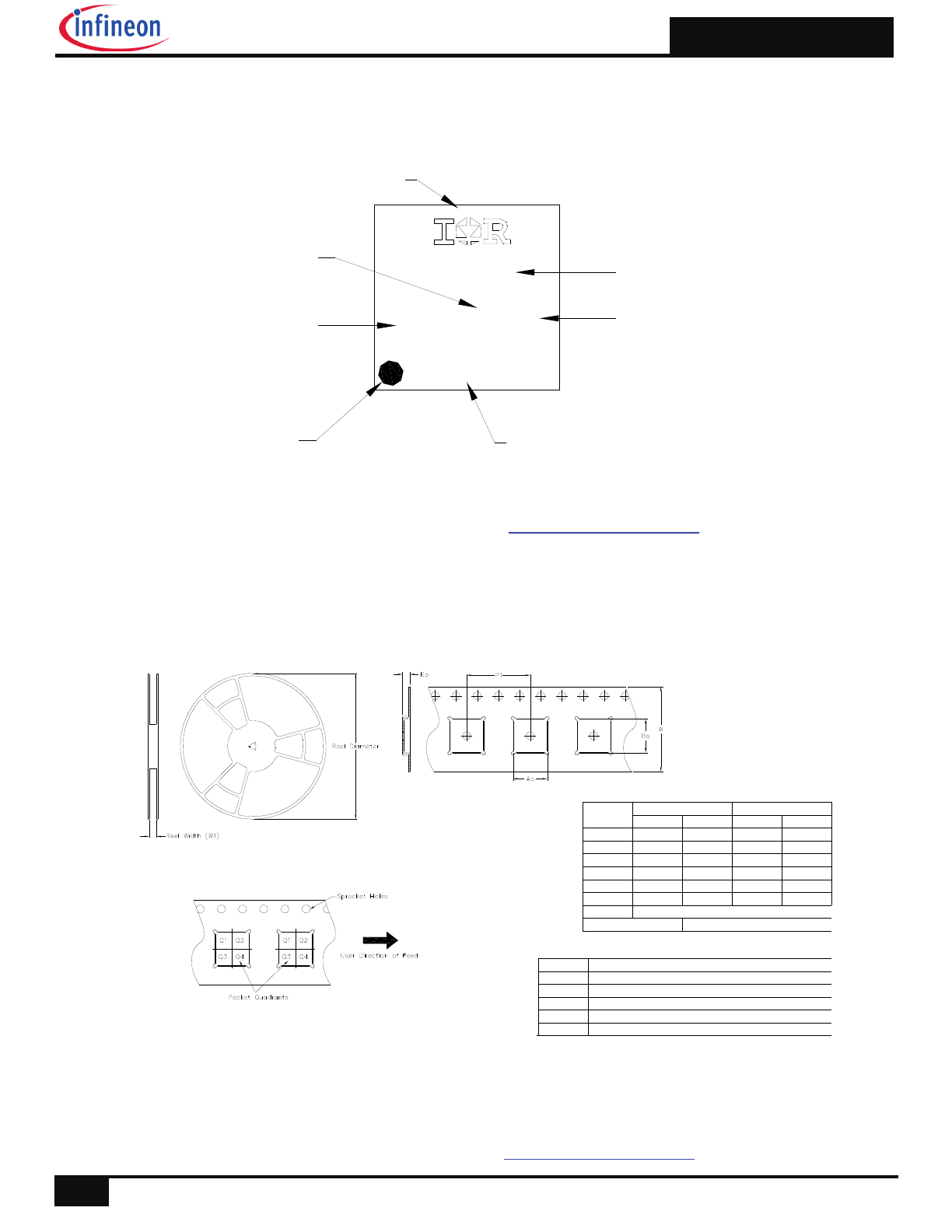

PQFN 3.3 x 3.3 Part Marking

XXXX

?YWW?

XXXXX

INTERNATIONAL

RECTIFIER LOGO

PART NUMBER

MARKING CODE

(Per Marking Spec)

ASSEMBLY

SITE CODE

(Per SCOP 200-002)

DATE CODE

LOT CODE

(Eng Mode - Min last 4 digits of EATI#)

(Prod Mode - 4 digits of SPN code)

PIN 1

IDENTIFIER

IRFHM8337TRPbF

10

2016-2-23

†

Qualification standards can be found at International Rectifier’s web site:

http://www.irf.com/product-info/reliability/

†† Higher qualification ratings may be available should the user have such requirements.

Please contact your International Rectifier sales representative for further information:

http://www.irf.com/whoto-call/salesrep/

††† Applicable version of JEDEC standard at the time of product release.

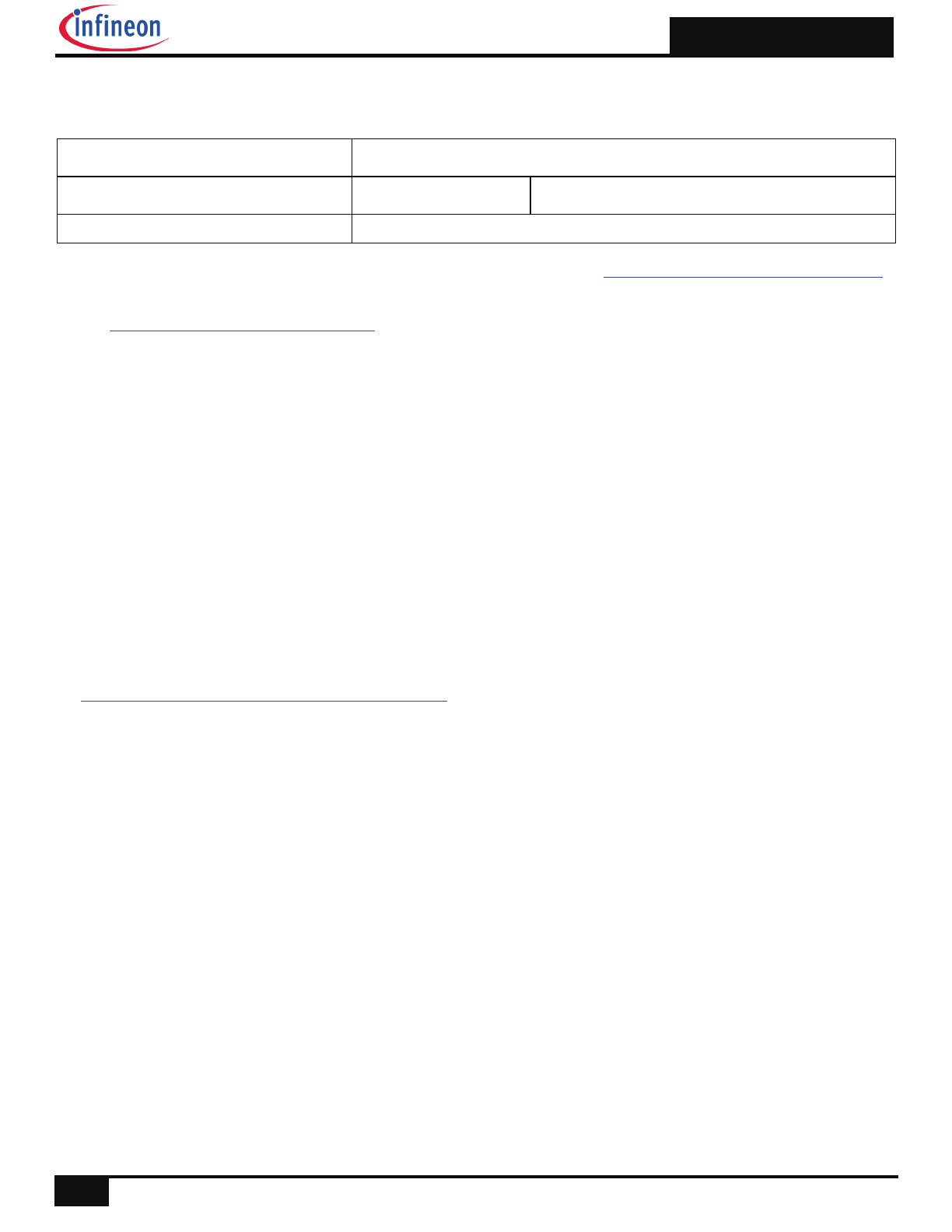

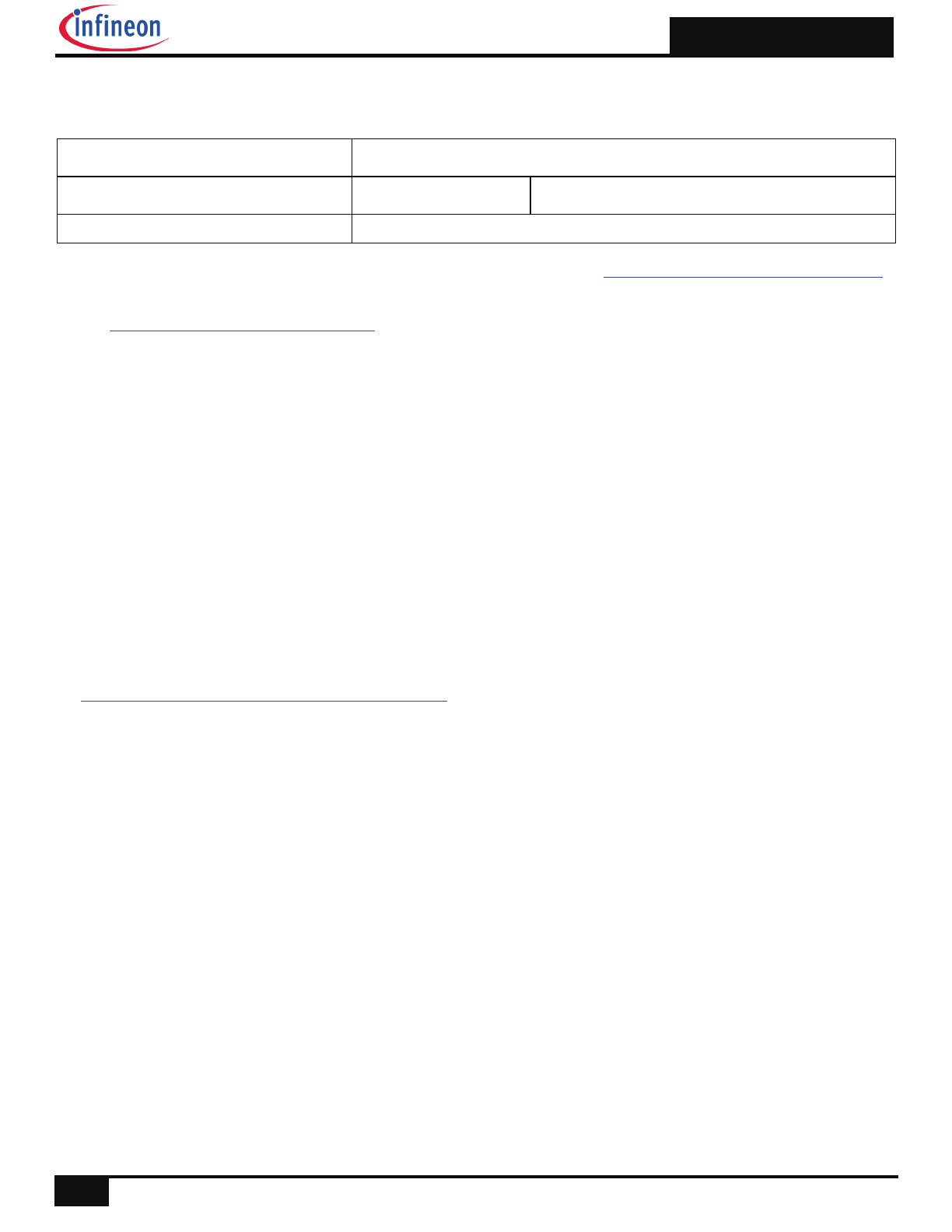

Qualification Information

†

Qualification Level

Moisture Sensitivity Level

PQFN 3.3mm x 3.3mm

MSL1

(per JEDEC J-STD-020D

†††

)

RoHS Compliant

Yes

Consumer

††

(per JEDEC JESD47F guidelines)

Notes:

Repetitive rating; pulse width limited by max. junction temperature.

Starting T

J

= 25°C, L = 0.297mH, R

G

= 50

, I

AS

= 9.4A.

Pulse width

400µs; duty cycle 2%.

R

is measured at TJ of approximately 90°C.

When mounted on 1 inch square PCB (FR-4). Please refer to AN-994 for more details:

http://www.irf.com/technical-info/appnotes/an-994.pdf

Calculated continuous current based on maximum allowable junction temperature.

Current limited to 18A by source bonding technology.

Pulse drain current is limited to 72A by source bonding technology.

IRFHM8337TRPbF

HEXFET

®

Power MOSFET

Base part number

Package Type

Standard Pack

Form

Quantity

IRFHM8337PbF

PQFN 3.3mm x 3.3mm

Tape and Reel

4000

IRFHM8337TRPbF

Orderable Part Number

V

DSS

30

V

R

DS(on)

max

(@ V

GS

= 10V)

12.4

(@ V

GS

= 4.5V)

17.9

Qg

(typical)

5.4

nC

I

D

(@T

C

= 25°C)

18 A

m

PQFN 3.3 x 3.3 mm

Features

Benefits

Low Thermal Resistance to PCB (< 5.0°C/W)

Enable better Thermal Dissipation

Low Profile (<1.05 mm)

results in Increased Power Density

Industry-Standard Pinout

Multi-Vendor Compatibility

Compatible with Existing Surface Mount Techniques

Easier Manufacturing

RoHS Compliant, Halogen-Free

Environmentally Friendlier

MSL1,Consumer Qualification

Increased Reliability

Notes through are on page 8

Absolute Maximum Ratings

Parameter Max.

Units

V

GS

Gate-to-Source Voltage

± 20

V

I

D

@ T

A

= 25°C

Continuous Drain Current, V

GS

@ 10V

12

A

I

D

@ T

A

= 70°C

Continuous Drain Current, V

GS

@ 10V

9.4

I

DM

Pulsed Drain Current 94

I

D

@ T

C(Bottom)

= 25°C

Continuous Drain Current, V

GS

@ 10V

35

I

D

@ T

C(Bottom)

= 100°C

Continuous Drain Current, V

GS

@ 10V

22

I

D

@ T

C

= 25°C

Continuous Drain Current, V

GS

@ 10V

(Source Bonding Technology Limited)

18

P

D

@T

A

= 25°C

Power Dissipation 2.8

W

P

D

@T

C(Bottom)

= 25°C

Power Dissipation 25

Linear Derating Factor 0.02

W/°C

T

J

Operating Junction and

-55 to + 150

°C

T

STG

Storage Temperature Range

Applications

System/load switch,

Charge or discharge switch for battery protection

1

2016-2-23

IRFHM8337TRPbF

2

2016-2-23

Static @ T

J

= 25°C (unless otherwise specified)

Parameter Min.

Typ.

Max.

Units

Conditions

BV

DSS

Drain-to-Source Breakdown Voltage

30

–––

–––

V

V

GS

= 0V, I

D

= 250µA

BV

DSS

/

T

J

Breakdown Voltage Temp. Coefficient

–––

0.02

–––

V/°C Reference to 25°C, I

D

= 1mA

R

DS(on)

Static Drain-to-Source On-Resistance

––– 9.4 12.4

m

V

GS

= 10V, I

D

= 12A

––– 14.5 17.9

V

GS

= 4.5V, I

D

=9.4A

V

GS(th)

Gate Threshold Voltage

1.35

1.8

2.35

V

V

DS

= V

GS

, I

D

= 25µA

V

GS(th)

Gate Threshold Voltage Coefficient

–––

-6.2

––– mV/°C

I

DSS

Drain-to-Source Leakage Current

––– ––– 1.0

µA

V

DS

= 24V, V

GS

= 0V

––– ––– 150

V

DS

= 24V, V

GS

= 0V,T

J

= 125°C

I

GSS

Gate-to-Source Forward Leakage –––

–––

100

µA

V

GS

= 20V

Gate-to-Source Reverse Leakage

–––

–––

-100

V

GS

=-20 V

gfs Forward

Transconductance

17

–––

–––

S

V

DS

= 15V, I

D

= 9.4A

Q

g

Total Gate Charge

–––

5.4

8.1

Q

gs1

Pre-Vth Gate-to-Source Charge

–––

1.1

–––

V

DS

= 15V

Q

gs2

Post-Vth Gate-to-Source Charge

–––

0.7

–––

nC V

GS

= 4.5V

Q

gd

Gate-to-Drain Charge

–––

2.2

–––

I

D

= 9.4A

Q

godr

Gate Charge Overdrive

–––

1.5

–––

Q

sw

Switch Charge (Q

gs2

+ Q

gd

) –––

2.9

–––

Q

oss

Output Charge

–––

3.8

–––

nC V

DS

= 16V, V

GS

= 0V

R

G

Gate Resistance

–––

2.0

–––

t

d(on)

Turn-On Delay Time

–––

9.0

–––

V

DD

= 15V, V

GS

= 4.5V

t

r

Rise Time

–––

11

–––

ns I

D

= 9.4A

t

d(off)

Turn-Off Delay Time

–––

9.9

–––

R

G

= 1.3

t

f

Fall Time

–––

5.6

–––

C

iss

Input Capacitance

–––

755

–––

V

GS

= 0V

C

oss

Output Capacitance

–––

171

–––

pF V

DS

= 15V

C

rss

Reverse Transfer Capacitance

–––

83

–––

ƒ = 1.0MHz

Parameter Typ.

Max.

Units

R

JC

(Bottom) Junction-to-Case –––

5.0

R

JC

(Top)

Junction-to-Case –––

50

°C/W

R

JA

Junction-to-Ambient –––

45

R

JA

(<10s)

Junction-to-Ambient –––

31

Thermal Resistance

Diode Characteristics

Parameter

Min.

Typ.

Max. Units

Conditions

I

S

Continuous Source Current

–––

–––

18 MOSFET

symbol

(Body Diode)

showing the

I

SM

Pulsed Source Current

–––

–––

94

integral reverse

(Body Diode)

p-n junction diode.

V

SD

Diode Forward Voltage

–––

–––

1.0

V

T

J

= 25°C, I

S

= 9.4A, V

GS

= 0V

t

rr

Reverse Recovery Time

–––

20

30

ns

T

J

= 25°C, I

F

= 9.4A, V

DD

= 15V

Q

rr

Reverse Recovery Charge

–––

27

41

nC di/dt = 200A/µs

A

Avalanche Characteristics

Parameter Typ.

Max.

Units

E

AS

Single Pulse Avalanche Energy –––

13 mJ

D

S

G

IRFHM8337TRPbF

3

2016-2-23

Fig 1. Typical Output Characteristics

Fig 4. Normalized On-Resistance vs. Temperature

Fig 5. Typical Capacitance vs. Drain-to-Source Voltage

Fig 6. Typical Gate Charge vs. Gate-to-Source Voltage

Fig 3. Typical Transfer Characteristics

Fig 2. Typical Output Characteristics

0.1

1

10

100

VDS, Drain-to-Source Voltage (V)

0.1

1

10

100

1000

I D

,

D

ra

in

-t

o

-S

ou

rc

e

C

u

rr

en

t

(A

)

VGS

TOP 10V

5.0V

4.5V

3.5V

3.3V

3.0V

2.9V

BOTTOM

2.7V

60µs PULSE WIDTH

Tj = 25°C

2.7V

0.1

1

10

100

VDS, Drain-to-Source Voltage (V)

1

10

100

1000

I D

, D

ra

in

-t

o-

S

o

ur

ce

C

u

rr

en

t

(A

)

2.7V

60µs PULSE WIDTH

Tj = 150°C

VGS

TOP 10V

5.0V

4.5V

3.5V

3.3V

3.0V

2.9V

BOTTOM

2.7V

1

2

3

4

5

6

VGS, Gate-to-Source Voltage (V)

0.1

1

10

100

I D

, D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(A

)

TJ = 25°C

TJ = 150°C

VDS = 15V

60µs PULSE WIDTH

-60 -40 -20 0 20 40 60 80 100 120 140 160

TJ , Junction Temperature (°C)

0.6

0.8

1.0

1.2

1.4

1.6

1.8

R

D

S

(o

n)

,

D

ra

in

-t

o-

S

ou

rc

e

O

n

R

es

is

ta

nc

e

(

N

or

m

al

iz

ed

)

ID = 12A

VGS = 10V

1

10

100

VDS, Drain-to-Source Voltage (V)

10

100

1000

10000

C

, C

ap

ac

ita

nc

e

(p

F

)

VGS = 0V, f = 1 MHZ

Ciss = Cgs + Cgd, C ds SHORTED

Crss = Cgd

Coss = Cds + Cgd

Coss

Crss

Ciss

0

2

4

6

8

10

12

14

16

QG, Total Gate Charge (nC)

0.0

2.0

4.0

6.0

8.0

10.0

12.0

14.0

V

G

S

, G

at

e-

to

-S

ou

rc

e

V

ol

ta

ge

(

V

)

VDS= 24V

VDS= 15V

ID= 9.4A

IRFHM8337TRPbF

4

2016-2-23

Fig 8. Maximum Safe Operating Area

Fig 7. Typical Source-Drain Diode Forward Voltage

25

50

75

100

125

150

TA , Ambient Temperature (°C)

0

2

4

6

8

10

12

I D

,

D

ra

in

C

ur

re

nt

(

A

)

Fig 9. Maximum Drain Current vs. Ambient Temperature

1E-006

1E-005

0.0001

0.001

0.01

0.1

1

10

100

1000

t1 , Rectangular Pulse Duration (sec)

0.01

0.1

1

10

100

T

he

rma

l R

es

po

ns

e

(

Z

th

JA

)

°

C

/W

0.20

0.10

D = 0.50

0.02

0.01

0.05

SINGLE PULSE

( THERMAL RESPONSE )

Notes:

1. Duty Factor D = t1/t2

2. Peak Tj = P dm x Zthja + TA

-75 -50 -25

0

25

50

75 100 125 150

TJ , Temperature ( °C )

0.5

1.0

1.5

2.0

2.5

V

G

S

(t

h)

, G

at

e

T

hr

es

ho

ld

V

ol

ta

ge

(

V

)

ID = 25µA

Fig 10.

Threshold Voltage Vs. Temperature

Fig 11. Maximum Effective Transient Thermal Impedance, Junction-to-Case

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

VSD, Source-to-Drain Voltage (V)

0.1

1

10

100

1000

I S

D

, R

ev

er

se

D

ra

in

C

ur

re

nt

(

A

)

TJ = 25°C

TJ = 150°C

VGS = 0V

0

1

10

100

VDS, Drain-to-Source Voltage (V)

0.1

1

10

100

1000

I D

,

D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(

A

)

OPERATION IN THIS AREA

LIMITED BY R DS(on)

TA = 25°C

Tj = 150°C

Single Pulse

100µsec

1msec

10msec

IRFHM8337TRPbF

5

2016-2-23

25

50

75

100

125

150

Starting TJ , Junction Temperature (°C)

0

10

20

30

40

50

60

E

A

S

,

S

in

gl

e

P

ul

se

A

va

la

nc

he

E

ne

rg

y

(m

J)

ID

TOP 2.95A

3.63A

BOTTOM 9.40A

Fig 13. Maximum Avalanche Energy vs. Drain Current

Fig 14. Single avalanche event: pulse current vs. pulse width

2

4

6

8

10

12

14

16

18

20

VGS, Gate -to -Source Voltage (V)

5

10

15

20

25

30

35

R

D

S

(o

n)

,

D

ra

in

-t

o

-S

ou

rc

e

O

n

R

es

is

ta

nc

e

(m

)

ID = 12A

TJ = 25°C

TJ = 125°C

Fig 12. On– Resistance vs. Gate Voltage

1.0E-05

1.0E-04

1.0E-03

1.0E-02

1.0E-01

tav (sec)

0.01

0.1

1

10

100

A

va

la

nc

he

C

ur

re

nt

(

A

)

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming

j = 25°C and

Tstart = 125°C.

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming

Tj = 125°C and

Tstart =25°C (Single Pulse)

IRFHM8337TRPbF

6

2016-2-23

Fig 15. Peak Diode Recovery dv/dt Test Circuit for N-Channel HEXFET

®

Power MOSFETs

Fig 18. Gate Charge Test Circuit

Vds

Vgs

Id

Vgs(th)

Qgs1 Qgs2

Qgd

Qgodr

Fig 19. Gate Charge Waveform

Fig 17a. Switching Time Test Circuit

Fig 17b. Switching Time Waveforms

Fig 16a. Unclamped Inductive Test Circuit

R G

I

AS

0.01

tp

D.U.T

L

VDS

+

- VDD

DRIVER

A

15V

20V

tp

V

(BR)DSS

I

AS

Fig 16b. Unclamped Inductive Waveforms

IRFHM8337TRPbF

7

2016-2-23

Placement and Layout Guidelines

The typical application topology for this product is the synchronous buck converter. These converters operate at high

frequencies (typically around 400 kHz). During turn-on and turn-off switching cycles, the high di/dt currents circulating in

the parasitic elements of the circuit induce high voltage ringing which may exceed the device rating and lead to undesir-

able effects. One of the major contributors to the increase in parasitics is the PCB power circuit inductance.

This section introduces a simple guideline that mitigates the effect of these parasitics on the performance of the circuit

and provides reliable operation of the devices.

To reduce high frequency switching noise and the effects of Electromagnetic Interference (EMI) when the control

MOSFET (Q1) is turned on, the layout shown in Figure 19 is recommended. The input bypass capacitors, control

MOSFET and output capacitors are placed in a tight loop to minimize parasitic inductance which in turn lowers the am-

plitude of the switch node ringing, and minimizes exposure of the MOSFETs to repetitive avalanche conditions.

When the synchronous MOSFET (Q2) is turned on, high average DC current flows through the path indicated in Figure

19. Therefore, the Q2 turn-on path should be laid out with a tight loop and wide traces at both ends of the inductor to

minimize loop resistance.

IRFHM8337TRPbF

8

2016-2-23

For more information on board mounting, including footprint and stencil recommendation, please refer to application note

AN-1136:

http://www.irf.com/technical-info/appnotes/an-1136.pdf

For more information on package inspection techniques, please refer to application note AN-1154:

http://www.irf.com/technical-info/appnotes/an-1154.pdf

PQFN 3.3 x 3.3 Outline “C” Package Details

PQFN 3.3 x 3.3 Outline “G” Package Details

5

8

7

6

#1

3

2

4

#1

2

3

4

8

7

6

5

5

8

7

6

1

3

2

4

1

2

3

4

8

7

6

5

IRFHM8337TRPbF

9

2016-2-23

Note: For the most current drawing please refer to IR website at

http://www.irf.com/package/

PQFN 3.3 x 3.3 Tape and Reel

Bo

W

P1

Ao

Ko

CODE

TAPE DIMENSIONS

REEL DIMENSIONS

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Dimension design to accommodate the component width

Dimension design to accommodate the component lenght

Dimension design to accommodate the component thickness

Pitch between successive cavity centers

Overall width of the carrier tape

Bo

W

P1

Ao

Ko

DIMENSION (MM)

CODE

MIN

MAX

DIMENSION (INCH)

MIN

MAX

3.50

3.70

.138

.146

1.10

1.30

7.90

8.10

.043

.051

11.80

12.20

.311

.319

12.30

12.50

.465

.480

.484

.492

3.50

3.70

.138

.146

DESCRIPTION

W1

Qty

4000

Reel Diameter

13 Inches

Note: For the most current drawing please refer to IR website at

http://www.irf.com/package/

PQFN 3.3 x 3.3 Part Marking

XXXX

?YWW?

XXXXX

INTERNATIONAL

RECTIFIER LOGO

PART NUMBER

MARKING CODE

(Per Marking Spec)

ASSEMBLY

SITE CODE

(Per SCOP 200-002)

DATE CODE

LOT CODE

(Eng Mode - Min last 4 digits of EATI#)

(Prod Mode - 4 digits of SPN code)

PIN 1

IDENTIFIER

IRFHM8337TRPbF

10

2016-2-23

†

Qualification standards can be found at International Rectifier’s web site:

http://www.irf.com/product-info/reliability/

†† Higher qualification ratings may be available should the user have such requirements.

Please contact your International Rectifier sales representative for further information:

http://www.irf.com/whoto-call/salesrep/

††† Applicable version of JEDEC standard at the time of product release.

Qualification Information

†

Qualification Level

Moisture Sensitivity Level

PQFN 3.3mm x 3.3mm

MSL1

(per JEDEC J-STD-020D

†††

)

RoHS Compliant

Yes

Consumer

††

(per JEDEC JESD47F guidelines)

Notes:

Repetitive rating; pulse width limited by max. junction temperature.

Starting T

J

= 25°C, L = 0.297mH, R

G

= 50

, I

AS

= 9.4A.

Pulse width

400µs; duty cycle 2%.

R

is measured at TJ of approximately 90°C.

When mounted on 1 inch square PCB (FR-4). Please refer to AN-994 for more details:

http://www.irf.com/technical-info/appnotes/an-994.pdf

Calculated continuous current based on maximum allowable junction temperature.

Current limited to 18A by source bonding technology.

Pulse drain current is limited to 72A by source bonding technology.