DirectFET

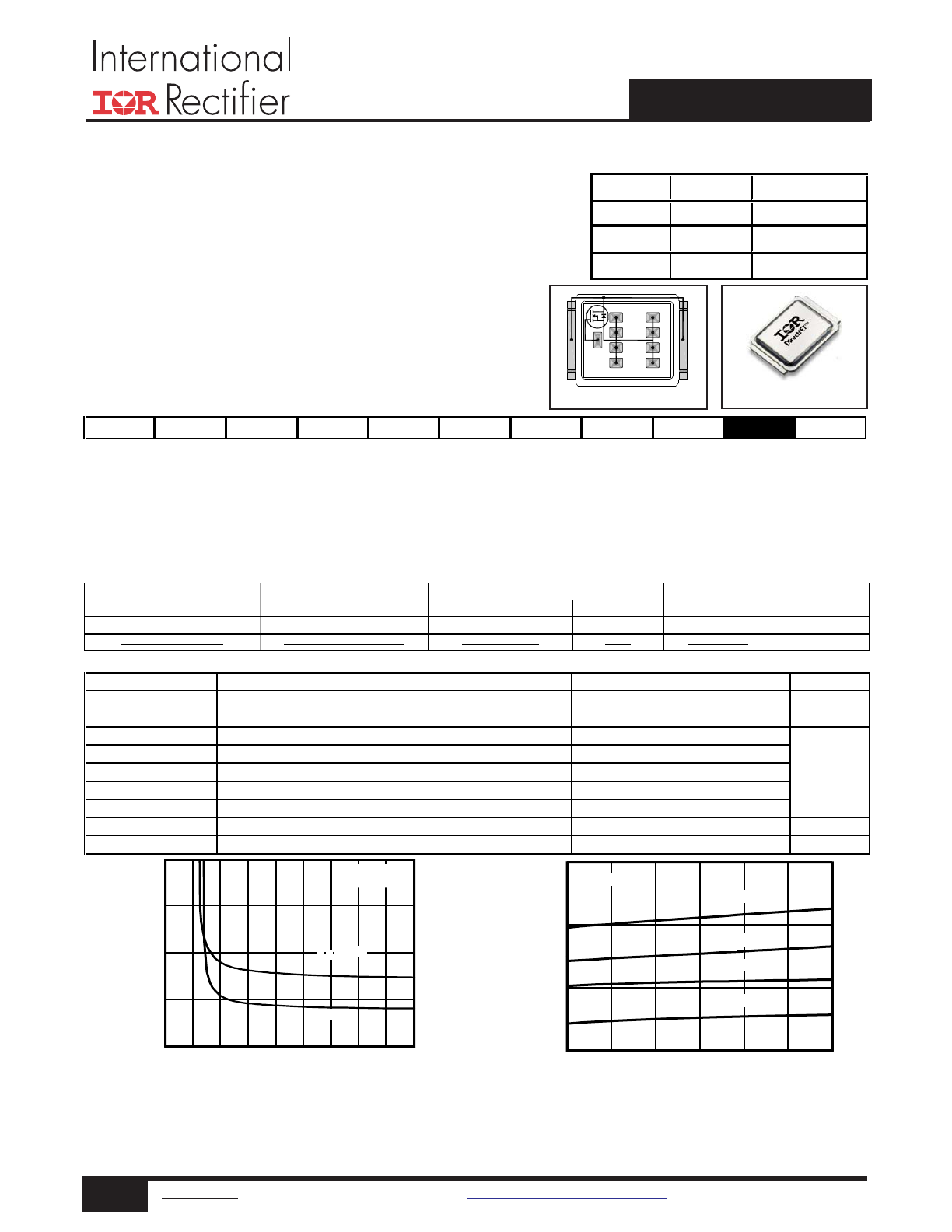

Power MOSFET

Typical values (unless otherwise specified)

DirectFET

ISOMETRIC

L8

Applicable DirectFET Outline and Substrate Outline

l

RoHS Compliant, Halogen Free

l

Lead-Free (Qualified up to 260°C Reflow)

l

Ideal for High Performance Isolated Converter

Primary Switch Socket

l

Optimized for Synchronous Rectification

l

Low Conduction Losses

l

High Cdv/dt Immunity

l

Low Profile (<0.7mm)

l

Dual Sided Cooling Compatible

l

Compatible with existing Surface Mount Techniques

l

Industrial Qualified

Description

The IRF7759L2TR/TR1PbF combines the latest HEXFET® Power MOSFET Silicon technology with the advanced DirectFET

TM

packaging to achieve the

lowest on-state resistance in a package that has a footprint smaller than a D

2

PAK and only 0.7 mm profile. The DirectFET package is compatible with existing

layout geometries used in power applications, PCB assembly equipment and vapor phase, infra-red or convection soldering techniques, when application

note AN-1035 is followed regarding the manufacturing methods and processes. The DirectFET package allows dual sided cooling to maximize thermal transfer

in power systems.

The IRF7759L2TR/TR1PbF is optimized for high frequency switching and synchronous rectification applications. The reduced total losses in the device

coupled with the high level of thermal performance enables high efficiency and low temperatures, which are key for system reliability improvements, and

makes this device ideal for high performance power converters.

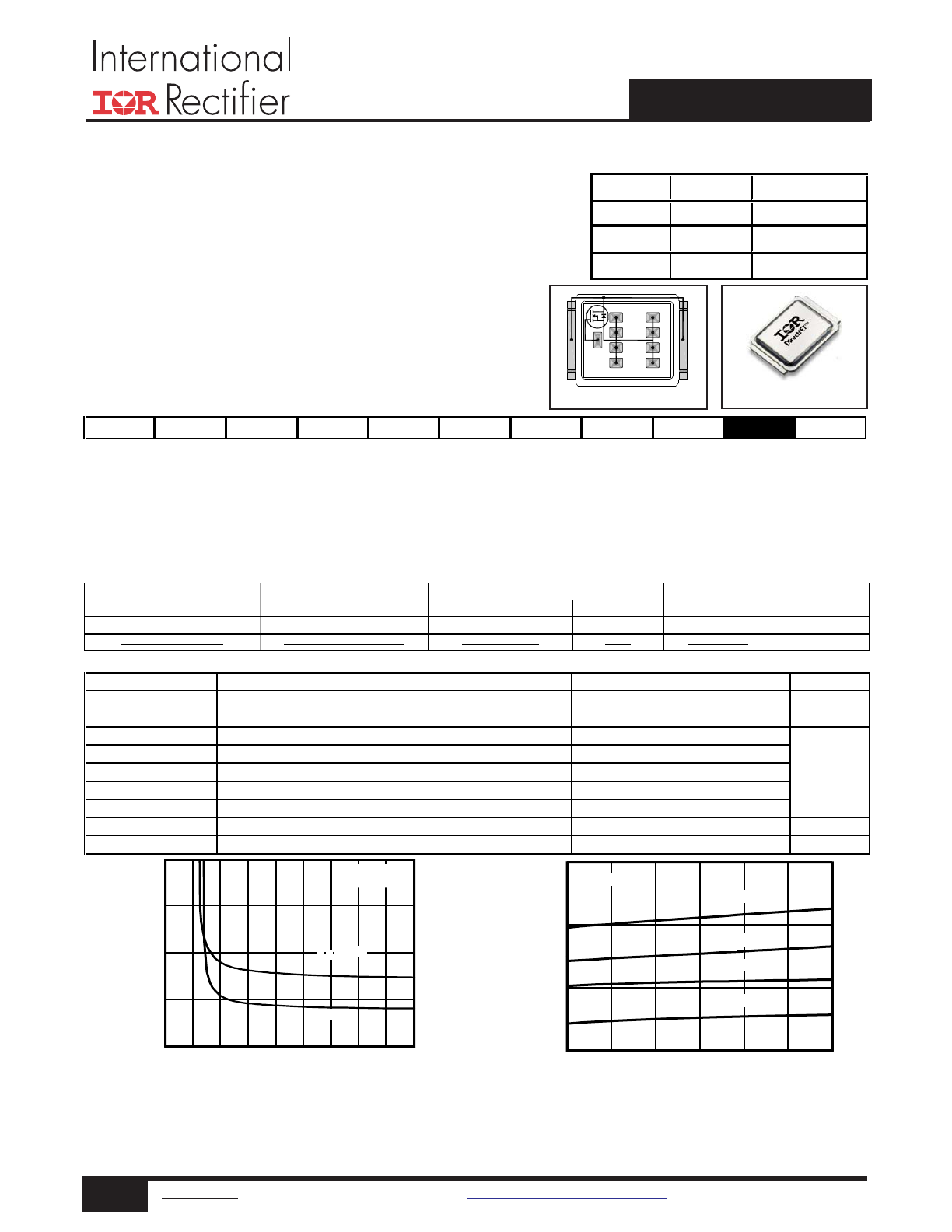

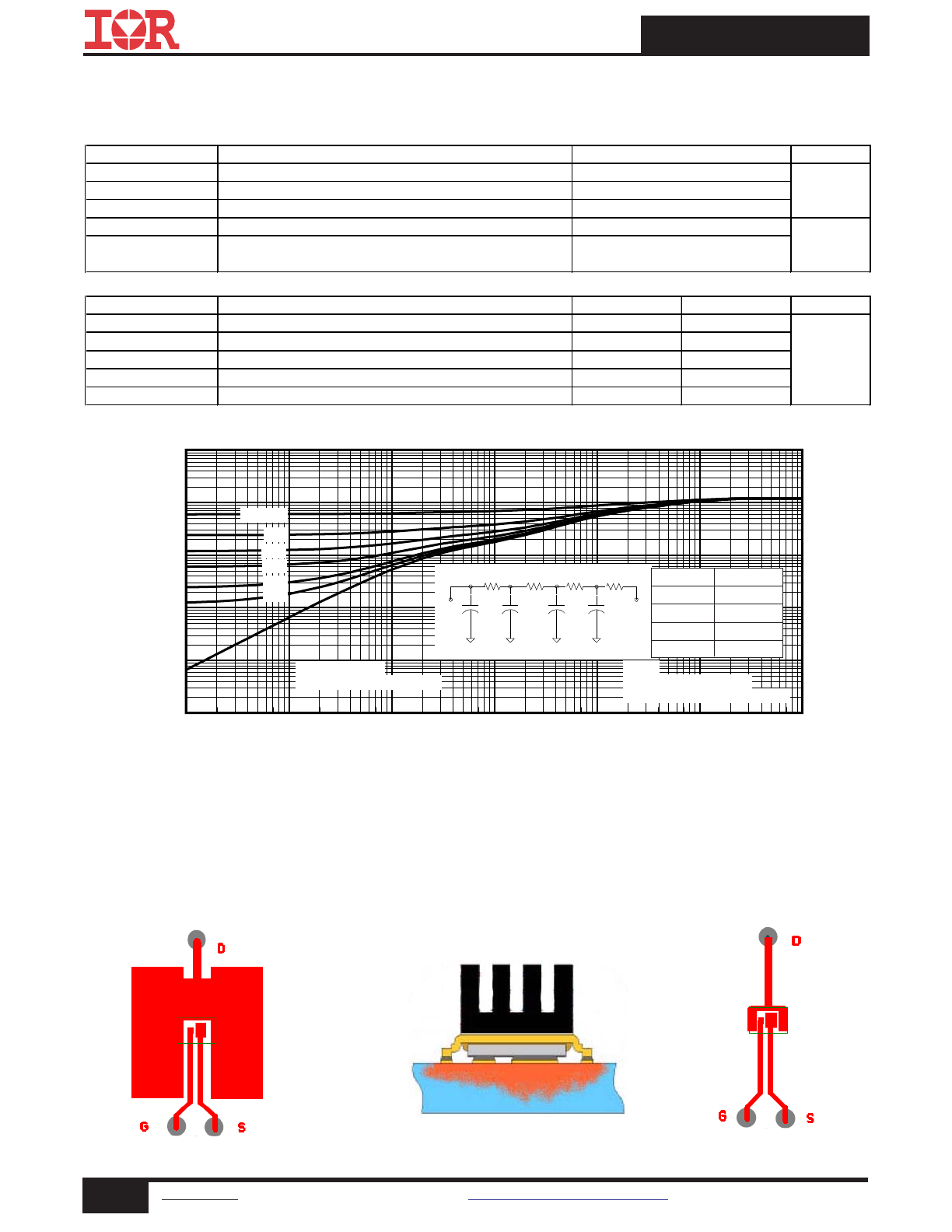

Fig 1. Typical On-Resistance vs. Gate Voltage

Click on this section to link to the appropriate technical paper.

Click on this section to link to the DirectFET Website.

Surface mounted on 1 in. square Cu board, steady state.

T

C

measured with thermocouple mounted to top (Drain) of part.

Repetitive rating; pulse width limited by max. junction temperature.

Starting T

J

= 25°C, L = 0.056mH, R

G

= 25

Ω, I

AS

= 96A.

Notes:

Fig 2. Typical On-Resistance vs. Drain Current

SB

SC

M2 M4

L4

L6

L8

D

S

G

D

S

S

S

S

S

S

S

Absolute Maximum Ratings

Parameter

Units

V

DS

Drain-to-Source Voltage

V

GS

Gate-to-Source Voltage

I

D

@ T

C

= 25°C

Continuous Drain Current, V

GS

@ 10V

(Silicon Limited)

f

I

D

@ T

C

= 100°C

Continuous Drain Current, V

GS

@ 10V

(Silicon Limited)

f

I

D

@ T

A

= 25°C

Continuous Drain Current, V

GS

@ 10V

(Silicon Limited)

e

I

D

@ T

C

= 25°C

Continuous Drain Current, V

GS

@ 10V

(Package Limited)

f

I

DM

Pulsed Drain Current

g

E

AS

Single Pulse Avalanche Energy

h

mJ

I

AR

Avalanche Current

g

A

A

V

96

375

257

Max.

113

26

640

±20

75

160

2

4

6

8

10

12

14

16

18

20

V GS, Gate -to -Source Voltage (V)

0

2

4

6

8

R

D

S

(o

n)

,

D

ra

in

-t

o

-S

ou

rc

e

O

n

R

es

is

ta

nc

e

(m

Ω

)

I D = 96A

T J = 25°C

T J = 125°C

15

30

45

60

75

90

105

ID, Drain Current (A)

1.65

1.75

1.85

1.95

T

yp

ic

al

R

D

S

(o

n)

( m

Ω

)

TA= 25°C

VGS = 8.0V

VGS = 7.0V

VGS = 10V

VGS = 15V

V

DSS

V

GS

R

DS(on)

75V min ±20V max 1.8mΩ@ 10V

Q

g tot

Q

gd

V

gs(th)

200nC

62nC

3.0V

IRF7759L2PbF

1

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

Form

Quantity

IRF7759L2TRPbF

DirectFET2 Large Can

Tape and Reel

4000

"TR" suffix

IRF7759L2TR1PbF

DirectFET2 Large Can

Tape and Reel

1000

"TR1" suffix EOL notice # 264

Note

Orderable part number

Package Type

Standard Pack

2

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

Notes:

Repetitive rating; pulse width limited by max. junction temperature.

Pulse width ≤ 400μs; duty cycle ≤ 2%.

Static @ T

J

= 25°C (unless otherwise specified)

Parameter

Min. Typ. Max. Units

BV

DSS

Drain-to-Source Breakdown Voltage

75

–––

–––

V

ΔΒV

DSS

/ΔT

J

Breakdown Voltage Temp. Coefficient

–––

0.02

–––

V/°C

R

DS(on)

Static Drain-to-Source On-Resistance

–––

1.8

2.3

m

Ω

V

GS(th)

Gate Threshold Voltage

2.0

3.0

4.0

V

ΔV

GS(th)

/

ΔT

J

Gate Threshold Voltage Coefficient

–––

-11

––– mV/°C

I

DSS

Drain-to-Source Leakage Current

–––

–––

20

–––

–––

250

I

GSS

Gate-to-Source Forward Leakage

–––

–––

100

Gate-to-Source Reverse Leakage

–––

–––

-100

gfs

Forward Transconductance

74

–––

–––

S

Q

g

Total Gate Charge

–––

200

300

Q

gs1

Pre-Vth Gate-to-Source Charge

–––

37

–––

Q

gs2

Post-Vth Gate-to-Source Charge

–––

11

–––

Q

gd

Gate-to-Drain Charge

–––

62

93

Q

godr

Gate Charge Overdrive

–––

91

–––

See Fig. 9

Q

sw

Switch Charge (Q

gs2

+ Q

gd

)

–––

73

–––

Q

oss

Output Charge

–––

60

–––

nC

R

G

Gate Resistance

–––

1.1

–––

Ω

t

d(on)

Turn-On Delay Time

–––

18

–––

t

r

Rise Time

–––

37

–––

t

d(off)

Turn-Off Delay Time

–––

80

–––

t

f

Fall Time

–––

33

–––

C

iss

Input Capacitance

–––

12222 –––

C

oss

Output Capacitance

–––

1465

–––

C

rss

Reverse Transfer Capacitance

–––

609

–––

C

oss

Output Capacitance

–––

7457

–––

C

oss

Output Capacitance

–––

955

–––

Diode Characteristics

Parameter

Min. Typ. Max. Units

I

S

Continuous Source Current

(Body Diode)

I

SM

Pulsed Source Current

(Body Diode)

g

V

SD

Diode Forward Voltage

–––

–––

1.3

V

t

rr

Reverse Recovery Time

–––

64

96

ns

Q

rr

Reverse Recovery Charge

–––

150

225

nC

pF

A

–––

–––

160

–––

–––

640

μA

nA

nC

ns

MOSFET symbol

R

G

=1.8

Ω

V

DS

= 25V

Conditions

V

GS

= 0V, V

DS

= 60V, f=1.0MHz

V

GS

= 0V, V

DS

= 1.0V, f=1.0MHz

V

DS

= 16V, V

GS

= 0V

V

DD

= 38V, V

GS

= 10Vi

V

GS

= 0V

ƒ = 1.0MHz

I

D

= 96A

V

DS

= 75V, V

GS

= 0V

Conditions

V

GS

= 0V, I

D

= 250μA

Reference to 25°C, I

D

= 2mA

V

GS

= 10V, I

D

= 96A i

V

DS

= V

GS

, I

D

= 250μA

T

J

= 25°C, I

F

= 96A, V

DD

= 38V

di/dt = 100A/μs i

T

J

= 25°C, I

S

= 96A, V

GS

= 0V

i

showing the

integral reverse

p-n junction diode.

I

D

= 96A

V

DS

= 60V, V

GS

= 0V, T

J

= 125°C

V

GS

= 20V

V

GS

= -20V

V

GS

= 10V

V

DS

= 25V, I

D

= 96A

V

DS

= 38V

3

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

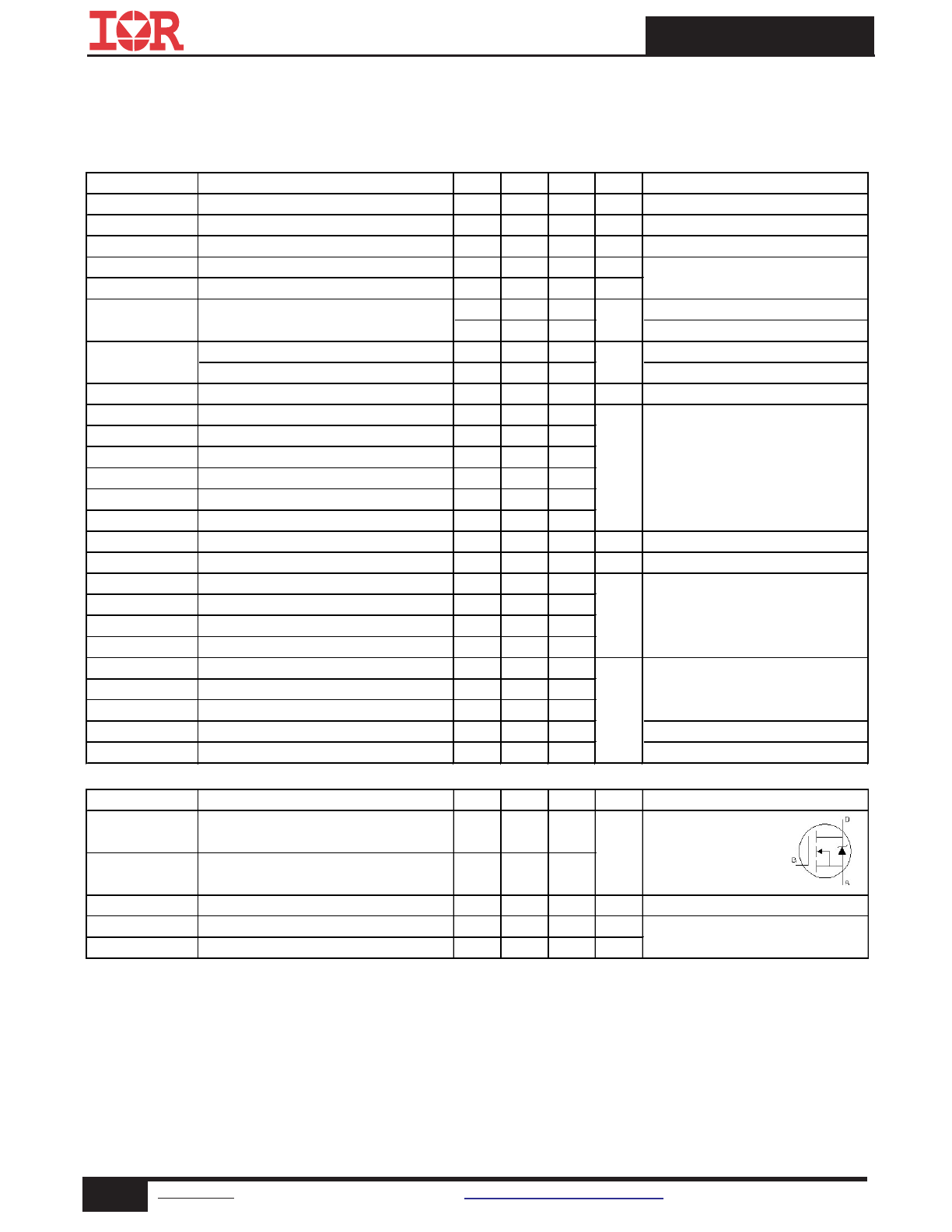

Fig 3. Maximum Effective Transient Thermal Impedance, Junction-to-Case

Surface mounted on 1 in. square Cu board, steady state.

T

C

measured with thermocouple incontact with top (Drain) of part.

Used double sided cooling, mounting pad with large heatsink.

Notes:

Mounted on minimum footprint full size board with metalized

back and with small clip heatsink.

R

θ

is measured at

T

J

of approximately 90°C.

Surface mounted on 1 in. square Cu

board (still air).

Mounted on minimum footprint full size board with metalized

back and with small clip heatsink. (still air)

1E-006

1E-005

0.0001

0.001

0.01

0.1

1

t1 , Rectangular Pulse Duration (sec)

0.0001

0.001

0.01

0.1

1

10

T

he

rm

al

R

es

po

ns

e

(

Z

th

JC

)

°

C

/W

0.20

0.10

D = 0.50

0.02

0.01

0.05

SINGLE PULSE

( THERMAL RESPONSE )

Notes:

1. Duty Factor D = t1/t2

2. Peak Tj = P dm x Zthjc + Tc

τ

J

τ

J

τ

1

τ

1

τ

2

τ

2

τ

3

τ

3

R

1

R

1

R

2

R

2

R

3

R

3

Ci i

/Ri

Ci=

τi/Ri

τ

τ

C

τ

4

τ

4

R

4

R

4

Ri (°C/W)

τi (sec)

0.10804 0.000171

0.61403 0.053914

0.45202 0.006099

0.00001 0.036168

Absolute Maximum Ratings

Parameter

Units

P

D

@T

C

= 25°C

Power Dissipation

f

P

D

@T

C

= 100°C

Power Dissipation

f

P

D

@T

A

= 25°C

Power Dissipation

c

T

P

Peak Soldering Temperature

T

J

Operating Junction and

T

STG

Storage Temperature Range

Thermal Resistance

Parameter

Typ.

Max.

Units

R

θJA

Junction-to-Ambient

e

–––

45

R

θJA

Junction-to-Ambient

j

12.5

–––

R

θJA

Junction-to-Ambient

k

20

–––

°C/W

R

θJ-Can

Junction-to-Can

fl

–––

1.2

R

θJ-PCB

Junction-to-PCB Mounted

–––

0.5

W

°C

270

-55 to + 175

Max.

3.3

125

63

4

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

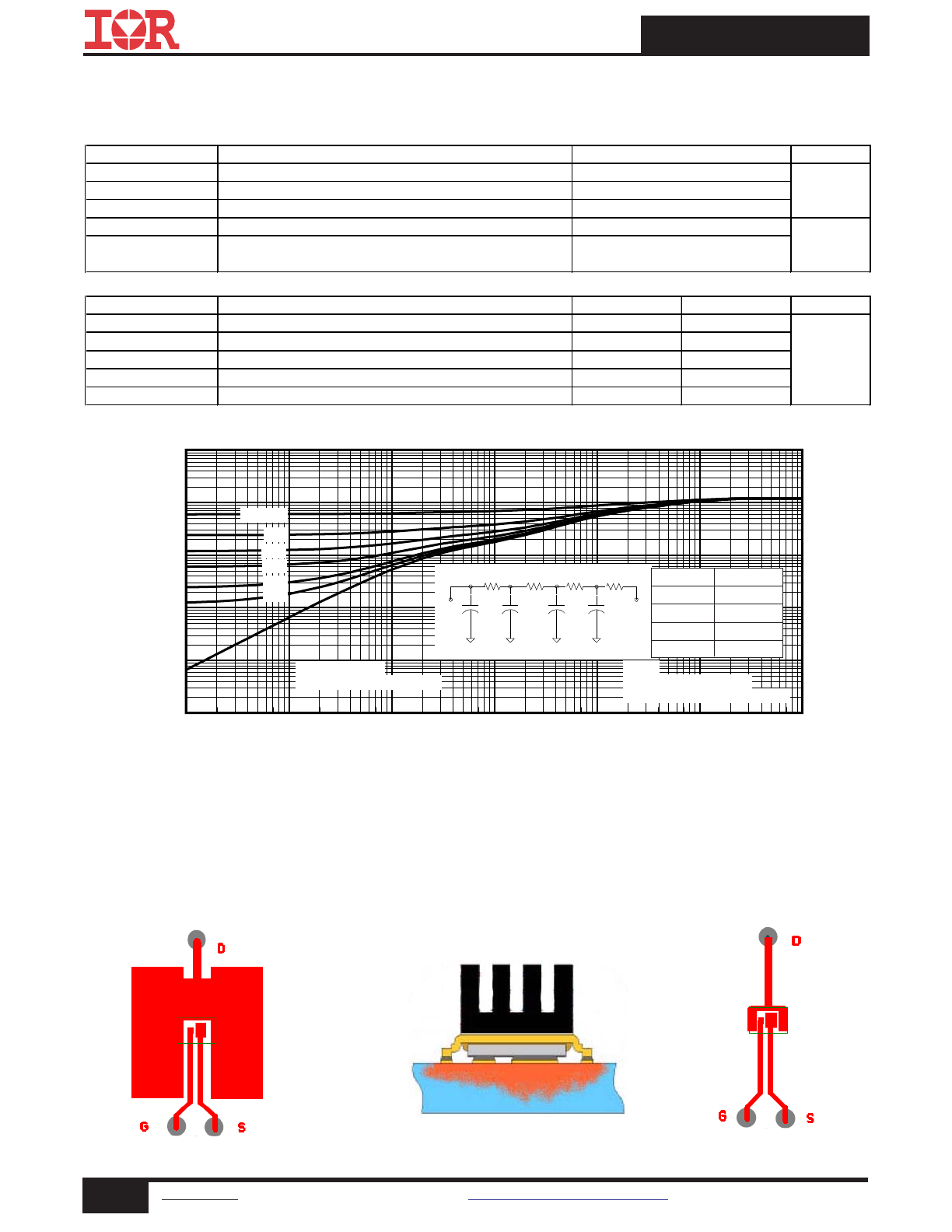

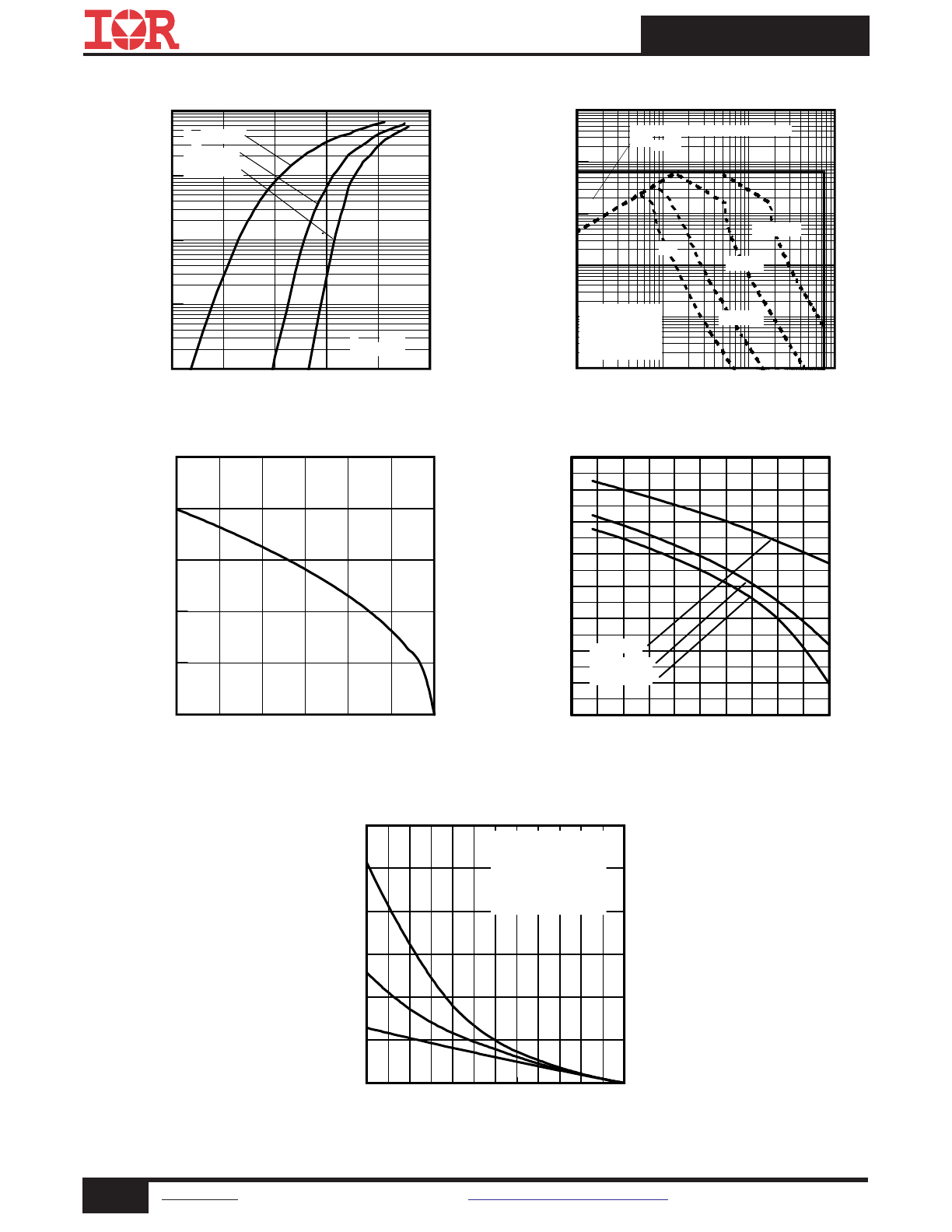

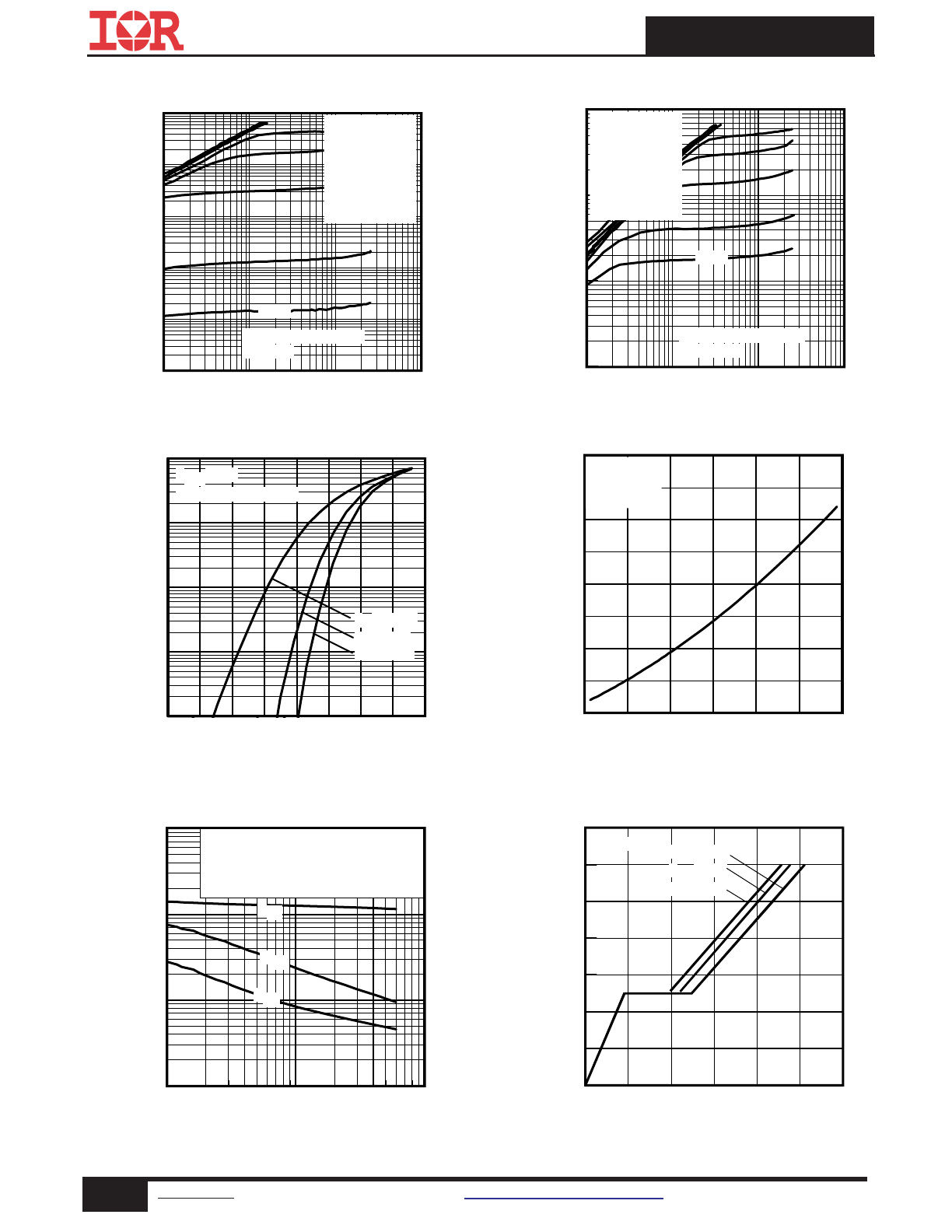

Fig 5. Typical Output Characteristics

Fig 4. Typical Output Characteristics

Fig 6. Typical Transfer Characteristics

Fig 7. Normalized On-Resistance vs. Temperature

Fig 8. Typical Capacitance vs.Drain-to-Source Voltage

Fig 9. Typical Total Gate Charge vs

Gate-to-Source Voltage

0.1

1

10

100

VDS, Drain-to-Source Voltage (V)

1

10

100

1000

I D

, D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(

A

)

3.75V

≤60μs

PULSE WIDTH

Tj = 175°C

VGS

TOP

15V

10V

7.00V

5.50V

5.00V

4.50V

4.00V

BOTTOM

3.75V

2

2.5

3

3.5

4

4.5

5

5.5

6

VGS, Gate-to-Source Voltage (V)

0.1

1

10

100

1000

I D

, D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(

A

)

TJ = 175°C

TJ = 25°C

TJ = -40°C

VDS = 25V

≤60μs PULSE WIDTH

-60

-20

20

60

100

140

180

TJ , Junction Temperature (°C)

0.5

1.0

1.5

2.0

2.5

R

D

S

(o

n)

,

D

ra

in

-t

o-

S

ou

rc

e

O

n

R

es

is

ta

nc

e

(

N

or

m

al

iz

ed

)

ID = 96A

VGS = 10V

1

10

100

VDS, Drain-to-Source Voltage (V)

100

1000

10000

100000

C

, C

ap

ac

ita

nc

e

(p

F

)

VGS = 0V, f = 1 MHZ

Ciss = Cgs + Cgd, C ds SHORTED

Crss = Cgd

Coss = Cds + Cgd

Coss

Crss

Ciss

0

50

100

150

200

250

300

QG, Total Gate Charge (nC)

0

2

4

6

8

10

12

14

V

G

S

, G

at

e-

to

-S

ou

rc

e

V

ol

ta

ge

(

V

)

VDS= 60V

VDS= 38V

VDS= 15V

ID= 96A

0.1

1

10

100

VDS, Drain-to-Source Voltage (V)

0.01

0.1

1

10

100

1000

I D

, D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(

A

)

VGS

TOP

15V

10V

7.00V

5.50V

5.00V

4.50V

4.00V

BOTTOM

3.75V

≤60μs

PULSE WIDTH

Tj = 25°C

3.75V

5

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

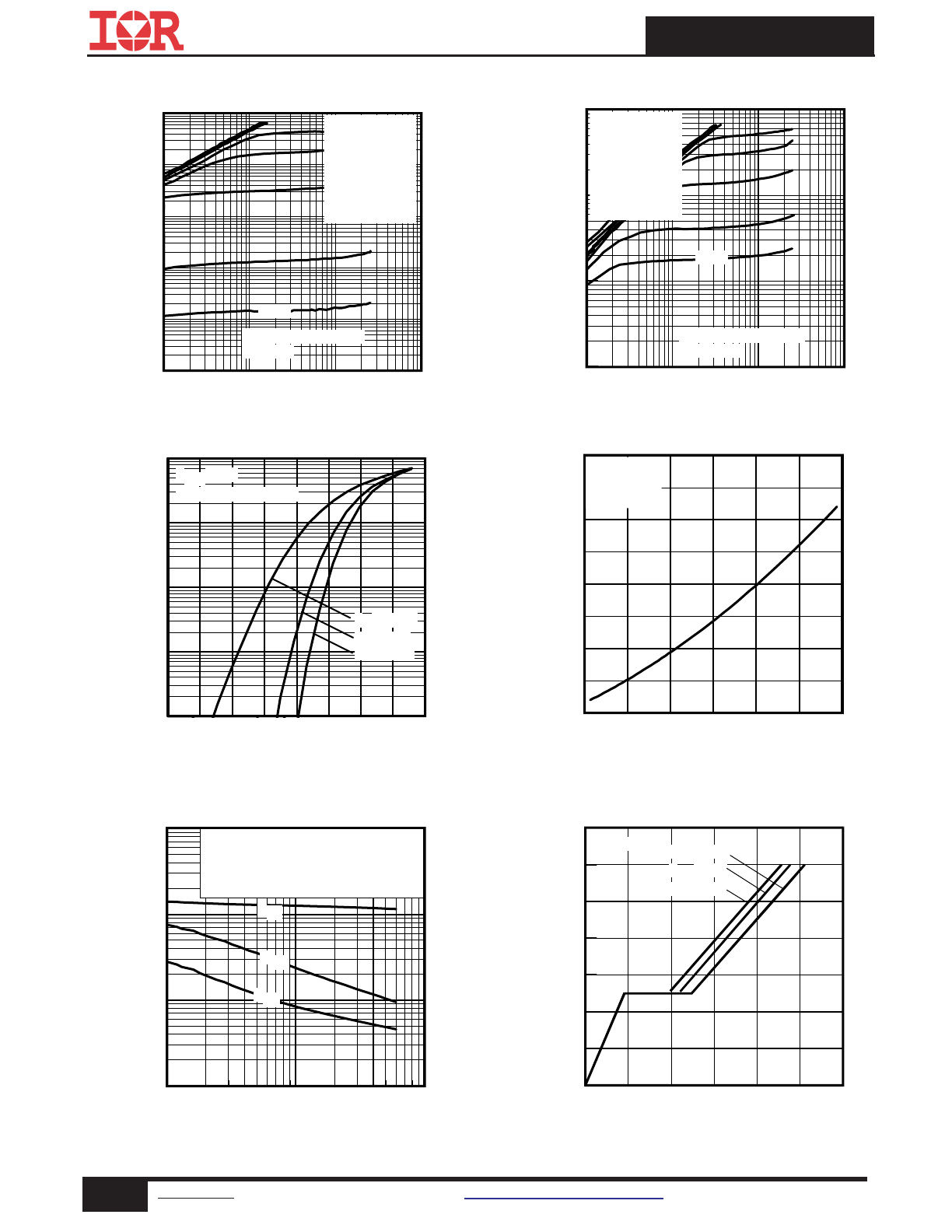

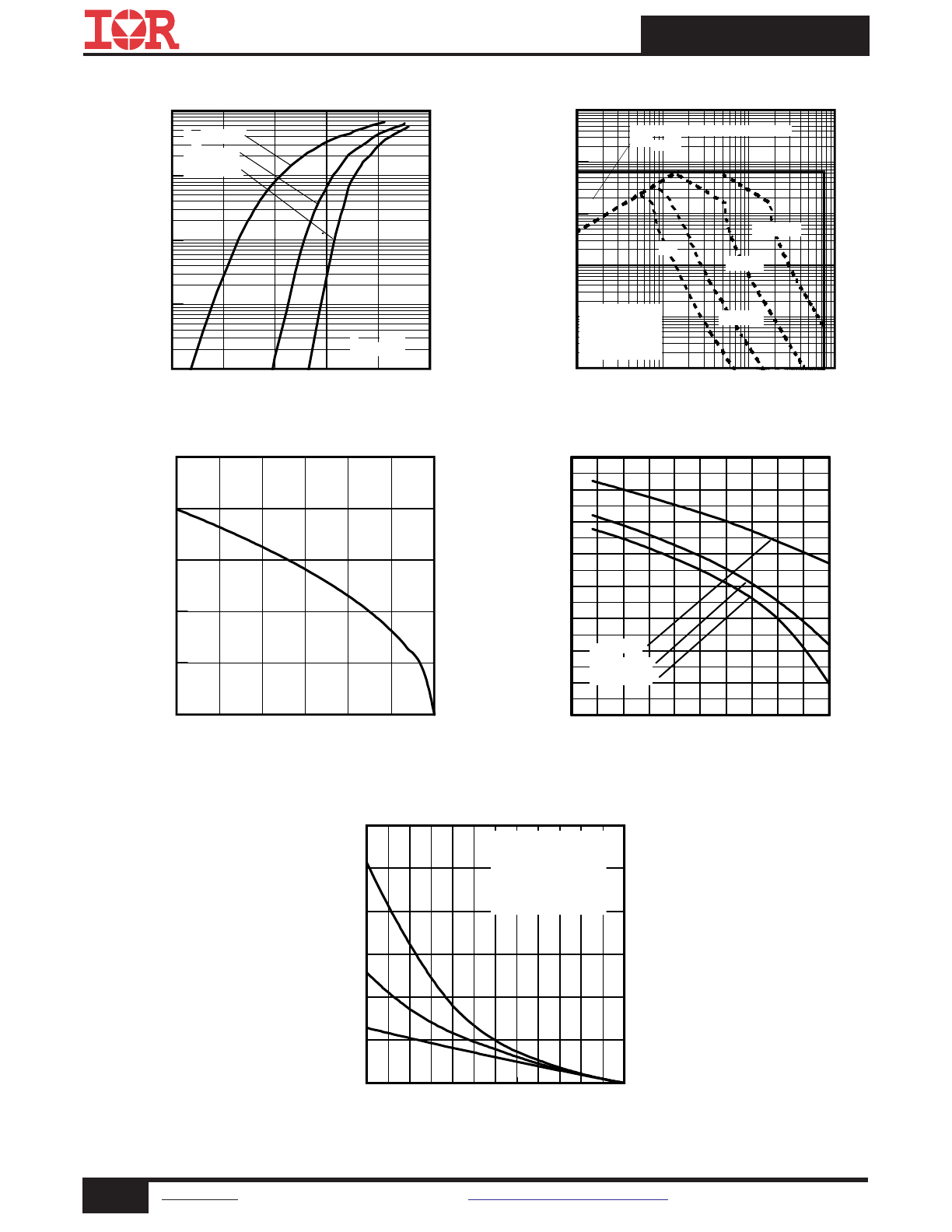

Fig 13. Typical Threshold Voltage vs.

Junction Temperature

Fig 12. Maximum Drain Current vs. Case Temperature

Fig 10. Typical Source-Drain Diode Forward Voltage

Fig11. Maximum Safe Operating Area

Fig 14. Maximum Avalanche Energy Vs. Drain Current

0.2

0.4

0.6

0.8

1.0

1.2

VSD, Source-to-Drain Voltage (V)

0.1

1

10

100

1000

I S

D

, R

ev

er

se

D

ra

in

C

ur

re

nt

(

A

)

TJ = 175°C

TJ = 25°C

TJ = -40°C

VGS = 0V

25

50

75

100

125

150

175

TC , Case Temperature (°C)

0

40

80

120

160

200

I D

,

D

ra

in

C

ur

re

nt

(

A

)

-75 -50 -25 0

25 50 75 100 125 150 175

TJ , Temperature ( °C )

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

V

G

S

(t

h)

, G

at

e

th

re

sh

ol

d

V

ol

ta

ge

(

V

)

ID = 1.0A

ID = 1.0mA

ID = 250μA

25

50

75

100

125

150

175

Starting TJ , Junction Temperature (°C)

0

200

400

600

800

1000

1200

E

A

S

,

S

in

gl

e

P

ul

se

A

va

la

nc

he

E

ne

rg

y

(m

J)

ID

TOP 15.39A

23.97A

BOTTOM 96A

0

1

10

100

VDS, Drain-to-Source Voltage (V)

0.1

1

10

100

1000

10000

I D

,

D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(

A

)

OPERATION IN THIS AREA LIMITED

BY RDS(on)

Tc = 25°C

Tj = 175°C

Single Pulse

100μsec

1msec

10msec

DC

6

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

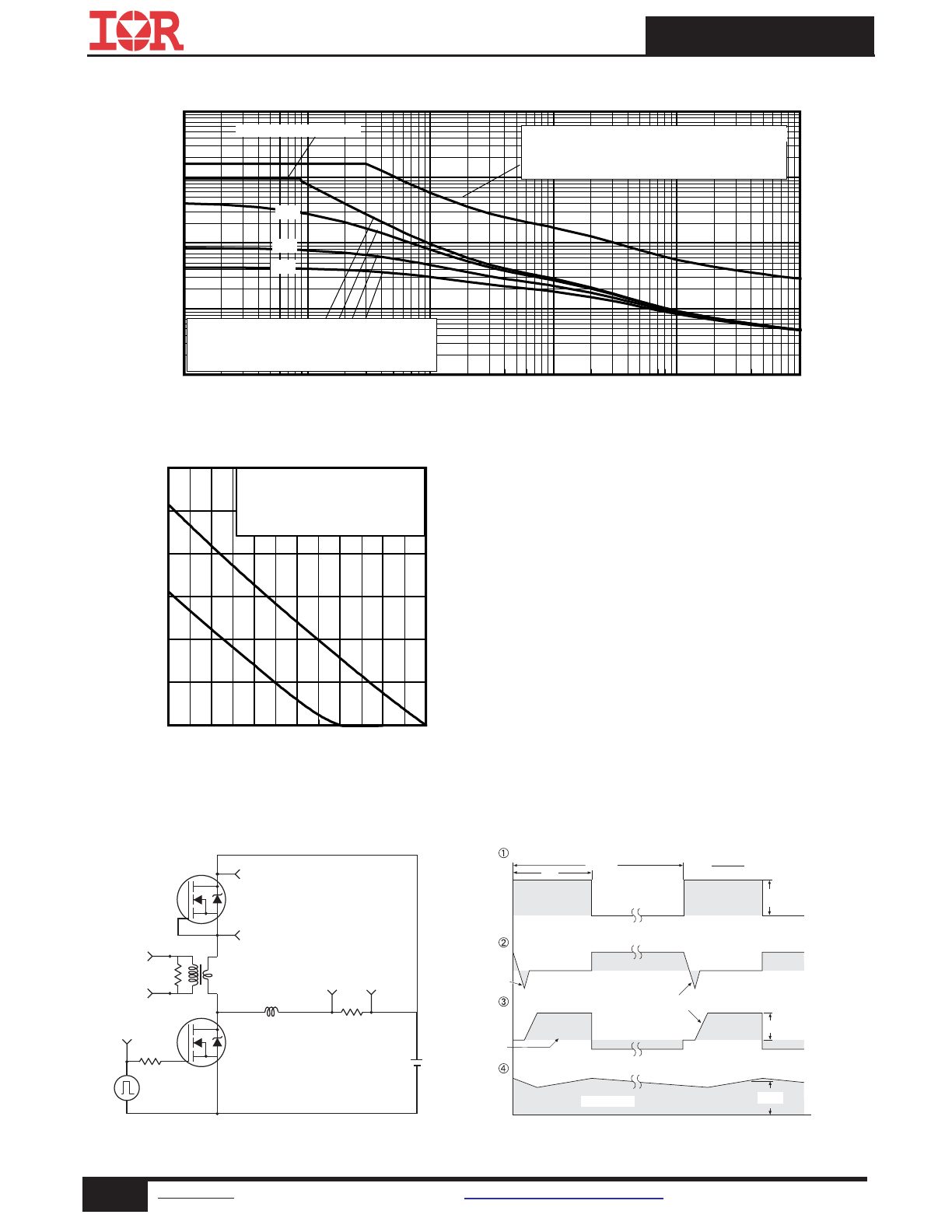

Fig 17.

Diode Reverse Recovery Test Circuit for N-Channel HEXFET

®

Power MOSFETs

Fig 15. Typical Avalanche Current Vs.Pulsewidth

Fig 16. Maximum Avalanche Energy Vs. Temperature

Notes on Repetitive Avalanche Curves , Figures 15, 16:

(For further info, see AN-1005 at www.irf.com)

1. Avalanche failures assumption:

Purely a thermal phenomenon and failure occurs at a

temperature far in excess of T

jmax

. This is validated for

every part type.

2. Safe operation in Avalanche is allowed as long asT

jmax

is

not exceeded.

3. Equation below based on circuit and waveforms shown in

Figures 19a, 19b.

4. P

D (ave)

= Average power dissipation per single

avalanche pulse.

5. BV = Rated breakdown voltage (1.3 factor accounts for

voltage increase during avalanche).

6. I

av

= Allowable avalanche current.

7.

ΔT

=

Allowable rise in junction temperature, not to exceed

T

jmax

(assumed as 25°C in Figure 15, 16).

t

av =

Average time in avalanche.

D = Duty cycle in avalanche = t

av

·f

Z

thJC

(D, t

av

) = Transient thermal resistance, see figure 11)

P

D (ave)

= 1/2 ( 1.3·BV·I

av

) =

DT/ Z

thJC

I

av

=

2

DT/ [1.3·BV·Z

th

]

E

AS (AR)

= P

D (ave)

·t

a

P.W.

Period

di/dt

Diode Recovery

dv/dt

Ripple

≤ 5%

Body Diode Forward Drop

Re-Applied

Voltage

Reverse

Recovery

Current

Body Diode Forward

Current

V

GS

=10V

V

DD

I

SD

Driver Gate Drive

D.U.T. I

SD

Waveform

D.U.T. V

DS

Waveform

Inductor Curent

D =

P.W.

Period

*

V

GS

= 5V for Logic Level Devices

*

Inductor Current

Circuit Layout Considerations

• Low Stray Inductance

• Ground Plane

• Low Leakage Inductance

Current Transformer

• di/dt controlled by R

G

• Driver same type as D.U.T.

• I

SD

controlled by Duty Factor "D"

• D.U.T. - Device Under Test

+

-

+

+

+

-

-

-

R

G

V

DD

D.U.T

1.0E-06

1.0E-05

1.0E-04

1.0E-03

1.0E-02

1.0E-01

tav (sec)

0.1

1

10

100

1000

A

va

la

nc

he

C

ur

re

nt

(

A

)

0.05

Duty Cycle = Single Pulse

0.10

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming

ΔΤj = 25°C and

Tstart = 150°C.

0.01

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming

ΔTj = 150°C and

Tstart =25°C (Single Pulse)

25

50

75

100

125

150

175

Starting TJ , Junction Temperature (°C)

0

50

100

150

200

250

300

E

A

R

,

A

va

la

nc

he

E

ne

rg

y

(m

J)

TOP Single Pulse

BOTTOM 1.0% Duty Cycle

ID = 96A

7

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

Fig 18a. Gate Charge Test Circuit

Fig 18b. Gate Charge Waveform

Fig 19b. Unclamped Inductive Waveforms

tp

V

(BR)DSS

I

AS

Fig 19a. Unclamped Inductive Test Circuit

Fig 20b. Switching Time Waveforms

Fig 20a. Switching Time Test Circuit

R G

IAS

0.01

Ω

tp

D.U.T

L

VDS

+

- VDD

DRIVER

A

15V

20V

V

GS

Vds

Vgs

Id

Vgs(th)

Qgs1

Qgs2

Qgd

Qgodr

1K

VCC

DUT

0

L

S

20K

V

DS

90%

10%

V

GS

t

d(on)

t

r

t

d(off)

t

f

V

DS

Pulse Width ≤ 1 µs

Duty Factor ≤ 0.1 %

R

D

V

GS

R

G

D.U.T.

10V

+

-

V

DD

V

GS

8

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

G = GATE

D = DRAIN

S = SOURCE

D

D

D

D

D

D

S

S

S

S

G

S

S

S

S

DirectFET

Board Footprint, L8 (Large Size Can).

Please see AN-1035 for DirectFET assembly details and stencil and substrate design recommendations

Note: For the most current drawing please refer to IR website at:

http://www.irf.com/package/

9

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

DirectFET

Part Marking

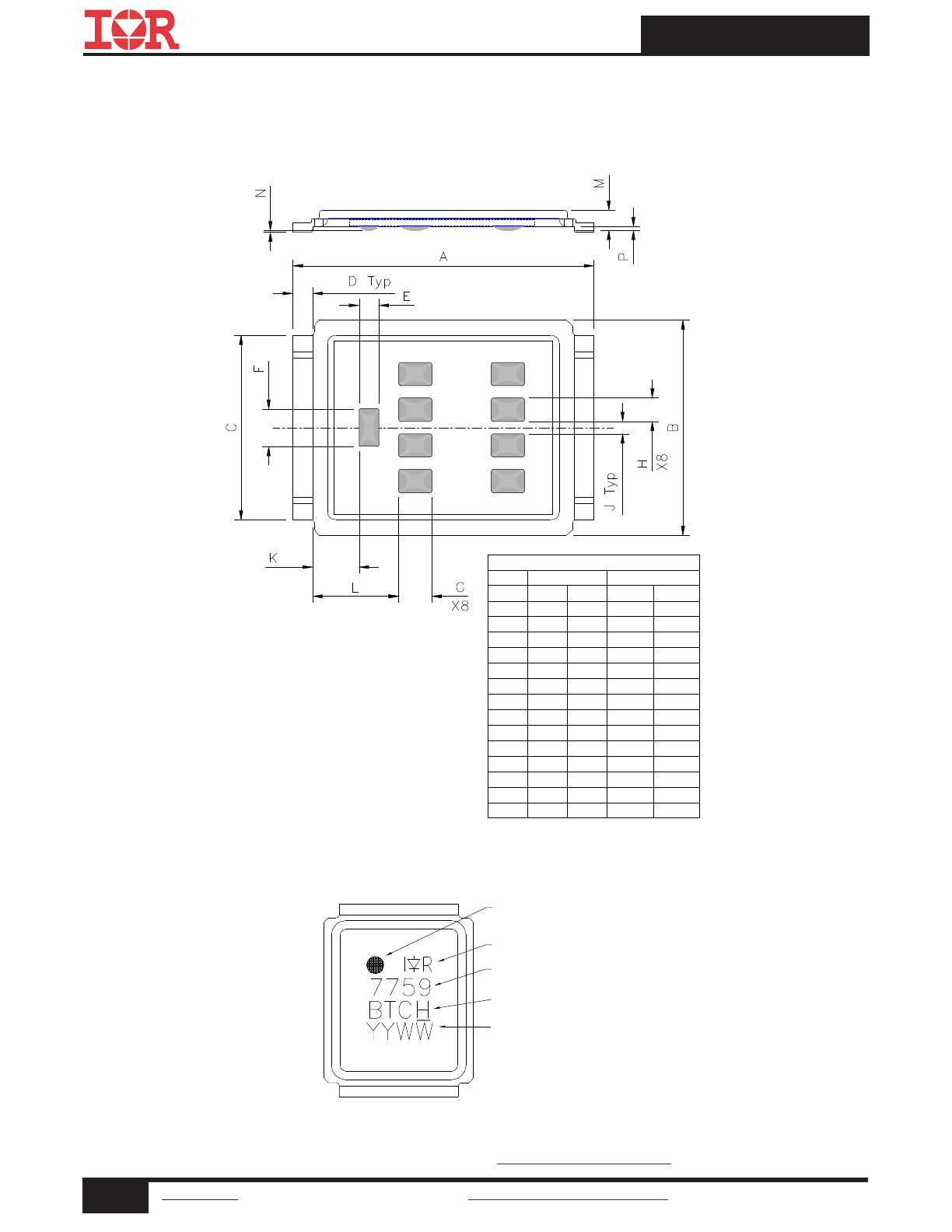

DirectFET

Outline Dimension, L8 Outline (LargeSize Can).

Please see AN-1035 for DirectFET assembly details and stencil and substrate design recommendations

MAX

0.360

0.280

0.236

0.026

0.024

0.048

0.017

0.030

0.017

0.058

0.106

0.028

0.003

0.007

IMPERIAL

METRIC

DIMENSIONS

MIN

0.356

0.270

0.232

0.022

0.023

0.046

0.015

0.029

0.015

0.053

0.099

0.023

0.001

0.003

CODE

A

B

C

D

E

F

G

H

J

K

L

M

N

P

MIN

9.05

6.85

5.90

0.55

0.58

1.18

0.98

0.73

0.38

1.34

2.52

0.59

0.03

0.09

MAX

9.15

7.10

6.00

0.65

0.62

1.22

1.02

0.77

0.42

1.47

2.69

0.70

0.08

0.18

LOGO

GATE MARKING

BATCH NUMBER

PART NUMBER

DATE CODE

Line above the last character of

the date code indicates "Lead-Free"

Note: For the most current drawing please refer to IR website at:

http://www.irf.com/package/

10

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

DirectFET

Tape & Reel Dimension (Showing component orientation).

LOADED TAPE FEED DIRECTION

MIN

11.90

3.90

15.90

7.40

7.20

9.90

1.50

1.50

NOTE: CONTROLLING

DIMENSIONS IN MM

CODE

A

B

C

D

E

F

G

H

MAX

12.10

4.10

16.30

7.60

7.40

10.10

NC

1.60

MIN

0.469

0.154

0.626

0.291

0.284

0.390

0.059

0.059

MAX

0.476

0.161

0.642

0.299

0.291

0.398

NC

0.063

DIMENSIONS

METRIC

IMPERIAL

Note: For the most current drawing please refer to IR website at:

http://www.irf.com/package/

R EEL DIMENSIONS

NOTE: Controlling dim ensions in m m

Std reel quantity is 4000 parts (ordered as IRF7759L2TR).

MAX

N.C

N.C

0.520

N.C

3.940

0.880

0.720

0.760

IM PERIAL

M IN

330.00

20.20

12.80

1.50

99.00

N .C

16.40

15.90

STANDARD OPTION (QTY 4000)

CODE

A

B

C

D

E

F

G

H

M AX

N .C

N .C

13.20

N .C

100.00

22.40

18.40

19.40

MIN

12.992

0.795

0.504

0.059

3.900

N.C

0.650

0.630

M ET RIC

DirectFET

Power MOSFET

Typical values (unless otherwise specified)

DirectFET

ISOMETRIC

L8

Applicable DirectFET Outline and Substrate Outline

l

RoHS Compliant, Halogen Free

l

Lead-Free (Qualified up to 260°C Reflow)

l

Ideal for High Performance Isolated Converter

Primary Switch Socket

l

Optimized for Synchronous Rectification

l

Low Conduction Losses

l

High Cdv/dt Immunity

l

Low Profile (<0.7mm)

l

Dual Sided Cooling Compatible

l

Compatible with existing Surface Mount Techniques

l

Industrial Qualified

Description

The IRF7759L2TR/TR1PbF combines the latest HEXFET® Power MOSFET Silicon technology with the advanced DirectFET

TM

packaging to achieve the

lowest on-state resistance in a package that has a footprint smaller than a D

2

PAK and only 0.7 mm profile. The DirectFET package is compatible with existing

layout geometries used in power applications, PCB assembly equipment and vapor phase, infra-red or convection soldering techniques, when application

note AN-1035 is followed regarding the manufacturing methods and processes. The DirectFET package allows dual sided cooling to maximize thermal transfer

in power systems.

The IRF7759L2TR/TR1PbF is optimized for high frequency switching and synchronous rectification applications. The reduced total losses in the device

coupled with the high level of thermal performance enables high efficiency and low temperatures, which are key for system reliability improvements, and

makes this device ideal for high performance power converters.

Fig 1. Typical On-Resistance vs. Gate Voltage

Click on this section to link to the appropriate technical paper.

Click on this section to link to the DirectFET Website.

Surface mounted on 1 in. square Cu board, steady state.

T

C

measured with thermocouple mounted to top (Drain) of part.

Repetitive rating; pulse width limited by max. junction temperature.

Starting T

J

= 25°C, L = 0.056mH, R

G

= 25

Ω, I

AS

= 96A.

Notes:

Fig 2. Typical On-Resistance vs. Drain Current

SB

SC

M2 M4

L4

L6

L8

D

S

G

D

S

S

S

S

S

S

S

Absolute Maximum Ratings

Parameter

Units

V

DS

Drain-to-Source Voltage

V

GS

Gate-to-Source Voltage

I

D

@ T

C

= 25°C

Continuous Drain Current, V

GS

@ 10V

(Silicon Limited)

f

I

D

@ T

C

= 100°C

Continuous Drain Current, V

GS

@ 10V

(Silicon Limited)

f

I

D

@ T

A

= 25°C

Continuous Drain Current, V

GS

@ 10V

(Silicon Limited)

e

I

D

@ T

C

= 25°C

Continuous Drain Current, V

GS

@ 10V

(Package Limited)

f

I

DM

Pulsed Drain Current

g

E

AS

Single Pulse Avalanche Energy

h

mJ

I

AR

Avalanche Current

g

A

A

V

96

375

257

Max.

113

26

640

±20

75

160

2

4

6

8

10

12

14

16

18

20

V GS, Gate -to -Source Voltage (V)

0

2

4

6

8

R

D

S

(o

n)

,

D

ra

in

-t

o

-S

ou

rc

e

O

n

R

es

is

ta

nc

e

(m

Ω

)

I D = 96A

T J = 25°C

T J = 125°C

15

30

45

60

75

90

105

ID, Drain Current (A)

1.65

1.75

1.85

1.95

T

yp

ic

al

R

D

S

(o

n)

( m

Ω

)

TA= 25°C

VGS = 8.0V

VGS = 7.0V

VGS = 10V

VGS = 15V

V

DSS

V

GS

R

DS(on)

75V min ±20V max 1.8mΩ@ 10V

Q

g tot

Q

gd

V

gs(th)

200nC

62nC

3.0V

IRF7759L2PbF

1

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

Form

Quantity

IRF7759L2TRPbF

DirectFET2 Large Can

Tape and Reel

4000

"TR" suffix

IRF7759L2TR1PbF

DirectFET2 Large Can

Tape and Reel

1000

"TR1" suffix EOL notice # 264

Note

Orderable part number

Package Type

Standard Pack

2

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

Notes:

Repetitive rating; pulse width limited by max. junction temperature.

Pulse width ≤ 400μs; duty cycle ≤ 2%.

Static @ T

J

= 25°C (unless otherwise specified)

Parameter

Min. Typ. Max. Units

BV

DSS

Drain-to-Source Breakdown Voltage

75

–––

–––

V

ΔΒV

DSS

/ΔT

J

Breakdown Voltage Temp. Coefficient

–––

0.02

–––

V/°C

R

DS(on)

Static Drain-to-Source On-Resistance

–––

1.8

2.3

m

Ω

V

GS(th)

Gate Threshold Voltage

2.0

3.0

4.0

V

ΔV

GS(th)

/

ΔT

J

Gate Threshold Voltage Coefficient

–––

-11

––– mV/°C

I

DSS

Drain-to-Source Leakage Current

–––

–––

20

–––

–––

250

I

GSS

Gate-to-Source Forward Leakage

–––

–––

100

Gate-to-Source Reverse Leakage

–––

–––

-100

gfs

Forward Transconductance

74

–––

–––

S

Q

g

Total Gate Charge

–––

200

300

Q

gs1

Pre-Vth Gate-to-Source Charge

–––

37

–––

Q

gs2

Post-Vth Gate-to-Source Charge

–––

11

–––

Q

gd

Gate-to-Drain Charge

–––

62

93

Q

godr

Gate Charge Overdrive

–––

91

–––

See Fig. 9

Q

sw

Switch Charge (Q

gs2

+ Q

gd

)

–––

73

–––

Q

oss

Output Charge

–––

60

–––

nC

R

G

Gate Resistance

–––

1.1

–––

Ω

t

d(on)

Turn-On Delay Time

–––

18

–––

t

r

Rise Time

–––

37

–––

t

d(off)

Turn-Off Delay Time

–––

80

–––

t

f

Fall Time

–––

33

–––

C

iss

Input Capacitance

–––

12222 –––

C

oss

Output Capacitance

–––

1465

–––

C

rss

Reverse Transfer Capacitance

–––

609

–––

C

oss

Output Capacitance

–––

7457

–––

C

oss

Output Capacitance

–––

955

–––

Diode Characteristics

Parameter

Min. Typ. Max. Units

I

S

Continuous Source Current

(Body Diode)

I

SM

Pulsed Source Current

(Body Diode)

g

V

SD

Diode Forward Voltage

–––

–––

1.3

V

t

rr

Reverse Recovery Time

–––

64

96

ns

Q

rr

Reverse Recovery Charge

–––

150

225

nC

pF

A

–––

–––

160

–––

–––

640

μA

nA

nC

ns

MOSFET symbol

R

G

=1.8

Ω

V

DS

= 25V

Conditions

V

GS

= 0V, V

DS

= 60V, f=1.0MHz

V

GS

= 0V, V

DS

= 1.0V, f=1.0MHz

V

DS

= 16V, V

GS

= 0V

V

DD

= 38V, V

GS

= 10Vi

V

GS

= 0V

ƒ = 1.0MHz

I

D

= 96A

V

DS

= 75V, V

GS

= 0V

Conditions

V

GS

= 0V, I

D

= 250μA

Reference to 25°C, I

D

= 2mA

V

GS

= 10V, I

D

= 96A i

V

DS

= V

GS

, I

D

= 250μA

T

J

= 25°C, I

F

= 96A, V

DD

= 38V

di/dt = 100A/μs i

T

J

= 25°C, I

S

= 96A, V

GS

= 0V

i

showing the

integral reverse

p-n junction diode.

I

D

= 96A

V

DS

= 60V, V

GS

= 0V, T

J

= 125°C

V

GS

= 20V

V

GS

= -20V

V

GS

= 10V

V

DS

= 25V, I

D

= 96A

V

DS

= 38V

3

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

Fig 3. Maximum Effective Transient Thermal Impedance, Junction-to-Case

Surface mounted on 1 in. square Cu board, steady state.

T

C

measured with thermocouple incontact with top (Drain) of part.

Used double sided cooling, mounting pad with large heatsink.

Notes:

Mounted on minimum footprint full size board with metalized

back and with small clip heatsink.

R

θ

is measured at

T

J

of approximately 90°C.

Surface mounted on 1 in. square Cu

board (still air).

Mounted on minimum footprint full size board with metalized

back and with small clip heatsink. (still air)

1E-006

1E-005

0.0001

0.001

0.01

0.1

1

t1 , Rectangular Pulse Duration (sec)

0.0001

0.001

0.01

0.1

1

10

T

he

rm

al

R

es

po

ns

e

(

Z

th

JC

)

°

C

/W

0.20

0.10

D = 0.50

0.02

0.01

0.05

SINGLE PULSE

( THERMAL RESPONSE )

Notes:

1. Duty Factor D = t1/t2

2. Peak Tj = P dm x Zthjc + Tc

τ

J

τ

J

τ

1

τ

1

τ

2

τ

2

τ

3

τ

3

R

1

R

1

R

2

R

2

R

3

R

3

Ci i

/Ri

Ci=

τi/Ri

τ

τ

C

τ

4

τ

4

R

4

R

4

Ri (°C/W)

τi (sec)

0.10804 0.000171

0.61403 0.053914

0.45202 0.006099

0.00001 0.036168

Absolute Maximum Ratings

Parameter

Units

P

D

@T

C

= 25°C

Power Dissipation

f

P

D

@T

C

= 100°C

Power Dissipation

f

P

D

@T

A

= 25°C

Power Dissipation

c

T

P

Peak Soldering Temperature

T

J

Operating Junction and

T

STG

Storage Temperature Range

Thermal Resistance

Parameter

Typ.

Max.

Units

R

θJA

Junction-to-Ambient

e

–––

45

R

θJA

Junction-to-Ambient

j

12.5

–––

R

θJA

Junction-to-Ambient

k

20

–––

°C/W

R

θJ-Can

Junction-to-Can

fl

–––

1.2

R

θJ-PCB

Junction-to-PCB Mounted

–––

0.5

W

°C

270

-55 to + 175

Max.

3.3

125

63

4

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

Fig 5. Typical Output Characteristics

Fig 4. Typical Output Characteristics

Fig 6. Typical Transfer Characteristics

Fig 7. Normalized On-Resistance vs. Temperature

Fig 8. Typical Capacitance vs.Drain-to-Source Voltage

Fig 9. Typical Total Gate Charge vs

Gate-to-Source Voltage

0.1

1

10

100

VDS, Drain-to-Source Voltage (V)

1

10

100

1000

I D

, D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(

A

)

3.75V

≤60μs

PULSE WIDTH

Tj = 175°C

VGS

TOP

15V

10V

7.00V

5.50V

5.00V

4.50V

4.00V

BOTTOM

3.75V

2

2.5

3

3.5

4

4.5

5

5.5

6

VGS, Gate-to-Source Voltage (V)

0.1

1

10

100

1000

I D

, D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(

A

)

TJ = 175°C

TJ = 25°C

TJ = -40°C

VDS = 25V

≤60μs PULSE WIDTH

-60

-20

20

60

100

140

180

TJ , Junction Temperature (°C)

0.5

1.0

1.5

2.0

2.5

R

D

S

(o

n)

,

D

ra

in

-t

o-

S

ou

rc

e

O

n

R

es

is

ta

nc

e

(

N

or

m

al

iz

ed

)

ID = 96A

VGS = 10V

1

10

100

VDS, Drain-to-Source Voltage (V)

100

1000

10000

100000

C

, C

ap

ac

ita

nc

e

(p

F

)

VGS = 0V, f = 1 MHZ

Ciss = Cgs + Cgd, C ds SHORTED

Crss = Cgd

Coss = Cds + Cgd

Coss

Crss

Ciss

0

50

100

150

200

250

300

QG, Total Gate Charge (nC)

0

2

4

6

8

10

12

14

V

G

S

, G

at

e-

to

-S

ou

rc

e

V

ol

ta

ge

(

V

)

VDS= 60V

VDS= 38V

VDS= 15V

ID= 96A

0.1

1

10

100

VDS, Drain-to-Source Voltage (V)

0.01

0.1

1

10

100

1000

I D

, D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(

A

)

VGS

TOP

15V

10V

7.00V

5.50V

5.00V

4.50V

4.00V

BOTTOM

3.75V

≤60μs

PULSE WIDTH

Tj = 25°C

3.75V

5

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

Fig 13. Typical Threshold Voltage vs.

Junction Temperature

Fig 12. Maximum Drain Current vs. Case Temperature

Fig 10. Typical Source-Drain Diode Forward Voltage

Fig11. Maximum Safe Operating Area

Fig 14. Maximum Avalanche Energy Vs. Drain Current

0.2

0.4

0.6

0.8

1.0

1.2

VSD, Source-to-Drain Voltage (V)

0.1

1

10

100

1000

I S

D

, R

ev

er

se

D

ra

in

C

ur

re

nt

(

A

)

TJ = 175°C

TJ = 25°C

TJ = -40°C

VGS = 0V

25

50

75

100

125

150

175

TC , Case Temperature (°C)

0

40

80

120

160

200

I D

,

D

ra

in

C

ur

re

nt

(

A

)

-75 -50 -25 0

25 50 75 100 125 150 175

TJ , Temperature ( °C )

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

V

G

S

(t

h)

, G

at

e

th

re

sh

ol

d

V

ol

ta

ge

(

V

)

ID = 1.0A

ID = 1.0mA

ID = 250μA

25

50

75

100

125

150

175

Starting TJ , Junction Temperature (°C)

0

200

400

600

800

1000

1200

E

A

S

,

S

in

gl

e

P

ul

se

A

va

la

nc

he

E

ne

rg

y

(m

J)

ID

TOP 15.39A

23.97A

BOTTOM 96A

0

1

10

100

VDS, Drain-to-Source Voltage (V)

0.1

1

10

100

1000

10000

I D

,

D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(

A

)

OPERATION IN THIS AREA LIMITED

BY RDS(on)

Tc = 25°C

Tj = 175°C

Single Pulse

100μsec

1msec

10msec

DC

6

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

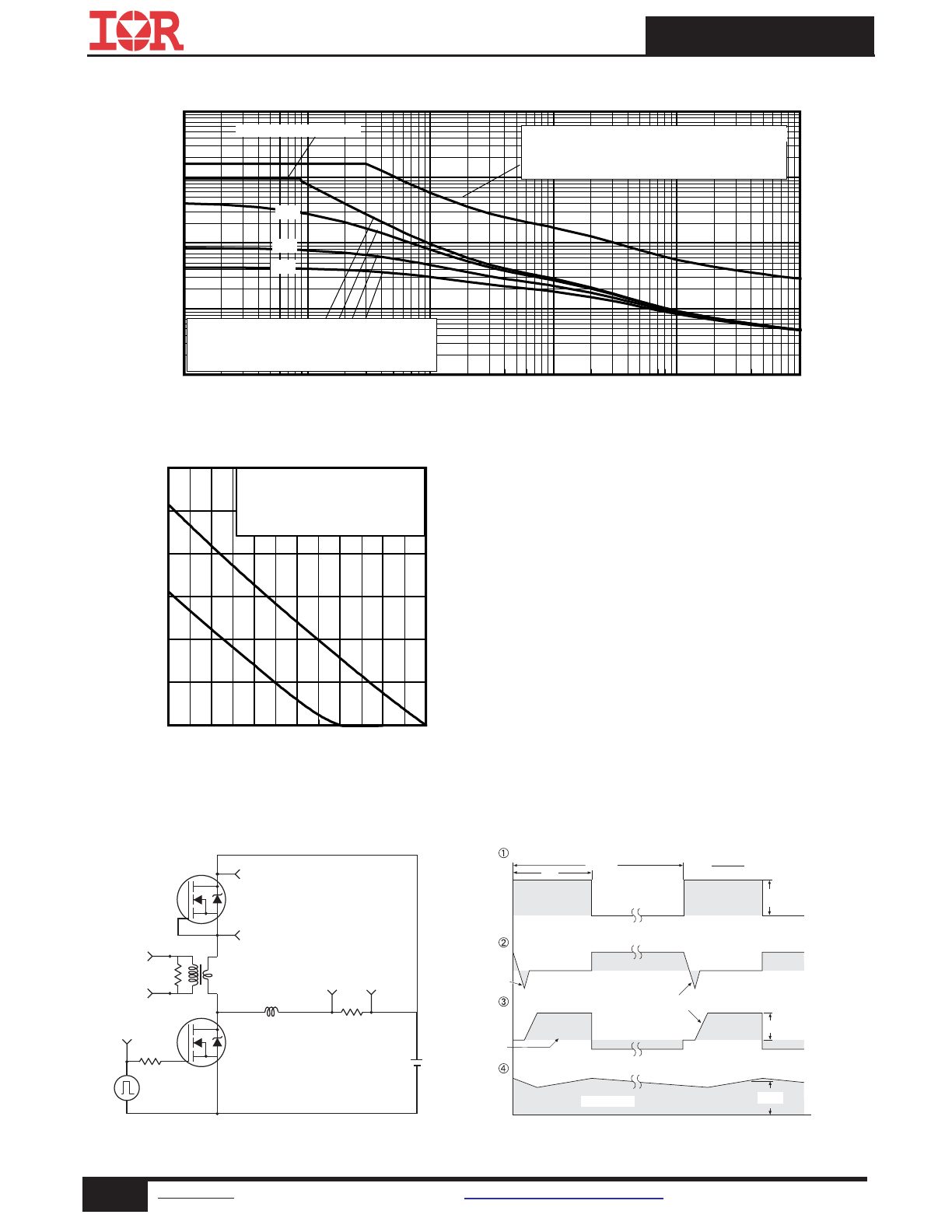

Fig 17.

Diode Reverse Recovery Test Circuit for N-Channel HEXFET

®

Power MOSFETs

Fig 15. Typical Avalanche Current Vs.Pulsewidth

Fig 16. Maximum Avalanche Energy Vs. Temperature

Notes on Repetitive Avalanche Curves , Figures 15, 16:

(For further info, see AN-1005 at www.irf.com)

1. Avalanche failures assumption:

Purely a thermal phenomenon and failure occurs at a

temperature far in excess of T

jmax

. This is validated for

every part type.

2. Safe operation in Avalanche is allowed as long asT

jmax

is

not exceeded.

3. Equation below based on circuit and waveforms shown in

Figures 19a, 19b.

4. P

D (ave)

= Average power dissipation per single

avalanche pulse.

5. BV = Rated breakdown voltage (1.3 factor accounts for

voltage increase during avalanche).

6. I

av

= Allowable avalanche current.

7.

ΔT

=

Allowable rise in junction temperature, not to exceed

T

jmax

(assumed as 25°C in Figure 15, 16).

t

av =

Average time in avalanche.

D = Duty cycle in avalanche = t

av

·f

Z

thJC

(D, t

av

) = Transient thermal resistance, see figure 11)

P

D (ave)

= 1/2 ( 1.3·BV·I

av

) =

DT/ Z

thJC

I

av

=

2

DT/ [1.3·BV·Z

th

]

E

AS (AR)

= P

D (ave)

·t

a

P.W.

Period

di/dt

Diode Recovery

dv/dt

Ripple

≤ 5%

Body Diode Forward Drop

Re-Applied

Voltage

Reverse

Recovery

Current

Body Diode Forward

Current

V

GS

=10V

V

DD

I

SD

Driver Gate Drive

D.U.T. I

SD

Waveform

D.U.T. V

DS

Waveform

Inductor Curent

D =

P.W.

Period

*

V

GS

= 5V for Logic Level Devices

*

Inductor Current

Circuit Layout Considerations

• Low Stray Inductance

• Ground Plane

• Low Leakage Inductance

Current Transformer

• di/dt controlled by R

G

• Driver same type as D.U.T.

• I

SD

controlled by Duty Factor "D"

• D.U.T. - Device Under Test

+

-

+

+

+

-

-

-

R

G

V

DD

D.U.T

1.0E-06

1.0E-05

1.0E-04

1.0E-03

1.0E-02

1.0E-01

tav (sec)

0.1

1

10

100

1000

A

va

la

nc

he

C

ur

re

nt

(

A

)

0.05

Duty Cycle = Single Pulse

0.10

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming

ΔΤj = 25°C and

Tstart = 150°C.

0.01

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming

ΔTj = 150°C and

Tstart =25°C (Single Pulse)

25

50

75

100

125

150

175

Starting TJ , Junction Temperature (°C)

0

50

100

150

200

250

300

E

A

R

,

A

va

la

nc

he

E

ne

rg

y

(m

J)

TOP Single Pulse

BOTTOM 1.0% Duty Cycle

ID = 96A

7

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

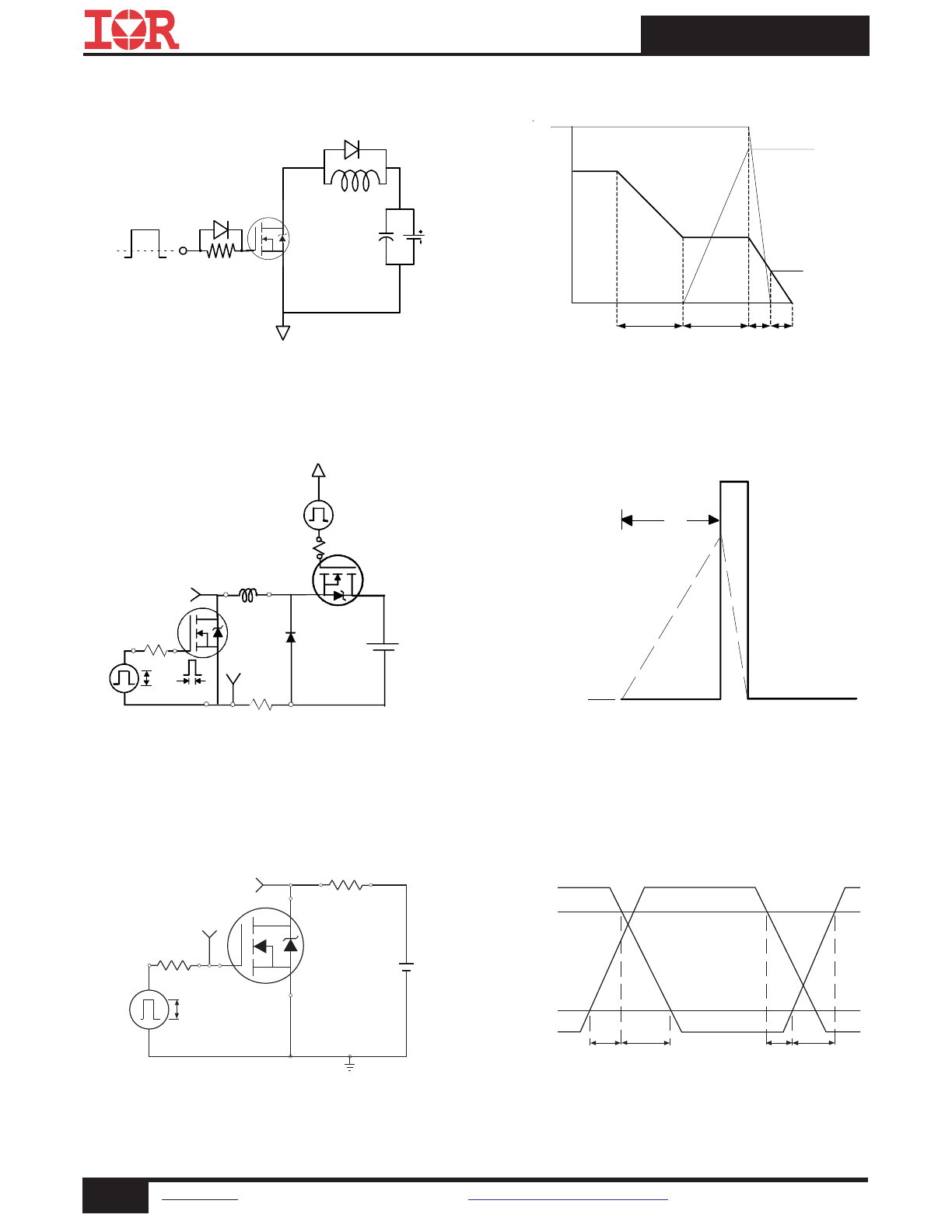

Fig 18a. Gate Charge Test Circuit

Fig 18b. Gate Charge Waveform

Fig 19b. Unclamped Inductive Waveforms

tp

V

(BR)DSS

I

AS

Fig 19a. Unclamped Inductive Test Circuit

Fig 20b. Switching Time Waveforms

Fig 20a. Switching Time Test Circuit

R G

IAS

0.01

Ω

tp

D.U.T

L

VDS

+

- VDD

DRIVER

A

15V

20V

V

GS

Vds

Vgs

Id

Vgs(th)

Qgs1

Qgs2

Qgd

Qgodr

1K

VCC

DUT

0

L

S

20K

V

DS

90%

10%

V

GS

t

d(on)

t

r

t

d(off)

t

f

V

DS

Pulse Width ≤ 1 µs

Duty Factor ≤ 0.1 %

R

D

V

GS

R

G

D.U.T.

10V

+

-

V

DD

V

GS

8

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

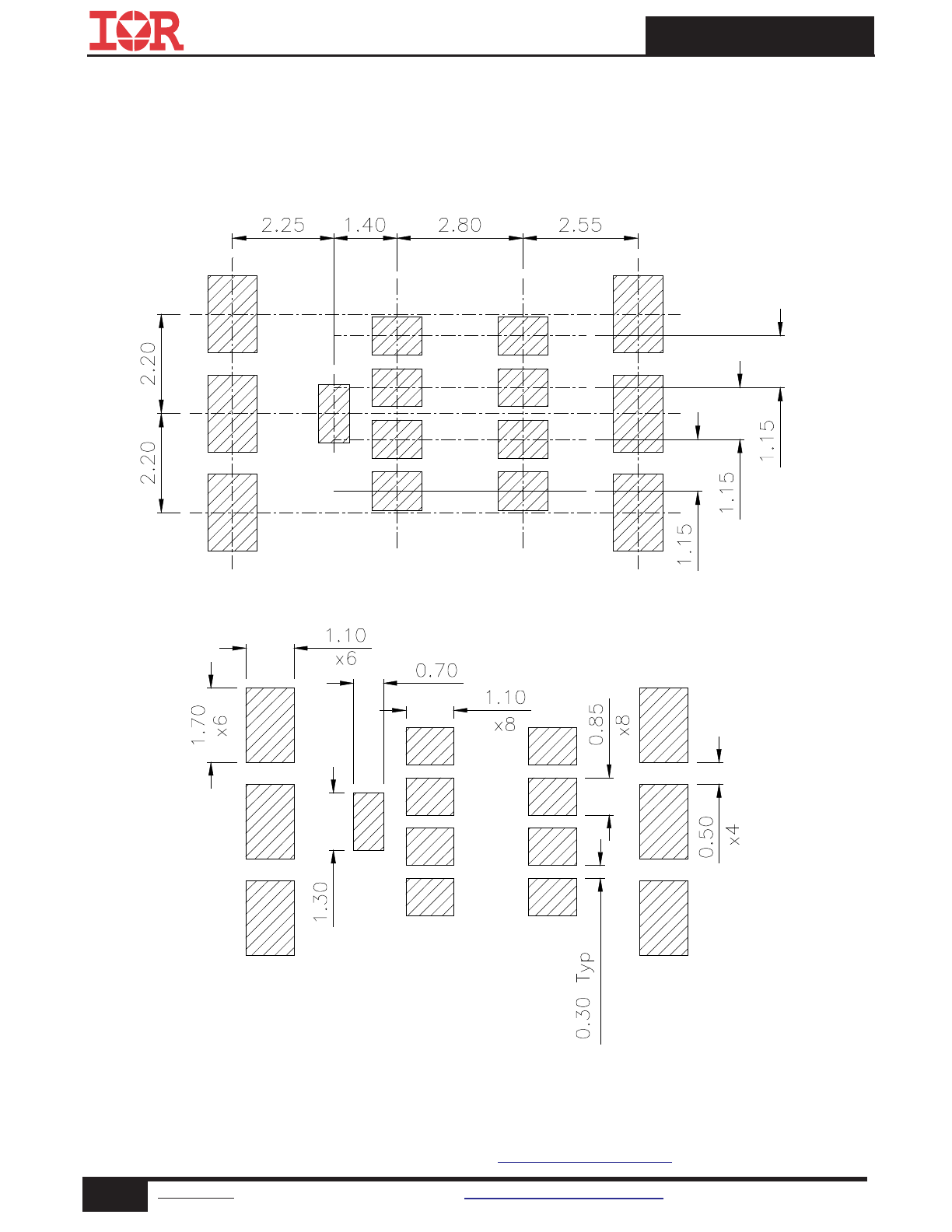

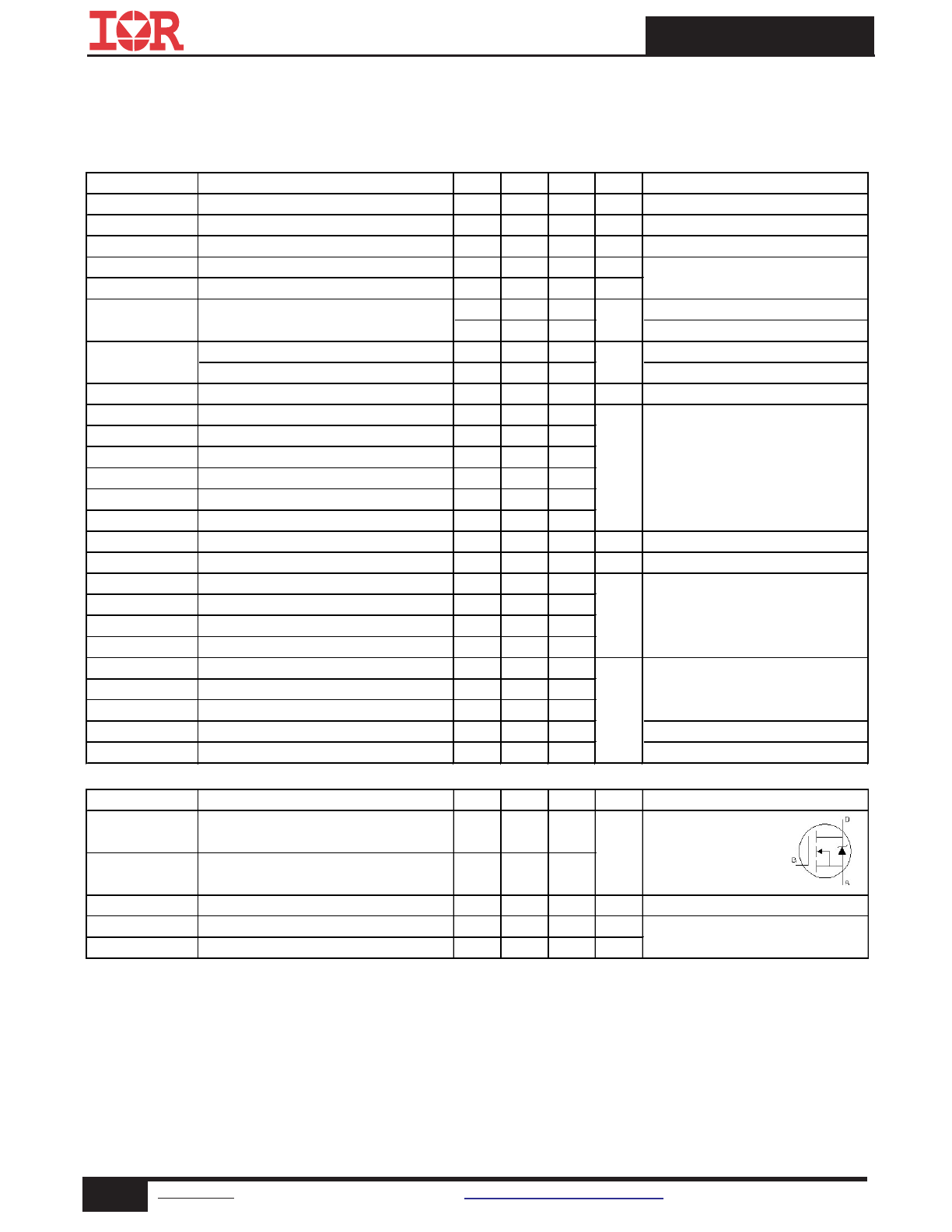

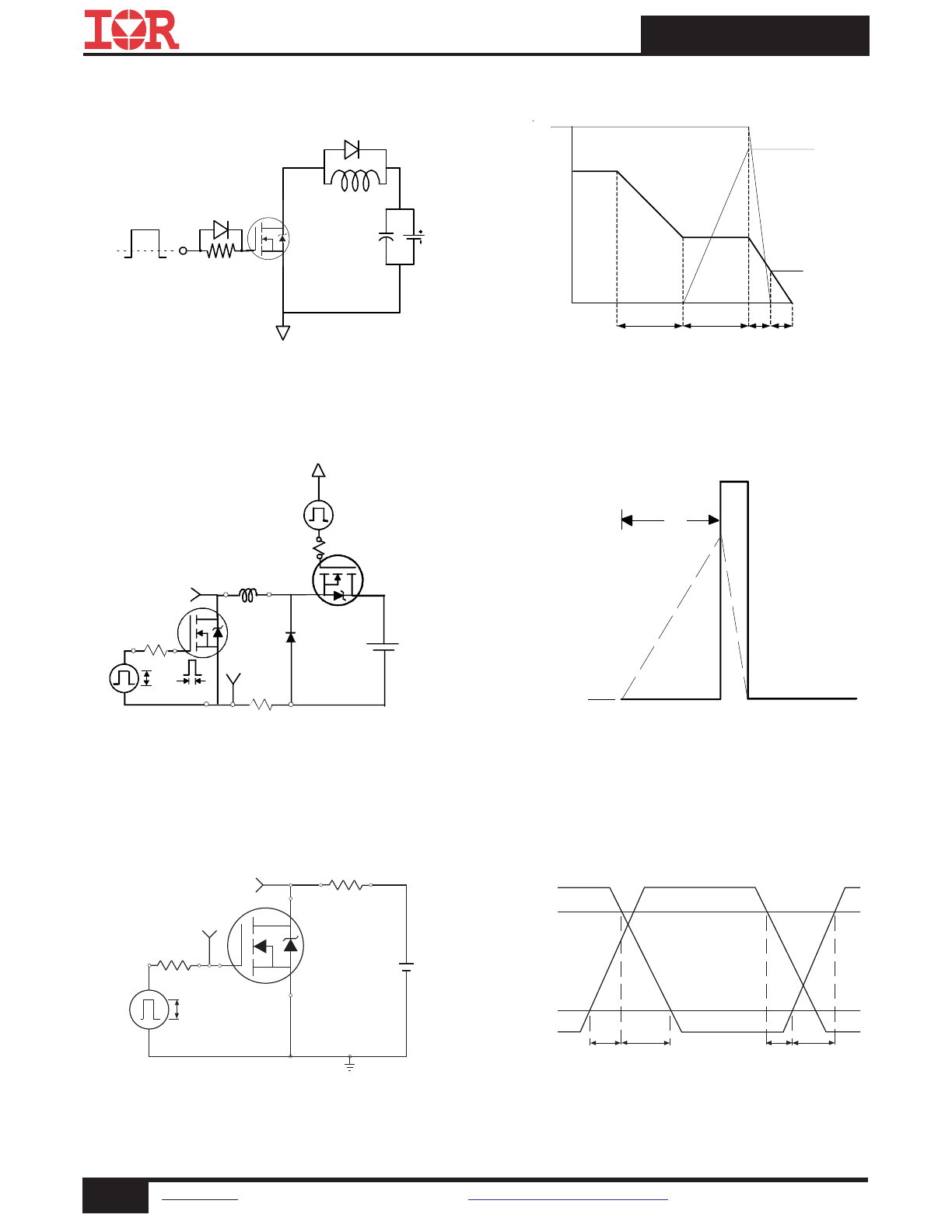

G = GATE

D = DRAIN

S = SOURCE

D

D

D

D

D

D

S

S

S

S

G

S

S

S

S

DirectFET

Board Footprint, L8 (Large Size Can).

Please see AN-1035 for DirectFET assembly details and stencil and substrate design recommendations

Note: For the most current drawing please refer to IR website at:

http://www.irf.com/package/

9

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

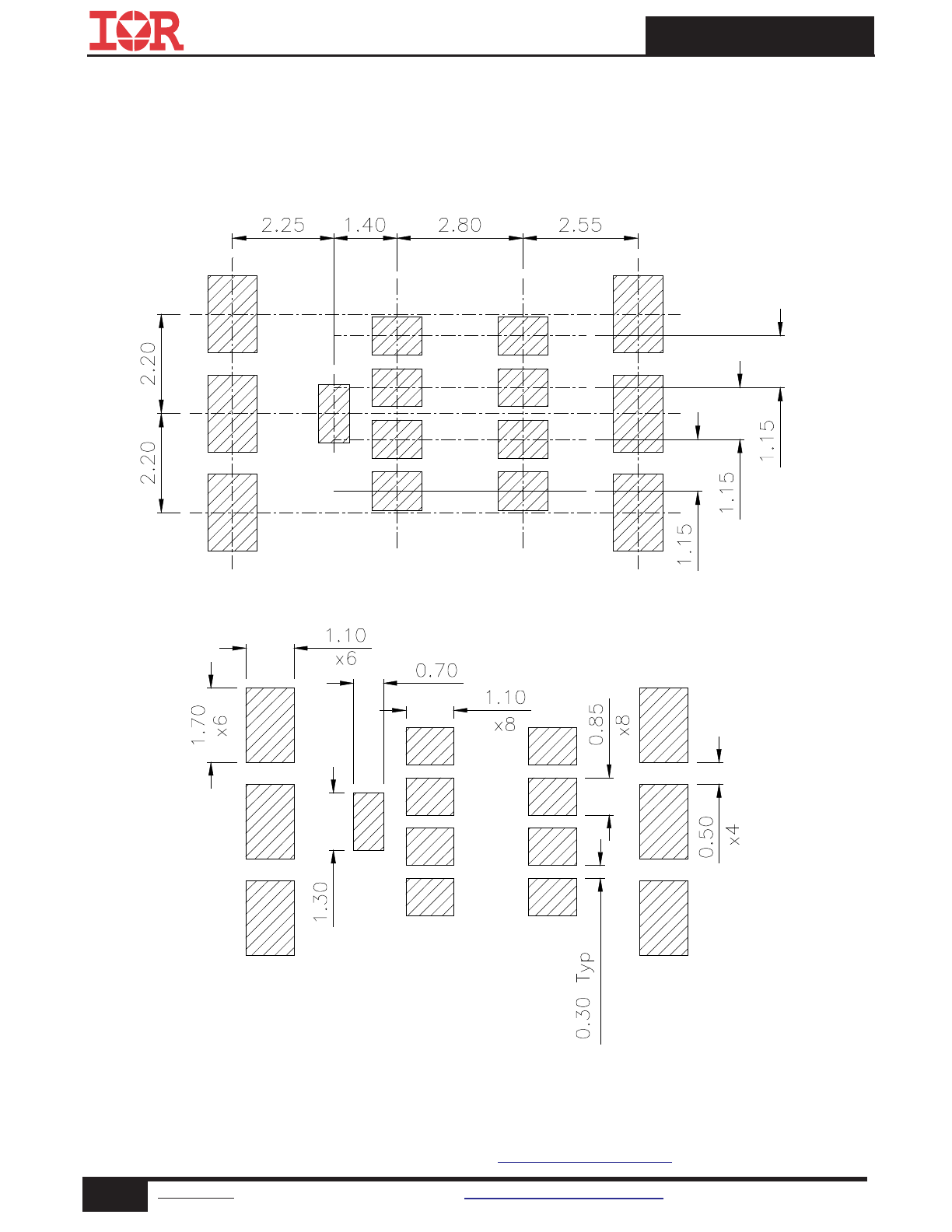

DirectFET

Part Marking

DirectFET

Outline Dimension, L8 Outline (LargeSize Can).

Please see AN-1035 for DirectFET assembly details and stencil and substrate design recommendations

MAX

0.360

0.280

0.236

0.026

0.024

0.048

0.017

0.030

0.017

0.058

0.106

0.028

0.003

0.007

IMPERIAL

METRIC

DIMENSIONS

MIN

0.356

0.270

0.232

0.022

0.023

0.046

0.015

0.029

0.015

0.053

0.099

0.023

0.001

0.003

CODE

A

B

C

D

E

F

G

H

J

K

L

M

N

P

MIN

9.05

6.85

5.90

0.55

0.58

1.18

0.98

0.73

0.38

1.34

2.52

0.59

0.03

0.09

MAX

9.15

7.10

6.00

0.65

0.62

1.22

1.02

0.77

0.42

1.47

2.69

0.70

0.08

0.18

LOGO

GATE MARKING

BATCH NUMBER

PART NUMBER

DATE CODE

Line above the last character of

the date code indicates "Lead-Free"

Note: For the most current drawing please refer to IR website at:

http://www.irf.com/package/

10

www.irf.com

©

2014 International Rectifier

Submit Datasheet Feedback

February 24, 2014

IRF7759L2PbF

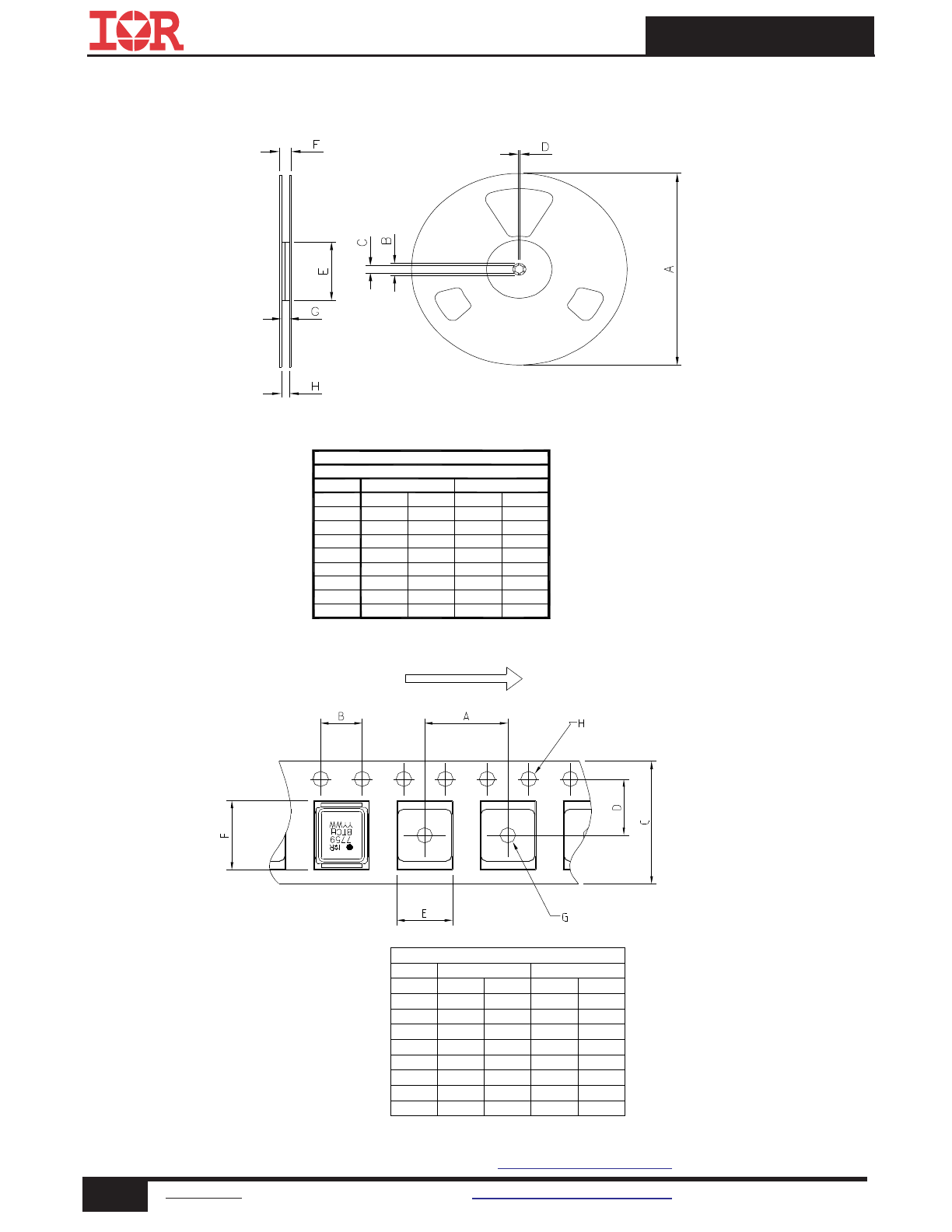

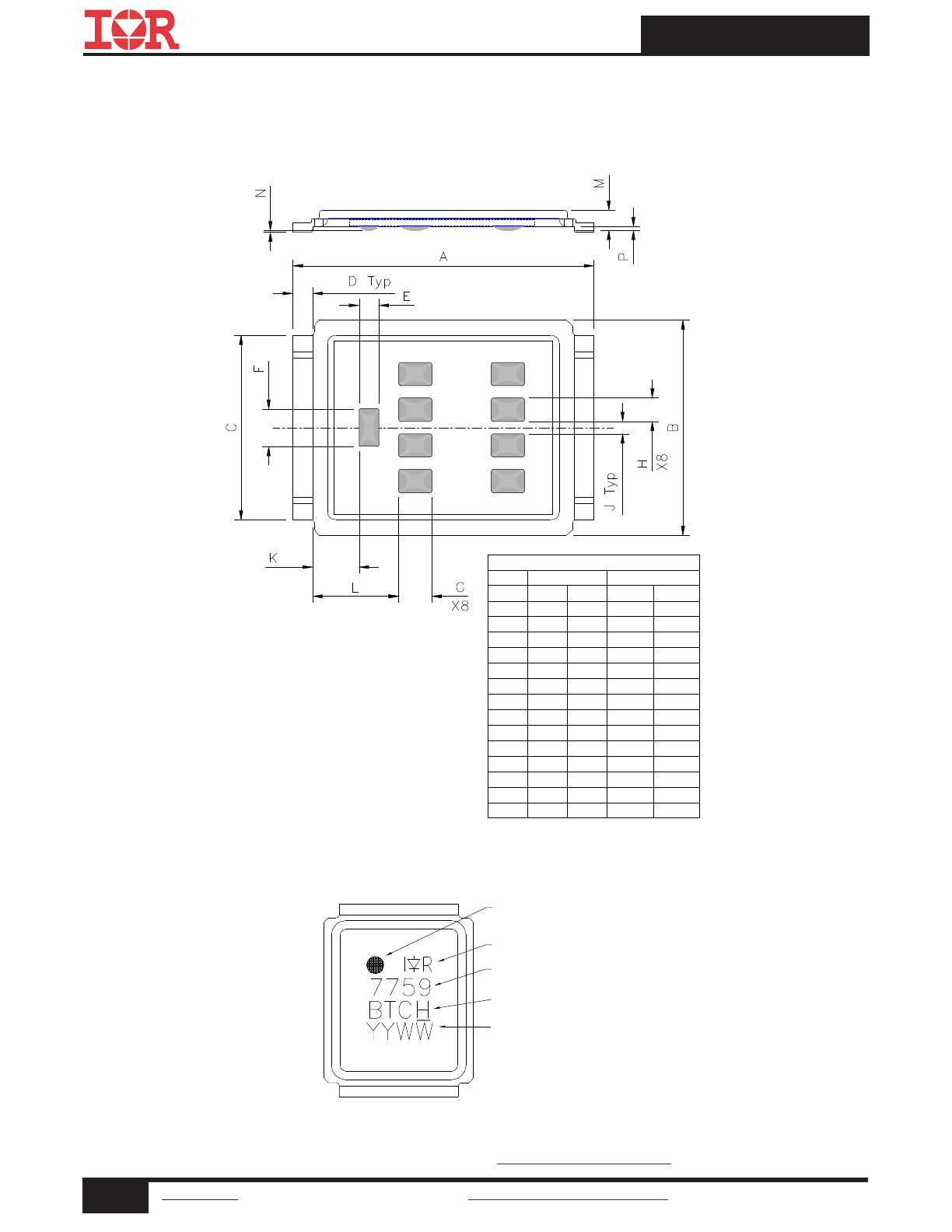

DirectFET

Tape & Reel Dimension (Showing component orientation).

LOADED TAPE FEED DIRECTION

MIN

11.90

3.90

15.90

7.40

7.20

9.90

1.50

1.50

NOTE: CONTROLLING

DIMENSIONS IN MM

CODE

A

B

C

D

E

F

G

H

MAX

12.10

4.10

16.30

7.60

7.40

10.10

NC

1.60

MIN

0.469

0.154

0.626

0.291

0.284

0.390

0.059

0.059

MAX

0.476

0.161

0.642

0.299

0.291

0.398

NC

0.063

DIMENSIONS

METRIC

IMPERIAL

Note: For the most current drawing please refer to IR website at:

http://www.irf.com/package/

R EEL DIMENSIONS

NOTE: Controlling dim ensions in m m

Std reel quantity is 4000 parts (ordered as IRF7759L2TR).

MAX

N.C

N.C

0.520

N.C

3.940

0.880

0.720

0.760

IM PERIAL

M IN

330.00

20.20

12.80

1.50

99.00

N .C

16.40

15.90

STANDARD OPTION (QTY 4000)

CODE

A

B

C

D

E

F

G

H

M AX

N .C

N .C

13.20

N .C

100.00

22.40

18.40

19.40

MIN

12.992

0.795

0.504

0.059

3.900

N.C

0.650

0.630

M ET RIC