AUIRFR8405

AUIRFU8405

V

DSS

40V

R

DS(on)

typ.

1.65m

I

D (Silicon Limited)

211A

max.

1.98m

I

D (Package Limited)

100A

Features

Advanced

Process

Technology

New Ultra Low On-Resistance

175°C

Operating

Temperature

Fast

Switching

Repetitive Avalanche Allowed up to Tjmax

Lead-Free,

RoHS

Compliant

Automotive Qualified *

Description

Specifically designed for Automotive applications, this HEXFET® Power MOSFET

utilizes the latest processing techniques to achieve extremely low on-resistance per

silicon area. Additional features of this design are a 175°C junction operating

temperature, fast switching speed and improved repetitive avalanche rating. These

features combine to make this design an extremely efficient and reliable device for

use in Automotive applications and wide variety of other applications.

1

2015-10-12

HEXFET® is a registered trademark of Infineon.

*Qualification standards can be found at

www.infineon.com

AUTOMOTIVE GRADE

Symbol Parameter

Max.

Units

I

D

@ T

C

= 25°C

Continuous Drain Current, V

GS

@ 10V (Silicon Limited)

211

A

I

D

@ T

C

= 100°C

Continuous Drain Current, V

GS

@ 10V (Silicon Limited)

150

I

D

@ T

C

= 25°C

Continuous Drain Current, V

GS

@ 10V (Package Limited)

100

I

DM

Pulsed Drain Current 804

P

D

@T

C

= 25°C

Maximum Power Dissipation

163

W

Linear Derating Factor

1.1

W/°C

V

GS

Gate-to-Source Voltage

± 20

V

T

J

Operating Junction and

-55 to + 175

T

STG

Storage Temperature Range

°C

Soldering Temperature, for 10 seconds (1.6mm from case)

300

Absolute Maximum Ratings

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress

ratings only; and functional operation of the device at these or any other condition beyond those indicated in the specifications is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. The thermal resistance and

power dissipation ratings are measured under board mounted and still air conditions. Ambient temperature (TA) is 25°C, unless

otherwise specified.

Thermal Resistance

Symbol Parameter

Typ.

Max.

Units

R

JC

Junction-to-Case –––

0.92

°C/W

R

JA

Junction-to-Ambient ( PCB Mount) –––

50

R

JA

Junction-to-Ambient

–––

110

D-Pak

AUIRFR8405

I-Pak

AUIRFU8405

Base part number

Package Type

Standard Pack

Form

Quantity

AUIRFU8405

I-Pak

Tube

75

AUIRFU8405

AUIRFR8405

D-Pak

Tube

75

AUIRFR8405

Tape and Reel Left

3000

AUIRFR8405TRL

Orderable Part Number

G D S

Gate Drain Source

G

S

D

D

S

G

D

Avalanche Characteristics

E

AS

Single Pulse Avalanche Energy (Thermally Limited) 208

E

AS

(tested)

Single Pulse Avalanche Energy (Tested Limited) 256

I

AR

Avalanche Current

See Fig. 14, 15, 24a, 24b

A

E

AR

Repetitive Avalanche Energy

mJ

mJ

Applications

Electric Power Steering (EPS)

Battery

Switch

Start/Stop Micro Hybrid

Heavy

Loads

DC-DC

Converter

AUIRFR/U8405

2

2015-10-12

Notes:

Calculated continuous current based on maximum allowable junction temperature. Bond wire current limit is 100A by source

bonding technology. Note that current limitations arising from heating of the device leads may occur with some lead mounting

arrangements. (Refer to AN-1140)

Repetitive rating; pulse width limited by max. junction temperature. (See fig. 11)

Limited by

T

Jmax ,

starting T

J

= 25°C, L = 0.051mH, R

G

= 50

, I

AS

= 90A, V

GS

=10V. Part not recommended for use above this value.

I

SD

90A, di/dt 1304A/µs, V

DD

V

(BR)DSS

, T

J

175°C.

Pulse width

400µs; duty cycle 2%.

C

oss eff

. (TR) is a fixed capacitance that gives the same charging time as C

oss

while V

DS

is rising from 0 to 80% V

DSS

.

C

oss eff

. (ER) is a fixed capacitance that gives the same energy as C

oss

while V

DS

is rising from 0 to 80% V

DSS

.

When mounted on 1" square PCB (FR-4 or G-10 Material). For recommended footprint and soldering techniques refer to

application note #AN-994

R

is measured at T

J

approximately 90°C

.

Pulse drain current is limited by source bonding technology.

**

All AC and DC test condition based on old Package

limitation current = 90A.

Static @ T

J

= 25°C (unless otherwise specified)

Parameter Min.

Typ.

Max.

Units

Conditions

V

(BR)DSS

Drain-to-Source Breakdown Voltage

40

––– –––

V V

GS

= 0V, I

D

= 250µA

V

(BR)DSS

/

T

J

Breakdown Voltage Temp. Coefficient

––– 0.03 ––– V/°C Reference to 25°C, I

D

= 5mA

R

DS(on)

Static Drain-to-Source On-Resistance

––– 1.65 1.98 m

V

GS

= 10V, I

D

= 90A**

V

GS(th)

Gate Threshold Voltage

2.2

3.0

3.9

V V

DS

= V

GS

, I

D

= 100µA

I

DSS

Drain-to-Source Leakage Current

––– ––– 1.0

µA

V

DS

= 40V, V

GS

= 0V

––– ––– 150

V

DS

= 40V,V

GS

= 0V,T

J

=125°C

I

GSS

Gate-to-Source Forward Leakage

–––

––– 100

nA

V

GS

= 20V

Gate-to-Source Reverse Leakage

–––

––– -100

V

GS

= -20V

R

G

Internal Gate Resistance

–––

2.3

–––

Dynamic Electrical Characteristics @ T

J

= 25°C (unless otherwise specified)

gfs

Forward Trans conductance

294

––– –––

S V

DS

= 10V, I

D

= 90A**

Q

g

Total Gate Charge

–––

103 155

nC

I

D

= 90A**

Q

gs

Gate-to-Source Charge

–––

26

–––

V

DS

= 20V

Q

gd

Gate-to-Drain Charge

–––

38

–––

V

GS

= 10V

Q

sync

Total Gate Charge Sync. (Q

g

- Q

gd

) –––

65

–––

t

d(on)

Turn-On Delay Time

–––

12

–––

ns

V

DD

= 26V

t

r

Rise Time

–––

80

–––

I

D

= 90A**

t

d(off)

Turn-Off Delay Time

–––

51

–––

R

G

= 2.7

t

f

Fall Time

–––

51

–––

V

GS

= 10V

C

iss

Input Capacitance

––– 5171 –––

pF

V

GS

= 0V

C

oss

Output Capacitance

–––

770 –––

V

DS

= 25V

C

rss

Reverse Transfer Capacitance

–––

523 –––

ƒ = 1.0MHz, See Fig. 5

C

oss eff.

(ER)

Effective Output Capacitance (Energy Related)

–––

939 –––

V

GS

= 0V, V

DS

= 0V to 32V

C

oss eff.

(TR)

Effective Output Capacitance (Time Related)

––– 1054 –––

V

GS

= 0V, V

DS

= 0V to 32V

Diode Characteristics

Parameter

Min. Typ. Max. Units

Conditions

I

S

Continuous Source Current

––– ––– 211

A

MOSFET symbol

(Body Diode)

showing the

I

SM

Pulsed Source Current

––– ––– 804

integral reverse

(Body Diode)

p-n junction diode.

V

SD

Diode Forward Voltage

–––

0.9

1.3

V T

J

= 25°C,I

S

= 90A** ,V

GS

= 0V

dv/dt

Peak Diode Recovery dv/dt

––– 2.1 –––

V/ns

T

J

= 175°C,I

S

= 90A** ,V

DS

= 40V

t

rr

Reverse Recovery Time

––– 28 –––

ns

T

J

= 25°C

––– 29 –––

T

J

= 125°C

Q

rr

Reverse Recovery Charge

––– 19 –––

nC

T

J

= 25°C

––– 20 –––

T

J

= 125°C

I

RRM

Reverse Recovery Current

–––

1.1

–––

A T

J

= 25°C

V

R

= 34V,

I

F

= 90A**

di/dt = 100A/µs

AUIRFR/U8405

3

2015-10-12

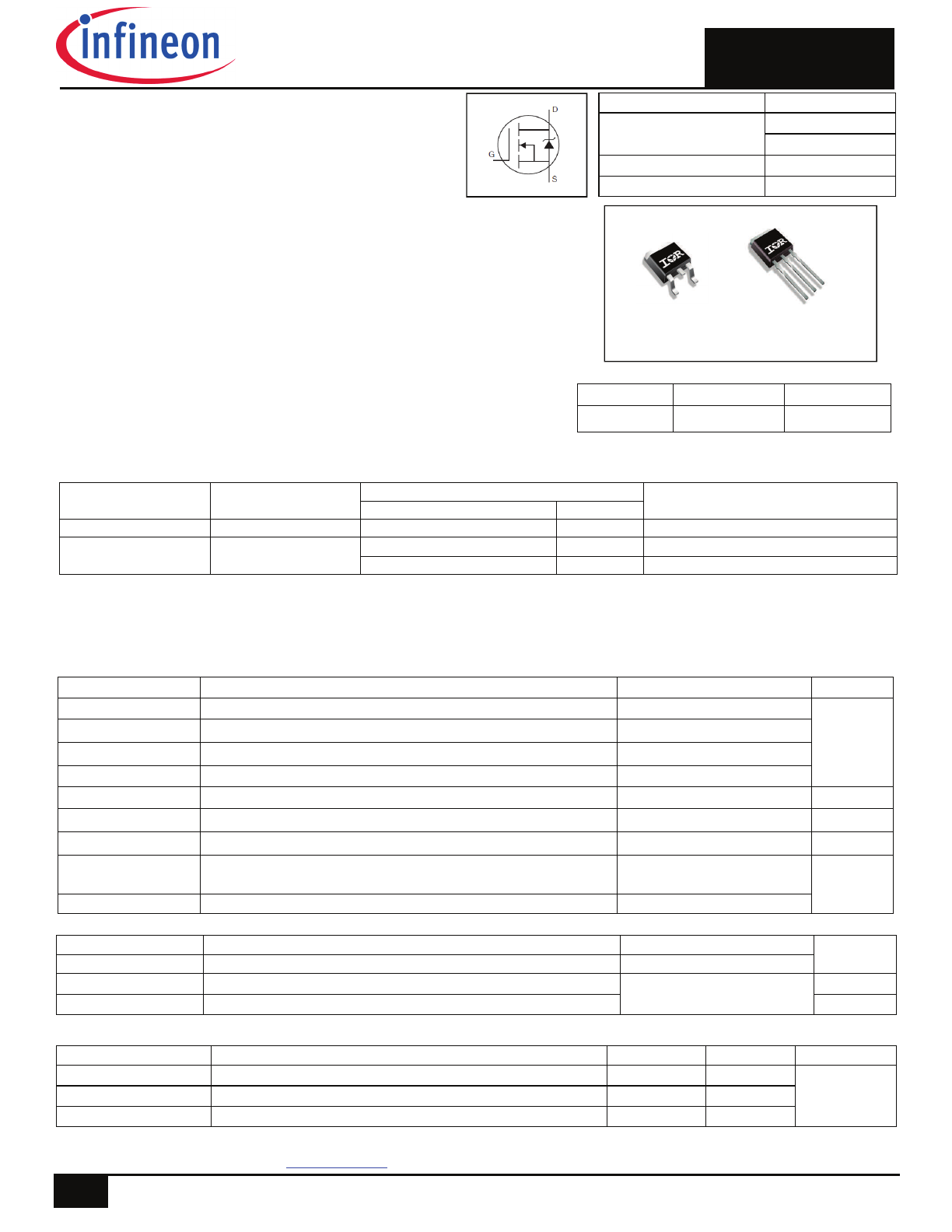

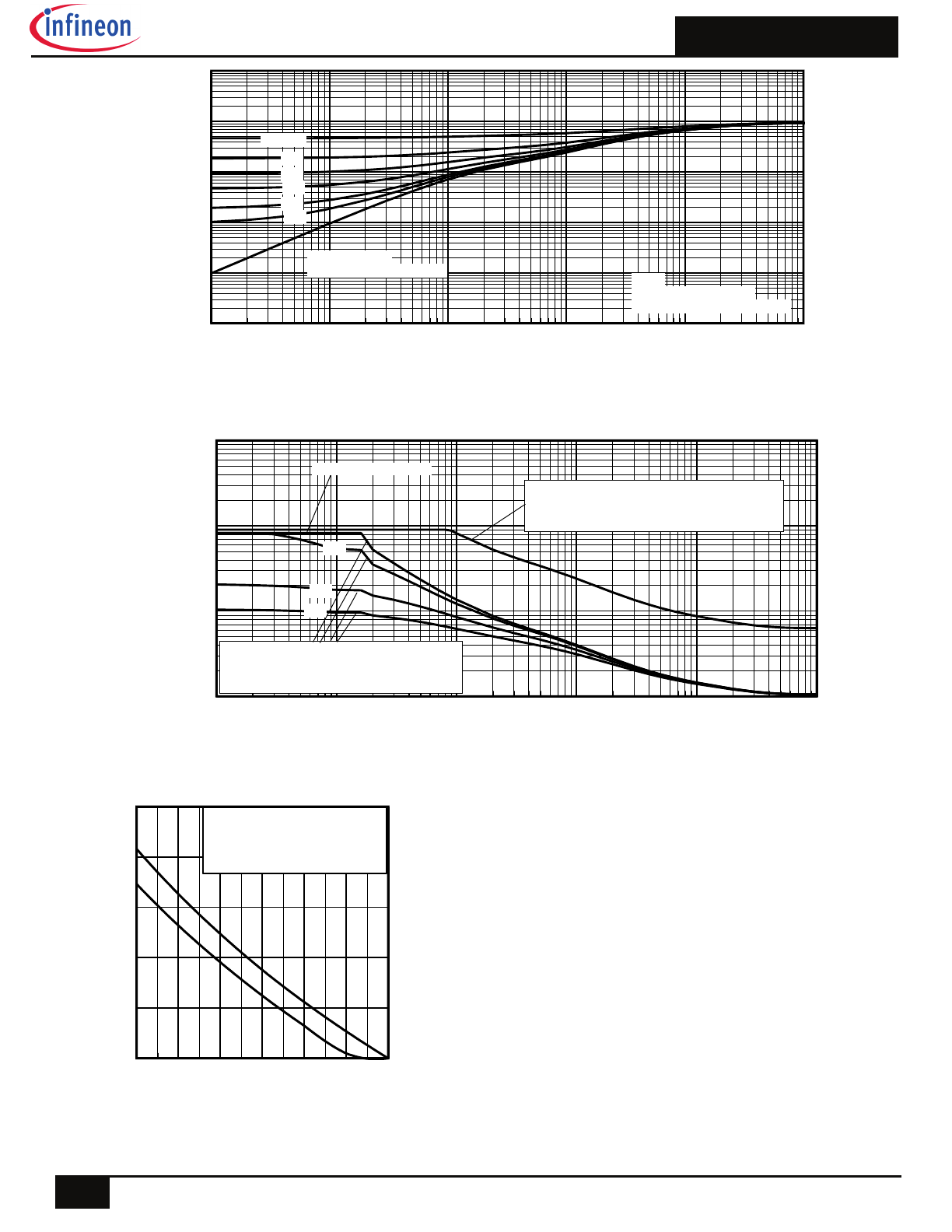

Fig. 2 Typical Output Characteristics

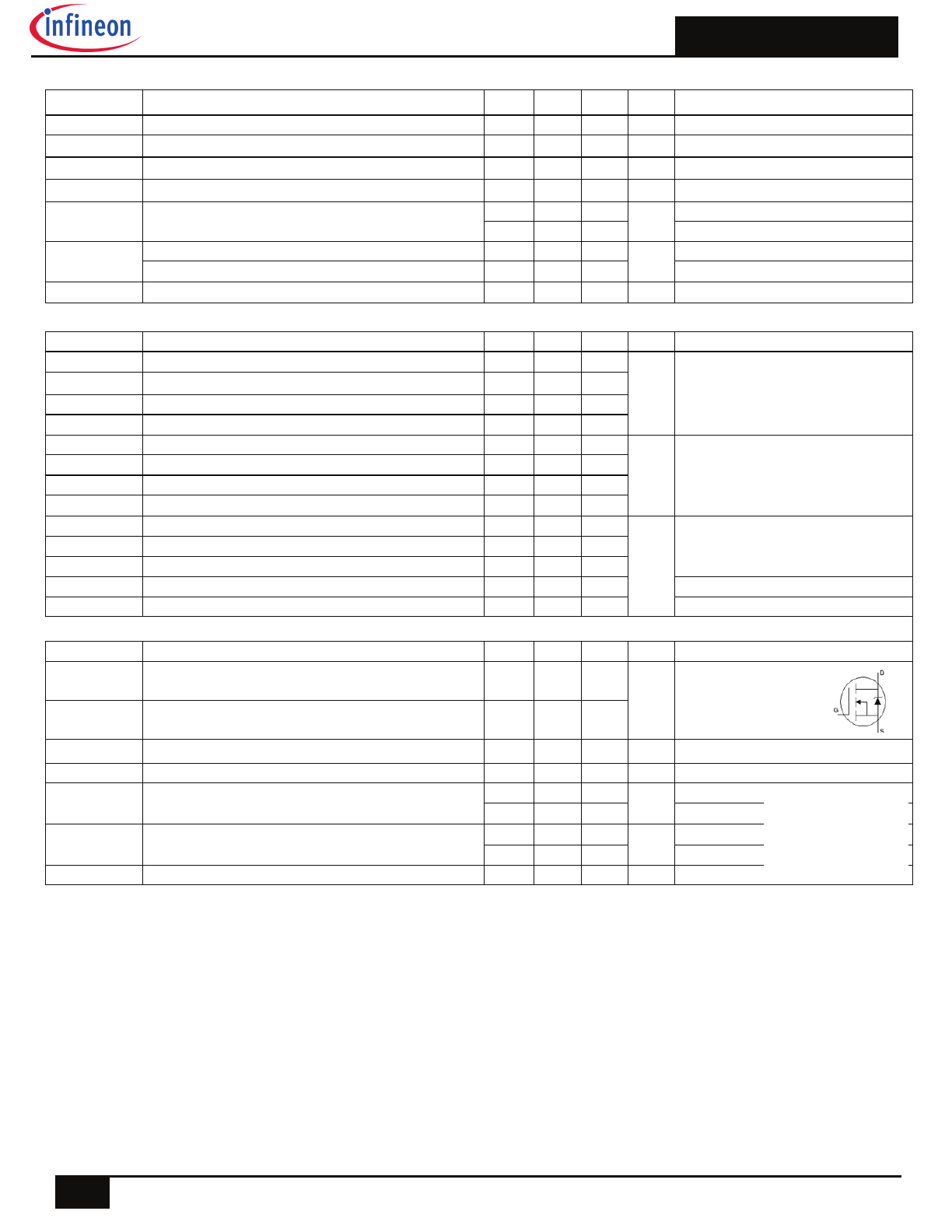

Fig. 3

Typical Transfer Characteristics

Fig. 1 Typical Output Characteristics

Fig 5. Typical Capacitance vs. Drain-to-Source Voltage

Fig 6. Typical Gate Charge vs. Gate-to-Source Voltage

Fig. 4 Normalized On-Resistance vs. Temperature

0.1

1

10

100

VDS, Drain-to-Source Voltage (V)

1

10

100

1000

I D

, D

ra

in

-t

o-

S

ou

rc

e

C

u

rr

en

t (

A

)

VGS

TOP 15V

10V

8.0V

7.0V

6.0V

5.5V

5.0V

BOTTOM

4.8V

60µs

PULSE WIDTH

Tj = 25°C

4.8V

0.1

1

10

100

VDS, Drain-to-Source Voltage (V)

10

100

1000

I D

, D

ra

in

-t

o-

S

ou

rc

e

C

u

rr

en

t (

A

)

60µs

PULSE WIDTH

Tj = 175°C

4.8V

VGS

TOP 15V

10V

8.0V

7.0V

6.0V

5.5V

5.0V

BOTTOM

4.8V

2

3

4

5

6

7

8

VGS, Gate-to-Source Voltage (V)

0.1

1

10

100

1000

I D

, D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(A

)

TJ = 25°C

TJ = 175°C

VDS = 10V

60µs PULSE WIDTH

-60

-20

20

60

100

140

180

TJ , Junction Temperature (°C)

0.4

0.8

1.2

1.6

2.0

R

D

S

(o

n)

,

D

ra

in

-t

o-

S

ou

rc

e

O

n

R

es

is

ta

nc

e

(

N

or

m

al

iz

ed

)

ID = 90A

VGS = 10V

0.1

1

10

100

VDS, Drain-to-Source Voltage (V)

100

1000

10000

100000

C

, C

ap

ac

ita

nc

e

(p

F

)

VGS = 0V, f = 1 MHZ

Ciss = Cgs + Cgd, C ds SHORTED

Crss = Cgd

Coss = Cds + Cgd

Coss

Crss

Ciss

0

20

40

60

80

100

120

140

QG, Total Gate Charge (nC)

0.0

2.0

4.0

6.0

8.0

10.0

12.0

14.0

V

G

S

, G

at

e-

to

-S

ou

rc

e

V

ol

ta

ge

(

V

)

VDS= 32V

VDS= 20V

ID = 90A

AUIRFR/U8405

4

2015-10-12

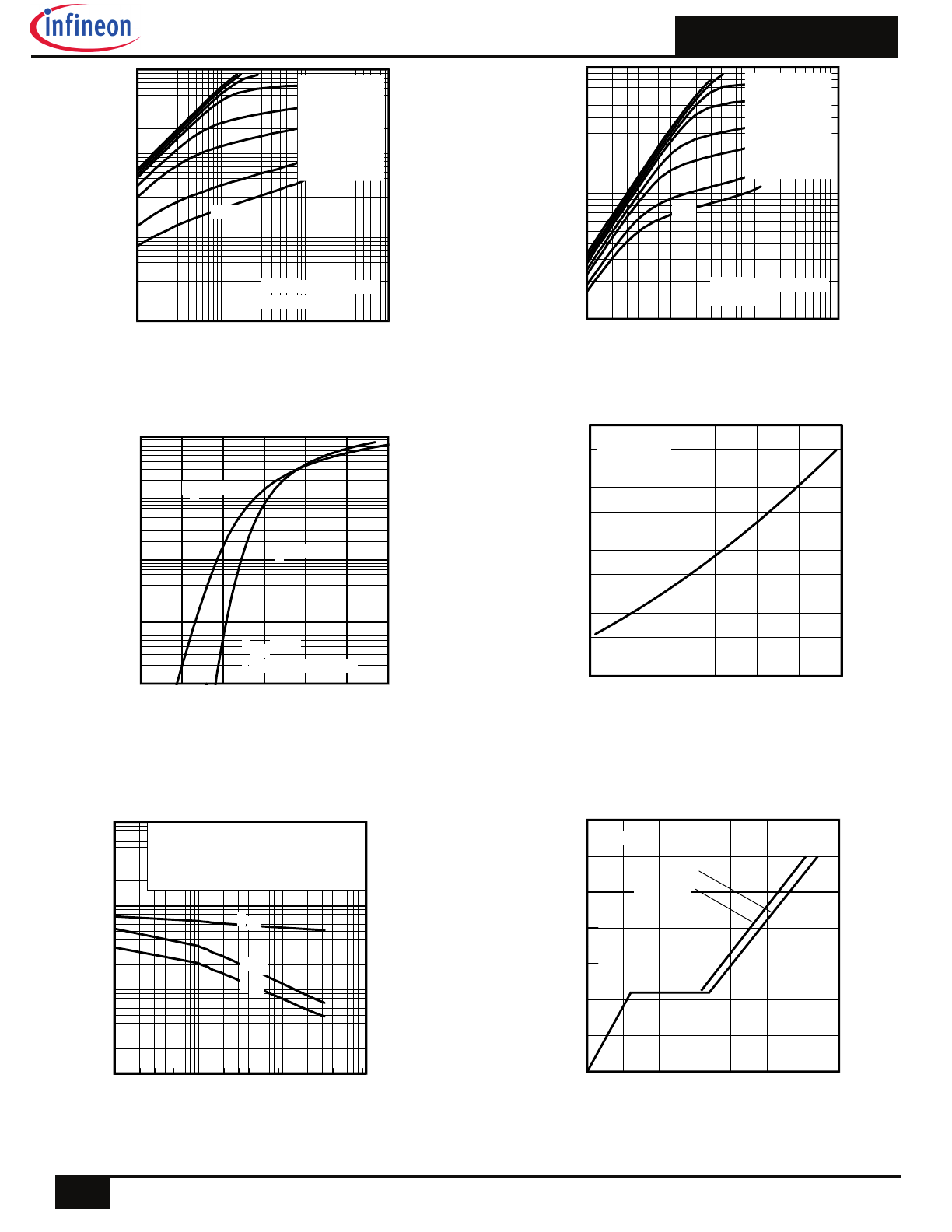

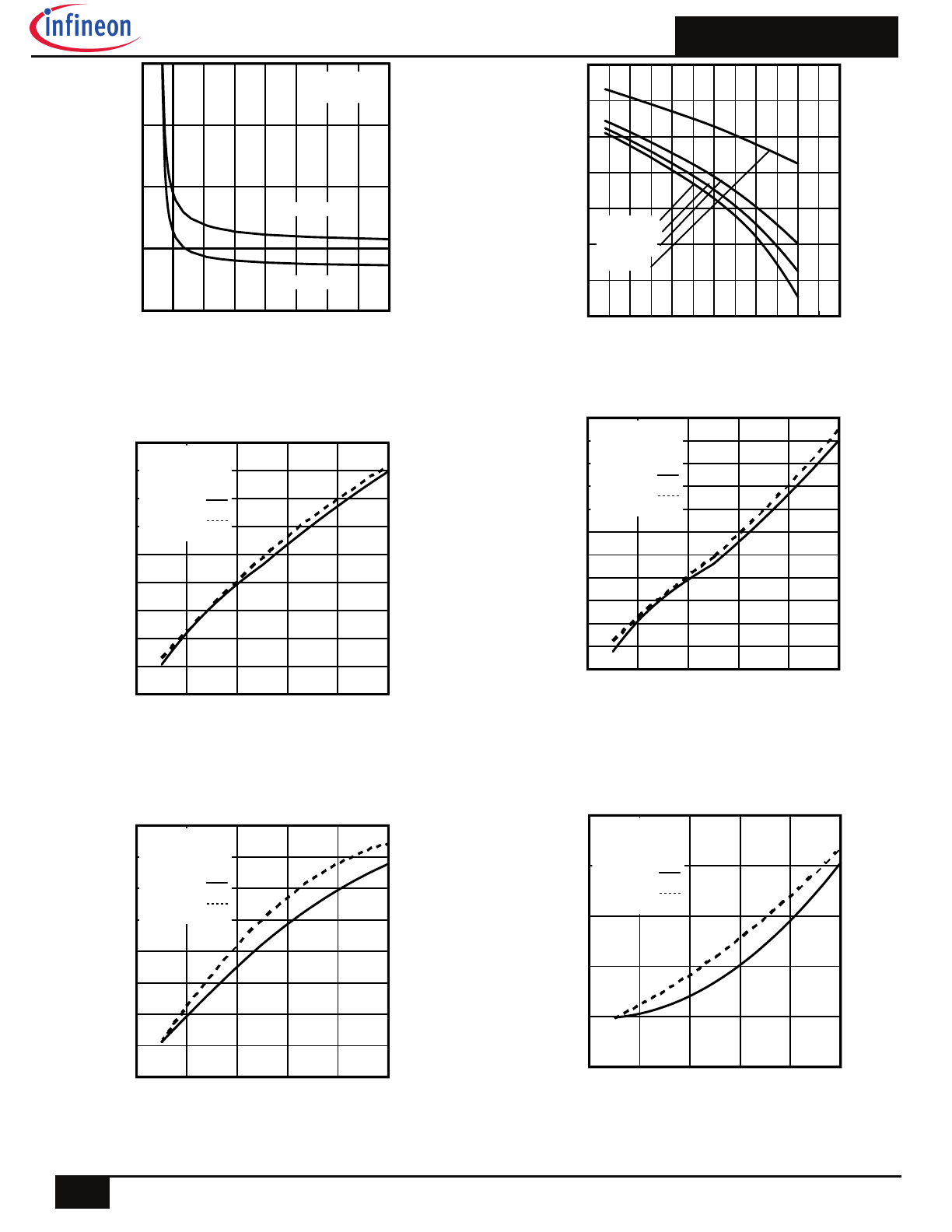

Fig 8. Maximum Safe Operating Area

Fig. 7 Typical Source-to-Drain Diode Forward Voltage

Fig. 9

Maximum Drain Current vs. Case Temperature

Fig. 11

Typical C

OSS

Stored Energy

0.2

0.6

1.0

1.4

1.8

VSD, Source-to-Drain Voltage (V)

0.1

1

10

100

1000

I S

D

, R

ev

er

se

D

ra

in

C

ur

re

nt

(

A

)

TJ = 25°C

TJ = 175°C

VGS = 0V

0.1

1

10

100

VDS, Drain-to-Source Voltage (V)

0.1

1

10

100

1000

10000

I D

,

D

ra

in

-t

o-

S

ou

rc

e

C

ur

re

nt

(

A

)

Tc = 25°C

Tj = 175°C

Single Pulse

1msec

10msec

OPERATION IN THIS AREA

LIMITED BY RDS(on)

100µsec

DC

Limited by Package

25

50

75

100

125

150

175

TC , Case Temperature (°C)

0

30

60

90

120

150

180

210

240

I D

,

D

ra

in

C

ur

re

nt

(

A

)

Limited By Package

-60

-20

20

60

100

140

180

TJ , Temperature ( °C )

40

41

42

43

44

45

46

47

48

V

(B

R

)D

S

S

, D

ra

in

-t

o-

S

ou

rc

e

B

re

ak

do

w

n

V

ol

ta

ge

(

V

)

Id = 5.0mA

-5

0

5

10 15 20 25 30 35 40 45

VDS, Drain-to-Source Voltage (V)

0.0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

E

ne

rg

y

(µ

J)

25

50

75

100

125

150

175

Starting TJ , Junction Temperature (°C)

0

100

200

300

400

500

600

700

800

900

E

A

S

,

S

in

gl

e

P

ul

se

A

va

la

nc

he

E

ne

rg

y

(m

J)

ID

TOP 18A

37A

BOTTOM 90A

Fig 12.

Maximum Avalanche Energy vs. Drain Current

Fig 10.

Drain-to-Source Breakdown Voltage

AUIRFR/U8405

5

2015-10-12

Notes on Repetitive Avalanche Curves , Figures 14, 15:

(For further info, see AN-1005 at www.infineon.com)

1. Avalanche failures assumption:

Purely a thermal phenomenon and failure occurs at a temperature far in

excess of T

jmax

. This is validated for every part type.

2. Safe operation in Avalanche is allowed as long as T

jmax

is not exceeded.

3. Equation below based on circuit and waveforms shown in Figures 22a, 22b.

4. P

D (ave)

= Average power dissipation per single avalanche pulse.

5. BV = Rated breakdown voltage (1.3 factor accounts for voltage increase

during

avalanche).

6. I

av

= Allowable avalanche current.

7.

T

=

Allowable rise in junction temperature, not to exceed

T

jmax

(assumed as

25°C in Figure 13, 14).

t

av =

Average time in avalanche.

D = Duty cycle in avalanche = t

av

·f

Z

thJC

(D, t

av

) = Transient thermal resistance, see Figures 13)

P

D (ave)

= 1/2 ( 1.3·BV·I

av

) =

T/ Z

thJC

I

av

= 2

T/ [1.3·BV·Z

th

]

E

AS (AR)

= P

D (ave)

·t

av

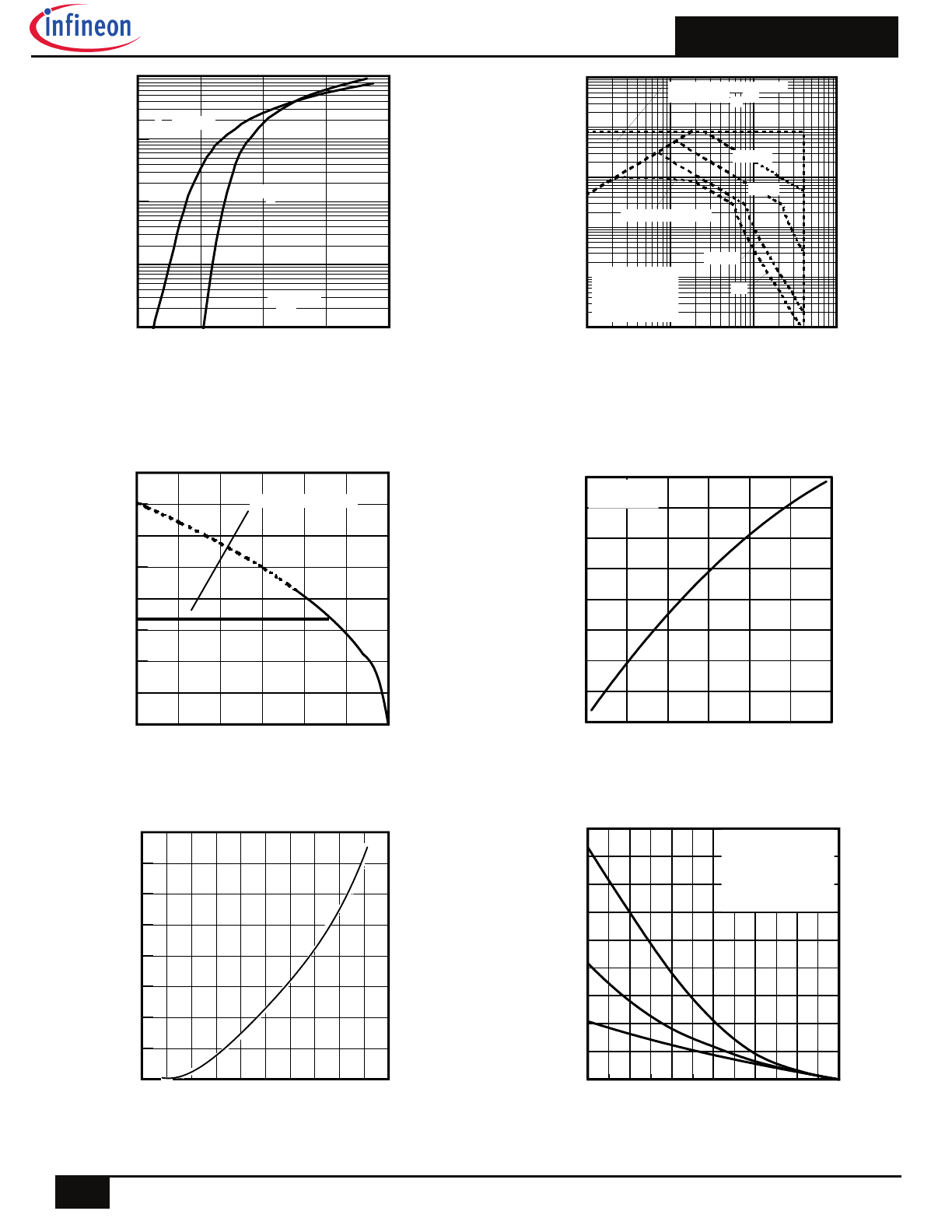

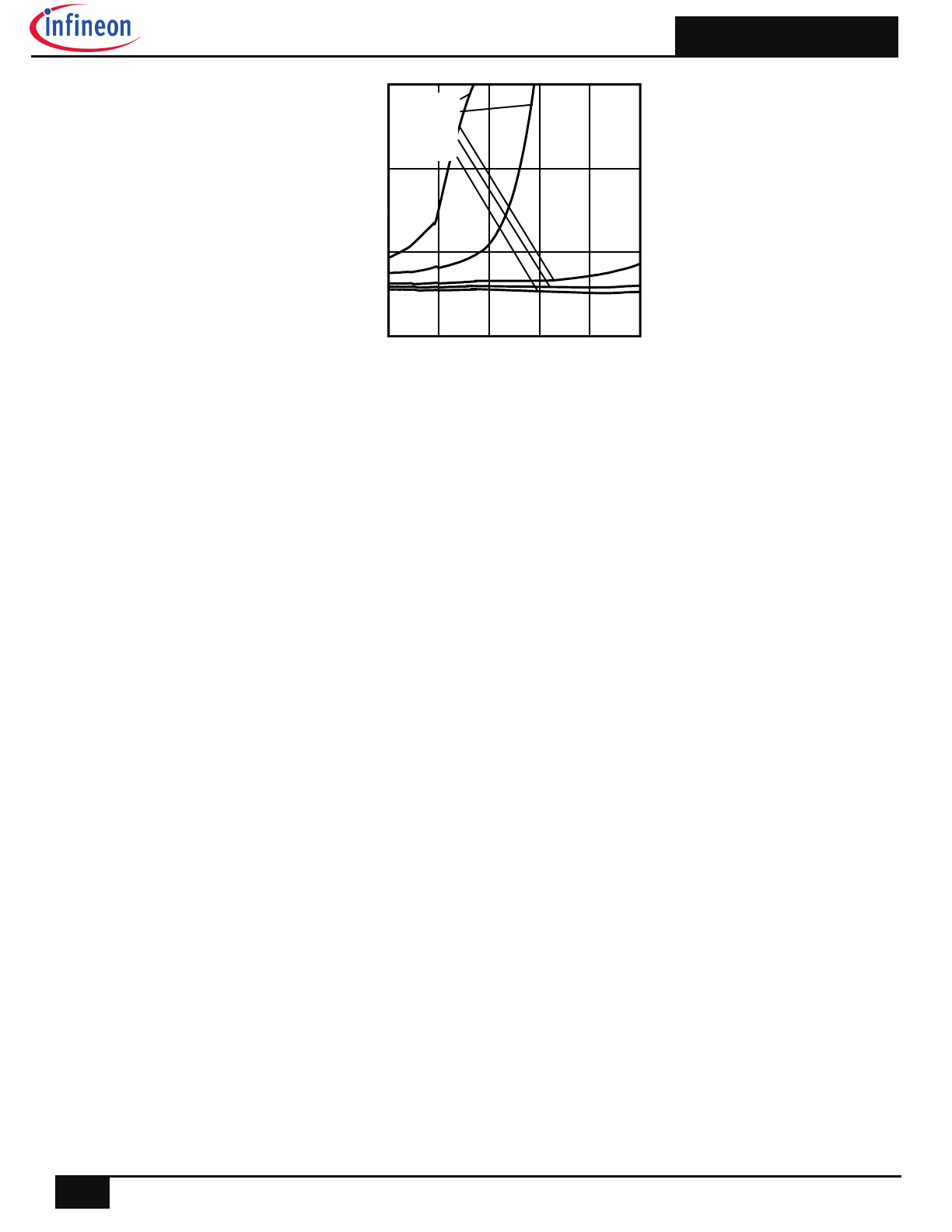

Fig 13. Maximum Effective Transient Thermal Impedance, Junction-to-Case

1E-006

1E-005

0.0001

0.001

0.01

0.1

t1 , Rectangular Pulse Duration (sec)

0.0001

0.001

0.01

0.1

1

10

T

he

rm

al

R

es

po

ns

e

(

Z

th

JC

)

°

C

/W

0.20

0.10

D = 0.50

0.02

0.01

0.05

SINGLE PULSE

( THERMAL RESPONSE )

Notes:

1. Duty Factor D = t1/t2

2. Peak Tj = P dm x Zthjc + Tc

1.0E-06

1.0E-05

1.0E-04

1.0E-03

1.0E-02

1.0E-01

tav (sec)

1

10

100

1000

A

va

la

nc

he

C

ur

re

nt

(

A

)

0.05

Duty Cycle = Single Pulse

0.10

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming j = 25°C and

Tstart = 150°C.

0.01

Allowed avalanche Current vs avalanche

pulsewidth, tav, assuming Tj = 150°C and

Tstart =25°C (Single Pulse)

25

50

75

100

125

150

175

Starting TJ , Junction Temperature (°C)

0

50

100

150

200

250

E

A

R

,

A

va

la

nc

he

E

ne

rg

y

(m

J)

TOP Single Pulse

BOTTOM 1.0% Duty Cycle

ID = 90A

Fig 15. Maximum Avalanche Energy Vs. Temperature

Fig 14. Typical Avalanche Current Vs. Pulse width

AUIRFR/U8405

6

2015-10-12

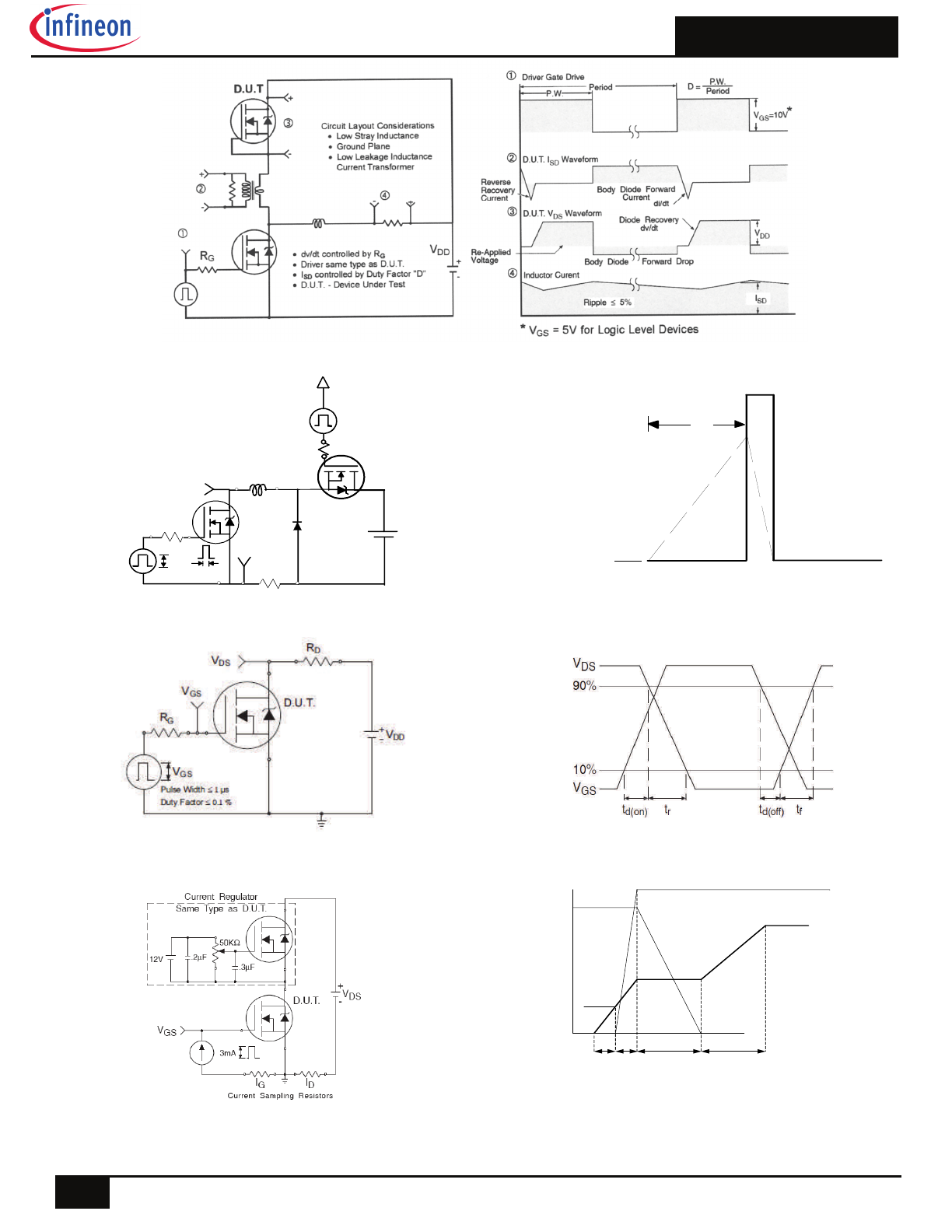

Fig 16. On-Resistance vs. Gate Voltage

Fig. 18 - Typical Recovery Current vs. di

f

/dt

Fig. 20 - Typical Recovery Current vs. di

f

/dt

Fig. 19 - Typical Stored Charge vs. di

f

/dt

Fig. 21 - Typical Stored Charge vs. di

f

/dt

4

6

8

10

12

14

16

18

20

VGS, Gate -to -Source Voltage (V)

0.0

2.0

4.0

6.0

8.0

R

D

S

(o

n)

,

D

ra

in

-t

o

-S

ou

rc

e

O

n

R

es

is

ta

nc

e

(

m

)

ID = 90A

TJ = 25°C

TJ = 125°C

-75

-25

25

75

125

175

225

TJ , Temperature ( °C )

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

V

G

S

(t

h)

, G

at

e

th

re

sh

ol

d

V

ol

ta

ge

(

V

)

ID = 100µA

ID = 250µA

ID = 1.0mA

ID = 1.0A

Fig. 17 - Threshold Voltage vs. Temperature

0

200

400

600

800

1000

diF /dt (A/µs)

0

1

2

3

4

5

6

7

8

9

I R

R

M

(

A

)

IF = 36A

VR = 34V

TJ = 25°C

TJ = 125°C

0

200

400

600

800

1000

diF /dt (A/µs)

10

20

30

40

50

60

70

80

90

100

110

120

Q

R

R

(

nC

)

IF = 36A

VR = 34V

TJ = 25°C

TJ = 125°C

0

200

400

600

800

1000

diF /dt (A/µs)

0

1

2

3

4

5

6

7

8

I R

R

M

(

A

)

IF = 90A

VR = 34V

TJ = 25°C

TJ = 125°C

0

200

400

600

800

1000

diF /dt (A/µs)

0

20

40

60

80

100

Q

R

R

(

nC

)

IF = 90A

VR = 34V

TJ = 25°C

TJ = 125°C

AUIRFR/U8405

7

2015-10-12

Fig 22. Typical On-Resistance vs. Drain Current

0

100

200

300

400

500

ID, Drain Current (A)

0.0

3.0

6.0

9.0

R

D

S

(o

n)

,

D

ra

in

-t

o

-S

ou

rc

e

O

n

R

es

is

ta

nc

e

(m

)

VGS = 5.5V

VGS = 6.0V

VGS = 7.0V

VGS = 8.0V

VGS = 10V

AUIRFR/U8405

8

2015-10-12

Fig 23. Peak Diode Recovery dv/dt Test Circuit for N-Channel HEXFET® Power MOSFETs

Fig 25a. Switching Time Test Circuit

Fig 25b. Switching Time Waveforms

Fig 24a. Unclamped Inductive Test Circuit

RG

IAS

0.01

tp

D.U.T

L

VDS

+

- VDD

DRIVER

A

15V

20V

Fig 24b. Unclamped Inductive Waveforms

tp

V

(BR)DSS

I

AS

Fig 26b. Gate Charge Waveform

Vds

Vgs

Id

Vgs(th)

Qgs1 Qgs2

Qgd

Qgodr

Fig 26a. Gate Charge Test Circuit

AUIRFR/U8405

9

2015-10-12

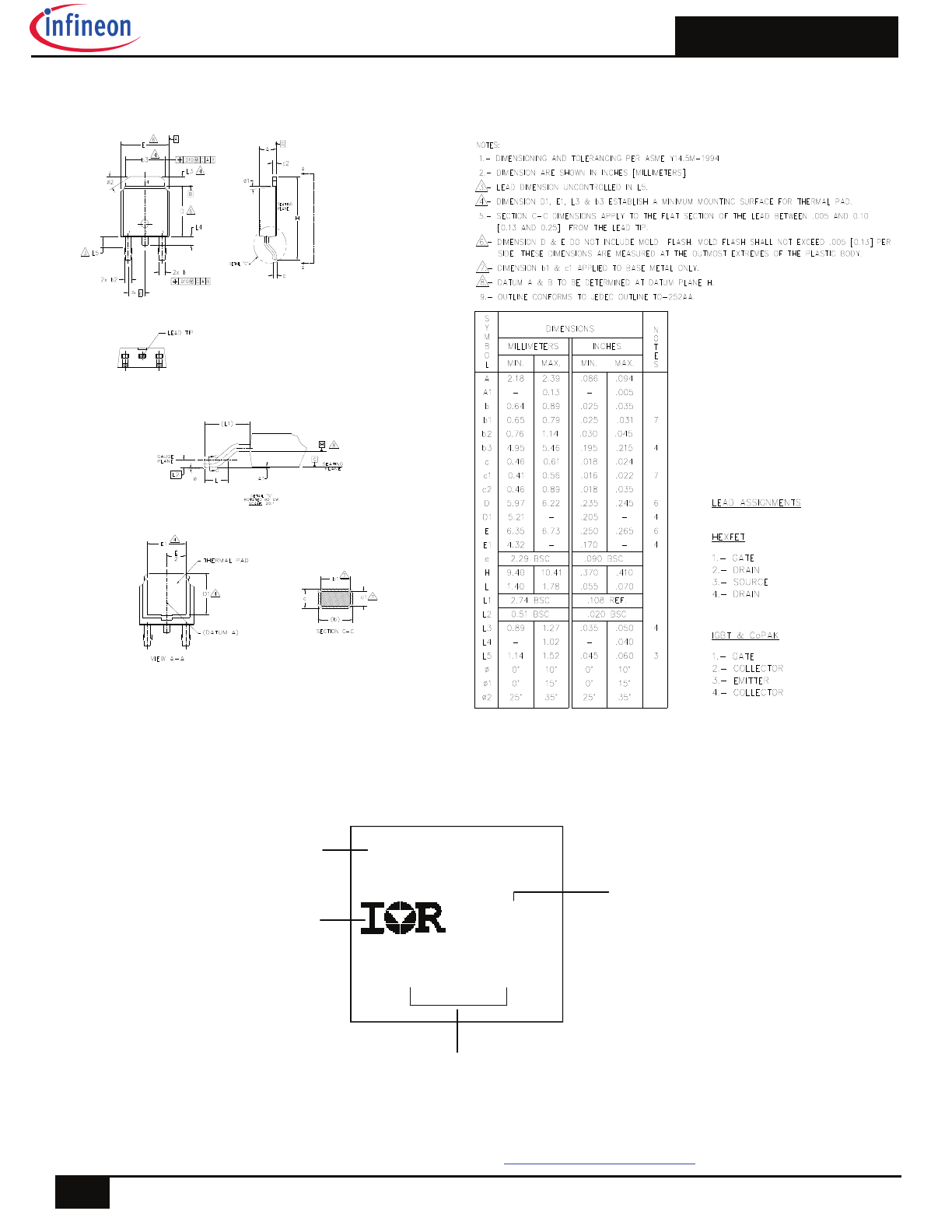

Note: For the most current drawing please refer to IR website at

http://www.irf.com/package/

D-Pak (TO-252AA) Package Outline (Dimensions are shown in millimeters (inches))

YWWA

XX

XX

Date Code

Y= Year

WW= Work Week

AUFR8405

Lot Code

Part Number

IR Logo

D-Pak (TO-252AA) Part Marking Information

AUIRFR/U8405

10

2015-10-12

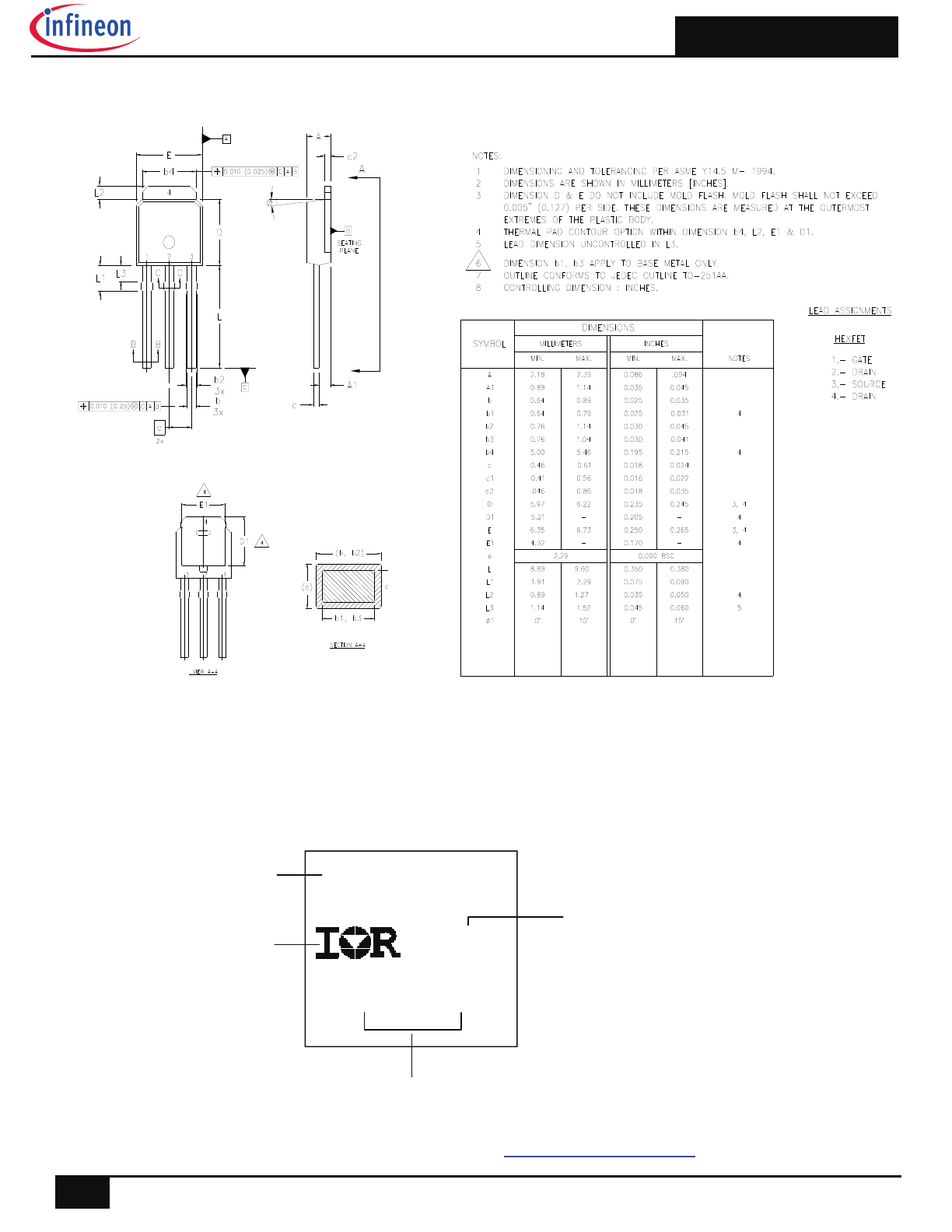

I-Pak (TO-251AA) Part Marking Information

YWWA

XX

XX

Date Code

Y= Year

WW= Work Week

AUFU8405

Lot Code

Part Number

IR Logo

I-Pak (TO-251AA) Package Outline (Dimensions are shown in millimeters (inches)

Note: For the most current drawing please refer to IR website at

http://www.irf.com/package/