2013-2015 Microchip Technology Inc.

DS00001570C-page 1

General Description

The CAP1208 is a multiple channel capacitive touch

sensor controller. It contains

eight (8) individual capac-

itive touch sensor inputs with programmable sensitivity

for use in touch sensor applications. Each sensor input

is calibrated to compensate for system parasitic capac-

itance and automatically recalibrated to compensate

for gradual environmental changes.

The CAP1208 includes Multiple Pattern Touch recogni-

tion that allows the user to select a specific set of but-

tons to be touched simultaneously. If this pattern is

detected, a status bit is set and an interrupt is gener-

ated.

The CAP1208 has Active and Standby states, each

with its own sensor input configuration controls. Power

consumption in the Standby state is dependent on the

number of sensor inputs enabled as well as averaging,

sampling time, and cycle time. Deep Sleep is the low-

est power state available, drawing 5μA (typical) of cur-

rent. In this state, no sensor inputs are active, and

communications will wake the device.

Applications

• Desktop and Notebook PCs

• LCD Monitors

• Consumer Electronics

• Appliances

Features

• Eight (8) Capacitive Touch Sensor Inputs

- Programmable sensitivity

- Automatic recalibration

- Calibrates for parasitic capacitance

- Individual thresholds for each button

• Multiple Button Pattern Detection

• Power Button Support

• Press and Hold Feature for Volume-like Applica-

tions

• 3.3V or 5V Supply

• Analog Filtering for System Noise Sources

• RF Detection and Avoidance Filters

• Digital EMI Blocker

• 8kV ESD Rating on All Pins (HBM)

• Low Power Operation

- 5μA quiescent current in Deep Sleep

- 50μA quiescent current in Standby (1 sensor

input monitored)

- Samples one or more channels in Standby

• SMBus / I

2

C Compliant Communication Interface

• Available in a 16-pin 3mm x 3mm QFN RoHS

compliant package

• Available in a 14-pin SOIC RoHS compliant pack-

age

CAP1208

8-Channel Capacitive Touch Sensor

CAP1208

DS00001570C-page 2

2013-2015 Microchip Technology Inc.

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at

docerrors@microchip.com

. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for cur-

rent devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the

revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site;

http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are

using.

Customer Notification System

Register on our web site at

www.microchip.com

to receive the most current information on all of our products.

2013-2015 Microchip Technology Inc.

DS00001570C-page 3

CAP1208

Table of Contents

1.0 Introduction ..................................................................................................................................................................................... 4

2.0 Pin Description and Configuration ................................................................................................................................................... 8

3.0 Functional Description .................................................................................................................................................................. 21

4.0 Register Descriptions .................................................................................................................................................................... 58

5.0 Operational Characteristics ........................................................................................................................................................... 69

6.0 Package Outline ............................................................................................................................................................................ 85

Appendix A: Data Sheet Revision History ........................................................................................................................................... 91

The Microchip Web Site ...................................................................................................................................................................... 93

Customer Change Notification Service ............................................................................................................................................... 93

Customer Support ............................................................................................................................................................................... 93

Product Identification System ............................................................................................................................................................. 94

CAP1208

DS00001570C-page 4

2013-2015 Microchip Technology Inc.

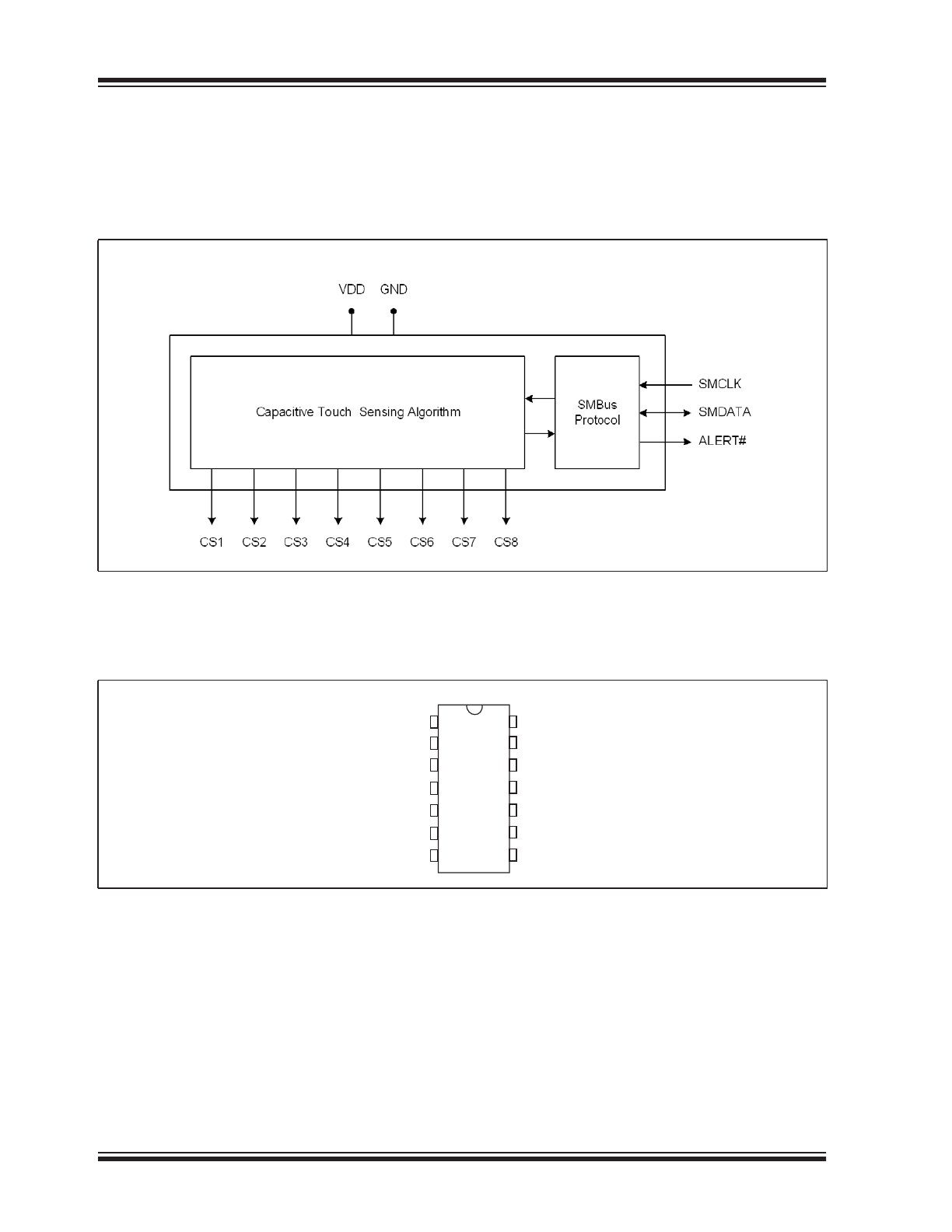

1.0

INTRODUCTION

1.1

Block Diagram

1.2

Pin Diagrams

FIGURE 1-1:

CAP1208 BLOCK DIAGRAM

FIGURE 1-2:

CAP1208 14-PIN SOIC

CAP1208

1

2

3

4

14

13

12

11

5

6

7

10

9

8

CS2

CS1

ALERT#

SMDAT

SMCLK

N/C

CS3

CS4

CS5

CS6

CS7

CS8

GND

VDD

2013-2015 Microchip Technology Inc.

DS00001570C-page 5

CAP1208

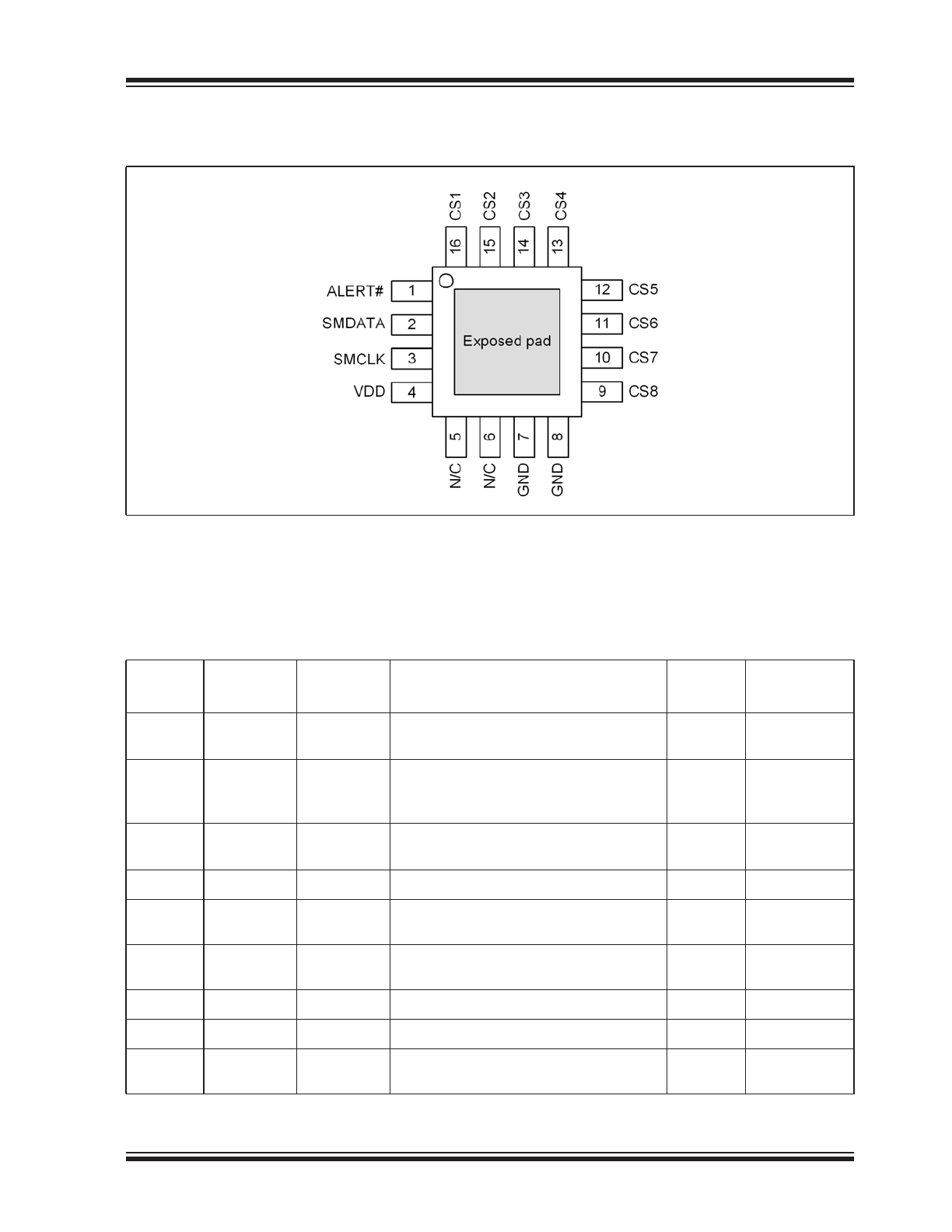

1.3

Pin Description

FIGURE 1-3:

CAP1208 PIN DIAGRAM (16-PIN QFN)

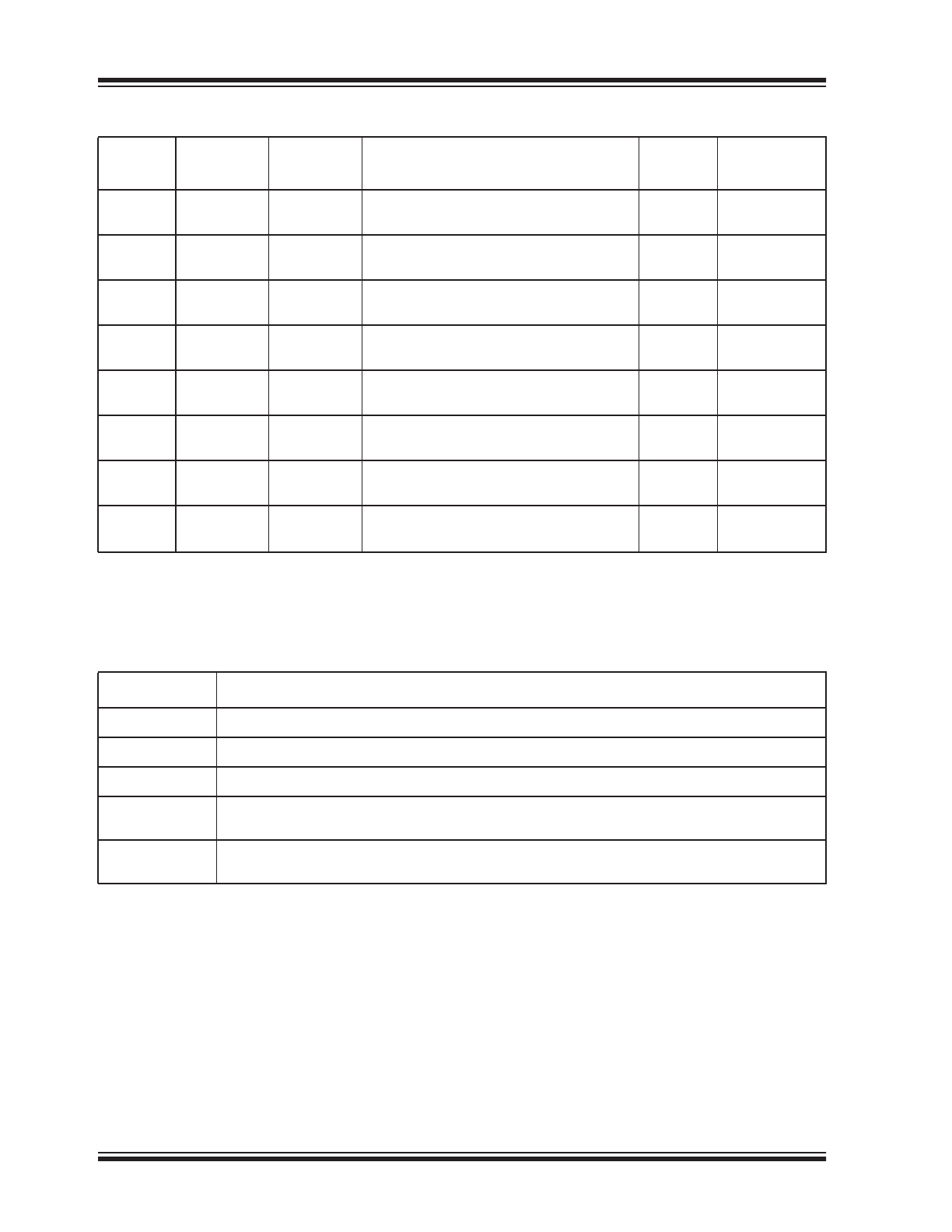

TABLE 1-1:

PIN DESCRIPTION FOR CAP1208

QFN Pin

#

SOIC Pin #

Pin Name

Pin Function

Pin Type

Unused

Connection

1

3

ALERT#

ALERT# - Active low alert / interrupt out-

put for SMBus alert

OD

Connect to

Ground

2

4

SMDATA

SMDATA - Bi-directional, open-drain

SMBus or I

2

C data - requires pull-up

resistor

DIOD

n/a

3

5

SMCLK

SMCLK - SMBus or I

2

C clock input -

requires pull-up resistor

DI

n/a

4

7

VDD

Positive Power supply

Power

n/a

5

6

N/C

Not internally connected

n/a

Connect to

Ground

6

-

N/C

Not internally connected

n/a

Connect to

Ground

7

8

GND

Ground

Power

n/a

8

-

GND

Ground

Power

n/a

9

9

CS8

Capacitive Touch Sensor Input 8

AIO

Connect to

Ground

CAP1208

DS00001570C-page 6

2013-2015 Microchip Technology Inc.

APPLICATION NOTE:

All digital pins are 5V tolerant pins.

The pin types are described in

Table 1-2, "Pin Types"

.

10

10

CS7

Capacitive Touch Sensor Input 7

AIO

Connect to

Ground

11

11

CS6

Capacitive Touch Sensor Input 6

AIO

Connect to

Ground

12

12

CS5

Capacitive Touch Sensor Input 5

AIO

Connect to

Ground

13

13

CS4

Capacitive Touch Sensor Input 4

AIO

Connect to

Ground

14

14

CS3

Capacitive Touch Sensor Input 3

AIO

Connect to

Ground

15

1

CS2

Capacitive Touch Sensor Input 2

AIO

Connect to

Ground

16

2

CS1

Capacitive Touch Sensor Input 1

AIO

Connect to

Ground

Bottom

pad

-

Exposed

pad

Not internally connected, but recommend

grounding

-

-

TABLE 1-2:

PIN TYPES

Pin Type

Description

Power

This pin is used to supply power or ground to the device.

DI

Digital Input - This pin is used as a digital input. This pin is 5V tolerant.

AIO

Analog Input / Output - This pin is used as an I/O for analog signals.

DIOD

Digital Input / Open Drain Output - This pin is used as a digital I/O. When it is used as an

output, it is open drain and requires a pull-up resistor. This pin is 5V tolerant.

OD

Open Drain Digital Output - This pin is used as a digital output. It is open drain and requires

a pull-up resistor. This pin is 5V tolerant.

TABLE 1-1:

PIN DESCRIPTION FOR CAP1208 (CONTINUED)

QFN Pin

#

SOIC Pin #

Pin Name

Pin Function

Pin Type

Unused

Connection

2013-2015 Microchip Technology Inc.

DS00001570C-page 7

CAP1208

2.0

ELECTRICAL SPECIFICATIONS

Note 2-1

Stresses above those listed could cause permanent damage to the device. This is a stress rating

only and functional operation of the device at any other condition above those indicated in the

operation sections of this specification is not implied.

Note 2-2

For the 5V tolerant pins that have a pull-up resistor, the voltage difference between V

5VT_PIN

and V

DD

must never exceed 3.6V.

Note 2-3

The Package Power Dissipation specification assumes a recommended thermal via design consisting

of a 2x2 matrix of 0.3mm (12mil) vias at 1.0mm pitch connected to the ground plane with a 1.6 x

1.6mm thermal landing.

Note 2-4

Junction to Ambient (

JA

) is dependent on the design of the thermal vias. Without thermal vias and

a thermal landing, the

JA

will be higher.

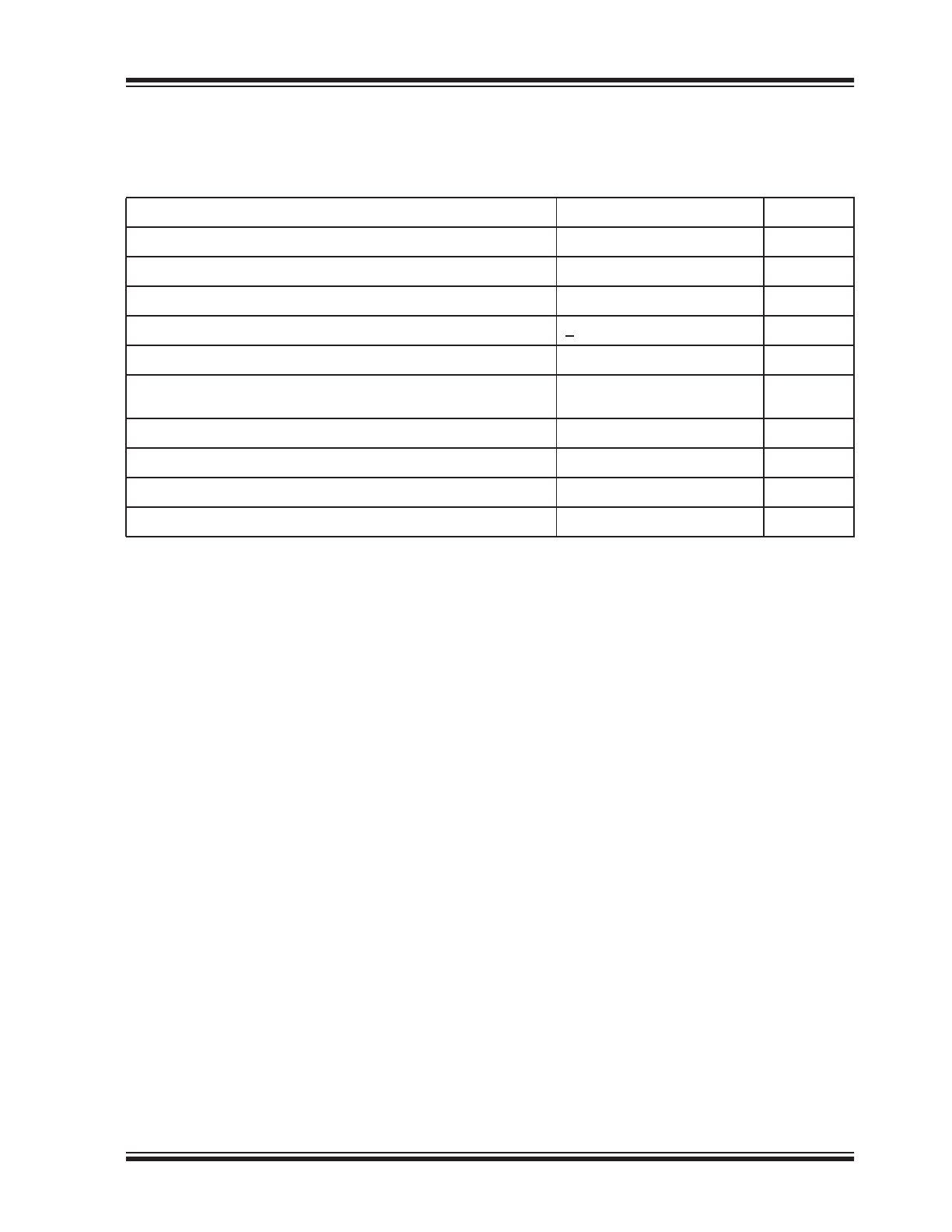

TABLE 2-1:

ABSOLUTE MAXIMUM RATINGS

Voltage on VDD pin

-0.3 to 6.5

V

Voltage on CS pins to GND

-0.3 to 4.0

V

Voltage on 5V tolerant pins (V

5VT_PIN

)

-0.3 to 5.5

V

Voltage on 5V tolerant pins (|V

5VT_PIN

- V

DD

|) (see

Note 2-2

)

0 to 3.6

V

Input current to any pin except VDD

+10

mA

Output short circuit current

Continuous

N/A

Package Power Dissipation up to T

A

= 85°C for 16-pin QFN

(see

Note 2-3

)

0.5

W

Junction to Ambient (

JA

) (see

Note 2-4

)

70

°C/W

Operating Ambient Temperature Range

-40 to 125

°C

Storage Temperature Range

-55 to 150

°C

ESD Rating, All Pins, HBM

8000

V

CAP1208

DS00001570C-page 8

2013-2015 Microchip Technology Inc.

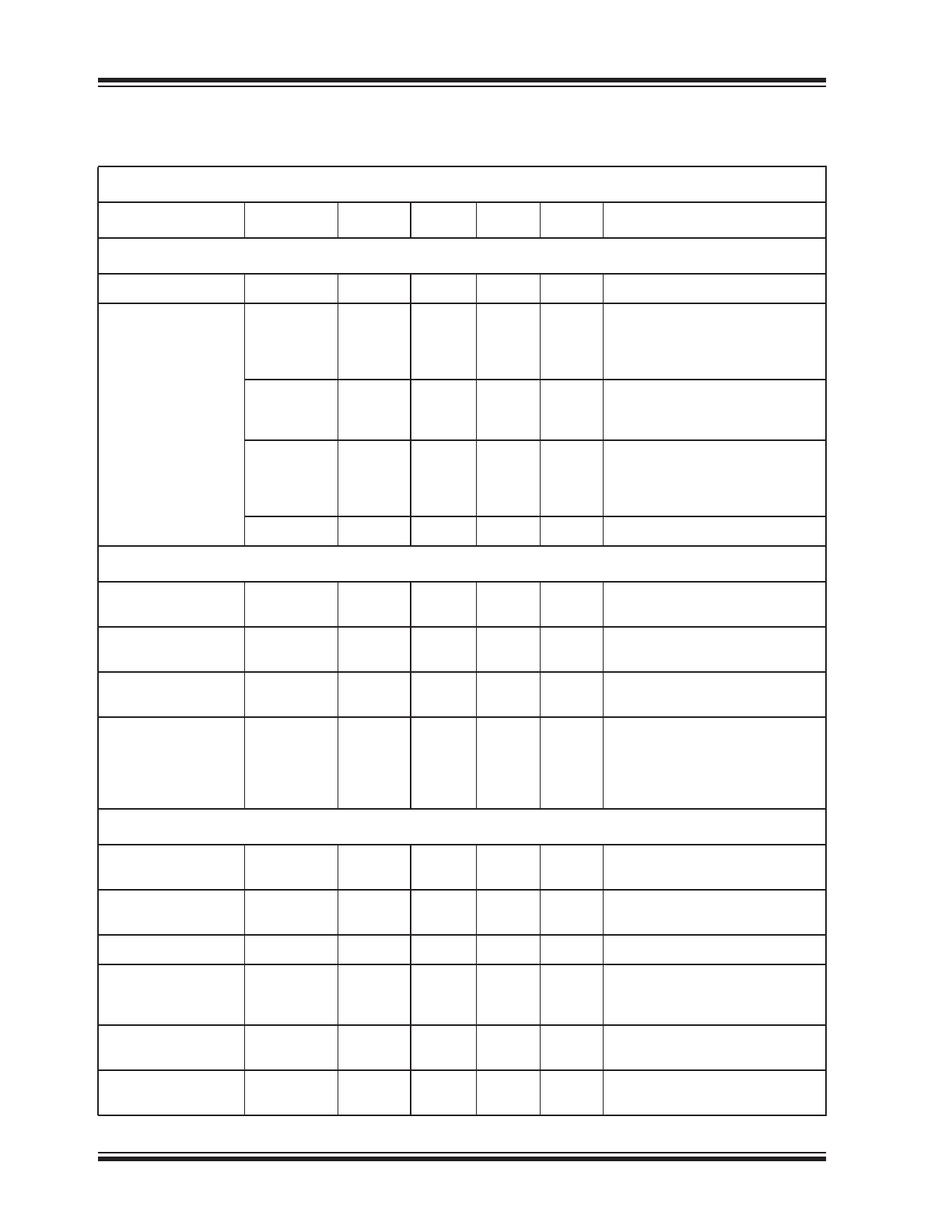

TABLE 2-2:

ELECTRICAL SPECIFICATIONS

V

DD

= 3V to 5.5V, T

A

= 0°C to 85°C, all Typical values at T

A

= 25°C unless otherwise noted.

Characteristic

Symbol

Min

Typ

Max

Unit

Conditions

DC Power

Supply Voltage

V

DD

3.0

5.5

V

Supply Current

I

STBY_DEF

120

170

μA

Standby state active

1 sensor input monitored

Default conditions (8 avg, 70ms

cycle time)

I

STBY_LP

50

μA

Standby state active

1 sensor input monitored

1 avg, 140ms cycle time

I

DSLEEP_3V

5

TBD

μA

Deep Sleep state active

No communications

T

A

< 40°C

3.135 < V

DD

< 3.465V

I

DD

500

750

μA

Capacitive Sensing Active

Capacitive Touch Sensor Inputs

Maximum Base

Capacitance

C

BASE

50

pF

Pad untouched

Minimum Detectable

Capacitive Shift

C

TOUCH

20

fF

Pad touched - default conditions

Recommended Cap

Shift

C

TOUCH

0.1

2

pF

Pad touched - Not tested

Power Supply

Rejection

PSR

±3

±10

counts

/ V

Untouched Current Counts

Base Capacitance 5pF - 50pF

Negative Delta Counts disabled

Maximum sensitivity

All other parameters default

Power-On and Brown-out Reset (see

Section 4.2, "Reset"

)

Power-On Reset

Voltage

V

POR

1

1.3

V

Pin States Defined

Power-On Reset

Release Voltage

V

PORR

2.85

V

Rising V

DD

Ensured by design

Brown-Out Reset

V

BOR

2.8

V

Falling V

DD

VDD Rise Rate

(ensures internal

POR signal)

SV

DD

0.05

V/ms

0 to 3V in 60ms

Power-Up Timer

Period

t

PWRT

10

ms

Brown-Out Reset

Voltage Delay

t

BORDC

1

μs

V

DD

= V

BOR

- 1

2013-2015 Microchip Technology Inc.

DS00001570C-page 9

CAP1208

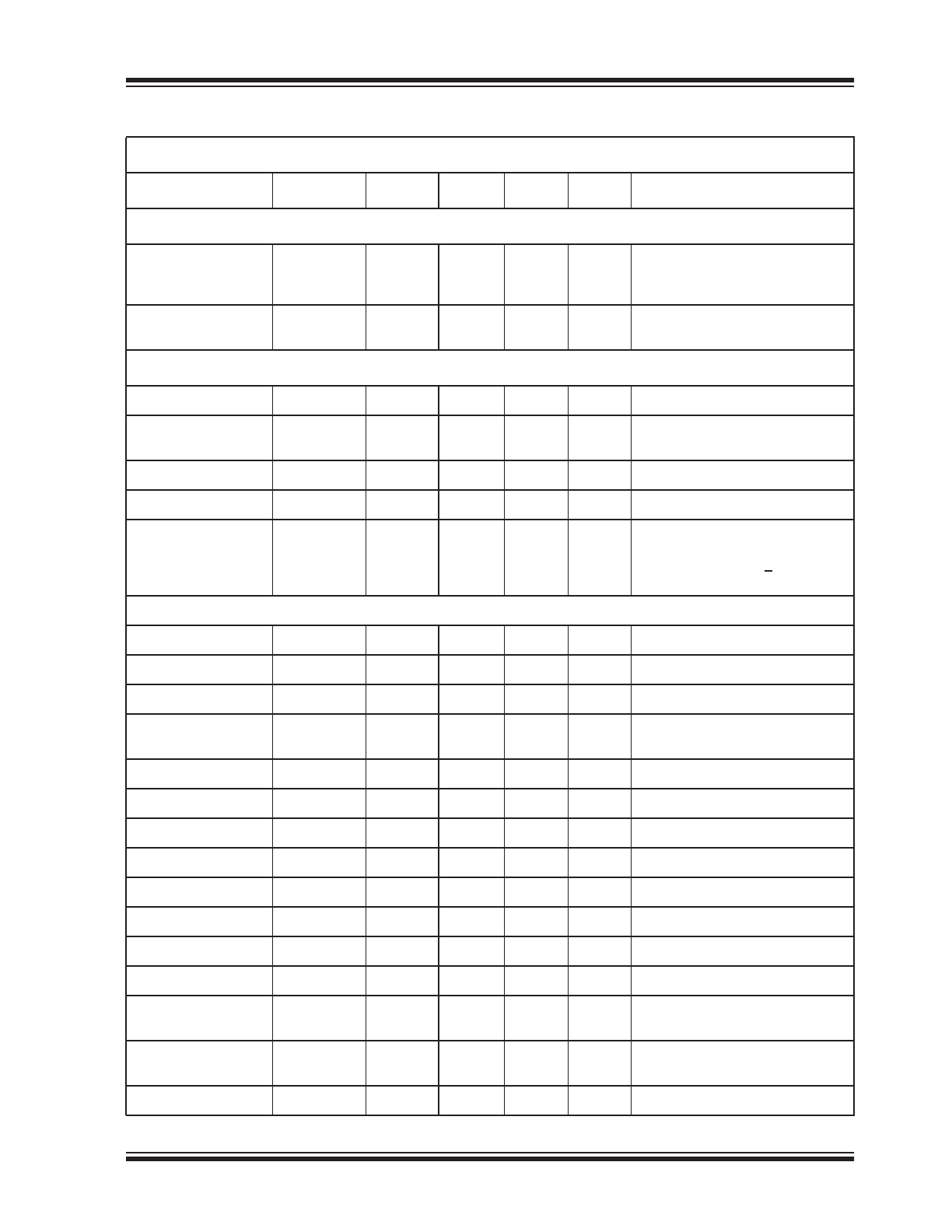

Timing

Time to

Communications

Ready

t

COMM_DLY

15

ms

Time to First

Conversion Ready

t

CONV_DLY

170

200

ms

I/O Pins

Output Low Voltage

V

OL

0.4

V

I

SINK_IO

= 8mA

Output High Voltage

V

OH

V

DD

-

0.4

V

I

SOURCE_IO

= 8mA

Input High Voltage

V

IH

2.0

V

Input Low Voltage

V

IL

0.8

V

Leakage Current

I

LEAK

±5

μA

powered or unpowered

T

A

< 85°C

pull-up voltage < 3.6V if

unpowered

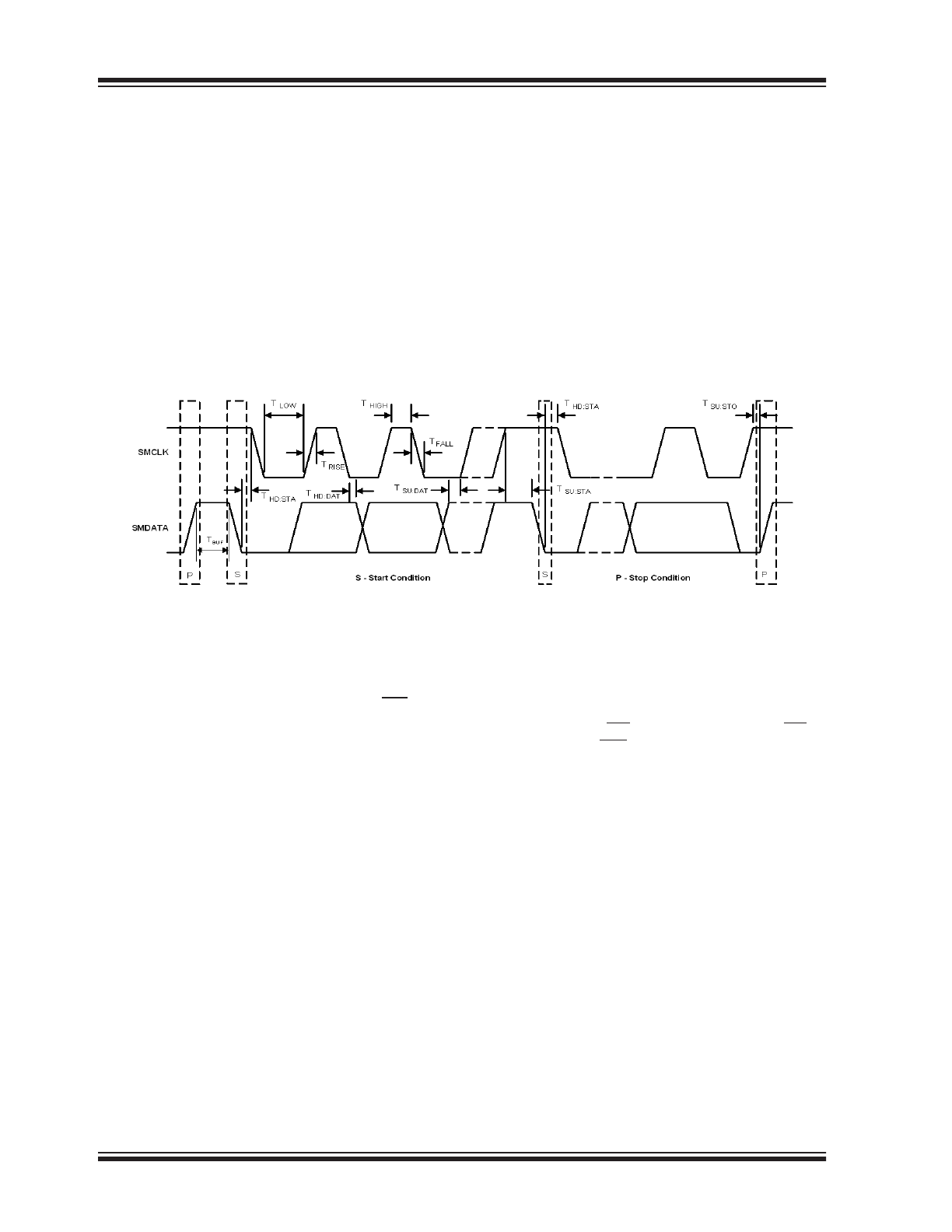

SMBus Timing

Input Capacitance

C

IN

5

pF

Clock Frequency

f

SMB

10

400

kHz

Spike Suppression

t

SP

50

ns

Bus Free Time Stop

to Start

t

BUF

1.3

μs

Start Setup Time

t

SU:STA

0.6

μs

Start Hold Time

t

HD:STA

0.6

μs

Stop Setup Time

t

SU:STO

0.6

μs

Data Hold Time

t

HD:DAT

0

μs

When transmitting to the master

Data Hold Time

t

HD:DAT

0.3

μs

When receiving from the master

Data Setup Time

t

SU:DAT

0.6

μs

Clock Low Period

t

LOW

1.3

μs

Clock High Period

t

HIGH

0.6

μs

Clock / Data Fall

Time

t

FALL

300

ns

Min = 20+0.1C

LOAD

ns

Clock / Data Rise

Time

t

RISE

300

ns

Min = 20+0.1C

LOAD

ns

Capacitive Load

C

LOAD

400

pF

per bus line

TABLE 2-2:

ELECTRICAL SPECIFICATIONS (CONTINUED)

V

DD

= 3V to 5.5V, T

A

= 0°C to 85°C, all Typical values at T

A

= 25°C unless otherwise noted.

Characteristic

Symbol

Min

Typ

Max

Unit

Conditions

CAP1208

DS00001570C-page 10

2013-2015 Microchip Technology Inc.

3.0

COMMUNICATIONS

3.1

Communications

The CAP1208 communicates using the SMBus or I

2

C protocol.

3.2

System Management Bus

The CAP1208 communicates with a host controller, such as an MCHP SIO, through the SMBus. The SMBus is a two-

wire serial communication protocol between a computer host and its peripheral devices. A detailed timing diagram is

shown in

Figure 3-1

. Stretching of the SMCLK signal is supported; however, the CAP1208 will not stretch the clock sig-

nal.

3.2.1

SMBUS START BIT

The SMBus Start bit is defined as a transition of the SMBus Data line from a logic ‘1’ state to a logic ‘0’ state while the

SMBus Clock line is in a logic ‘1’ state.

3.2.2

SMBUS ADDRESS AND RD / WR BIT

The SMBus Address Byte consists of the 7-bit client address followed by the RD / WR indicator bit. If this RD / WR bit

is a logic ‘0’, then the SMBus Host is writing data to the client device. If this RD / WR bit is a logic ‘1’, then the SMBus

Host is reading data from the client device.

The CAP1208-1 responds to SMBus address 0101_000(r/w). The CAP1208-2 responds to the SMBus address

0101_001(r/w).

3.2.3

SMBUS DATA BYTES

All SMBus Data bytes are sent most significant bit first and composed of 8-bits of information.

3.2.4

SMBUS ACK AND NACK BITS

The SMBus client will acknowledge all data bytes that it receives. This is done by the client device pulling the SMBus

Data line low after the 8th bit of each byte that is transmitted. This applies to both the Write Byte and Block Write proto-

cols.

The Host will NACK (not acknowledge) the last data byte to be received from the client by holding the SMBus data line

high after the 8th data bit has been sent. For the Block Read protocol, the Host will ACK each data byte that it receives

except the last data byte.

3.2.5

SMBUS STOP BIT

The SMBus Stop bit is defined as a transition of the SMBus Data line from a logic ‘0’ state to a logic ‘1’ state while the

SMBus clock line is in a logic ‘1’ state. When the CAP1208 detects an SMBus Stop bit and it has been communicating

with the SMBus protocol, it will reset its client interface and prepare to receive further communications.

FIGURE 3-1:

SMBUS TIMING DIAGRAM