1997-2013 Microchip Technology Inc.

DS30561C-page 1

Devices Included in this Data Sheet:

• PIC12C671

• PIC12C672

• PIC12CE673

• PIC12CE674

High-Performance RISC CPU:

• Only 35 single word instructions to learn

• All instructions are single cycle (400 ns) except for

program branches which are two-cycle

• Operating speed: DC - 10 MHz clock input

DC - 400 ns instruction cycle

• 14-bit wide instructions

• 8-bit wide data path

• Interrupt capability

• Special function hardware registers

• 8-level deep hardware stack

• Direct, indirect and relative addressing modes for

data and instructions

Peripheral Features:

• Four-channel, 8-bit A/D converter

• 8-bit real time clock/counter (TMR0) with 8-bit

programmable prescaler

• 1,000,000 erase/write cycle EEPROM data

memory

• EEPROM data retention > 40 years

Note:

Throughout this data sheet PIC12C67X

refers to the PIC12C671, PIC12C672,

PIC12CE673 and PIC12CE674.

PIC12CE67X refers to PIC12CE673 and

PIC12CE674.

Device

Memory

Program

Data

RAM

Data

EEPROM

PIC12C671

1024 x 14

128 x 8

—

PIC12C672

2048 x 14

128 x 8

—

PIC12CE673

1024 x 14

128 x 8

16 x 8

PIC12CE674

2048 x 14

128 x 8

16 x 8

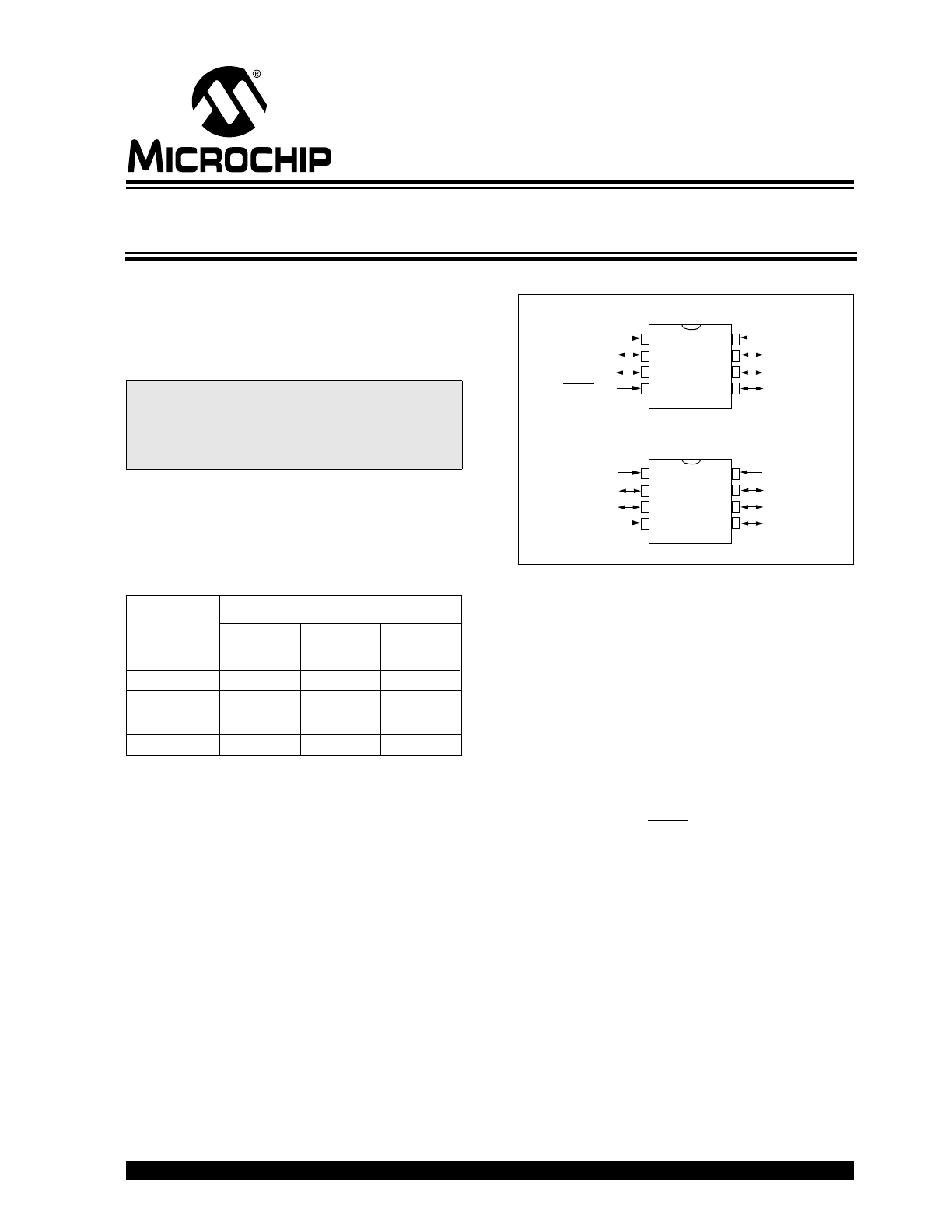

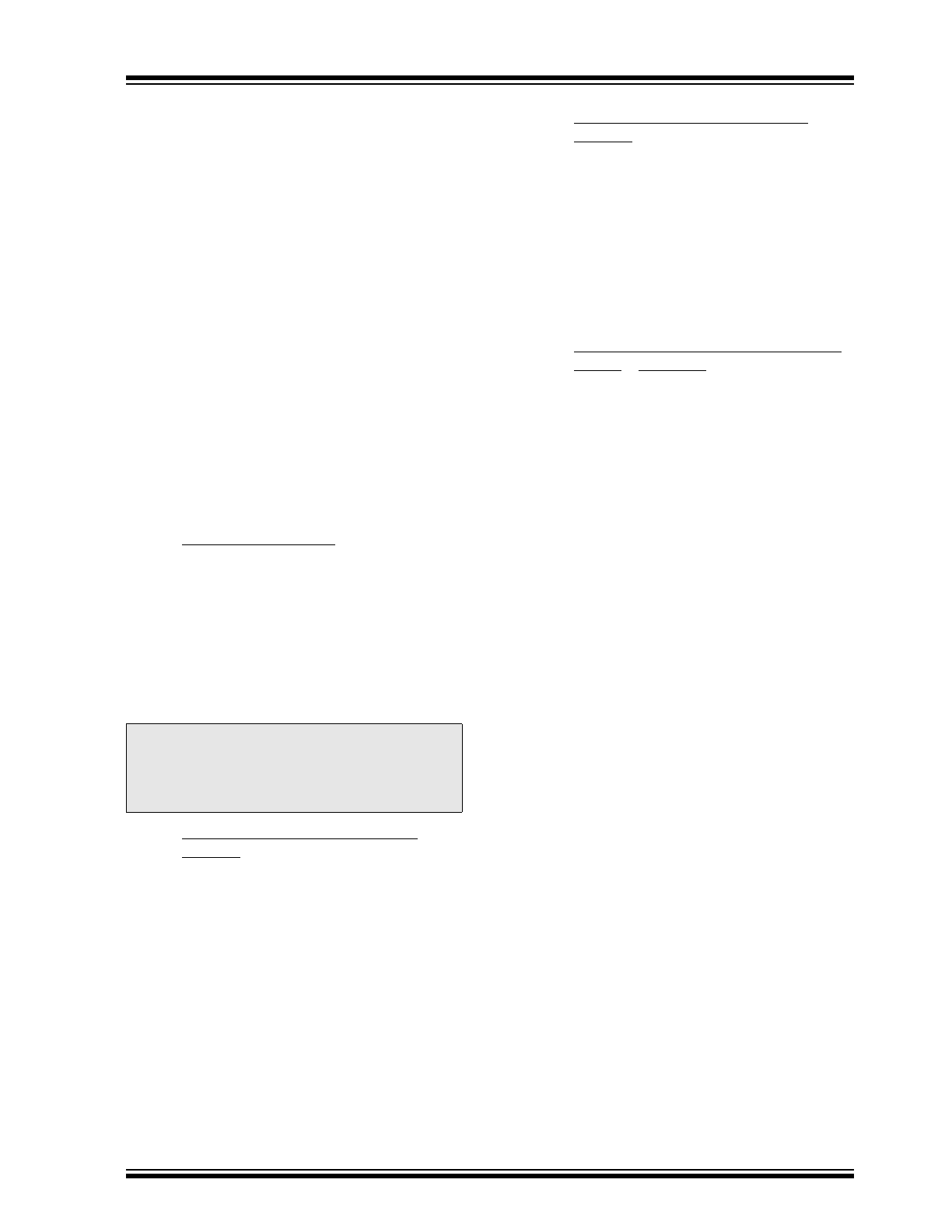

Pin Diagrams:

Special Microcontroller Features:

• In-Circuit Serial Programming (ICSP™)

• Internal 4 MHz oscillator with programmable calibration

• Selectable clockout

• Power-on Reset (POR)

• Power-up Timer (PWRT) and Oscillator Start-up

Timer (OST)

• Watchdog Timer (WDT) with its own on-chip RC

oscillator for reliable operation

• Programmable code protection

• Power saving SLEEP mode

• Interrupt-on-pin change (GP0, GP1, GP3)

• Internal pull-ups on I/O pins (GP0, GP1, GP3)

• Internal pull-up on MCLR pin

• Selectable oscillator options:

- INTRC: Precision internal 4 MHz oscillator

- EXTRC: External low-cost RC oscillator

- XT:

Standard crystal/resonator

- HS:

High speed crystal/resonator

- LP:

Power saving, low frequency crystal

CMOS Technology:

• Low-power, high-speed CMOS EPROM/EEPROM

technology

• Fully static design

• Wide operating voltage range 2.5V to 5.5V

• Commercial, Industrial and Extended

temperature ranges

• Low power consumption

< 2 mA @ 5V, 4 MHz

15

A typical @ 3V, 32 kHz

< 1

A typical standby current

PDIP, SOIC, Windowed CERDIP

8

7

6

5

1

2

3

4

PI

C12C671

PI

C12C672

V

SS

GP0/AN0

GP1/AN1/V

REF

GP2/T0CKI/AN2/

INT

PDIP, Windowed CERDIP

8

7

6

5

1

2

3

4

PI

C12CE6

73

PI

C12CE6

74

V

SS

GP0/AN0

GP1/AN1/V

REF

GP2/T0CKI/AN2/

INT

V

DD

GP5/OSC1/CLKIN

GP4/OSC2/AN3/

CLKOUT

GP3/MCLR/V

PP

V

DD

GP5/OSC1/CLKIN

GP4/OSC2/AN3/

CLKOUT

GP3/MCLR/V

PP

8-Pin, 8-Bit CMOS Microcontroller with A/D Converter

and EEPROM Data Memory

PIC12C67X

PIC12C67X

DS30561C-page 2

1997-2013 Microchip Technology Inc.

Table of Contents

1.0

General Description ...................................................................................................................................................................... 3

2.0

PIC12C67X Device Varieties ........................................................................................................................................................ 5

3.0

Architectural Overview .................................................................................................................................................................. 7

4.0

Memory Organization.................................................................................................................................................................. 11

5.0

I/O Port........................................................................................................................................................................................ 25

6.0

EEPROM Peripheral Operation .................................................................................................................................................. 33

7.0

Timer0 Module ............................................................................................................................................................................ 39

8.0

Analog-to-Digital Converter (A/D) Module................................................................................................................................... 45

9.0

Special Features of the CPU....................................................................................................................................................... 53

10.0 Instruction Set Summary............................................................................................................................................................. 69

11.0 Development Support ................................................................................................................................................................. 83

12.0 Electrical Specifications .............................................................................................................................................................. 89

13.0 DC and AC Characteristics ....................................................................................................................................................... 109

14.0 Packaging Information .............................................................................................................................................................. 115

Appendix A:Compatibility ................................................................................................................................................................... 119

Appendix B:Code for Accessing EEPROM Data Memory ................................................................................................................. 119

Index .................................................................................................................................................................................................. 121

On-Line Support................................................................................................................................................................................. 125

Reader Response .............................................................................................................................................................................. 126

PIC12C67X Product Identification System ........................................................................................................................................ 127

To Our Valued Customers

Most Current Data Sheet

To automatically obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended

workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revi-

sion of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include liter-

ature number) you are using.

Corrections to this Data Sheet

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure

that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing

or appears in error, please:

• Fill out and mail in the reader response form in the back of this data sheet.

• E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

1997-2013 Microchip Technology Inc.

DS30561C-page 3

PIC12C67X

1.0

GENERAL DESCRIPTION

The PIC12C67X devices are low-cost, high-perfor-

mance, CMOS, fully-static, 8-bit microcontrollers with

integrated analog-to-digital (A/D) converter and

EEPROM data memory (EEPROM on PIC12CE67X

versions only).

All PIC

®

microcontrollers employ an advanced RISC

architecture. The PIC12C67X microcontrollers have

enhanced core features, eight-level deep stack, and

multiple internal and external interrupt sources. The

separate instruction and data buses of the Harvard

architecture allow a 14-bit wide instruction word with

the separate 8-bit wide data. The two stage instruction

pipeline allows all instructions to execute in a single

cycle, except for program branches, which require two

cycles. A total of 35 instructions (reduced instruction

set) are available. Additionally, a large register set gives

some of the architectural innovations used to achieve a

very high performance.

PIC12C67X microcontrollers typically achieve a 2:1

code compression and a 4:1 speed improvement over

other 8-bit microcontrollers in their class.

The PIC12C67X devices have 128 bytes of RAM, 16

bytes of EEPROM data memory (PIC12CE67X only), 5

I/O

pins and 1 input pin. In addition a timer/counter is

available. Also a 4-channel, high-speed, 8-bit A/D is

provided. The 8-bit resolution is ideally suited for appli-

cations requiring low-cost analog interface, (i.e.,

thermostat control, pressure sensing, etc.)

The PIC12C67X devices have special features to

reduce external components, thus reducing cost,

enhancing system reliability and reducing power con-

sumption. The Power-On Reset (POR), Power-up

Timer (PWRT), and Oscillator Start-up Timer (OST)

eliminate the need for external reset circuitry. There are

five oscillator configurations to choose from, including

INTRC precision internal oscillator mode and the

power-saving LP (Low Power) oscillator mode. Power-

saving SLEEP mode, Watchdog Timer and code

protection features improve system cost, power and

reliability. The SLEEP (power-down) feature provides a

power-saving mode. The user can wake-up the chip

from SLEEP through several external and internal

interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip

RC oscillator provides protection against software

lock-up.

A UV erasable windowed package version is ideal for

code development, while the cost-effective One-Time-

Programmable (OTP) version is suitable for production

in any volume. The customer can take full advantage of

Microchip’s price leadership in OTP microcontrollers,

while benefiting from the OTP’s flexibility.

1.1

Applications

The PIC12C67X series fits perfectly in applications

ranging from personal care appliances and security

systems to low-power remote transmitters/receivers.

The EPROM technology makes customizing applica-

tion programs (transmitter codes, appliance settings,

receiver frequencies, etc.) extremely fast and conve-

nient, while the EEPROM data memory (PIC12CE67X

only) technology allows for the changing of calibration

factors and security codes. The small footprint pack-

ages, for through hole or surface mounting, make this

microcontroller series perfect for applications with

space limitations. Low-cost, low-power, high perfor-

mance, ease of use and I/O flexibility make the

PIC12C67X series very versatile even in areas where

no microcontroller use has been considered before

(i.e., timer functions, replacement of "glue" logic and

PLD’s in larger systems, coprocessor applications).

1.2

Family and Upward Compatibility

The PIC12C67X products are compatible with other

members of the 14-bit PIC16CXXX families.

1.3

Development Support

The PIC12C67X devices are supported by a full-

featured macro assembler, a software simulator, an in-

circuit emulator, a low-cost development programmer

and a full-featured programmer. A “C” compiler and

fuzzy logic support tools are also available.

PIC12C67X

DS30561C-page 4

1997-2013 Microchip Technology Inc.

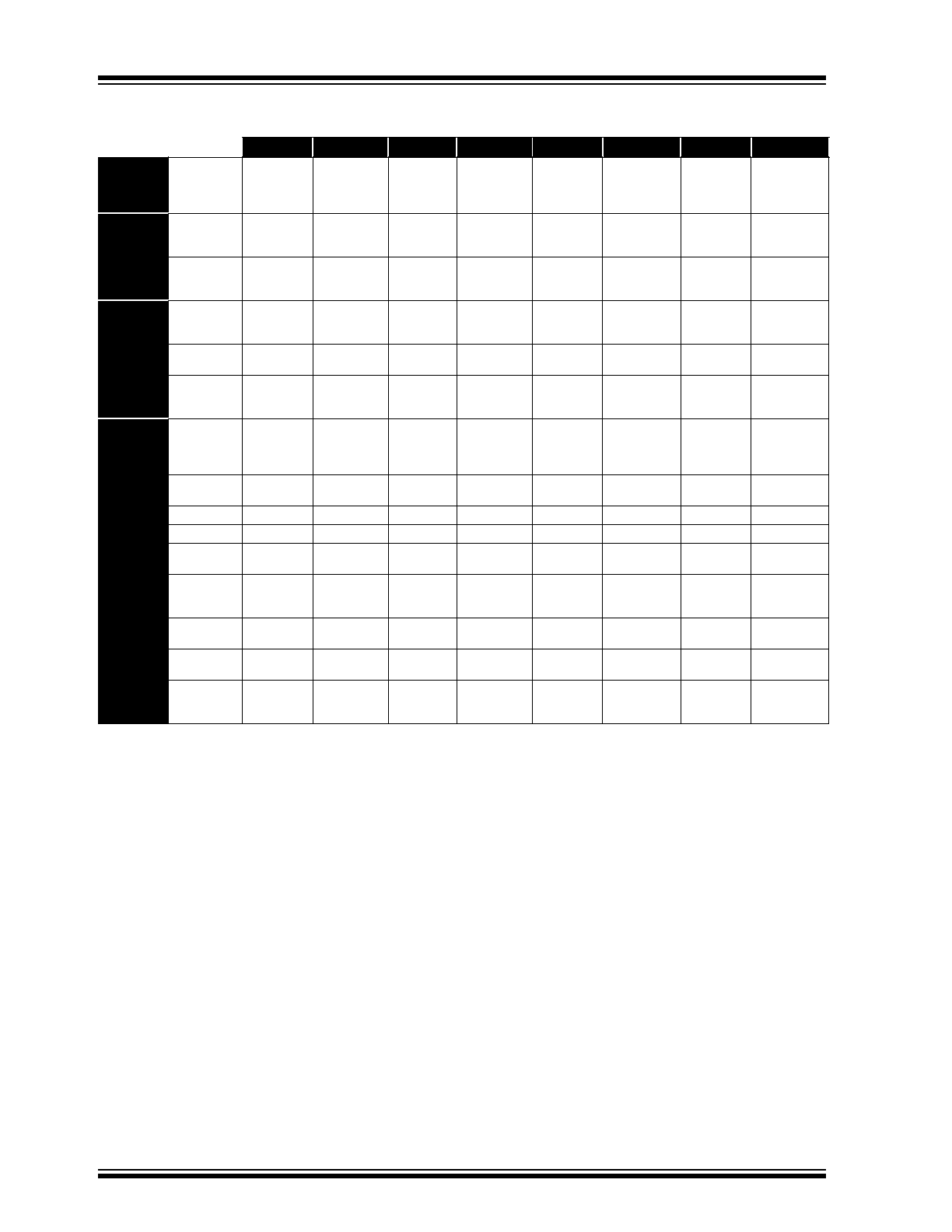

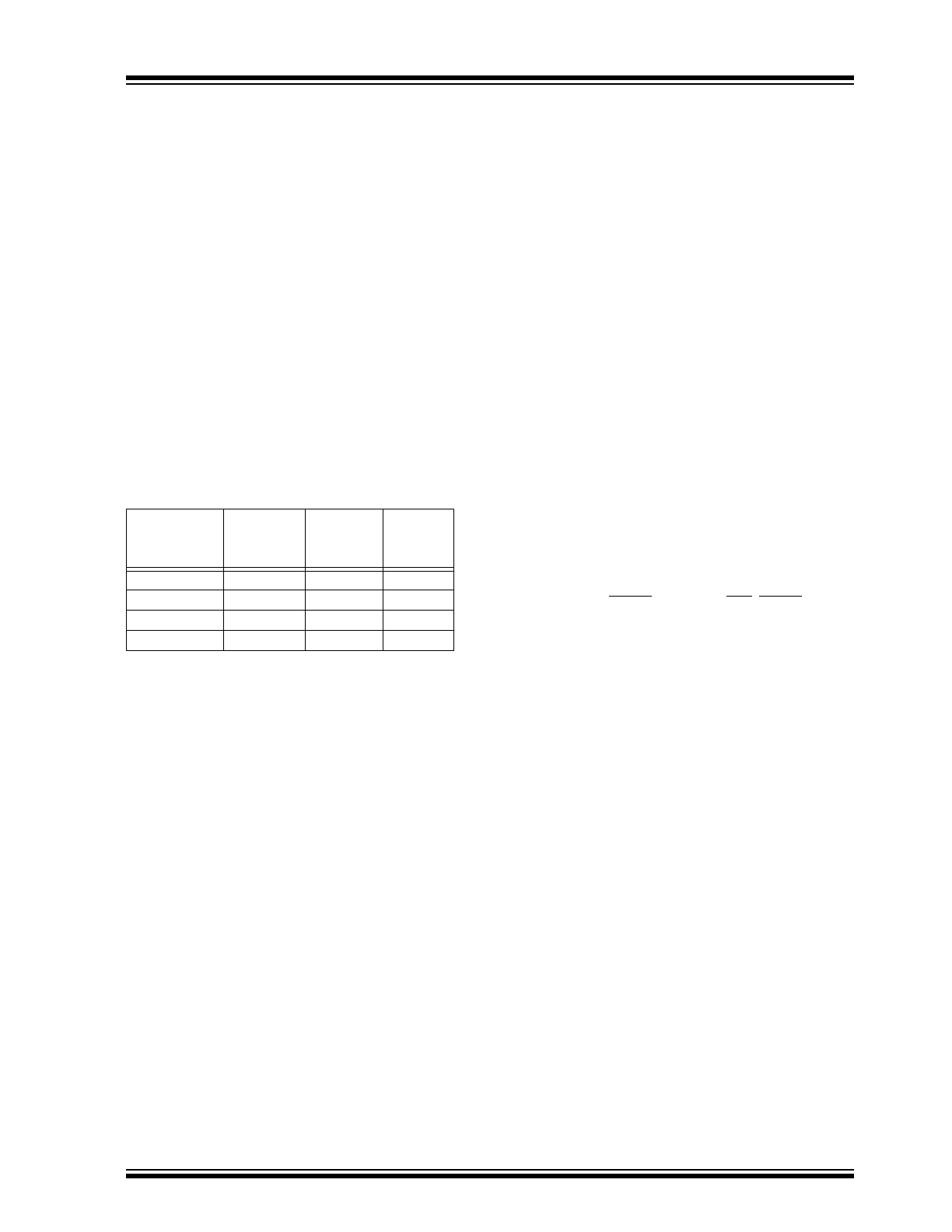

TABLE 1-1:

PIC12C67X & PIC12CE67X FAMILY OF DEVICES

PIC12C671

PIC12LC671

PIC12C672

PIC12LC672 PIC12CE673 PIC12LCE673 PIC12CE674 PIC12LCE674

Clock

Maximum

Frequency

of Operation

(MHz)

10

10

10

10

10

10

10

10

Memory

EPROM

Program

Memory

1024 x 14

1024 x 14

2048 x 14

2048 x 14

1024 x 14

1024 x 14

2048 x 14

2048 x 14

RAM Data

Memory

(bytes)

128

128

128

128

128

128

128

128

Peripherals

EEPROM

Data Memory

(bytes)

—

—

—

—

16

16

16

16

Timer

Module(s)

TMR0

TMR0

TMR0

TMR0

TMR0

TMR0

TMR0

TMR0

A/D Con-

verter (8-bit)

Channels

4

4

4

4

4

4

4

4

Features

Wake-up

from SLEEP

on pin

change

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Interrupt

Sources

4

4

4

4

4

4

4

4

I/O Pins

5

5

5

5

5

5

5

5

Input Pins

1

1

1

1

1

1

1

1

Internal

Pull-ups

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

In-Circuit

Serial

Programming

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Number of

Instructions

35

35

35

35

35

35

35

35

Voltage

Range (Volts)

3.0V - 5.5V

2.5V - 5.5V

3.0V - 5.5V

2.5V - 5.5V

3.0V - 5.5V

2.5V - 5.5V

3.0V - 5.5V

2.5V - 5.5V

Packages

8-pin DIP,

JW, SOIC

8-pin DIP,

JW, SOIC

8-pin DIP,

JW, SOIC

8-pin DIP,

JW, SOIC

8-pin DIP,

JW

8-pin DIP,

JW

8-pin DIP,

JW

8-pin DIP,

JW

All PIC12C67X devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability.

All PIC12C67X devices use serial programming with data pin GP0 and clock pin GP1.

1997-2013 Microchip Technology Inc.

DS30561C-page 5

PIC12C67X

2.0

PIC12C67X DEVICE VARIETIES

A variety of frequency ranges and packaging options

are available. Depending on application and production

requirements, the proper device option can be selected

using the information in the PIC12C67X Product Iden-

tification System section at the end of this data sheet.

When placing orders, please use that page of the data

sheet to specify the correct part number.

For example, the PIC12C67X device “type” is indicated

in the device number:

1.

C, as in PIC12C671. These devices have

EPROM type memory and operate over the

standard voltage range.

2.

LC, as in PIC12LC671. These devices have

EPROM type memory and operate over an

extended voltage range.

3.

CE, as in PIC12CE674. These devices have

EPROM type memory, EEPROM data memory

and operate over the standard voltage range.

4.

LCE, as in PIC12LCE674. These devices have

EPROM type memory, EEPROM data memory

and operate over an extended voltage range.

2.1

UV Erasable Devices

The UV erasable version, offered in windowed pack-

age, is optimal for prototype development and pilot pro-

grams.

The UV erasable version can be erased and repro-

grammed to any of the configuration modes.

Microchip's PICSTART

Plus and PRO MATE

pro-

grammers both support the PIC12C67X. Third party

programmers also are available; refer to the Microchip

Third Party Guide for a list of sources.

2.2

One-Time-Programmable (OTP)

Devices

The availability of OTP devices is especially useful for

customers who need the flexibility for frequent code

updates and small volume applications.

The OTP devices, packaged in plastic packages, per-

mit the user to program them once. In addition to the

program memory, the configuration bits must also be

programmed.

Note:

Please note that erasing the device will

also erase the pre-programmed internal

calibration value for the internal oscillator.

The calibration value must be saved prior

to erasing the part.

2.3

Quick-Turn-Programming (QTP)

Devices

Microchip offers a QTP Programming Service for fac-

tory production orders. This service is made available

for users who choose not to program a medium to high

quantity of units and whose code patterns have stabi-

lized. The devices are identical to the OTP devices, but

with all EPROM locations and configuration options

already programmed by the factory. Certain code and

prototype verification procedures apply before produc-

tion shipments are available. Please contact your local

Microchip Technology sales office for more details.

2.4

Serialized Quick-Turn Programming

(SQTP

SM

) Devices

Microchip offers a unique programming service where

a few user-defined locations in each device are pro-

grammed with different serial numbers. The serial num-

bers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a

unique number which can serve as an entry-code,

password, or ID number.

PIC12C67X

DS30561C-page 6

1997-2013 Microchip Technology Inc.

NOTES:

1997-2013 Microchip Technology Inc.

DS30561C-page 7

PIC12C67X

3.0

ARCHITECTURAL OVERVIEW

The high performance of the PIC12C67X family can be

attributed to a number of architectural features com-

monly found in RISC microprocessors. To begin with,

the PIC12C67X uses a Harvard architecture, in which

program and data are accessed from separate memo-

ries using separate buses. This improves bandwidth

over traditional von Neumann architecture in which pro-

gram and data are fetched from the same memory

using the same bus. Separating program and data

buses also allow instructions to be sized differently than

the 8-bit wide data word. Instruction opcodes are 14-

bits wide making it possible to have all single word

instructions. A 14-bit wide program memory access

bus fetches a 14-bit instruction in a single instruction

cycle. A two-stage pipeline overlaps fetch and execu-

tion of instructions (Example 3-1). Consequently, all

instructions (35) execute in a single cycle (200 ns @ 20

MHz) except for program branches.

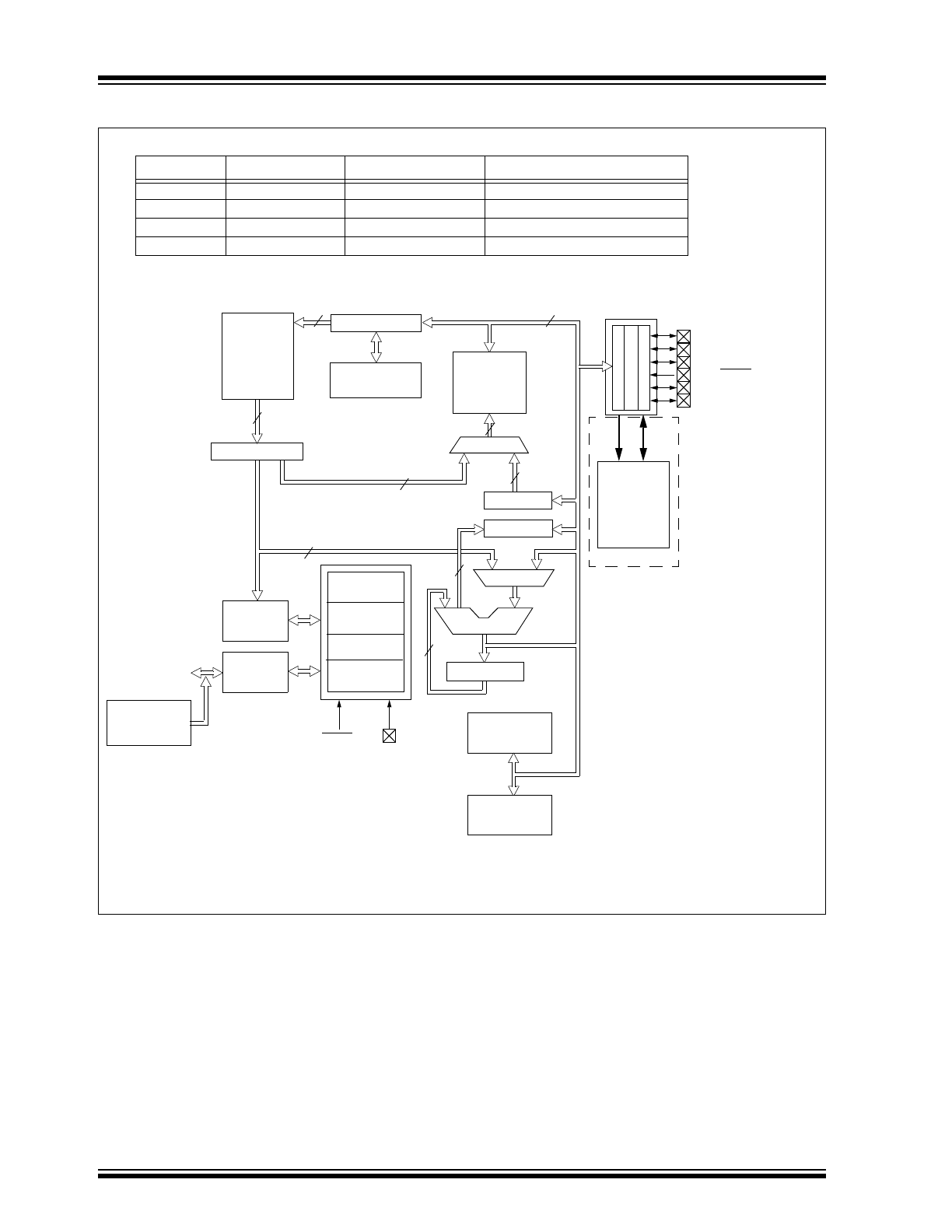

The table below lists program memory (EPROM), data

memory (RAM), and non-volatile memory (EEPROM)

for each PIC12C67X device.

Device

Program

Memory

RAM Data

Memory

EEPROM

Data

Memory

PIC12C671

1K x 14

128 x 8

—

PIC12C672

2K x 14

128 x 8

—

PIC12CE673

1K x 14

128 x 8

16x8

PIC12CE674

2K x 14

128 x 8

16x8

The PIC12C67X can directly or indirectly address its

register files or data memory. All special function regis-

ters, including the program counter, are mapped in the

data memory. The PIC12C67X has an orthogonal

(symmetrical) instruction set that makes it possible to

carry out any operation on any register using any

addressing mode. This symmetrical nature and lack of

‘special optimal situations’ make programming with the

PIC12C67X simple yet efficient. In addition, the learn-

ing curve is reduced significantly.

PIC12C67X devices contain an 8-bit ALU and working

register. The ALU is a general purpose arithmetic unit.

It performs arithmetic and Boolean functions between

the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, sub-

traction, shift and logical operations. Unless otherwise

mentioned, arithmetic operations are two's comple-

ment in nature. In two-operand instructions, typically

one operand is the working register (W register). The

other operand is a file register or an immediate con-

stant. In single operand instructions, the operand is

either the W register or a file register.

The W register is an 8-bit working register used for ALU

operations. It is not an addressable register.

Depending on the instruction executed, the ALU may

affect the values of the Carry (C), Digit Carry (DC), and

Zero (Z) bits in the STATUS register. The C and DC bits

operate as a borrow bit and a digit borrow out bit,

respectively, in subtraction. See the SUBLW and SUBWF

instructions for examples.

PIC12C67X

DS30561C-page 8

1997-2013 Microchip Technology Inc.

FIGURE 3-1:

PIC12C67X BLOCK DIAGRAM

Power-up

Timer

Oscillator

Start-up Timer

EPROM

Program

Memory

13

Data Bus

8

14

Program

Bus

Instruction reg

Program Counter

RAM

File

Registers

Direct Addr

7

RAM Addr

(1)

9

Addr MUX

Indirect

Addr

FSR reg

STATUS reg

MUX

ALU

W reg

Instruction

Decode &

Control

Timing

Generation

OSC1/CLKIN

OSC2/CLKOUT

MCLR

V

DD

, V

SS

Timer0

GPIO

8

8

GP4/OSC2/AN3/CLKOUT

GP3/MCLR/V

PP

GP2/T0CKI/AN2/INT

GP1/AN1/V

REF

GP0/AN0

8

3

GP5/OSC1/CLKIN

8 Level Stack

(13 bit)

128 bytes

Note 1: Higher order bits are from the STATUS Register.

A/D

Watchdog

Timer

Power-on

Reset

4 MHz Clock

Internal

Data

Memory

16x8

EEPROM

SCL

SD

A

Device

Program Memory

Data Memory (RAM)

Non-Volatile Memory (EEPROM)

PIC12C671

1K x 14

128 x 8

—

PIC12C672

2K x 14

128 x 8

—

PIC12CE673

1K x 14

128 x 8

16 x 8

PIC12CE674

2K x 14

128 x 8

16 x 8

PIC12CE673

PIC12CE674

1997-2013 Microchip Technology Inc.

DS30561C-page 9

PIC12C67X

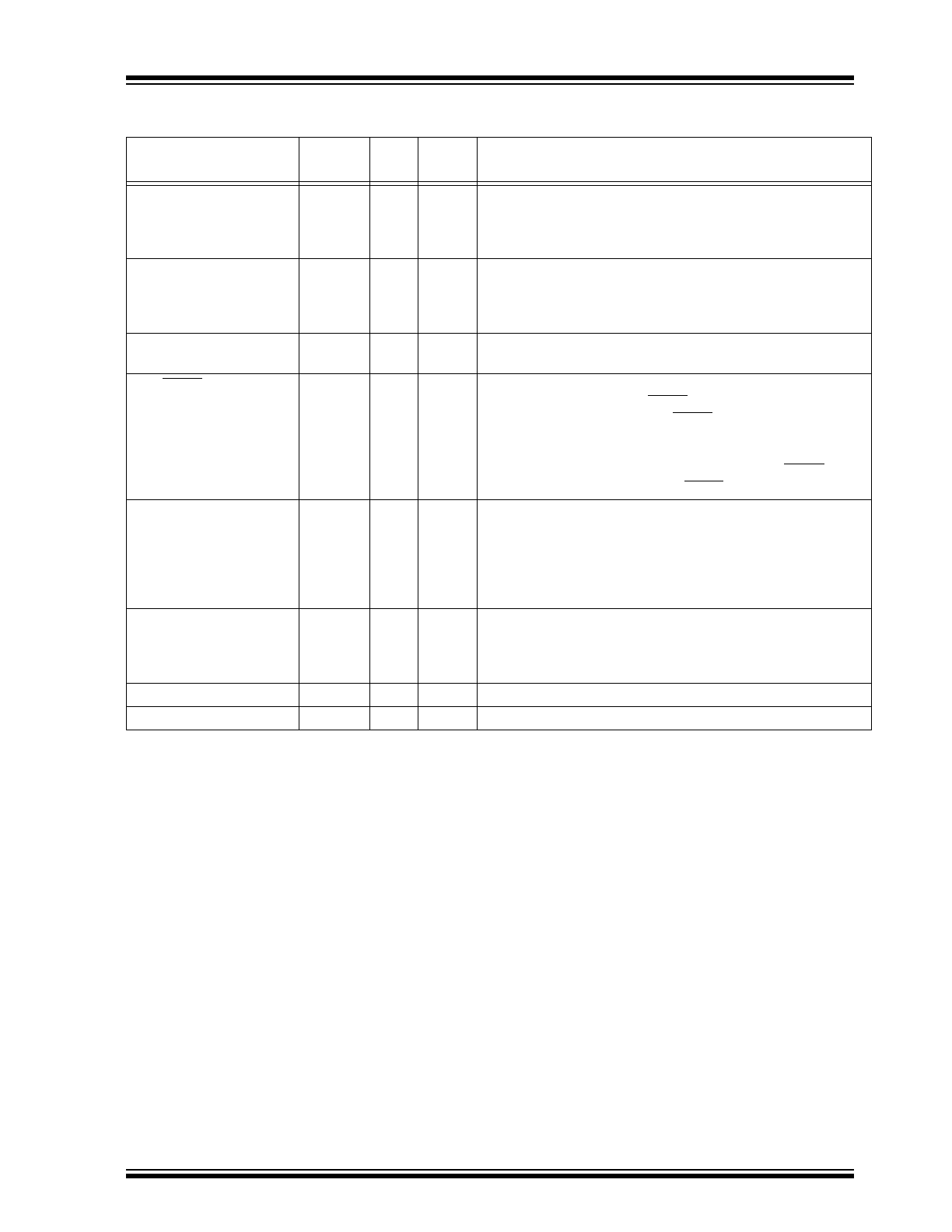

TABLE 3-1:

PIC12C67X PINOUT DESCRIPTION

Name

DIP Pin #

I/O/P

Type

Buffer

Type

Description

GP0/AN0

7

I/O

TTL/ST Bi-directional I/O port/serial programming data/analog input 0.

Can be software programmed for internal weak pull-up and

interrupt-on-pin change. This buffer is a Schmitt Trigger input

when used in serial programming mode.

GP1/AN1/V

REF

6

I/O

TTL/ST Bi-directional I/O port/serial programming clock/analog input 1/

voltage reference. Can be software programmed for internal

weak pull-up and interrupt-on-pin change. This buffer is a

Schmitt Trigger input when used in serial programming mode.

GP2/T0CKI/AN2/INT

5

I/O

ST

Bi-directional I/O port/analog input 2. Can be configured as

T0CKI or external interrupt.

GP3/MCLR/V

PP

4

I

TTL/ST Input port/master clear (reset) input/programming voltage

input. When configured as MCLR, this pin is an active low

reset to the device. Voltage on MCLR/V

PP

must not exceed

V

DD

during normal device operation. Can be software pro-

grammed for internal weak pull-up and interrupt-on-pin

change. Weak pull-up always on if configured as MCLR . This

buffer is Schmitt Trigger when in MCLR mode.

GP4/OSC2/AN3/CLKOUT

3

I/O

TTL

Bi-directional I/O port/oscillator crystal output/analog input 3.

Connections to crystal or resonator in crystal oscillator mode

(HS, XT and LP modes only, GPIO in other modes). In EXTRC

and INTRC modes, the pin output can be configured to CLK-

OUT, which has 1/4 the frequency of OSC1 and denotes the

instruction cycle rate.

GP5/OSC1/CLKIN

2

I/O

TTL/ST Bi-directional IO port/oscillator crystal input/external clock

source input (GPIO in INTRC mode only, OSC1 in all other

oscillator modes). Schmitt trigger input for EXTRC oscillator

mode.

V

DD

1

P

—

Positive supply for logic and I/O pins.

V

SS

8

P

—

Ground reference for logic and I/O pins.

Legend: I = input, O = output, I/O = input/output, P = power, — = not used, TTL = TTL input,

ST = Schmitt Trigger input.

PIC12C67X

DS30561C-page 10

1997-2013 Microchip Technology Inc.

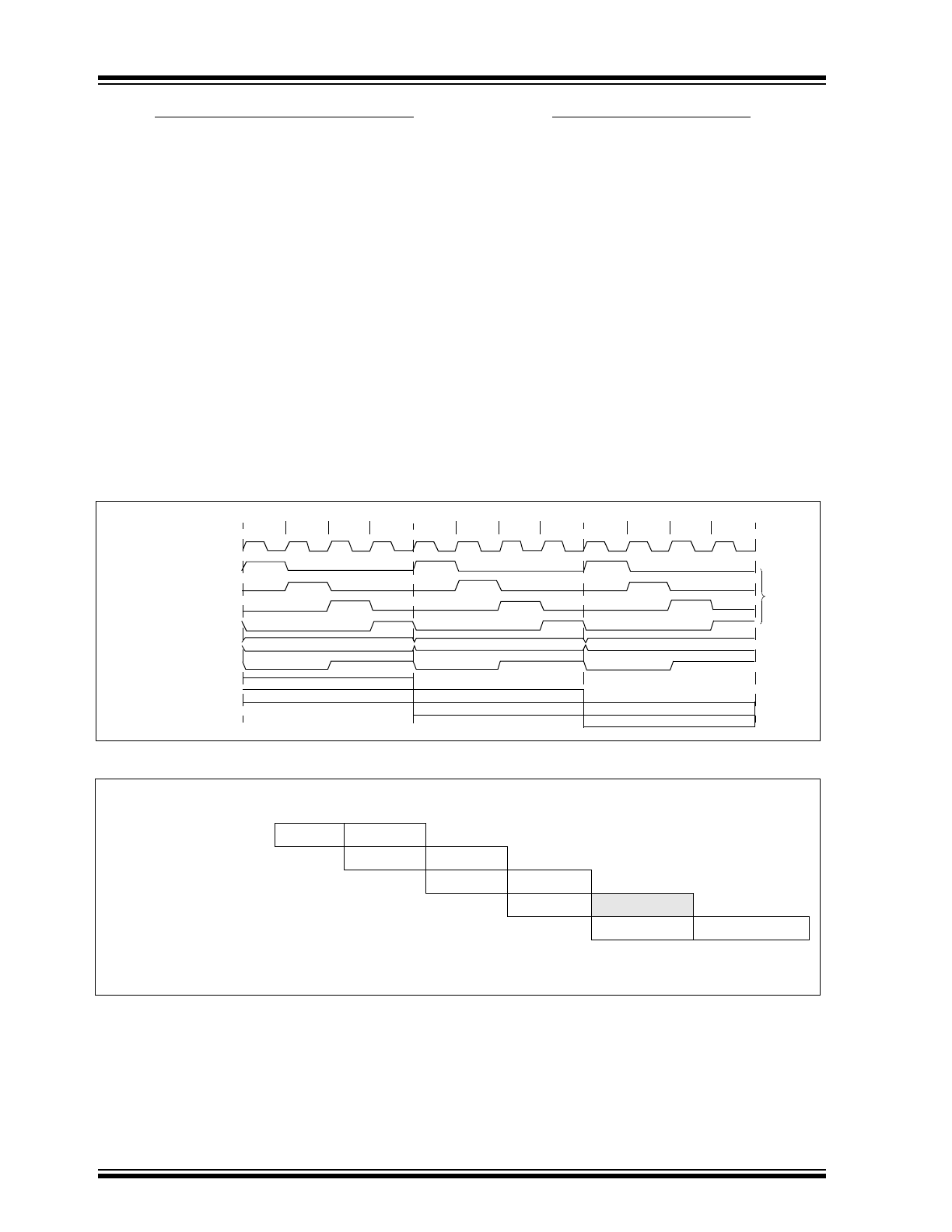

FIGURE 3-2:

CLOCK/INSTRUCTION CYCLE

EXAMPLE 3-1:

INSTRUCTION PIPELINE FLOW

Q1

Q2

Q3

Q4

Q1

Q2

Q3

Q4

Q1

Q2

Q3

Q4

OSC1

Q1

Q2

Q3

Q4

PC

OSC2/CLKOUT

(EXTRC and

PC

PC+1

PC+2

Fetch INST (PC)

Execute INST (PC-1)

Fetch INST (PC+1)

Execute INST (PC)

Fetch INST (PC+2)

Execute INST (PC+1)

Internal

phase

clock

INTRC modes)

All instructions are single cycle, except for any program branches. These take two cycles since the fetched

instruction is “flushed” from the pipeline while the new instruction is being fetched and then executed.

T

CY

0

T

CY

1

T

CY

2

T

CY

3

T

CY

4

T

CY

5

1. MOVLW 55h

Fetch 1

Execute 1

2. MOVWF GPIO

Fetch 2

Execute 2

3. CALL SUB_1

Fetch 3

Execute 3

4. BSF GPIO, BIT3 (Forced NOP)

Fetch 4

Flush

5. Instruction @ address SUB_1

Fetch SUB_1

Execute SUB_1

3.1

Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by

four to generate four non-overlapping quadrature

clocks, namely Q1, Q2, Q3 and Q4. Internally, the pro-

gram counter (PC) is incremented every Q1, and the

instruction is fetched from the program memory and

latched into the instruction register in Q4. The instruc-

tion is decoded and executed during the following Q1

through Q4. The clocks and instruction execution flow

is shown in Figure 3-2.

3.2

Instruction Flow/Pipelining

An “Instruction Cycle” consists of four Q cycles (Q1,

Q2, Q3 and Q4). The instruction fetch and execute

are pipelined such that fetch takes one instruction

cycle, while decode and execute takes another

instruction cycle. However, due to the pipelining, each

instruction effectively executes in one cycle. If an

instruction causes the program counter to change

(i.e., GOTO), then two cycles are required to complete

the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC)

incrementing in Q1.

In the execution cycle, the fetched instruction is

latched into the “Instruction Register" (IR) in cycle

Q1. This instruction is then decoded and executed

during the Q2, Q3, and Q4 cycles. Data memory is

read during Q2 (operand read) and written during Q4

(destination write).