HITFET - BTS3405G

Smart Low-Side Power Switch

Data Sheet, Rev. 1.1, September 2011

Automotive Power

Smart Low-Side Power Switch

BTS3405G

Data Sheet

2

Rev. 1.1, 2011-09-01

1

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.1

Terms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3

Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.1

Pin Assignment BTS3405G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.2

Pin Definitions and Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

4

General Product Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4.1

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4.2

Thermal Resistance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4.2.1

Transient Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

5

Block Description and Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

5.1

Input and Power Stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

5.1.1

Input Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

5.1.2

Failure Feedback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

5.1.3

Output On-State Resistance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

5.1.4

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.1.5

Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.1.6

Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

6

Protection Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.1

Thermal Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.2

Overvoltage Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.3

Short Circuit Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

6.4

Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

7

Package Outlines BTS3405G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

8

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

PG-DSO-8-25

Type

Package

Marking

BTS3405G

PG-DSO-8-25

BTS3405G

Data Sheet

3

Rev. 1.1, 2011-09-01

Smart Low-Side Power Switch

HITFET

BTS3405G

1

Overview

Features

•

Low input current

•

Short circuit and Overload protection

•

Current limitation

•

Input protection (ESD)

•

Thermal protection with auto restart

•

Compatible to standard Power MOSFET

•

Analog driving possible

•

Two channel concept saves PCB footprint

•

Green Product (RoHS compliant)

•

AEC Qualified

Description

The BTS3405G is a two channel low-side power switch in PG-DSO-8-25 package providing embedded protective

functions. The device consists of two separate monolithic IC. Each with one N-channel power MOSFET transistor

and additional protection circuitry.

Table 1

Product Summary

Drain Voltage

V

D

42 V

1)

1) Active clamped

Input Voltage

V

IN(max)

10 V

Typical On-State Resistance at

T

j

= 25

°C and Vin = 10V

R

DS(ON,amb typ)

0.7

Ω

Maximum On-State Resistance at

T

j

= 150

°C and Vin = 10V

R

DS(ON,hot max)

1.9

Ω

Nominal Load Current

I

Dnom(min)

350 mA

Drain Current

I

D

600 mA

2)

2) Internally limited

Single Clamping Energy

E

AS

65 mJ

Smart Low-Side Power Switch

BTS3405G

Overview

Data Sheet

4

Rev. 1.1, 2011-09-01

Protective Functions

•

Electrostatic discharge protection (ESD)

•

Active clamp over voltage protection

•

Thermal shutdown with auto restart

•

Short circuit protection

Fault Information

•

Thermal shutdown

•

Short to Battery and overload

Applications

•

Designed for driving Relays in Automotive Applications

•

All types of resistive, inductive and capacitive loads

•

Suitable for loads with peak currents

•

Replaces discrete circuits

Detailed Description

The device is able to switch all kind of resistive, inductive and capacitive loads, limited by

E

AS

and maximum

current capabilities.

The BTS3405G offers ESD protection of each IN Pin in relation to the corresponding Source Pin.

The overtemperature protection prevents the device from overheating due to overload and/or bad cooling

conditions. The temperature information is given by a temperature sensor in each of the two power MOSFET.

During thermal shutdown the device tries to sink an increased input current at the corresponding IN pin to feedback

the fault condition on this channel.

The BTS3405G has a thermal-auto-restart function, the regarding channel will turn on again after the measured

temperature has dropped down for the thermal hysteresis.

The over voltage protection is active during load-dump or inductive turn off conditions. The power MOSFET is

limiting the Drain - Source voltage to the defined clamping voltage. This function is available regardless of the input

pin state, means without voltage on the IN pins.

Data Sheet

5

Rev. 1.1, 2011-09-01

Smart Low-Side Power Switch

BTS3405G

Block DiagramTerms

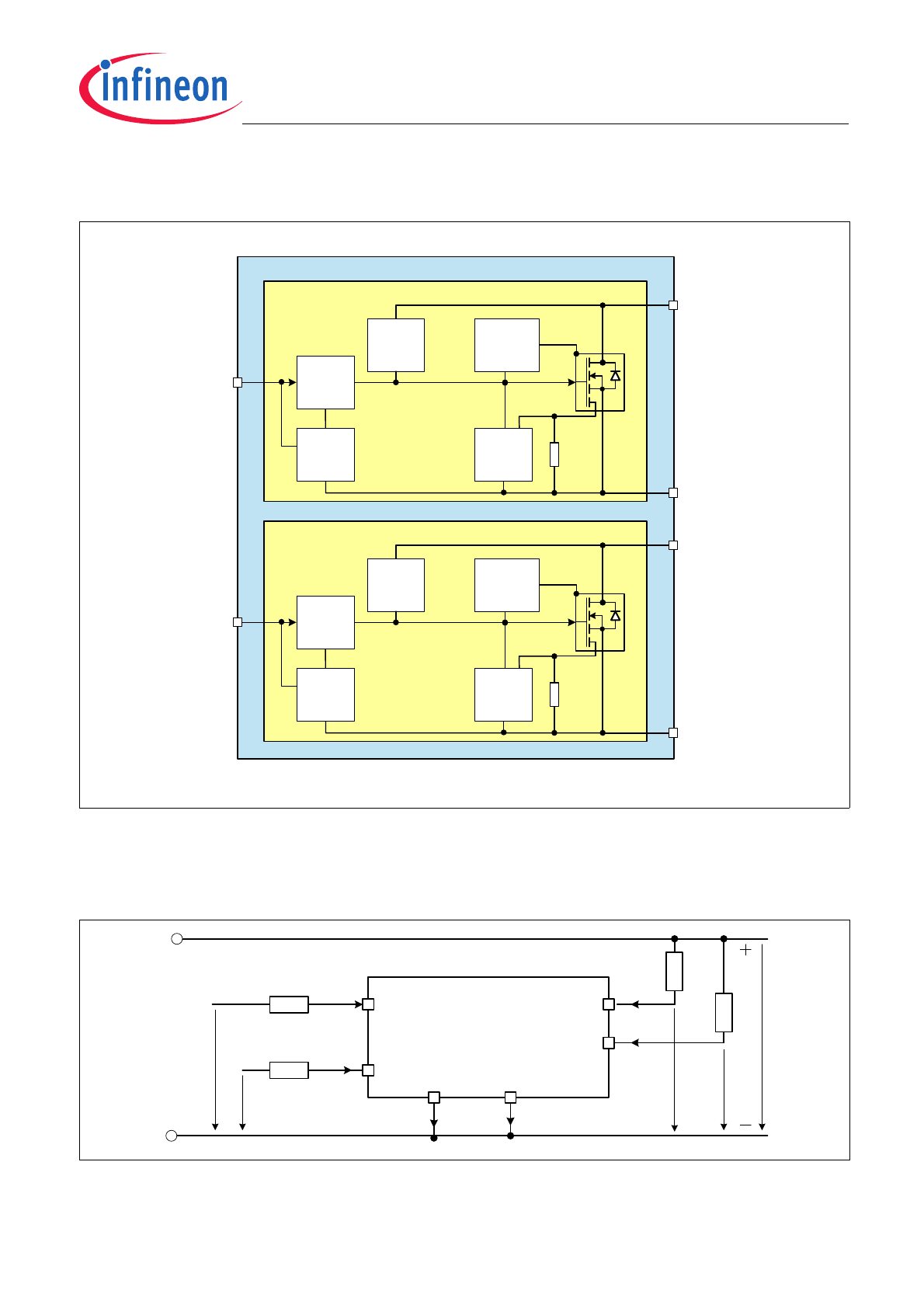

2

Block Diagram

Figure 1

Block Diagram

2.1

Terms

Figure 2

shows all external terms used in this data sheet.

Figure 2

Terms

Drain 1

Source 1

Drain2

Source2

IN 2

BlockDiagram_3405

Over-

voltage

Protection

IN 1

Gate

Driving

Unit

ESD

Protection

Over-

temperature

Protection

Short

circuit

detection

Over-

voltage

Protection

Gate

Driving

Unit

ESD

Protection

Over-

temperature

Protection

Short

circuit

detection

V

bb

GND

Terms.emf

IN2

V

bb

V

IN2

I

IN2

R

in2

V

IN1

I

IN1

R

in1

IN1

Source1

I

S 1

Source2

I

S 2

Drain1

I

D1

V

D1

Z

L2

I

D2

V

D2

Drain2

Z

L1

BTS3405G

Smart Low-Side Power Switch

BTS3405G

Pin ConfigurationPin Assignment BTS3405G

Data Sheet

6

Rev. 1.1, 2011-09-01

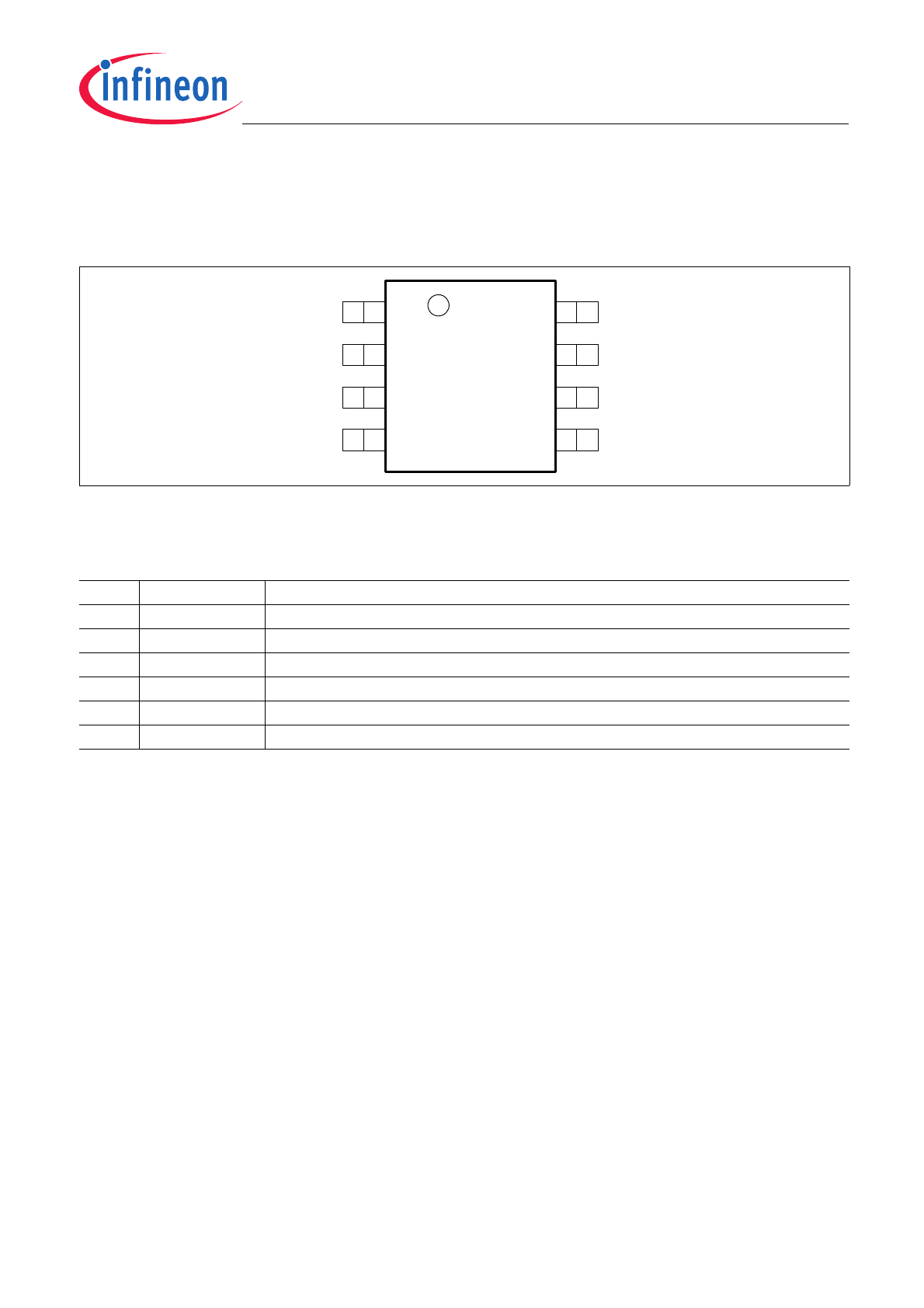

3

Pin Configuration

3.1

Pin Assignment BTS3405G

Figure 3

Pin Configuration PG-DSO-8-25

3.2

Pin Definitions and Functions

Pin

Symbol

Function

1

Source1

Ground connection for channel 1

2

IN1

Input / Fault feedback for channel 1

3

Source2

Ground connection for channel 2

4

IN2

Input / Fault feedback for channel 2

5, 6

Drain2

Load connection channel 2

7, 8

Drain1

Load connection channel 1

P-DSO-8.vsd

1

2

Source 2

8

7

Drain 2

IN1

6

5

3

4

Drain 2

Drain 1

Drain 1

Source 1

IN2

Data Sheet

7

Rev. 1.1, 2011-09-01

Smart Low-Side Power Switch

BTS3405G

General Product CharacteristicsAbsolute Maximum Ratings

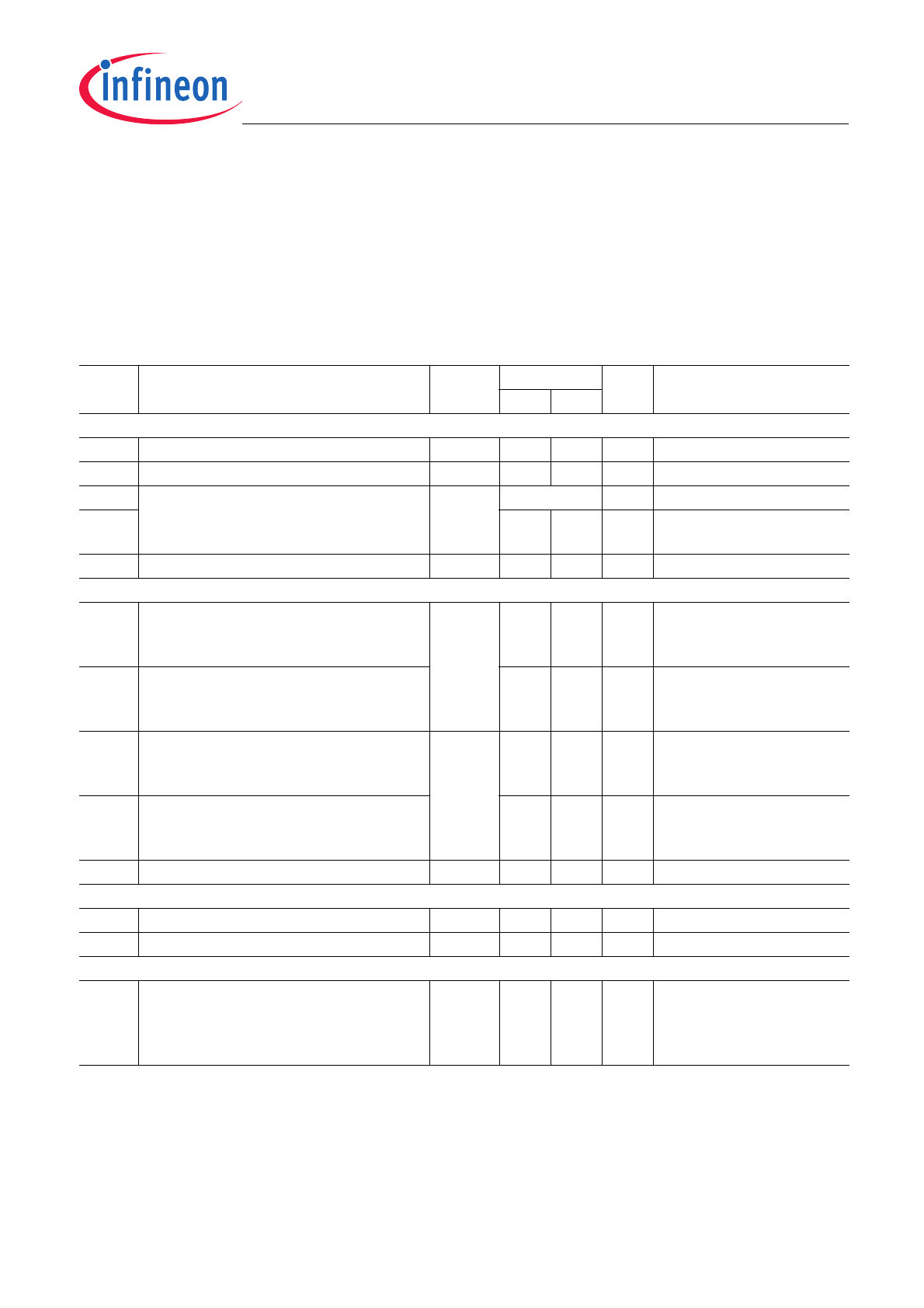

4

General Product Characteristics

4.1

Absolute Maximum Ratings

All parameters apply for both channels accordingly.

Absolute Maximum Ratings

1)

T

j

= -40

⋅C to +150 ⋅C; all voltages with respect to ground, positive current flowing into pin

(unless otherwise specified), all values valid for both channels

1) Not subject to production test, specified by design.

Pos.

Parameter

Symbol Limit Values Unit

Test Conditions

Min.

Max.

Voltages

4.1.1

Drain voltage

V

D

–

42

V

2)

V

IN

= 0 V,

I

D

= 10 mA

2) Active clamped.

4.1.2

Input Voltage

V

IN

-0.2

10

V

–

4.1.3

Input Current

I

IN

self limited

mA

-0.2 V <

V

IN

< 10 V

4.1.4

-2

2

mA

V

IN

< -0.2 V

or

V

IN

> 10 V

4.1.5

Drain Current

I

D

–

600

mA

3)

T

j

= 25

°C

3) Internally limited.

Energies

4.1.6

Unclamped single pulse inductive energy

single pulse

E

AS

0

65

mJ

I

D

= 350 mA;

V

bb

= 28 V;

T

J(start)

= 85

°C

4.1.7

Unclamped single pulse inductive energy

single pulse

–

30

mJ

I

D

= 250 mA;

V

bb

= 28 V;

T

J(start)

= 150

°C

4.1.8

Unclamped repetitive pulse inductive

energy 1

×10

4

cycles

E

AR

0

18

mJ

I

D

= 200 mA;

V

bb

= 13.5 V;

T

J(start)

= 105

°C

4.1.9

Unclamped repetitive pulse inductive

energy 1

×10

6

cycles

–

13

mJ

I

D

= 170 mA;

V

bb

= 13.5 V;

T

J(start)

= 105

°C

4.1.10

Total Power Dissipation

P

tot

–

0.78

W

4)

T

a

= 85

°C

4) Device mounted on PCB according EIA/JEDEC standard JESD51-7 (4-layer FR4, 76.2 mm

× 114.3 mm with buried

planes). PCB is mounted vertical without blown air.

Temperatures

4.1.11

Operating temperature

T

J

-40

+150

°C

–

4.1.12

Storage temperature

T

stg

-55

+150

°C

–

ESD Susceptibility

4.1.13

Electrostatic discharge voltage

5)

5) ESD susceptibility HBM according to EIA/JESD 22-A 114B, section 4.

V

ESD

-2

2

kV

IN Pin

R

= 1.5 k

;

C

= 100 pF;

T

J

= 25

°C

Smart Low-Side Power Switch

BTS3405G

General Product CharacteristicsThermal Resistance

Data Sheet

8

Rev. 1.1, 2011-09-01

4.2

Thermal Resistance

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the

data sheet. Fault conditions are considered as “outside” normal operating range. Protection functions are

not designed for continuous repetitive operation.

4.2.1

Transient Thermal Impedance

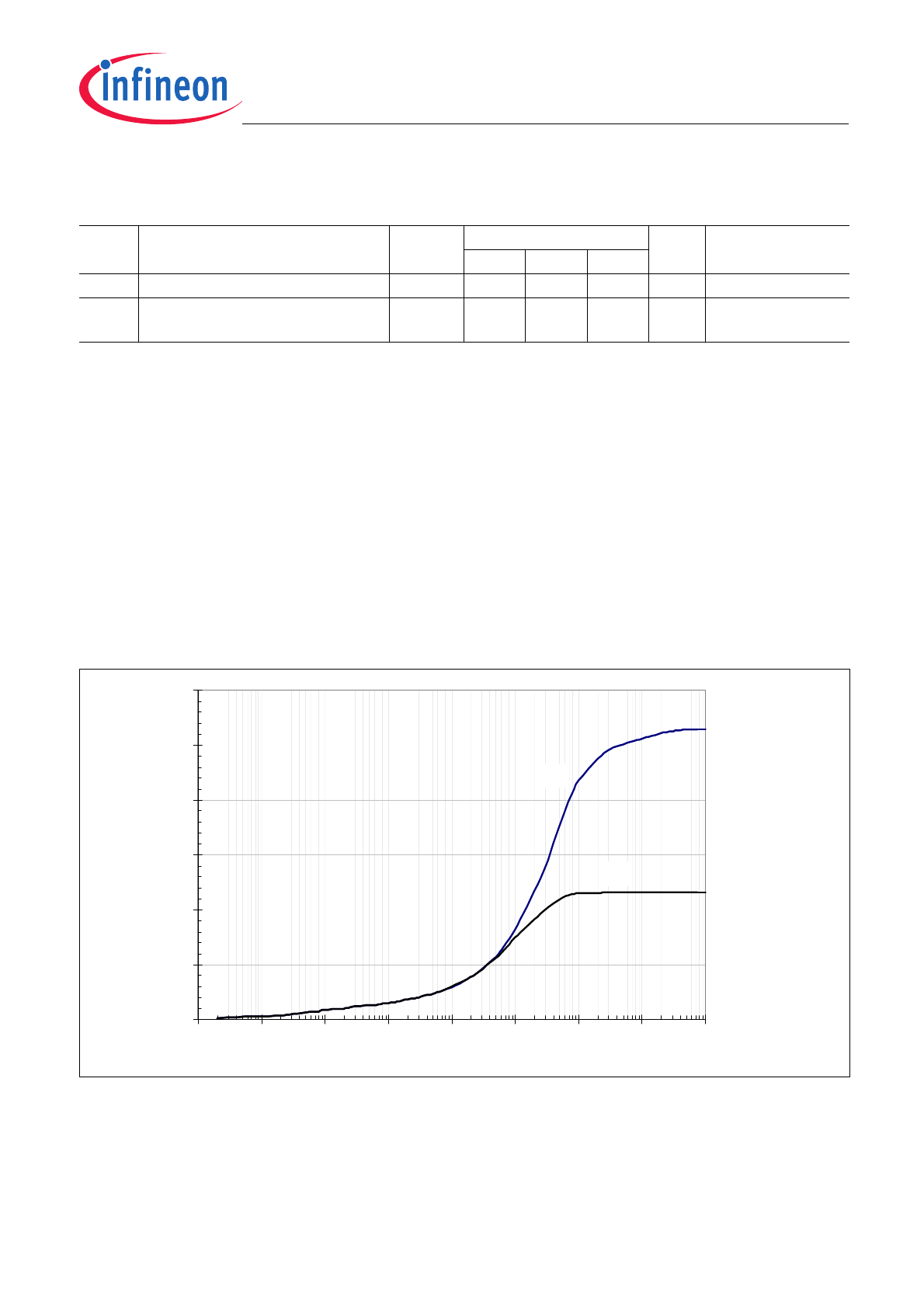

Figure 4

Typical Transient Thermal Impedance single pulse,

Z

thJA

and

Z

thJC

Pos.

Parameter

Symbol

Limit Values

Unit

Conditions

Min.

Typ.

Max.

4.2.1

Junction to Soldering Point

R

thJC

–

–

38

K/W

1)

2)

1) Not subject to production test, specified by design.

2) Device mounted on PCB according EIA/JEDEC standard JESD51-7 (4-layer FR4, 76.2 mm

× 114.3 mm with buried

planes). PCB is mounted vertical without blown air with 0.78W power dissipation generated in each channel on the DMOS.

4.2.2

Junction to Ambient

all channel ON

R

thJA

–

80

–

K/W

1)

2)

t

p

[ s ]

Zt

h

[

K

/

W

]

10

1

1

15

Zth_3405 .emf

10

-1

10

-2

10

2

10

3

10

-3

10

-4

10

-5

0

30

45

60

75

90

Z

thJC

Z

thJA

Data Sheet

9

Rev. 1.1, 2011-09-01

Smart Low-Side Power Switch

BTS3405G

General Product CharacteristicsThermal Resistance

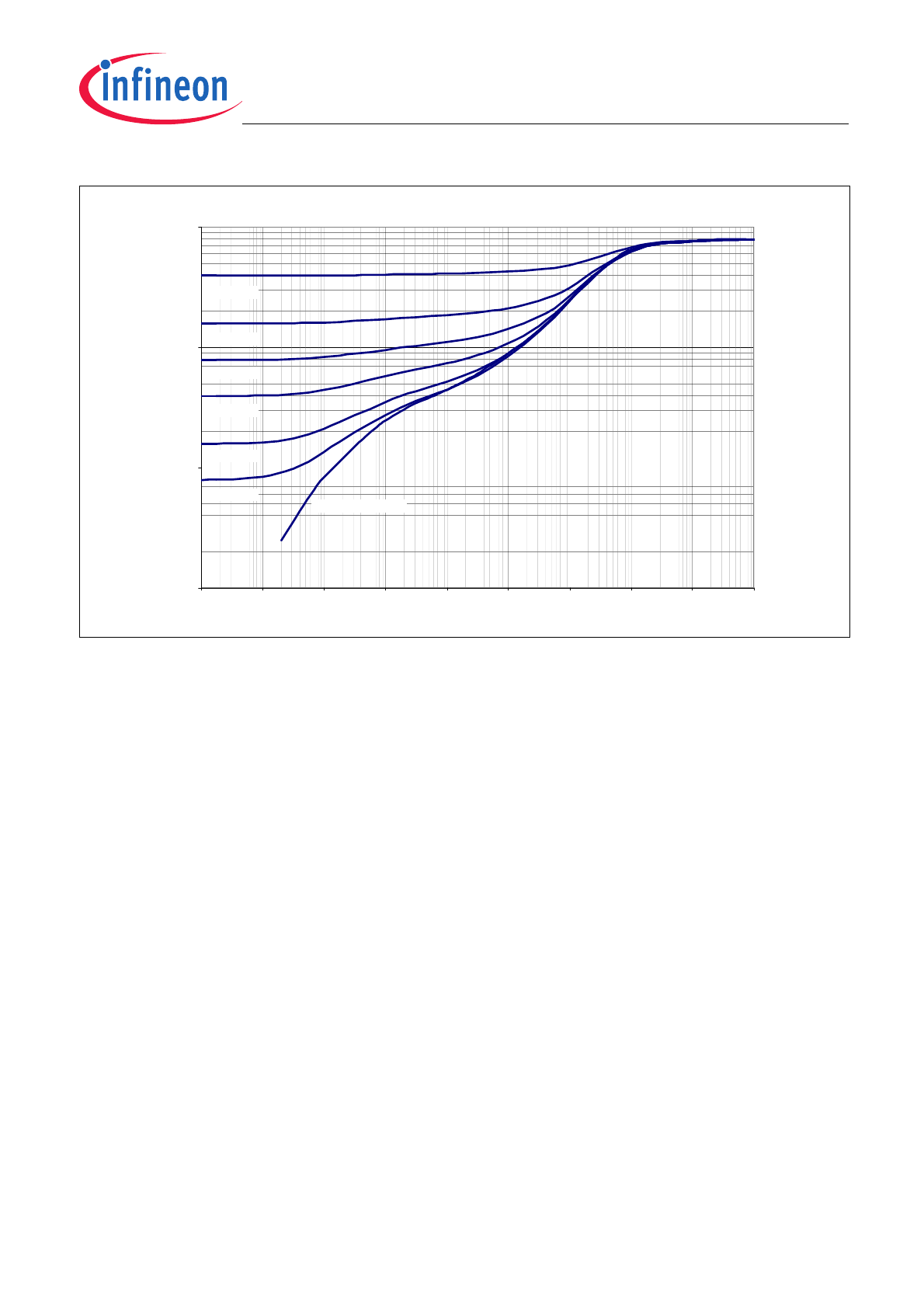

Figure 5

Typical Transient Thermal Impedance

Z

thJA

with different Duty cycles

Z

thJA

= f(t

p

) , D = tp/T, T

a

= 25 °C

Device mounted on PCB according EIA/JEDEC standard JESD51-7 (4-layer FR4, 76.2 mm

× 114.3 mm with

buried planes). PCB is mounted vertical without blown air with 0.78W power dissipation generated in each

channel for single pulse on the DMOS

Z

th

JA

[K

/W

]

10

-3

10

-2

10

-1

10

-1

10

-6

10

-5

10

-4

t

p

[s]

10

2

1

10

1

10

3

10

2

10

1

1

D = 0.5

D = 0.2

D = 0.1

D = 0.05

D = 0.02

D = 0.01

Single pulse

pulse_BTS3405_25 .emf

Smart Low-Side Power Switch

BTS3405G

Block Description and CharacteristicsInput and Power Stage

Data Sheet

10

Rev. 1.1, 2011-09-01

5

Block Description and Characteristics

5.1

Input and Power Stage

5.1.1

Input Circuit

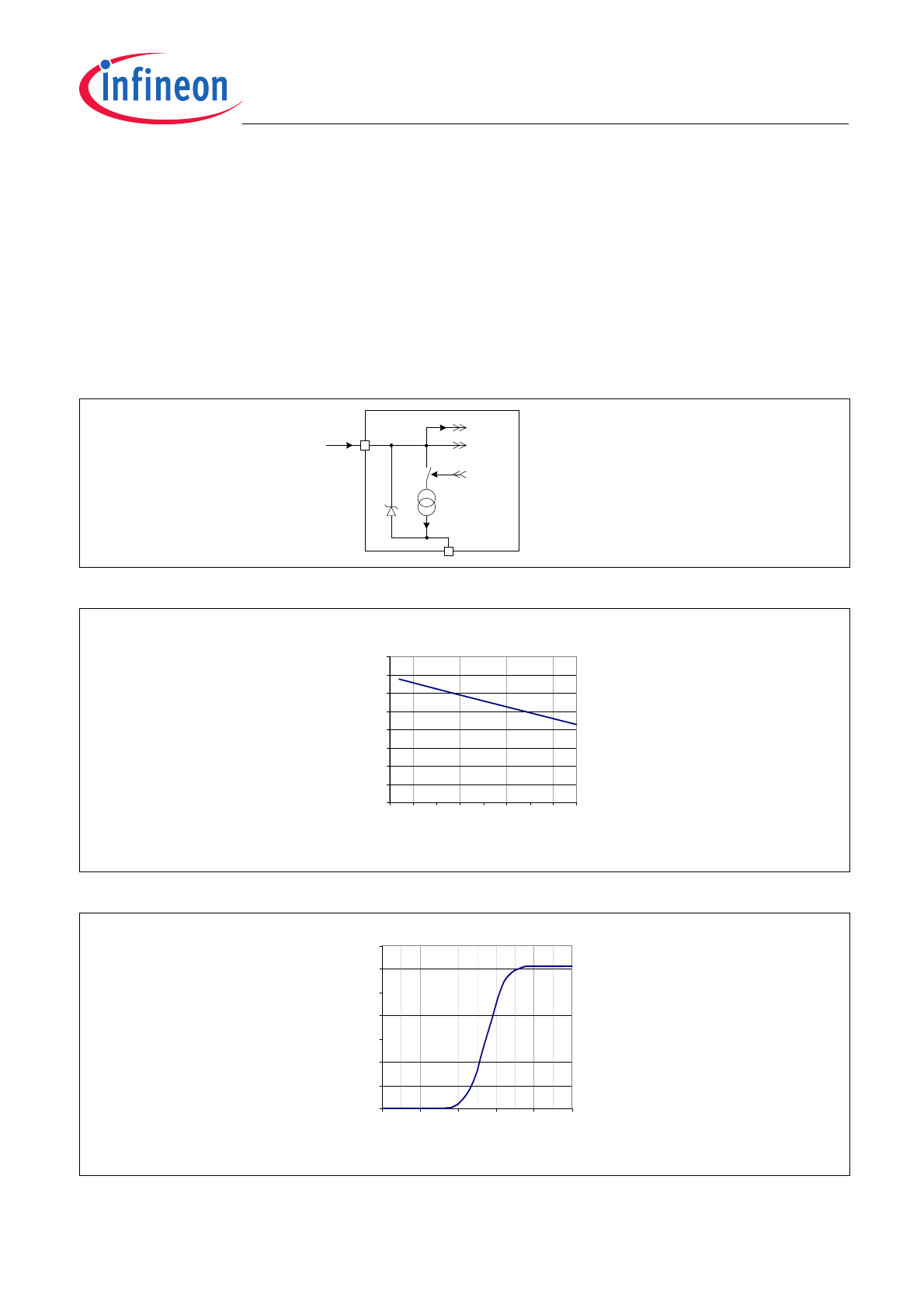

Figure 6

shows the input circuit of the BTS3405G. The zener Diode protects the input circuit against ESD pulses.

The internal circuitry is supplied by the input PIN. During normal operation the Input is connected to the Gate of

the power MOSFET. During fault condition the device tries to sink the current

I

INlim

in order to give the fault

information back to the driving circuit.

Figure 6

Input Circuit

Figure 7

Typical Input Threshold Voltage

V

inth

= f(

T

J

);

I

D

= 50

μA,

V

D

=

V

IN

Figure 8

Typical Transfer Characteristic

I

D

= f(

V

IN

);

V

D

= 12 V,

T

Jstart

= 25 °C

Input.emf

Source

Z

D

IN

I

IN

Gate

Fault

condition

I

INlim

I

INnom

Logic

0,00

0,25

0,50

0,75

1,00

1,25

1,50

1,75

2,00

-50

-25

0

25

50

75

100 125 150

V

IN

(t

h)

[

V

]

T [°C]

Vinth.emf

0

0,1

0,2

0,3

0,4

0,5

0,6

0,7

0

1

2

3

4

5

I

D

[ A

]

V

IN

[ V ]

Transferchar.emf